The FACETS hardware system features several hundred integrated computing nodes, each hosting up to 512 neurons which are interconnected and operated on un-cut silicon wafers. Special communication circuitry and protocols are developed especially for this hardware architecture. However, such a complex hardware system is of no use without appropriate software to operate it. One of the needed software components includes the mapping from biology to hardware.

Neural populations and network topologies are realized on the hardware by configuring a complex system of programmable routing switches, signal repeaters, and address decoders.

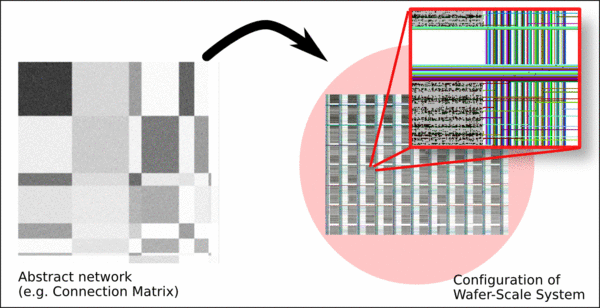

The task faced when employing the hardware system for an actual simulation is to configure its various components to realize the desired network model. This mapping task is not trivial. Moreover, it turns out that the high speed, small form factor, and low power consumption of the hardware system must be paid off by certain restrictions in flexibility probably disallowing to configure some desired inter-neuron connections.

Systematic mapping algorithms are developed in cooperation with the Technical University of Dresden to realize a given network model to the hardware system.

Mapping of a biological network description (left) into an actual configuration of the hardware components (right).

Realizing Biological Spiking Network Models in a Configurable Wafer-Scale Hardware System

Johannes Fieres, Johannes Schemmel, Karlheinz Meier

Proceedings IJCNN2008, IEEE Press (2008) [accepted for publication]

Keywords: wafer-scale, integration, neuromorphic, hardware, spiking, neural networks, analog, routing, graph model

Electronic Vision(s) Group – Dr. Johannes Schemmel

Im Neuenheimer Feld 227

69120 Heidelberg

Germany

phone: +49 6221 549849

fax: +49 6221 549839

email: schemmel(at)kip.uni-heidelberg.de

How to find us