Beetle - a readout chip for LHCb

Content

What is Beetle?

The ASIC laboratory of the university of Heidelberg and the Max-Planck-Institute for Nuclear physics in Heidelberg, together with the NIKHEF/Free University Amsterdam and Oxford University, develop a radiation hard read-out chip for the LHCb experiment. The chip will be useable for the LHCb Vertex Detector, the Silicon Tracker and the RICH.

Details about the latest Beetle chip can be found in The Beetle Reference Manual for Beetle version 1.3 / 1.4 / 1.5 (LHCb-2005-105).

The requirements (LHCb-2001-048) of the chip are mainly imposed by the LHCb key parameters. It is somewhat extended to make the chip more useable for other experiments. For example, the chip can either be used as an analogue pipeline chip or as binary pipeline chip.

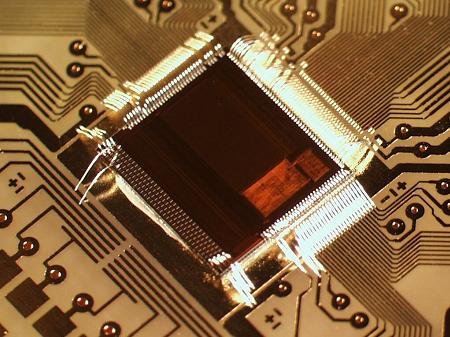

Picture of a Beetle readout chip

Picture of a Beetle readout chip

|

Block schematic of the Beetle chip

Block schematic of the Beetle chip

|

Each channel consists of a charge sensitive preamplifier/shaper, an analogue pipeline of a programmable maximum length of 160 stages with integrated derandomizing buffer of 16 stages and a serial read-out for up to 40MHz read-out speed. In case of using the chip as binary pipeline the discriminated output of the shaper is stored into the pipeline and a fast binary multiplexor is used to read out the chip at a speed of 80MHz maximum.

Read-out multiplexing can be done in several modes: for fastest read-out four ports, each carrying 32 channels can be used at 40MHz speed for analogue data and two ports carrying 64 channels running at 80MHz can be used for binary data. For applications which do not demand fast readout, a single port carrying 128 channels can be used and several chips can be connected to build up a read-out daisy chain, sharing a single read-out line.

In addition to the pipelined data path the combined signals of each four adjacent discriminators is send of the chip. All digital control and data signals are realized as low voltage differential signals (LVDS). The chip is programmable via the standard I2C interface.