### RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Tigran Mkrtchyan

Extension of the L1Calo PreProcessor System for the ATLAS Phase-I Calorimeter Trigger Upgrade

Dissertation

HD-KIP-23-18

#### Dissertation

submitted to the

#### Combined Faculty of Natural Sciences and

#### Mathematics

of the Ruperto-Carola-University of Heidelberg, Germany for the degree of

Doctor of Natural Sciences

Put forward by

Tigran Mkrtchyan

born in: Yerevan

Oral examination: 18-01-2023

# Extension of the L1Calo PreProcessor System for the ATLAS Phase-I Calorimeter Trigger Upgrade

Referees: Prof. Dr. Hans-Christian Schultz-Coulon

Prof. Dr. Ulrich Uwer

#### Zusammenfassung

Der hardwarebasierte Level-1-Kalorimeter-Trigger (L1Calo) des ATLAS-Experiments am Large Hadron Collider (LHC) wurde für die Run-3 Periode der Datenaufnahme verbessert. Durch neue und anspruchsvolle Algorithmen wird das Upgrade die Leistung des Triggers in einer herausfordernden, hohen Pile-Up Umgebung erhöhen und dabei die niedrigen Trigger Schwellwerte beibehalten.

Die Tile Rear Extension (TREX)-Module sind die neueste Erweiterung des L1Calo PreProcessor-Systems. Mit modernsten FPGAs und optischen Hochgeschwindigkeits-Transceivern liefern die TREX-Module digitalisierte hadronische Transversalenergien aus dem ATLAS Tile Calorimeter alle 25 ns an die neuen Feature Extractor-Prozessoren (FEX). Außerdem sind die Module so gestaltet, dass die Kompatibilität mit den ursprünglichen Trigger-Prozessoren erhalten bleibt. Das System aus 32 TREX-Modulen wurde entwickelt, produziert und erfolgreich in ATLAS installiert. Diese Arbeit beschreibt die funktionale Implementierung der Module und die detaillierte Integration und Inbetriebnahme in den ATLAS-Detektor.

#### Abstract

For the Run-3 data-taking period at the Large Hadron Collider (LHC), the hardware-based Level-1 Calorimeter Trigger (L1Calo) of the ATLAS experiment was upgraded. Through new and sophisticated algorithms, the upgrade will increase the trigger performance in a challenging, high-pileup environment while maintaining low selection thresholds.

The Tile Rear Extension (TREX) modules are the latest addition to the L1Calo Pre-Processor system. Hosting state-of-the-art FPGAs and high-speed optical transceivers, the TREX modules provide digitised hadronic transverse energies from the ATLAS Tile Calorimeter to the new feature extractor (FEX) processors every 25 ns. In addition, the modules are designed to maintain compatibility with the original trigger processors. The system of 32 TREX modules has been developed, produced and successfully installed in ATLAS. The thesis describes the functional implementation of the modules and the detailed integration and commissioning into the ATLAS detector.

# Contents

| A        | bstract                                                                        | v     |

|----------|--------------------------------------------------------------------------------|-------|

| 1        | Introduction                                                                   | 1     |

| <b>2</b> | Theoretical Background                                                         | 5     |

|          | 2.1 The Standard Model of Particle Physics                                     | 5     |

| 3        | The LHC and the ATLAS Experiment                                               | 9     |

|          | 3.1 The Large Hadron Collider                                                  | 9     |

|          | 3.2 The ATLAS Detector                                                         | 12    |

| 4        | The Trigger and Data Acquisition of ATLAS                                      | 19    |

|          | 4.1 The Level-1 Trigger System                                                 | 20    |

|          | 4.2 The Central Trigger Processor                                              | 25    |

|          | 4.3 The DAQ and the Higher-Level Trigger system                                | 25    |

| 5        | The Upgrade of the Level-1 Calorimeter Trigger                                 | 27    |

|          | 5.1 Motivation for the upgrade                                                 | 27    |

|          | 5.2 New L1Calo Trigger system                                                  | 28    |

| 6        | The L1Calo PreProcessor and the TREX                                           | 37    |

|          | 6.1 Hardware design, from prototyping to production                            | 37    |

|          | 6.2 Adapting the PPMs for TREX compatibility                                   | 42    |

|          | 6.3 Control, configuration of the TREX and the interface with the PreProcessor | or 44 |

|          | 6.4 Clocking and trigger information                                           | 51    |

|          | 6.5 The Real-time data path                                                    | 53    |

|          | 6.6 The Readout data path                                                      | 63    |

|          | 6.7 The System-On-Chip and Monitoring                                          | 70    |

| 7        | Functional Tests                                                               | 85    |

|          | 7.1 Test software suite                                                        | 85    |

|          | 7.2 Acceptance tests                                                           | 85    |

viii Contents

|                | 7.3          | Power and thermal measurements                  | 87  |

|----------------|--------------|-------------------------------------------------|-----|

|                | 7.4          | Clock stability measurements                    | 88  |

|                | 7.5          | Latency measurements                            | 89  |

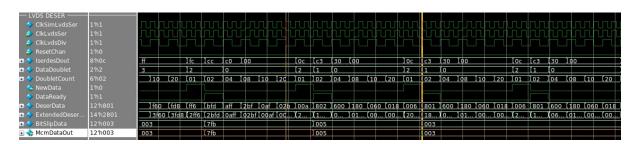

|                | 7.6          | LVDS transmission measurements                  | 94  |

|                | 7.7          | Signal integrity of the high-speed transmission | 95  |

| 8              | Inst         | allation, Commissioning and First Data          | 99  |

|                | 8.1          | Installation in ATLAS                           | 99  |

|                | 8.2          | Connectivity and Fibre Mapping                  | 103 |

|                | 8.3          | Integration with the legacy trigger systems     | 106 |

|                | 8.4          | Integration with the FEX systems                | 108 |

|                | 8.5          | Interfaces to the DAQ                           | 111 |

|                | 8.6          | Performance and first data                      | 113 |

| 9              | Con          | aclusions                                       | 119 |

| $\mathbf{A}$   | Glo          | ssary and conventions                           | 123 |

| Li             | st of        | Figures                                         | 126 |

| List of Tables |              |                                                 | 134 |

| Bi             | Bibliography |                                                 |     |

| A              | cknov        | wledgements                                     | 143 |

# Chapter 1

### Introduction

At the Large Hadron Collider (LHC) protons are accelerated and collided at unprecedented centre-of-mass energies of up to  $\sqrt{s} = 13.6$  TeV and instantaneous luminosities of around  $\mathcal{L} = 10^{33} \, cm^{-2} \, s^{-1}$ .

Situated around one of the interaction points is the ATLAS detector experiment, which studies the physics processes based on the slew of secondary particles resulting from the pp collisions. The sheer amount of data produced by the detector from the high interaction rate and the limitations of mass storage technology make a trigger system an absolute necessity in ATLAS. The trigger system searches through the dominating QCD background to find and select rare physics events of interest.

The ATLAS Level-1 Trigger is a fast, hardware-based system that performs decisions based on partial detector information and reduces the event rate from 40 MHz down to 100 kHz. The Level-1 Calorimeter Trigger exploits the fast nature of calorimeter signals to analyse the energy deposits and build high-level trigger candidates based on the shower shape development.

As the operating conditions of the LHC grow harsher in Run-3 with higher energies and an increased number of pp interactions, the ATLAS trigger system is undertaking a major upgrade. Utilising novel Field Programmable Gate Array (FPGA) -based technologies, the fully digital trigger system implements sophisticated object-finding and clustering algorithms.

To supply the new trigger algorithms with digitised hadronic energy deposits from the Tile Calorimeter, the Tile Rear Extension (TREX) module for the L1Calo PreProcessor (PPr) has been developed and commissioned in ATLAS. Equipped with advanced FPGAs and high-speed optical transceivers, the TREX system provides digitised hadronic transverse energy results optically to the upgraded trigger processors every 25 ns. The data provided by the TREX improves the identification of the trigger candidates, leading to higher efficacy. In parallel, the system maintains compatibility with the existing trigger processors, used in Run-1 and Run-2.

2 1-Introduction

The thesis discusses the development, testing, installation and commissioning of the TREX modules in ATLAS. Chapter 2 briefly describes the Standard Model. The LHC accelerator complex and the ATLAS detector are summarised in Chapter 3. Chapter 4 gives an overview of the ATLAS Trigger and Data Acquisition System. An overview of the new Level-1 Trigger system and its expected performance is given in Chapter 4. The functionality of the Tile Rear Extension modules is covered in Chapter 6. Chapter 7 presents the functional tests of the TREX modules. The installation in ATLAS and the operation of the final system are discussed in Chapter 8. The conclusions are presented in Chapter 9. A list of common naming conventions is available in the Glossary A.

#### **Author's Contributions**

As with large collaborations such as ATLAS, being a part of the Level-1 Trigger and calorimeter communities, the author received invaluable support and infrastructure to integrate the TREX modules in ATLAS. The work presented in this thesis has been carried out from July 2019 until November 2022.

The author's contributions started with developing test firmware and software for the prototype and pre-production TREX modules. Soon after, the author became the main firmware developer and system responsible, maintaining the designs for all FPGAs on the TREX and also on the PreProcessor Modules (PPMs)<sup>1</sup>. Throughout the thesis, the firmware functionality was developed in all aspects, while also preparing companion test and control software.

Multiple test procedures were designed and carried out for the TREX, which majorly contributed to the schematic and layout improvements for the final production version of the TREX hardware.

Once the final hardware modules arrived, all of the acceptance tests for the 40 boards and the assembly of the mechanics were conducted. The next contribution was the installation of the modules in ATLAS and configuring them to an operational state.

Most importantly, the author was responsible for fully integrating the TREX modules with the existing and upgraded DAQ and trigger systems by designing and improving the firmware functionality of all FPGAs.

In parallel, the author carried out the full development of the System-on-Chip firmware, operating system and the hardware monitoring framework.

In addition, as part of the ATLAS operations, the author became the main responsible and first responder regarding any issues of the PPr, for both PPMs and TREX systems. The contributions continued by analysing the first Run-3 collision data to validate the complete behaviour and functionality of the installed system.

<sup>&</sup>lt;sup>1</sup>Abbreviations are available in the Glossary A

1-Introduction 3

Overall, the author brought the TREX system from a concept to complete operation as part of the ATLAS detector in its entirety with stable and error-free running during pp collisions.

At the end of the thesis, the author also started developing the FPGA firmware and designing test routines for the hardware prototype of the Tile Calorimeter PreProcessor trigger interface (TDAQi) of the Phase-II upgrade for the High-Luminosity LHC. In relation to this, the Tile Calorimeter response to isolated hadrons using the Phase-II electronics in a testbeam environment was analysed.

# Chapter 2

# Theoretical Background

#### 2.1 The Standard Model of Particle Physics

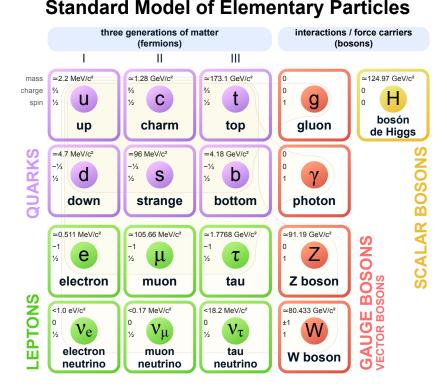

Leptons, quarks, and gauge bosons are three different types of fundamental elementary particles that interact with one another in three different ways: electromagnetic (EM), weak, and strong interactions. This ensemble of quantum field theories is known as the Standard Model (SM). Quantum Electro-Dynamics (QED), which makes predictions that have been confirmed by a large number of experimental results up to extremely high precision, governs electromagnetic interaction. It is unified with weak interaction theory, and the two are frequently referred to as the Electro-Weak (EW) sector of the Standard Model. The interactions between quarks and gluons carrying colour charge are mediated via the strong force that is described by Quantum Chromo-Dynamics (QCD).

Together QCD and the Glashow-Weinberg-Salam (GWS) models form the SM, which is symmetric under the Poincaré-group of special relativity as well as the combined gauge groups:  $SU(3)_C \otimes SU(2)_L \otimes U(1)_Y$ , where C stands for colour, L for left-handed and Y for hypercharge.

Quarks are fermions with a spin- $\frac{1}{2}$  that carry a fractional electrical charge and colour. They take part in each of the three groups of interactions. The Six quarks up (u), down (d), charm (c), strange (s), top (t), and bottom (b) are divided into three generations. Only the u and d quarks from the first generation are the fundamental components of ordinary matter. They make up the neutrons (udd) and protons (uud) necessary to build any atomic nucleus. Each quark has an antiquark that has identical mass, but differs in quantum numbers such as electrical and colour charges, which are the opposite. All hadrons, including nucleons, unstable mesons, and hyperons, are made up of quarks and antiquarks.

#### Figure 2.1. The Standard Model of Elementary Particles [1]

Fig. 2.1 presents the list of particles included in the SM. For each particle the mass, electrical charge and spin values are given.

The leptons e,  $\mu$  and  $\tau$  are also spin- $\frac{1}{2}$  fermions with an integer electrical charge and no colour. The three associated neutrinos,  $\nu_e$ ,  $\nu_\mu$ , and  $\nu_\tau$  are electrically neutral and only participate in weak interactions, whereas the charge leptons also partake in EW interactions. Leptons are also divided into three generations and have anti-leptons with an opposite electric charge. The only component of ordinary matter is the electron, which together with nuclei forms all atoms in the universe.

The carriers of the fundamental interactions are the gauge bosons. The electromagnetic interaction is transmitted via a massless spin-1 boson, the photon  $(\gamma)$ , whereas the weak interaction is transmitted via the exchange of the massive  $W^{\pm}$  and Z spin-1 bosons. The strong force is carried by eight gluons (g), neutral, massless vector bosons that carry colour charges.

The Higgs-Englert-Brout mechanism of spontaneous symmetry breaking in the EW sector generates the masses of fermions (potentially excluding neutrinos) as well as the masses of the weak gauge- and the Higgs-boson. It was predicted back in the 1960s [2].

The Higgs boson associated with this measurement has been discovered by ATLAS [3] and CMS [4] at the LHC in 2012.

The experimental development of the SM has advanced quickly over the past few

decades. However, there are still fundamental questions left unanswered, such as the hierarchy problem, matter-antimatter imbalance, dark matter, etc. These are the subjects of ongoing research, and different Beyond-SM (BSM) extension models are under study which could explain these phenomena. No signs of BSM physics have been observed so far except for neutrino oscillations. Nevertheless, SM theory has done an excellent job of describing a plethora of experimental evidence.

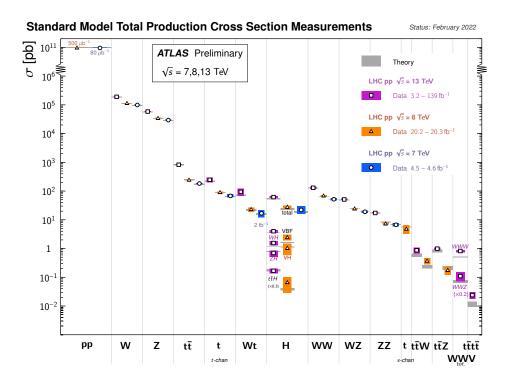

Fig. 2.2 presents the comparison of total production cross-sections measured by the ATLAS detector and predicted by the SM. As the centre-of-mass energy increases, so does the production cross-section, which can be easily seen from the W, Z,  $t\bar{t}$  cross-sections. With Run-3, the additional recorded data is set out to enhance BSM searches and allow for high-precision measurements of SM parameters.

**Figure 2.2.** The total production cross-sections predicted by the SM and measured by the ATLAS detector [5].

# Chapter 3

# The LHC and the ATLAS Experiment

#### 3.1 The Large Hadron Collider

The Large Hadron Collider (LHC) [6] is the most powerful particle accelerator in the world, located at the European Organisation for Nuclear Research (CERN¹) in Geneva, Switzerland. It is placed in a circular tunnel between 45m and 170m underground and boasts a circumference of 27 km. The LHC is designed for colliding beams of protons and heavy ions at unprecedented energies. It is an invaluable tool for probing a large phase-space in particle physics.

Two parallel beam pipes pass through 392 quadrupole and 1232 niobium-titanium dipole superconducting magnets, focusing and bending the particle beams in opposite directions. Additionally, several thousand corrector magnets are placed to precisely focus the beams near the interaction points. The beam acceleration is performed with 8 superconducting radio-frequency (RF) cavities operated at a frequency of 400.8 MHz, reaching record-breaking centre-of-mass energies of 13.6 TeV.

The LHC beams collide at four interaction points along the ring, where four major experimental detectors are located to measure the physics processes ensuing from the collisions. Two of the physics experiments are the general-purpose detectors A Toroidal LHC ApparatuS (ATLAS) [7] and Compact Muon Solenoid (CMS) [8]. They are designed for studying p-p collisions in the Terascale range. The A Large Ion Collider Experiment (ALICE) [9] detector is dedicated to heavy ion collisions, which allow for studying the physics of strong interactions and quark-gluon plasma. The fourth experiment, called the Large Hadron Collider beauty (LHCb) [10], is designed for precision measurements of CP violation, B-meson decays and matter-antimatter asymmetries.

<sup>&</sup>lt;sup>1</sup>Derived from Conseil Européen pour la Recherche Nucléaire

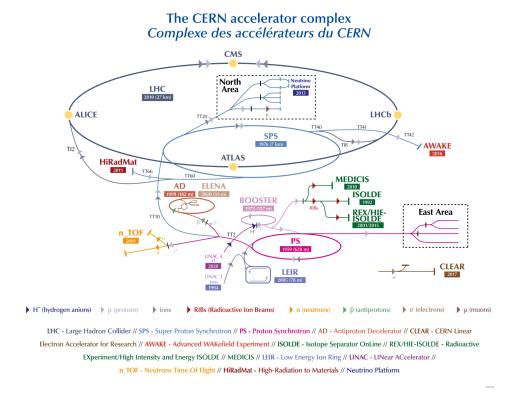

Figure 3.1. The CERN accelerator complex [11].

Fig. 3.1 illustrates the series of accelerator machines with progressively higher energies. The source of the protons is negatively charged hydrogen ion gas, which is stripped of its electrons through an electric field and accelerated by the LINAC4 linear accelerator. The beam of protons is then passed through multiple pre-acceleration circular accelerators, first through the BOOSTER, then the Proton-Synchrotron (PS) and finally the Super Proton-Synchrotron (SPS). The SPS brings the energy up to 450 GeV, at which point the beam is injected into the LHC ring.

The Run-1 period of the LHC beam operation began in 2010 with a ramp-up of the beam energy to 3.5 TeV. The beam operated at the same energy until November of 2011. In 2012 the beam energy increased to 4 TeV and delivered collisions until the end of Run-1, which was December 2012. After successful data-taking, the LHC accelerator complex was shut down for upgrades and maintenance that lasted until 2015. During this time, the detectors prepared for Run-2 with upgrades of their own. In 2015, Run-2 started successfully with LHC beam energies of 6.5 TeV. The machine operated until the end of 2018, delivering collisions far beyond its design. To prepare for Run-3 of the LHC, the detectors started an upgrade campaign in 2019. For ATLAS, it is referred to as the Phase-I upgrade. This upgrade went on for three years until July of 2022 when Run-3 began. Run-3 is planned to operate for four years until 2026, after which the upgrade for High-Luminosity LHC will commence, referred to as Phase-II.

| LHC Runs | Operating years | ATLAS Upgrade  |

|----------|-----------------|----------------|

| Run-1    | 2010-2012       | -              |

| Run-2    | 2015-2018       | Phase-0 (LS1)  |

| Run-3    | 2022-2026       | Phase-I (LS2)  |

| Run-4+   | 2029-           | Phase-II (LS3) |

**Table 3.1.** The naming conventions of LHC runs, the years of operation and the corresponding ATLAS upgrade phase.

#### The LHC bunch structure

The two LHC proton beams are ordered into bunches containing up to  $10^{11}$  particles. They circulate at a frequency of  $f_{orbit} = 11.245$  kHz, where one revolution around the LHC is called an *orbit*. The nominal bunch spacing is 25 ns, which corresponds to a  $f_{BC} = 40.08$  MHz bunch clock. The harmonic number of the LHC constrains the number of possible slots, where a bunch can be assigned:

$$h = \frac{f_{BC}}{f_{orbit}} = 3564 \tag{3.1}$$

This means that per orbit, there are 3564 potential Bunch-Crossing (BC) slots where a collision between the opposite travelling beams can occur. Each BC is assigned with a unique number from 0 to 3563, commonly referred to as Bunch-Crossing Identifier (BCID). Even though there are 3564 BCs, the fill pattern is not necessarily uniform. There are BCs where both, one or neither bunches of the two beams are filled. The maximum occupancy of the filled bunches is 2808 within one orbit. This is due to operational restrictions and standards that permit steady and secure beam operation. A gap of 120 BCs is dedicated to the beam extraction kicker magnet to extract the beam out of the LHC. This occurs at the end of the orbit and is called the abort gap. There are further gaps for calibration purposes and the LHC ensures none of the bunches within this gap contain protons.

During data-taking, the protons are typically distributed in a train structure with alternating filled and empty bunches. When the bunches of both beams are filled for a particular BC, then this BC is called *paired*. When only one beam contains protons, that BC is called *unpaired*.

#### Luminosity and Pileup

The performance of the LHC is quantified through the delivered Luminosity and the  $\sqrt{s}$  centre-of-mass energy. The luminosity can be defined as a first approximation:

$$\mathcal{L} = \frac{f_{orbit} n_b N^{(1)} N^{(2)}}{4\pi \sigma^{(1)} \sigma^{(2)}}$$

(3.2)

where  $N^{(1)}$  and  $N^{(2)}$  are the number of protons in each bunch and  $n_b$  is the number of filled bunches. The transverse beam sizes of each beam at the interaction point are  $\sigma^{(1)}$  and  $\sigma^{(2)}$ .

The number of collision events can be expressed as a function of the luminosity and the cross section for a given physics process. Taking the total cross section  $\sigma_{tot}$  for any SM pp interaction, the event rate will be:

$$\frac{dN}{dt} = \sigma_{tot} \mathcal{L} \tag{3.3}$$

Therefore, the mean number of interactions per collision  $\langle \mu \rangle$  can be expressed as:

$$\mu = \frac{\sigma_{tot}}{n_b f_{orbit}} \mathcal{L} \tag{3.4}$$

Through the LHC operation runs the mean number of interactions per collision has varied from an average of  $\langle \mu \rangle \simeq 13$  up to  $\langle \mu \rangle \simeq 33$ . This indicates that the hard scatter event is contaminated with additional soft interactions, which is known as pileup.

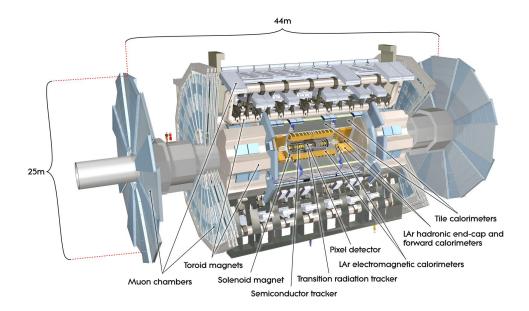

#### 3.2 The ATLAS Detector

The ATLAS detector is a general-purpose detector located in one of the four experimental caverns 100 m below ground. It consists of a cylindrical *barrel* around the centre of the interaction point, creating a rotational symmetry around the beam axis. Two endcaps are attached to the barrel, one on each side.

The detector itself contains multiple layers of sub-detectors. Starting from the interaction point, the first subsystem is the Inner Detector, dedicated to particle track reconstruction and momentum measurements.

The next subsystems are the Electromagnetic and Hadronic Calorimeters, which measure the energy and position of the incident particles. The Muon Spectrometers surround the calorimeter system, composed of toroidal air cores and gaseous chambers.

An overview of the ATLAS detector is depicted in Fig. 3.2. It has a length of 46 m and a diameter of 25 m. The weight of the entire detector is approximately 7000 tonnes.

Figure 3.2. The ATLAS Detector [12].

#### 3.2.1 Coordinate System

The coordinate system used in ATLAS is right-handed with the p-p interaction point taken as its origin. The z-axis points in the direction along the beamline, while the x-axis is pointing radially towards the centre of the LHC ring and the y-axis points in the vertical direction. The azimuthal angle  $\phi$  spans from 0 to  $2\pi$  in the transverse x-y plane and the polar angle is defined from 0 to  $\pi$  relative to the z-axis. In particle detectors, typically, the pseudorapidity is used instead of the polar angle to describe the angle of the particle relative to the beam:

$$\eta = -\ln\left(\tan\frac{\theta}{2}\right). \tag{3.5}$$

At high energies, where the mass of the particle becomes negligible ( $m \ll \mathbf{p}$ ), the pseudorapidity approximates to the rapidity:

$$y = \frac{1}{2} \ln \left( \frac{E + p_z}{E - p_z} \right), \tag{3.6}$$

where the  $p_z$  is the momentum component in the z-direction.

#### 3.2.2 Inner Detector

The Inner Detector is the first point of detection in ATLAS, which is used for track reconstruction of the charged particles produced by the p-p collisions and for identifying the primary collision vertex along with decay vertices of short-lived particles. It is immersed

in a 2 T magnetic field parallel to the beamline, which curves the path of the entering particles and allows to measure their momenta.

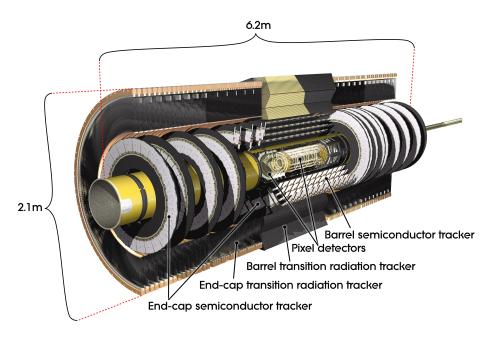

Fig. 3.3 shows an overview of the Inner Detector, which is made up of three different detector layers. In the barrel region, the layers are stacked up in concentric cylinders around the beam axis, while in the endcap region the detectors are arranged in disks perpendicular to the z-axis. The inner layer houses two high-resolution detectors, the Pixel Detector and the Semiconductor Tracker (SCT), while the outer layer is made up of the Transition Radiation Tracker (TRT). The acceptance for the Pixel and SCT detectors is  $|\eta| < 2.5$ , while for the TRT it is  $|\eta| < 2.0$ .

**Figure 3.3.** A cross-section of the ATLAS Inner Detector depicting the Pixel Detector, Semiconductor Tracker and the Transition Radiation Tracker [13].

The Pixel Detector is closest to the interaction point, just 3.3 cm away from the beam pipe. It consists of 4 layers of silicon pixels, with a pixel size of  $50 \times 400 \,\mu m^2$  in the outer layer and  $50 \times 250 \,\mu m^2$  in the innermost layer. Particles traversing through the pixels cause ionisation that is localised in the medium. The produced signals are used to measure the position of the trajectory with an intrinsic precision of around  $10 \,\mu m$ . With over 92 million channels, the Pixel Detector offers very high-granularity measurements of the vertex resolution in order to separate between production and decay vertices.

The SCT surrounding the Pixel Detector is used for track detection and reconstruction. It provides radially eight points in space per track, which add to the measurements of the particle momentum, impact parameter and vertex position. It is made up of over 4088 two-sided modules and over 6 million micro-strips, which provide a precision of up to  $25 \,\mu m$ .

The final layer of the Inner Detector is the TRT. It consists of 350000 thin-walled

drift tubes or straws. Each of the straws has a surface diameter of  $4\,mm$ , made of conductive-coated Kapton. A  $30\,\mu m$  gold-plated tungsten wire is placed in the centre and the straw is filled with a gas mixture of 70% Xe, 27% CO2 and 3% O2. The TRT combines the principle of ionisation and the transition radiation effect for particle identification and track reconstruction. As a relativistic particle crosses the boundary between materials with different dielectric constants, it emits photons proportional to the Lorentz factor. The wavelength of the radiated photons is proportional to the mass of the incident particle, which allows differentiation between lighter and heavier particles.

#### 3.2.3 Magnet System

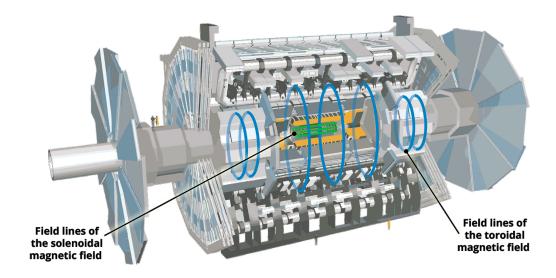

The ATLAS magnet system consists of four superconducting magnets, that bend the trajectories for particle identification and momentum measurements. The central solenoid magnet provides a powerful magnetic field of 2 T in the barrel region. The three outer toroid magnets supply the Muon Spectrometer with a field between 0.5 T and 1 T in magnitude.

**Figure 3.4.** The ATLAS Magnet System. The solenoidal magnetic field lines are illustrated in green, the toroidal magnetic field lines in blue [14].

Fig. 3.4 illustrates the magnetic field lines within the ATLAS detector. The magnetic field from the solenoid, shown in green, is contained in the central barrel region between the Inner Detector and the electromagnetic calorimeter, while the toroidal fields are present in the outer barrel and endcap regions of the muon spectrometer, forming a cylindrical magnetic field around the beam pipe.

#### 3.2.4 Calorimetry

ATLAS employs calorimetry to measure the energies and positions of charged and neutral particles produced by the colliding protons. The calorimeter system is composed of an electromagnetic and a hadronic calorimeter. The electromagnetic calorimeter is designed for containing electrons and photons through their electromagnetic interaction, such as bremsstrahlung and pair-production, while the hadronic calorimeter measures the energy of mostly hadrons through electromagnetic and strong interactions.

Both calorimeters are sampling calorimeters made up of alternating layers of dense material, called absorbers, and an active medium which produces a signal that can be detected. The incident particle interacts with the absorber material, lowering the energy and producing showers of secondary particles. To account for the energy loss in the absorber material, a *sampling fraction constant* is calculated during beam tests with electron and pion beams.

The sampling calorimeters have a lower energy resolution compared to homogenous calorimeters, where the whole calorimeter is composed of an active medium. However, sampling calorimeters have an advantage in the longitudinal and lateral segmentation, offering much higher spatial resolution and better particle identification through the shower shape.

Due to the non-compensating nature of the calorimeters, the overall calorimeter response for hadrons is lower than for particles interacting purely electromagnetically.

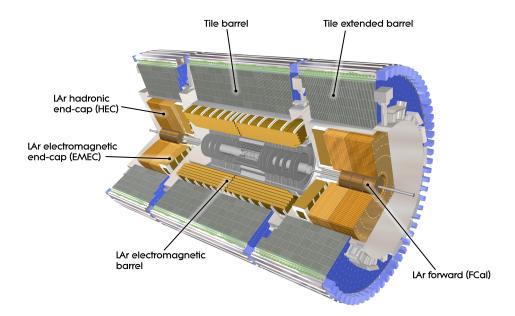

**Figure 3.5.** The ATLAS Calorimeters. LAr is shown in yellow-gold and the Tile in grey colour [15].

An overview of the ATLAS calorimeters is presented in Fig. 3.5. The electromagnetic

and hadronic calorimeters cover the region of  $|\eta| < 4.9$  and a full  $2\pi$  in  $\phi$ .

#### The Liquid Argon Calorimeter

ATLAS uses lead/liquid-Argon (LAr) [16] for the barrel electromagnetic barrel (EMB) and endcap (EMEC) calorimeter, while the hadronic endcaps (HEC) use copper and the forward calorimeters (FCAL) use tungsten plates as absorbers. The barrel region covers a range of  $|\eta| < 1.475$  while the endcaps cover  $1.375 < |\eta| < 3.2$ . The HEC covers  $1.5 < |\eta| < 3.2$  and FCAL  $3.1 < |\eta| < 4.9$ .

The accordion-shaped lead absorber plates in the central barrel region provide full azimuthal symmetry without cracks in  $\phi$ . The volume between the lead absorber plates is filled with liquid argon and submerged within are Kapton-Copper electrodes. The induced electromagnetic showers ionise the LAr atoms. The electrodes placed within the active medium collect the ionisation charges which produce a detectable signal.

#### The Tile Calorimeter

The Tile hadronic calorimeter (TileCal) [17] is situated in the central region of the detector, divided into a long barrel (LB) and an extended barrel (EB) modules on each side. The LB has a coverage of  $|\eta| < 0.8$ , while the EBs cover  $0.8 < |\eta| < 1.7$ . Both the LB and the EBs consist of 64 trapezoidal wedges with full  $\phi$  coverage, therefore each module has an azimuthal size of  $\Delta \phi = 0.1$ .

TileCal uses steel as absorbers and scintillating tiles as the active medium. The showers induced by the incident particles cause light production in the scintillators. The light is collected from opposite sides of each tile via two wavelength-shifting fibres and directed to a pair of photo-multiplier tubes (PMTs).

The PMTs convert the photons to an amplified electrical signal that is directly proportional to the energy deposited in the scintillator. The segmentation of each Tile module is done by grouping the wavelength-shifting fibres of corresponding tiles into two bundles, resulting in a cell granularity of  $\Delta \eta = 0.1$

Radially, the barrel is segmented into 3 sampling depths with interaction lengths of 1.4, 3.9 and 1.8. The fast PMT signals are amplified and shaped on-detector, in order to mitigate aliasing effects during digitisation.

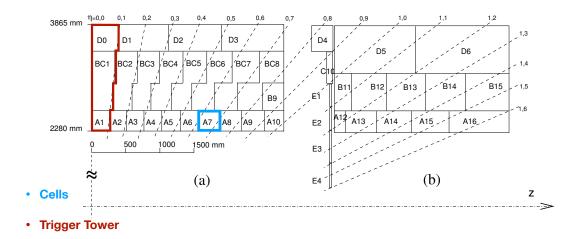

For the Level-1 Calorimeter trigger, the analogue PMTs signals of cells are summed radially, creating reduced granularity trigger-towers and sent to the PreProcessor system, which will be discussed in Chapter 4. Fig. 3.6 illustrates the TileCal segmentation, where a cell is outlined in blue, while a trigger-tower is shown in red.

**Figure 3.6.** Segmentation of the Tile Calorimeter for the Long Barrel (a) and the Extended Barrel (b) [18].

#### 3.2.5 Muon Spectrometers

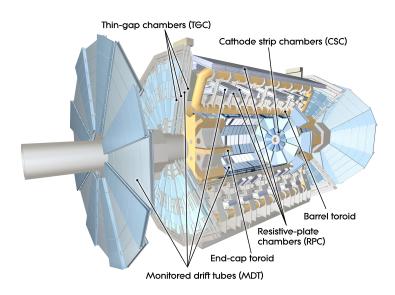

Figure 3.7. A cut-out of the ATLAS detecter illustrating the Muon Spectrometers [19].

The ATLAS Muon Spectrometers form the last layer of the detector and are divided into two groups of gaseous detectors.

The first group consists of Monitored Drift Tubes (MDTs) and Cathode Strip Chambers (CSCs) for measuring the momenta of the particles that manage to pass through the calorimeters, with their trajectories curving under the toroidal magnetic fields.

The second group is made up of Resistive Plate Chambers (RPCs) in the central barrel region and Thin Gap Chambers (TGCs) in the endcaps. The fast gaseous detectors measure the particle coordinates for triggering purposes.

Fig. 3.7 presents the four different types of muon detectors in ATLAS. The high-precision tracking MDTs and CSCs cover the region of  $|\eta| < 2.7$ . The RPCs and the TGCs, used for the trigger system, have an acceptance of  $|\eta| < 2.4$ .

# Chapter 4

# The Trigger and Data Acquisition of ATLAS

The ATLAS detector produces a tremendous amount of data at a rate of 40 MHz and an event size of roughly 1.5 MBs. Storing all of the data is impossible due to bandwidth and storage limitations, thus a trigger system is implemented to reduce the rate by selecting events with physics signatures of interest.

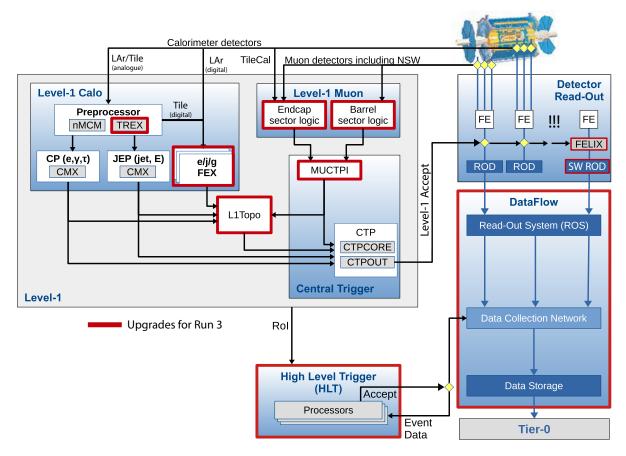

The Trigger and Data Acquisition (TDAQ) system [20] of the ATLAS experiment is tasked with treating the huge data flow produced by the subdetectors. The trigger system consists of a hardware-based first-level (L1) trigger and a higher-level software-based filter. The Level-1 Trigger is based on custom and commercial electronics and processes the data with strict latency requirements.

Each sub-detector front-end contains a pipelined memory buffer, where the incoming event data is placed at a rate of 40 MHz. These buffers are large enough to store approximately  $2.5~\mu s$  worth of data, hence the trigger decision from the Level-1 must arrive within that time constraint. The data remains in the pipeline and awaits a trigger decision by the Central Trigger Processor (CTP) [21] in the form of a Level-1 Accept (L1A) signal that is distributed to all sub-detectors. The maximum rate of the L1A is around 100 kHz, causing 400 times reduction in the rate.

After the event passes the conditions imposed by the L1 Trigger System, the DAQ system is responsible for aggregating the transfer of event data from the detector frontends, including the L1 processing hardware, to the HLT where the rate is further reduced to 1 kHz and written to permanent storage.

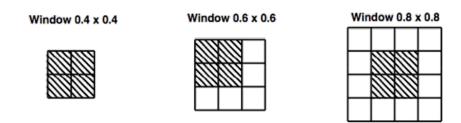

Fig. 4.1 outlines the ATLAS TDAQ system. It can be divided into four parts, the Level-1 Trigger, Detector Readout, the High-Level-Trigger and the DataFlow. The rectangles encircled in red showcase new and upgraded hardware and software added for Run-3.

Figure 4.1. Overview of the ATLAS TDAQ system, taken and modified from [22].

#### 4.1 The Level-1 Trigger System

The ATLAS Level-1 Trigger is made up of multiple sub-systems that search for events with high-energy electrons, photons, muons and jets. They use reduced granularity data from the calorimeter and muon systems to perform fast identification of various physics signatures. Once the objects have been identified, their information is collected and sent to the CTP, where the results are compared to 256 pre-defined trigger conditions.

For Run 3, both the calorimeter- (L1Calo) and muon-based (L1Muon) trigger systems have undergone major upgrades to improve the trigger efficiency. The upgrade of the L1Calo trigger is presented in Chapter 5.

#### 4.1.1 The Level-1 Muon Trigger

The L1Muon trigger uses the RPC and TGC chambers from the Muon Spectrometer system to identify muon candidates and their transverse momenta. The  $p_T$  of the muon candidate is compared to six programmable thresholds and assigned to the correct bunch crossing. Each of the 208 muon trigger sectors transmits data on muon candidates to the ATLAS Muon-to-CTP interface (MUCTPI) [23], which then determines the muon candidate multiplicity for each of the six transverse momenta  $(p_T)$  thresholds and delivers

it to the CTP.

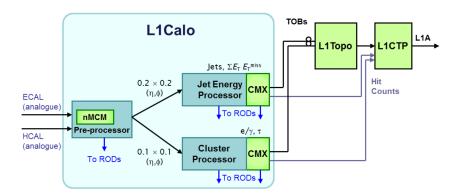

#### 4.1.2 The Level-1 Calorimeter Trigger

The ATLAS Level-1 Calorimeter (L1Calo) Trigger [24] is a pipelined system that receives around 7200 analogue signals from the electromagnetic and hadronic calorimeters. Both calorimeters have about 200000 cells in total. In order to process the full calorimeter granularity, it would require a large amount of cabling and an increase in the scale of the L1Calo system. Therefore, a reduced-granularity trigger-tower approach is used that lowers the number of input channels to about 7200.

The analogue pulses are digitised, synchronised and calibrated to transverse energy  $E_T$ . Based on the calorimeter  $E_T$  particle candidates are formed and their information is passed to the Level-1 Topological Trigger (L1Topo) and the CTP.

This section covers the legacy trigger system used in Runs 1,2 and also in Run-3. The upgrade system runs alongside the legacy, which is discussed in Chapter 5.

Figure 4.2. Overview of the L1Calo System in Run-2 [20].

Fig. 4.2 depicts the data flow through L1Calo. The green colour indicates upgrades performed in LS1, in preparation for Run-2.

#### **PreProcessor**

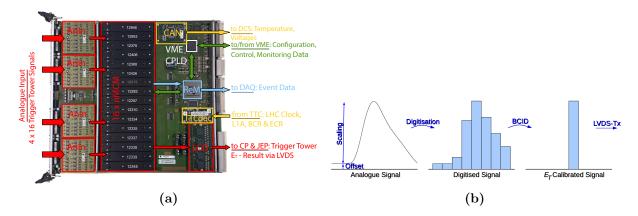

The L1Calo PreProcessor system is composed of 124 PreProcessor Modules (PPM) organised into eight VME<sup>1</sup> crates. Six crates process the analogue signals from the LAr calorimeter, while the other 2 are dedicated to Tile.

The PPM is a highly modular system, a base plane (carrier) holds 16 so-called Multichip-module (MCM) mezzanines. While the carrier itself remained unchanged since Run-1, the MCMs were upgraded for Run-2, called the new Multichip-Modules (nM-CMs) [25], from an Application Specific Integrated Circuit (ASIC)-based design to an FPGA. The choice of the FPGA was a Xilinx Spartan-6 [26] with plenty of room to

<sup>&</sup>lt;sup>1</sup>Versa Module Europa

accommodate the ASIC design and add a new layer of functionality improvements.

**Figure 4.3.** The PreProcessor Module in Run-2 (a) and its functionality (b), taken and modified from [27].

The calorimeter signals arrive in the form of bipolar differential signals. To prepare them for digitisation, first the signals are conditioned and converted to single-ended via the so-called An-In boards. Once the signals are ready to be digitised, they're used as an input for the nMCMs.

Every nMCM receives 4-channels as input, each of them corresponding to a trigger-tower covering a region of  $0.1 \times 0.1$  in  $\eta \times \phi$ . The digitisation is performed with 10-bit flash Analog-to-Digital Converters (ADCs) at a sampling frequency of 80 MHz, synchronous to the LHC clock. An adjustable fine-timing scheme allows the sampling clock phase to be shifted with steps of 1.042 ns.

After digitisation, a coarse timing procedure aligns the data and compensates for the signal propagation time due to cable length differences between the various parts of the calorimeter. It is realised through a First-In-First-Out (FIFO) memory buffer that has a maximum programmable depth of 16 Bunch-Crossings (BCs).

Once the ADC output data is aligned, a bunch-crossing identification logic assigns the energy deposition to the corresponding LHC bunch-crossing. The algorithm is performed through the use of Finite Impulse Response (FIR) Filters, where weighted sums are built over five ADC samples at a 40 MHz frequency<sup>1</sup>:

$$f_i = \sum_{j=0}^{5} c_j A_{i-2+j} \tag{4.1}$$

where the  $c_j$  are the coefficient weights,  $A_i$  is the ADC sample at the given BC and  $f_i$  is the filter output at BC i. To calculate the filter output, the ADC samples of the two previous and two next BCs are used. The set of coefficients used corresponds to an

<sup>&</sup>lt;sup>1</sup>Every other sample is taken from the digitisation at 80 MHz

Autocorrelation Filter scheme, following the pulse shape, where the signal-to-noise ratio is increased for the peak sample.

The peak finder algorithm [28] monitors the output of the FIR filters for a local maximum condition:

$$f_{i-1} < f_i \ge f_{i+1}. \tag{4.2}$$

When the condition is met, the FIR filter output is classified as the amplitude of the reconstructed pulse. Through the use of a programmable Look-Up-Table (LUT) the filter output is calibrated to transverse energy  $E_T$  in the electromagnetic scale. The resulting  $E_T$  value is 8-bits in length, with a range from 0 to 256 GeV and a resolution of 500 MeV per LSB for electromagnetic candidates.

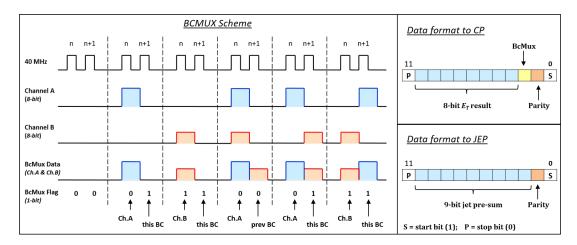

The transverse energy, resulting from the bunch-crossing identification, is transmitted to the Cluster and Jet-Energy Processors for further processing, via electrical Low-Voltage Differential Signals (LVDS).

The upgrade of the PPr for Run-3 is described in Chapter 6.

#### Cluster Processor

The CP system consists of 56 Cluster Processor Modules (CPM), distributed into four VME crates.

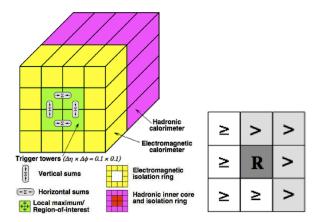

Energy clusters deposited in the calorimeters that correspond to isolated electron, photon, or hadronically decaying tau candidates are identified through the CP system. The CP system receives the digitised 8-bit  $E_T$  results from the PPr with a resolution of  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ . Two algorithms are used to perform the identification, one for  $e/\gamma$  and one for  $\tau/hadrons$ . Both algorithms are based on a 4 × 4 trigger-tower window in the electromagnetic and hadronic layers. The window contains a *core*, made up of the central 2 × 2 towers, surrounded by an isolation ring. Within the core, four possible  $E_T$  sums are computed with neighbouring trigger-towers and evaluated against programmable thresholds.

The algorithm looking for  $e/\gamma$  candidates applies a selection where the induced shower is localised within two neighbouring trigger-towers and no energy deposits are detected in the hadronic layer. Here, the isolation ring is used to identify narrow electromagnetic showers. The  $\tau/hadrons$  algorithm uses the same core as the other algorithm but adds the contribution from the core of the hadronic layer.

In order to avoid double counting the same trigger object  $E_T$  sums of both the electromagnetic and hadronic cores are compared to eight equally sized areas within the  $4 \times 4$  window. After comparing all 8 regions, the core with the local maximum is identified as the trigger object and the corresponding  $\eta - \phi$  coordinate is sent to the HLT as a Region of Interest (RoI).

**Figure 4.4.** The CP algorithm (left) depicting the core (local maximum) and the isolation and the definition of the RoI (right) [24].

Fig. 4.4 illustrates the CP trigger algorithms on the left-hand side, where the core region is depicted in green and the isolation ring in yellow. The right-hand image presents the eight neighbouring regions where a local maximum is searched for.

#### **Jet-Energy Processor**

The JEP system is made up of 32 Jet/Energy Processor Modules (JEM) within two VME crates.

The JEP algorithms search for jets and calculate sums such as the total, missing and jet-sum transverse energies. The data received from the PPr is a coarser 9-bit jet-sum with a resolution of  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$ . The JEP employs a sliding window algorithm, similar to the CP, with 3 different sizes and moves within the calorimeter coverage by single steps in  $\eta - \phi$ . At each step, jet-elements are built by summing the jet-sums with sizes of  $2 \times 2$ ,  $3 \times 3$  and  $4 \times 4$  and the summed  $E_T$  is then compared to programmable thresholds. In this case, the RoI is also based on the region with a local maximum and sent to the HLT.

**Figure 4.5.** The three sizes of the sliding window of the JEP algorithm [24].

Fig. 4.5 depicts the three sliding window sizes employed by the JEP algorithm.

#### Level-1 Topological Trigger

Particle candidates identified by the L1Calo and L1Muon systems are sent to the Level-1 Topological (L1Topo) trigger systems, where selection criteria, based on the event topology, are used to make a trigger decision. The criteria include cuts to the invariant mass or to the angular spacing between particle candidates.

#### 4.2 The Central Trigger Processor

The final step in the Level-1 trigger system's processing is the Central Trigger Processor (CTP). It gathers digital trigger signals from several forward detectors, the MUCTPI, L1Calo, L1Topo and time-aligns them. In addition, it manages deadtime, prescales, and implements the trigger logic setup in accordance with the physics trigger menu.

The CTP applies dynamically adjustable prescales to each trigger item in order to regulate rates, especially for trigger items which have low energy thresholds. A prescale factor of n means that only every n'th event of that trigger item is accepted. This serves as a reduction factor of the trigger rate. Unprescaled trigger items are particularly significant since the adoption of a prescale imparts a statistical bias to the trigger selection. Unprescaled triggers with the lowest energy thresholds are primarily used as the main trigger during data analysis.

Furthermore, the CTP receives the timing signals from the LHC machine, such as the 40.08 MHz clock and distributes them to all detector sub-systems through the network of ATLAS Local Trigger Interface (ALTI) [29] modules.

The ALTI system is also used to distribute the trigger signal generated by the CTP, called the Level-1 Accept signal, and other Timing, Trigger and Control (TTC) commands to the sub-detectors.

#### 4.3 The DAQ and the Higher-Level Trigger system

Upon the issuance of an L1A, all of the detector data that was previously stored in pipeline memories is moved to a different set of storage elements called read-out buffers (ROBs), where it remains until it is validated or ignored by the HLT.

For Run 3, the ATLAS readout system is upgraded with two main components [30]. The first is the Front-End Link EXchange (FELIX) system, which is made up of PCIe FPGA cards and high-speed network interfaces, housed in commodity servers. The FELIX system acts as a router between the detector sub-systems and the switched Data Collection Network. The second component is the Software ReadOut Driver (SW ROD),

which performs data aggregation, buffering, detector-specific processing, and routing to the HLT.

The HLT consists of a computing farm using commodity servers. There are around 40000 physical cores which analyse the events triggered by L1 and reduce the output rate further to around 1.5 kHz. The filtered events are then written to mass storage. The HLT software has seen a massive upgrade for Run 3, in particular, the software is now multi-threaded, which brings improvements to memory consumption and performance. [31]

# Chapter 5

# The Upgrade of the Level-1 Calorimeter Trigger

#### 5.1 Motivation for the upgrade

The ATLAS recorded integrated luminosity is estimated to be at 300 fb<sup>-1</sup> by the end of Run-3. The collected dataset will allow for precision measurements in the Higgs production and for many Standard Model physics processes. It will also offer a large phase-space for Beyond-Standard Model (BSM) searches. To enrich the recorded data with a wide coverage of physics processes, the L1 Trigger must be able to search and identify many interesting physics signatures with high efficiency.

The decays of electroweak particles like the W, Z, and Higgs bosons, which have masses between 80 and 125 GeV, span a significant portion of the trigger phase space. These electroweak particles primarily decay to leptons and jets, producing detector objects that typically have a transverse momentum greater than 30 GeV. The most useful Level-1 trigger signatures for electroweak-scale particles are that of isolated electrons and muons, which predominantly originate from the decay products of W and Z bosons.

One of the main objectives of the Phase-I upgrade is to maintain low- $p_T$  trigger thresholds at Level-1 for single electrons and muons. Maintaining unprescaled Level-1 triggers on the low- $p_T$  objects will increase the data samples for high precision and new physics measurements. It will also yield data samples that can be studied in more detail, leading to physics results with low systematic uncertainty.

The ability to perform physics measurements with electroweak-scale particles that result in jets, missing transverse momentum and hadronically decaying tau leptons is also a key objective of the Phase-I upgrade. In comparison to muons and electrons, signatures of these objects are less distinct due to their shower shapes within the calorimeter, discussed further in this chapter. In order to achieve rates that can be supported by the ATLAS TDAQ system, it is preferable to combine numerous trigger objects at Level-1

(including very low- $p_T$  electrons and muons, if suitable) in order to trigger on these decay products of electroweak-scale particles effectively.

## 5.2 New L1Calo Trigger system

The original L1Calo design, using over 7000 analogue inputs of coarse granularity calorimeter information, was very successful in the first 10 years of LHC operation, which already provided integrated luminosities beyond design.

However, the expected higher luminosities in future LHC operation will compromise the efficacy of the original hardware, and so an upgrade of the system has been built and installed during the recent LHC shutdown period. The basis of the improvement was to increase the level of detail of information available to the trigger, with more granular information both in longitudinal position and calorimeter depth.

In particular, this allows more sophisticated algorithms to be used based on shower shapes, while also aiding energy resolution in a higher pile-up environment. The higher data rate needed to transmit this additional information (approximately a factor of 10 in the electromagnetic layer) necessitated the use of a new digital trigger signal path which is integrated into the calorimeter outputs, replacing the old analogue path with digital signals at 40 MHz transferred on optical links. The algorithmic part of the Level-1 processing is performed on three Feature Extractors (FEX) which specialize in identifying different physics signatures.

The front-end electronics of the LAr has been upgraded during the Phase-I period, to provide L1Calo with fine-granularity digital information (SuperCells) [32] via optical fibres running at 11.2 Gb/s, in addition to the already existing analogue signal path. For each trigger-tower, ten so-called SuperCells with an area as narrow as  $\Delta \eta \times \Delta \phi = 0.025 \times 0.1$  in the front and middle layers, provide  $E_T$  information from the four longitudinal calorimeter layers. The digital data is sent to the FEX subsystems via an optical plant, called Fibre Optics eXchange (FOX) [33], which rearranges the input fibres to the mapping required by the FEX systems.

The Tile Calorimeter continues to send only analogue signals to L1Calo in Run-3. An upgrade of the Tile front-end electronics, to provide L1Calo with digitised data via optical fibres, is planned only for the Phase-II upgrade taking place after Run-3. To accommodate these plans, Tile Rear Extension (TREX) modules were built and installed in the two PreProcessor crates that process analogue signals from Tile Calorimeter, to extract copies of the digitised hadronic  $E_T$  values from the legacy trigger data path to CP and JEP, and to transmit them optically at 11.2 Gb/s to the FEXes.

**Figure 5.1.** Schematic of the L1Calo system in Run-3. The Phase-I upgrade modules are outlined in yellow. The existing legacy system is depicted alongside the new system in blue and green. Taken and adapted from [20].

The design of the new Level-1 Calorimeter Trigger is shown in Fig. 5.1.

The original (legacy) trigger system, shown in blue, is still maintained in place for the start of LHC Run-3, with necessary connections between the two, so that initial data-taking for physics purposes is not compromised while the new system is being understood and tuned for best performance. The Phase-I upgrade items are indicated in yellow.

#### 5.2.1 Overview

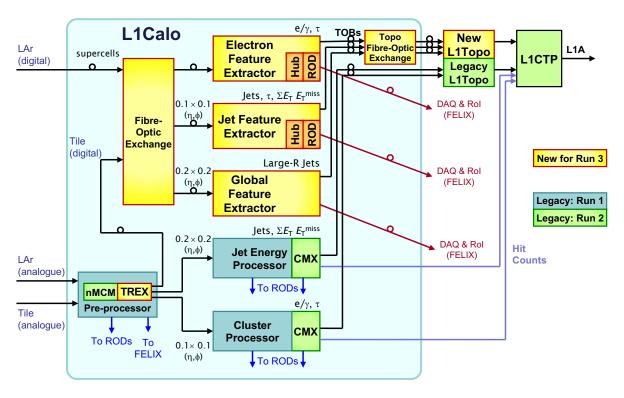

The FEX processors are built in the form of Advanced Telecommunications Computing Architecture (ATCA) blades, hosting multiple Field Programmable Gate Arrays (FP-GAs) and high-speed optical transceivers. The modules perform fast calculations to create higher-level trigger objects (TOBs) based on the calorimeter input. There are three flavours of FEX systems:

- electron Feature EXtractor (eFEX)

- jet Feature EXtractor (jFEX)

- global Feature EXtractor (gFEX)

A new Phase-I Level-1 Toplogical Trigger system is included in the upgrade, consisting of

three ATCA-based modules. Fig. 5.2 shows the production versions of the eFEX, jFEX and gFEX modules.

(a) eFEX module

Figure 5.2. Single modules of the eFEX, jFEX and gFEX [34].

#### **Electron Feature Extractor**

The electron Feature Extractor (eFEX) processes the finer-granularity SuperCell trigger information of the electromagnetic calorimeter in order to find narrow electron, photon or tau-like showers, using the full depth and spatial information of the shower development to better distinguish, and reject the dominant jet background. It consists of 24 individual ATCA-based modules running entirely independently and in parallel in order to handle smaller blocks of the central detector coverage. The eFEX system covers an area of  $|\eta| < 2.5$  and the whole  $\phi$  range and receives SuperCells from LAr and  $0.1 \times 0.1$  trigger-towers from Tile.

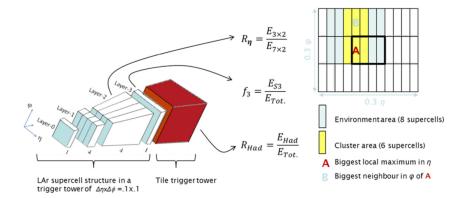

Figure 5.3. Overview of the eFEX trigger algorithm [35] with the calorimeter layer segmentation depicted on the left and the  $R_{\eta}$  condition on the right. The  $R_{\eta}$  cluster in Layer-2 is illustrated in yellow and the environment in blue. The seed cell A is the local maximum in  $\eta$ , B is the highest neighbour of A in  $\phi$ .

The  $e/\gamma$  algorithm [36] improves upon its CP counterpart, utilising the finer granularity cells from the electromagnetic calorimeter to identify narrow electromagnetic showers. A seed-finder algorithm scans the calorimeter cells in a window of  $0.3 \times 0.3$  ( $\eta \times \phi$ ) to determine the starting point of the cluster reconstruction. Within each window, the four central cells are compared to the surrounding area to find a local maximum. This comparison is done in parallel for the 36 cells.

Once the cluster with the highest  $E_T$  is found and classified as a particle candidate, two parameters are calculated for vetoing significant  $E_T$  contributions around the particle candidate:  $R_{\eta}$  and  $R_{had}$ .  $R_{\eta}$  is defined as the isolation of an electron candidate in the cluster in Layer-2 of the electromagnetic calorimeter. This is where the highest energy deposit occurs.

$$R_{\eta} = 1 - \frac{E_{cluster}}{E_{Env} + E_{cluster}} \tag{5.1}$$

Fig. 5.3 illustrates a schematic overview of the  $R_{\eta}$  parameter. The  $E_{cluster}$  is depicted in yellow and the surrounding area,  $E_{env}$ , in blue. The seed cell indicated with the letter A has the highest  $E_T$  and is classified as the local maximum. The highest neighbour is indicated with the letter B.

The second parameter  $R_{had}$  is defined as the ratio between the energy deposited in the hadronic calorimeter and the total energy. The electron candidates are expected to have a small  $R_{had}$  due to the showers induced by electrons being confined in the electromagnetic layer.

$$R_{had} = \frac{E_{had}}{E_{had} + E_0 + E_1 + E_2 + E_3} \tag{5.2}$$

The  $\tau$  algorithm [36] involves identifying narrow electromagnetic and hadronic clusters

and separating those from potential jet background. The seeding algorithm scans all towers in  $\eta - \phi$  and also longitudinally through the electromagnetic and hadronic layers. Once a seed with the highest  $E_T$  is found, the clustering is performed to find the energy of the tau candidate and the shower development in  $\phi$ . Due to the taus inducing narrower showers than jets, an isolation condition is applied to improve the efficacy of the algorithm.

#### Jet Feature Extractor

The jet feature extractor (jFEX) does not require the full granular information, and so consists of only 6 similar modules, assessing jet-like objects but with greater flexibility than the original JEP system for making regional corrections for pile-up effects.

In the central region of the calorimeters, the jFEX receives trigger-towers of  $0.1 \times 0.1$  in  $\eta - \phi$  from both LAr and Tile. However in the forward region, the granularity becomes coarser and  $\eta$ -dependant.

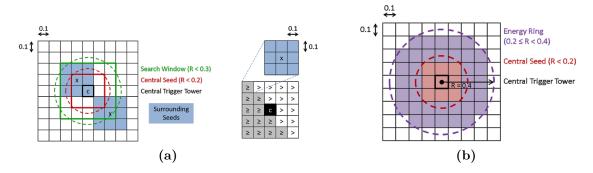

The jFEX small-radius jet algorithm [36] is based on a sliding window algorithm with a size of  $0.9 \eta \times 0.9 \phi$ . Around each trigger-tower within the window,  $0.3 \eta \times 0.3 \phi$ -sized sums are built to form so-called *seeds*. To identify the local maximum, the seeds inside a  $0.5 \eta \times 0.5 \phi$  search window are compared. In parallel to the seeding, jet energy sums are built around each trigger-tower by summing all towers within a radius of  $R^1 < 0.4$ .

Fig. 5.4 (a) illustrates the seeding algorithm used to identify local maxima. (b) presents the definition of a jet candidate with a radius of R = 0.4.

**Figure 5.4.** The diagram of the jFEX seeding algorithm (a) and the definition (b) of a jFEX jet candidate with a radius of R = 0.4 [36].

The jFEX tau algorithm [36] uses a larger area of up to  $1.7 \eta \times 1.7 \phi$  compared to the eFEX, therefore a larger isolation can be calculated which complements the eFEX algorithm. In addition to the jet and tau algorithms, the jFEX computes two global variables, the sum of the total transverse energy  $\sum E_T$  and  $E_T^{miss}$ .

#### Global Feature Extractor

<sup>&</sup>lt;sup>1</sup>Definition of  $R = \sqrt{\Delta \eta^2 + \Delta \phi^2}$

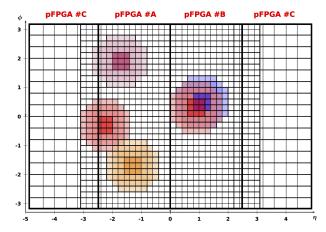

**Figure 5.5.** Example event with large-R jet candidates spanning across multiple FPGAs of the gFEX module [37].

The global feature extractor (gFEX) is a single module processing data from the whole detector at a coarser granularity of  $0.2 \times 0.2$  in  $\eta - \phi$ , also identifying jets and measuring missing energy, but being a single module, has the capacity to make full event-level corrections and identify large jet objects.

The large-R jet objects [36] are formed by summing of 69 towers from the electromagnetic and hadronic layers. Once the large-R jet object is formed, a pile-up density  $\rho$  is calculated and multiplied by the number of towers making up the jet object. This value is then subtracted from the jet energy. The pileup density is calculated event-by-event by dividing the sum of the tower  $E_T$  values below a programmable threshold by the number of towers that have an  $E_T$  below this threshold:

$$\rho = \frac{\sum_{i}^{N} E_{T,i}}{N} \tag{5.3}$$

The jet object with the highest  $E_T$  out of 32  $\phi$ -bins is transmitted to the L1Topo for a trigger decision.

Fig. 5.5 illustrates a simulated example of the large-R jet formation in gFEX. The  $\eta - \phi$  space is segmented into three regions, processed by separate FPGAs.

For the  $E_T^{miss}$  calculation, the "Jets without jets" algorithm is implemented in the gFEX, further described in [38].

### Phase-I Level-1 Topological Trigger

The results from these FEX modules will be further assessed by a new topological trigger system, which can apply flexible algorithms from the multiplicity counting up to complex multiple object-based topological algorithms.

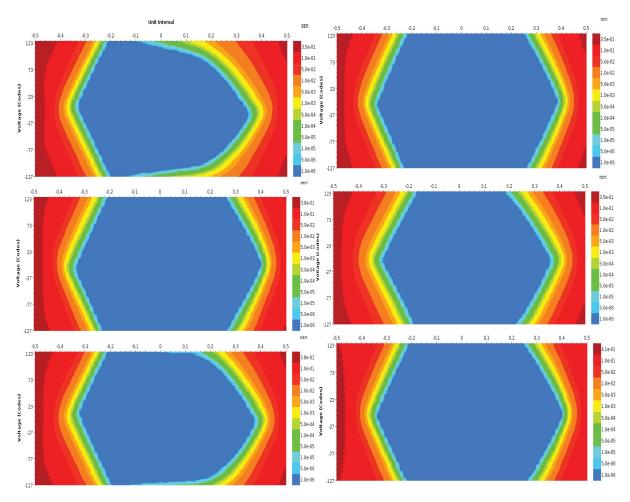

## 5.2.2 Expected performance

The new algorithms have been integrated as part of the ATLAS offline software framework. The algorithms performed by the FEXes are integrated into the offline simulation of the L1Calo system. Therefore they can be simulated to gauge the expected performance and behaviour for Run-3.

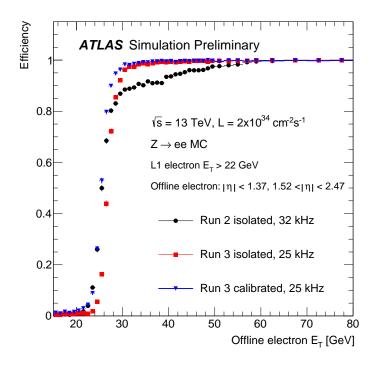

Figure 5.6. Single-electron efficiency comparison between Run-2 and the Run-3 eFEX [39].

An example of the expected single-electron trigger efficiency is depicted in Fig. 5.6. The results are based on Monte Carlo simulation of the  $Z \to ee$  process. The performance of the new Run-3 trigger is compared to the existing Run-2 electron trigger, and also to offline reconstructed electron candidates that satisfy a likelihood-based identification and gradient isolation.

The Run-3 isolation thresholds were tuned to give the lowest rate while introducing only a 2% inefficiency for electrons passing the Level-1 energy threshold. The isolation requirement is not applied for clusters with  $E_T > 50(60)$  GeV in the Run-2 (3) trigger. A threshold of 22 GeV is used for the Run-2 (black) and uncalibrated Run-3 (red) triggers. The improved performance of the Run-3 trigger results in smaller rate and improved efficiency. A layer- and  $\eta$ -dependent calibration is introduced (blue) to compensate for varying detector response. The threshold on the calibrated cluster energy is chosen to produce the same rate as the uncalibrated trigger, resulting in an improved efficiency.

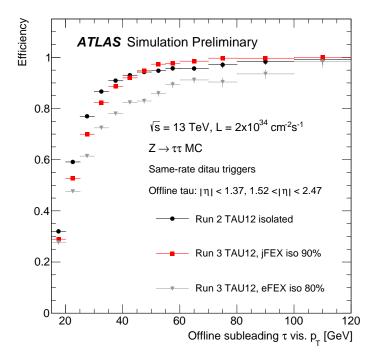

Figure 5.7. Di-tau trigger efficiency comparison between Run-2 and the Run-3 eFEX and jFEX [39].

For tau-based algorithms, Fig. 5.7 shows the comparison of the di-tau trigger efficiency between Run-2 and the Run-3 eFEX and jFEX. The efficiencies are derived from  $Z \to \tau\tau$  Monte Carlo simulation samples, with a 20 (12) GeV threshold on the leading (subleading) tau, with respect to the offline reconstructed tau candidates. The energy threshold corresponds to the primary Run-2 di-tau trigger, without the additional topological selection applied.

The Run-3 isolation thresholds were tuned to produce the same rate as the Run-2 trigger. Run-3 taus are reconstructed in eFEX, and the isolation requirement is computed from surrounding energy as seen in eFEX (grey) or jFEX (red).

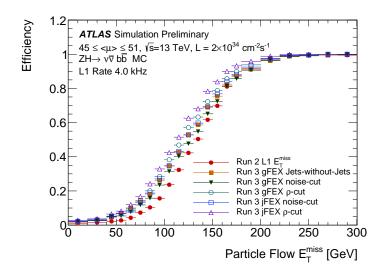

The efficiency of the new missing transverse momentum  $(E_T^{miss})$  algorithms of the Run-3 jFEX and gFEX are presented in Fig. 5.8. A comparison is performed with the Run-2  $E_T^{miss}$  trigger. The results are based on a  $ZH \to \nu\nu$  bb Monte Carlo simulation sample, and the efficiency is computed with respect to the offline  $E_T^{miss}$  with a Tight selection [40]. The thresholds are tuned to give a L1 rate similar to Run-2.

**Figure 5.8.**  $E_T^{miss}$  algorithm efficiency comparison between Run-2 and Run-3 jFEX and gFEX [39].

The noise-cut algorithm computes  $E_T^{miss}$  from the vector sum of all towers with  $E_T$  above an  $\eta$ -dependent threshold. The  $\rho$ -cut algorithm computes  $E_T^{miss}$  from the vector sum of all towers with  $E_T$  above a threshold depending on  $\eta$  and corrected for the local per-event pileup density  $(\rho)$ . The jets without jets algorithm computes  $E_T^{miss}$  based on a linear combination of soft and hard contributions to the  $E_T$  of all towers.

The Run-3 algorithms have steeper turn-on curves at earlier  $E_T^{miss}$  values, which shows better expected performance from the FEX processors compared to the Run-2  $E_T^{miss}$ .

## Chapter 6

# The L1Calo PreProcessor and the TREX

The functionality of the L1Calo PreProcessor (PPr) and its upgrade for Run-3 was covered in Sec. 4.1.2. This chapter describes the hardware of the upgraded PPr system with the addition of the Tile Rear Extension (TREX) modules and the functional aspects that treat the incoming calorimeter signals.

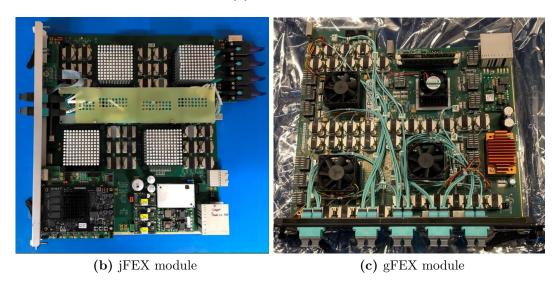

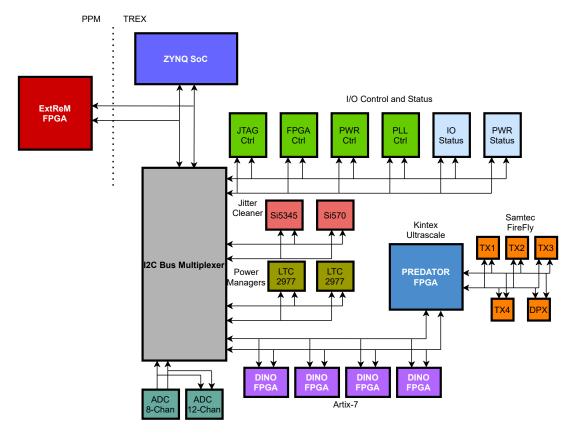

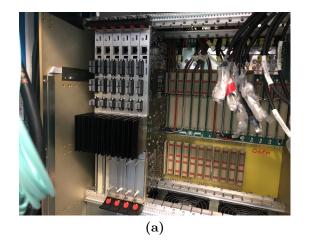

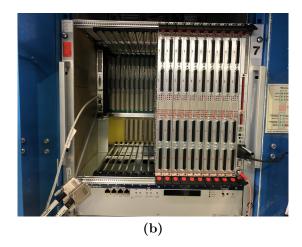

The initial development of the TREX started in 2015 when a conceptual design was proposed to create an interface that would allow the PPr system to provide digital optical data to the Feature Extractor (FEX) processors of the upgrade system, described in Sec. 5.2.1, while maintaining all of the older interfaces with the legacy trigger processors. As a prototype, the first iteration of the hardware was produced in 2017, after which it underwent two more iterations of design changes in 2019 and in 2020 respectively, before being installed in ATLAS.

The work described here started in 2019, at a time when the TREX module was still in its early development phase. The second iteration of the modules was under production and most of the functionality was not complete nor fully tested.

## 6.1 Hardware design, from prototyping to production

The TREX is a VME-compliant 9U rear transition module hosting multiple FPGAs designed specifically for fast data processing and high-speed optical transmission of the calorimeter signals. Although it is highly specialised, the module can be repurposed for other demanding processing and networking tasks, thanks to the onboard high-power FPGA coupled with fast optical transceiver modules. The hardware design revolves around five key criteria that the system must fulfil:

- Fast data formatting

- Optical outputs for the Phase-I trigger and DAQ system

- Compatibility with the existing (legacy) DAQ and Trigger processors

- Low and deterministic latency

- High redundancy and configurability

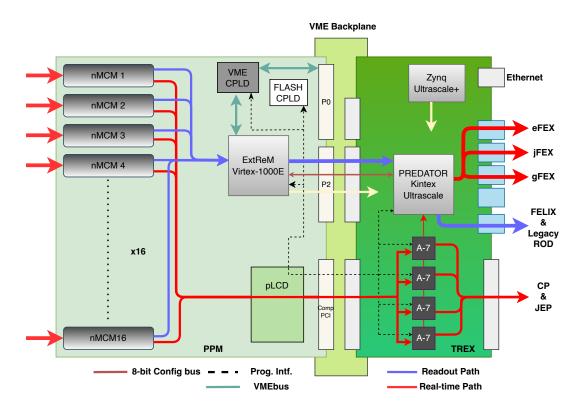

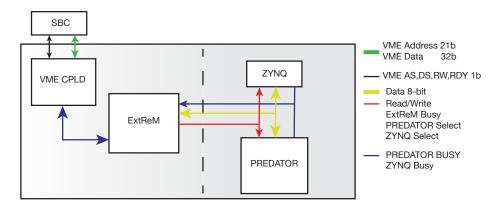

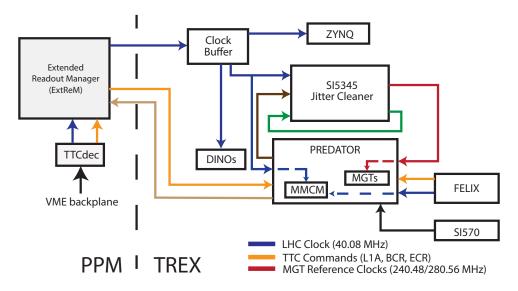

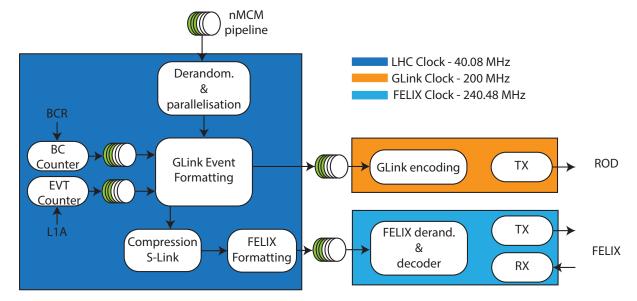

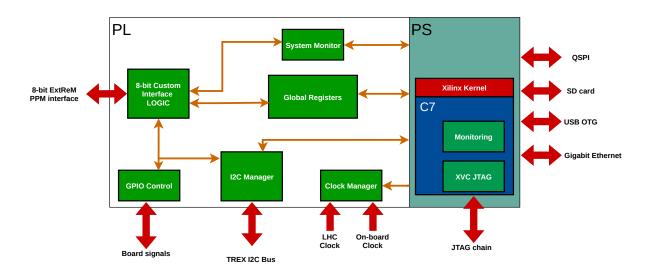

**Figure 6.1.** A diagram illustrating the various data paths of the PPM and TREX.

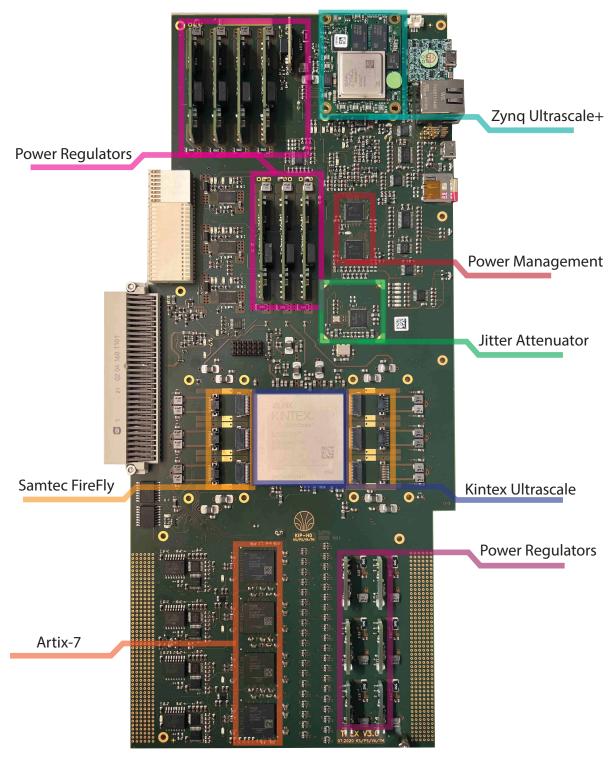

The processing elements are listed below along with their firmware design name:

- 4x Artix-7 FPGAs [41]- Data-IN-Out (DINO)

- 1x Kintex Ultrascale FPGA [42] PREprocessor Data CollectOR (PREDATOR)

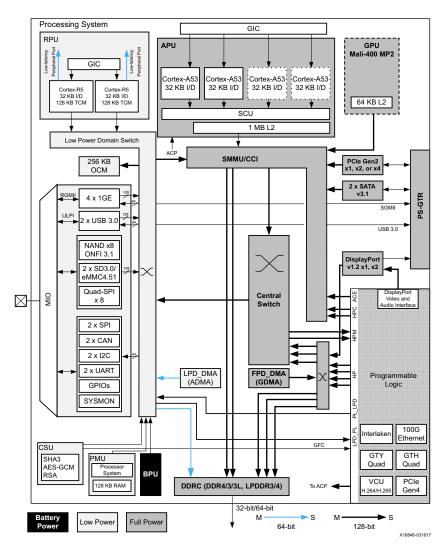

- 1x Zynq Ultrascale+ Multi-Processor System-On-Chip (MPSoC) [43] Global Loader And Monitor (GLAM)

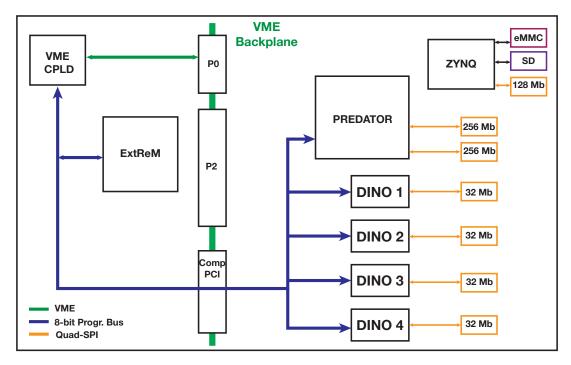

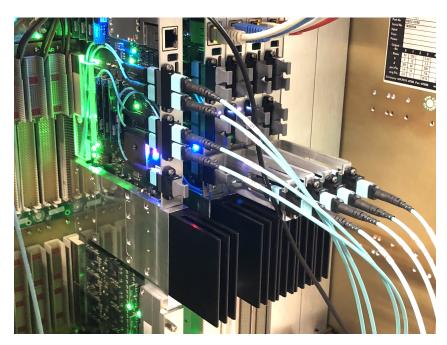

In addition to the FPGAs, the latest production TREX hosts four 12-way optoelectrical Samtec FireFly [44] transmitter modules, one bi-directional 4-way module, and an optional 12-way receiver. Each of the PREDATOR and four DINO FPGAs performs specialised tasks, therefore five individual firmware designs are created and maintained. Integrating the TREX modules into the existing PPr system, however, necessitated also a re-design of the Virtex-1000E (ExtReM) control FPGA firmware on the PreProcessor Modules (PPMs) as well as hardware modifications.

In order to visualise the combined system, a schematic diagram depicting a PPM coupled with a TREX module is shown in Fig. 6.1. The data flow through the system is highlighted in red and blue colours, while the rest of the connections show the configuration paths. The complete L1Calo PPr system for the Tile Calorimeter is composed of 32 PPMs and TREX modules in 2 VME crates.

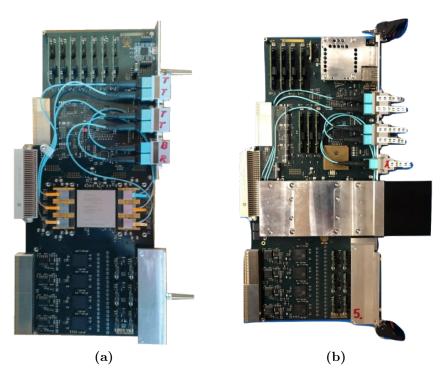

Throughout the development cycle, the TREX design has undergone three iterations of changes. At each step, the hardware has been thoroughly scrutinised.

The first iteration, called the **prototype V1.0**, gave tremendous insight into the high-speed transmission architecture. However, there were design issues in the power distribution and in the routing of the high-speed signals. Whenever large current draws occurred, the DC-DC converters located further away from the FPGA, resulted in large ripples and drops across the core voltage as well as the voltage supplied to the high-speed transceivers. Routing of the high-speed lanes through VIAs created stubs, which acted as antennas and degraded the signal integrity. A fully assembled V1.0 prototype is shown in Fig. 6.2 (left).

The second version, referred to as the **pre-production V2.0**, improved the power delivery to the processing FPGA by moving the DC-DC converters closer to the FPGA and by an increase of the output voltage. The FPGA model was changed to a more power-efficient and package-compatible variant with a lower number of high-speed transceivers, which improved the thermal performance while maintaining the required number of transceivers. The I2C bus and clocking network were also changed for the Artix-7 FP-GAs. The final change came with the introduction of the carrier functionality for the Zynq MPSoC. While the module was functional in most aspects, it suffered from larger capacitive couplings in long traces, in particular, between the ExtReM FPGA and the Zynq which caused unstable behaviour during data transfers.

The pre-production module is depicted in Fig. 6.2 (right) equipped with an improved heatsink.

**Figure 6.2.** The first TREX prototype (a) is depicted with the FPGA and optical transceivers exposed. The pre-production (b) is shown with the latest custom heatsinks.

The third and final design, the **prodction V3.0**, shown in Fig. 6.3, brought a multitude of improvements to the overall stability of the module, most of which were identified during rigorous testing of V2.0. The power logic saw changes as well, by adding a feedback signal from the PPM, any leakage current flow could be controlled when the module is powered off.

The clock tree was improved with better distribution to the processing FPGA and the Zynq. Further changes were made in the Zynq and the programming interface. The final iteration fixed all issues that could've caused instabilities during the operation period in ATLAS.

The large-scale production of 40 TREX modules posed challenges as, during the acceptance tests, the majority of the assembled boards had a short circuit inside the second Artix-7 FPGA. The issue was identified through thermal imaging and showed a short-to-ground for the 2.5 V bank. It is suspected to have been caused due to thermo-mechanical stress asserted during the assembly process. A reworking campaign was started, where all the affected FPGAs were manually extracted and replaced. It was a major undertaking with a high yield rate.

**Figure 6.3.** A partially assembled production (V3) TREX without a heatsink and CompactPCI connectors and FireFly transceivers. It is used to showcase the various components of the TREX.

Powering the TREX modules is done through the VME crate power supply and is directly coupled to the PPM power circuitry. 5.0 V and 3.3 V are used as input voltages to derive all necessary bus and FPGA voltages. A configurable load-balancing mechanism is implemented, which allows for regulation of the current draw between the voltage sources. Two power management units supervise and control the DC-DC converters and issue a power sequencing routine during power on and off.

## 6.2 Adapting the PPMs for TREX compatibility

The PreProcessor module underwent both hardware and firmware adjustments to achieve compatibility with the TREX module.

#### **Hardware Changes**

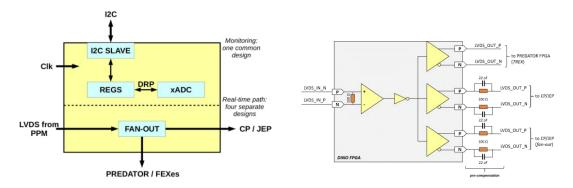

The first hardware change is the replacement of the LVDS Cable Driver (LCD) mezzanine card with a passive bridge (pLCD). The LCD card houses four Virtex-II FPGAs and a pre-emphasis circuit that drives the incoming LVDS streams from the nMCMs to the CP and JEP processors. The LCD functionality is moved over to the TREX, where the four Artix-7 FPGAs perform the required additional data duplication for the FEX processors. The pLCD bridge remaps the LVDS signals to the new FPGAs through the Compact PCI connector on the PPM. It also enables the TREX to use the programming interface and multiple control signals from the VME CPLD¹ located on the PPM. Further details on the programming interface are described in Sec. 6.3.4

The next set of changes include the removal of resistors along the differential signals, which would limit the bandwidth on the LVDS streams. This is done to achieve higher transfer speeds in the future if needed. Furthermore, the production series of the TREX modules require a static signal from the PPM power manager circuit, which is fed through an external wire to one of the P2 connector pins. The signal indicates the power state of the PPM. The corresponding power logic of the TREX board uses the indicator to control any leakage currents flowing into the board when the main PPM rail is powered off. All 32 modules in the TileCal crate have been modified with these changes.

#### CPLD changes

With the introduction of the pLCD card, the programming and configuration signals that were used for the Virtex-II FPGAs are repurposed and routed to the TREX. The VME CPLD firmware is modified to show the configuration status of the TREX FPGAs and to control the programming interface.

<sup>&</sup>lt;sup>1</sup>Complex Programmable Logic Device

An additional change is performed for the V3.0 TREX modules, where the programming interface is changed from a uni-directional, write-only bus to a bi-directional interface. The change gives direct read and write access to the TREX flash memory modules via the VMEbus. The procedure is described in Sec. 6.3.4.

#### The ExtReM FPGA

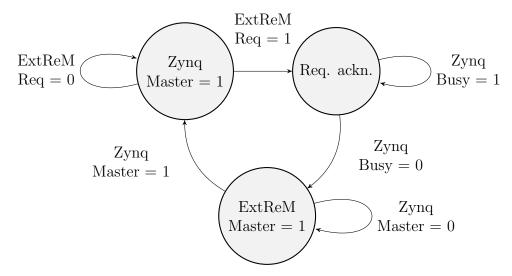

In Run-1 and 2, the Readout Manager FPGA [45], located on the PPM was responsible for the control of the nMCMs, rate metering and histogramming. In addition, it was also performing the collection and processing of event data to be read-out to the ATLAS DAQ system. With the addition of the TREX to the PreProcessor system, the functionality of the FPGA is modified for managing the TREX, hence aptly named the Extended Readout Manager(ExtReM). It is acting as a communications hub between the Single-Board Computer (SBC) and the TREX. The VME commands issued by the SBC are received and decoded on the ExtReM FPGA. Based on the destination address, the data is passed to TREX. The response from the destination module is also processed and sent back to the SBC.

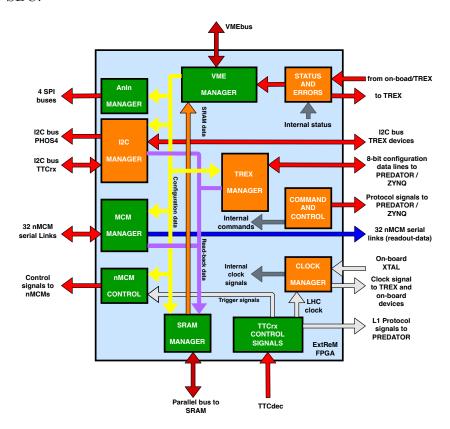

**Figure 6.4.** A schematic overview of the ExtReM firmware. The orange-coloured logic blocks illustrate the new or modified functionality for the TREX.

The ExtReM logic blocks are depicted in Fig. 6.4. Multiple new management logic circuits are added to the design, the internal clock distribution is also modified to provide

the TREX module with the 40.08 MHz LHC clock. The status and error handling segments have new registers for the new module. The removal of the readout processing block freed-up resources for implementing the functionality required for the TREX.

## 6.3 Control, configuration of the TREX and the interface with the PreProcessor

#### 6.3.1 Communication between the PPM and TREX

There are three methods for interacting with the TREX via VME, each interface serves a specific purpose:

- Custom 8-bit protocol. A custom FPGA to FPGA protocol that connects the processing (PREDATOR) FPGA and the Zynq to the PPM. It is used for loading and retrieving configuration parameters required for initialising the devices and preparing them for data-taking operations.

- Inter-Integrated Circuit (I2C) bus A synchronous, serial communication bus dedicated to accessing onboard programmable devices. Hardware control and collection of monitoring information are performed via the I2C protocol.

- 8-bit Programming interface The programming interface is a multipurpose 8-bit wide data bus, dedicated to programming the FPGAs and their flash memory modules. Multiple transfer protocols are initiated over the bus, such as QSPI for the flash memories and SelectMAP [46] for the FPGAs.

The interfaces are described in more detail in Sec. 6.3.2.

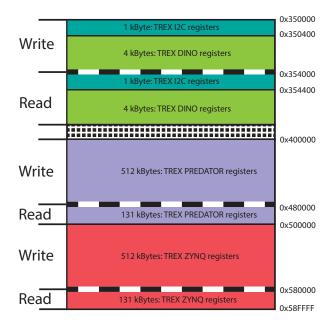

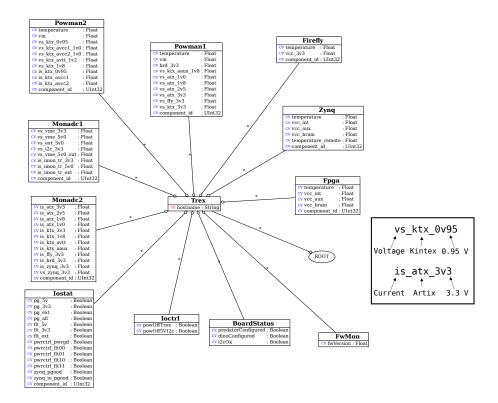

#### Register map of the TREX

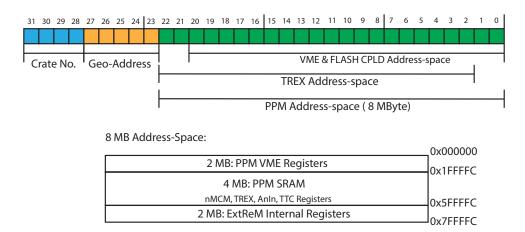

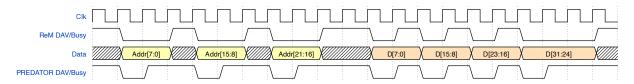

Before the data transfer protocols can be initiated, a dedicated TREX register map is required within the VME address space. The register model implemented for the PreProcessor uses a 32-bit addressing mode with 32-bits data (A32/D32). For every PPM, 8 MBytes of memory is allocated, which is divided into three sub-spaces. This is shown in Fig. 6.5.

**Figure 6.5.** The VME address-space of the PPM and TREX.

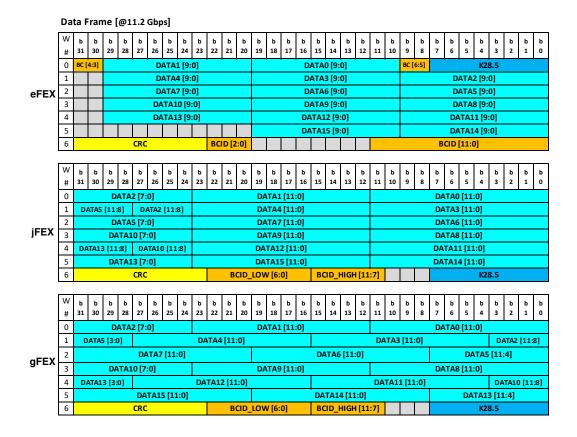

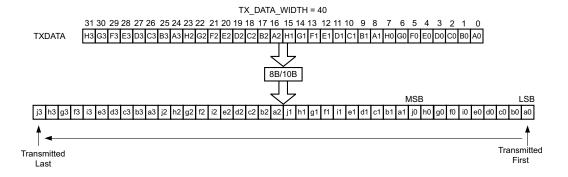

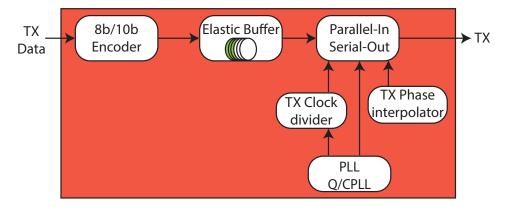

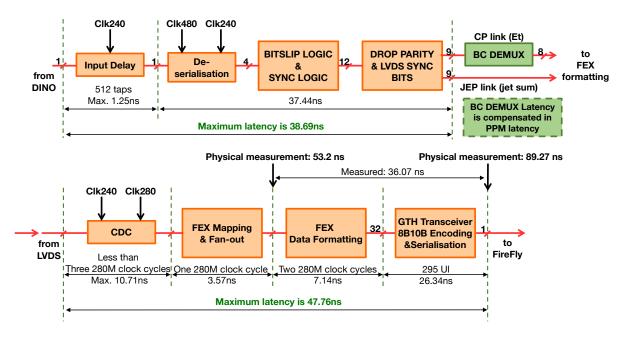

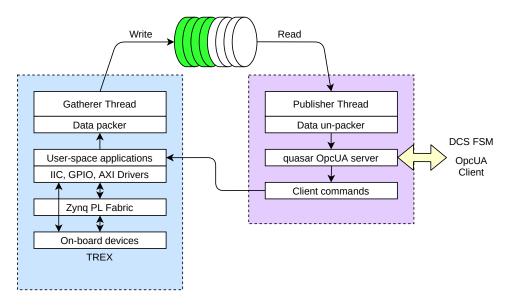

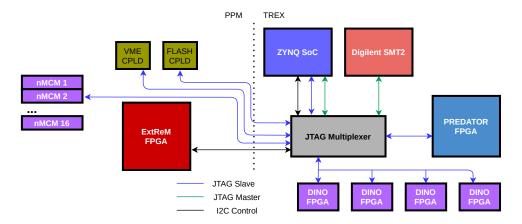

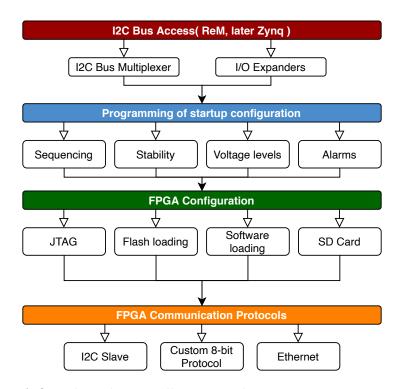

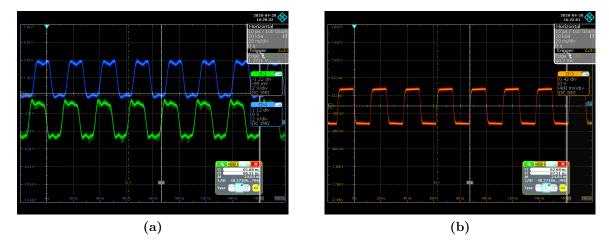

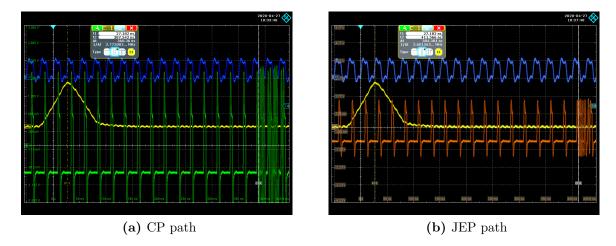

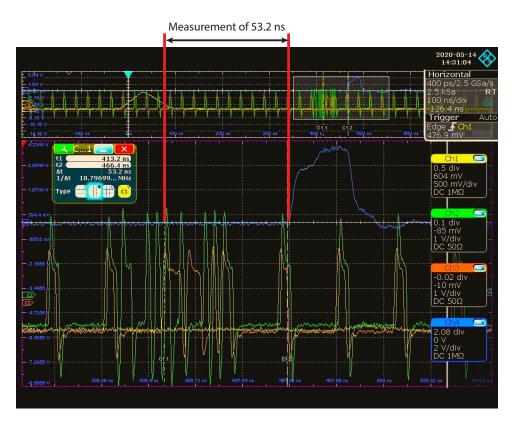

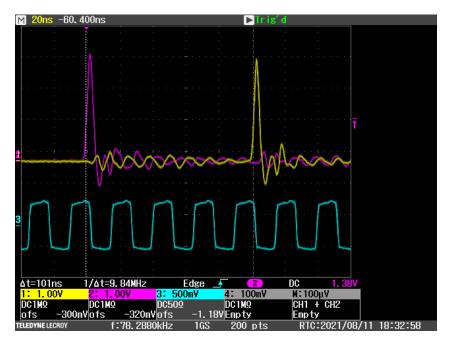

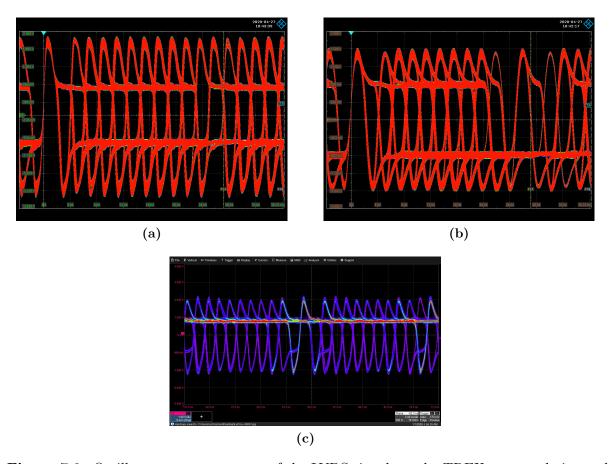

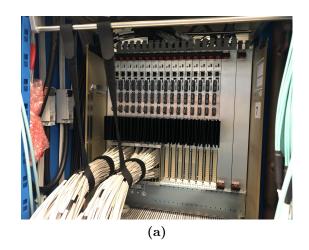

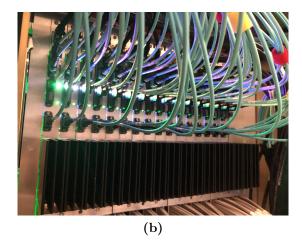

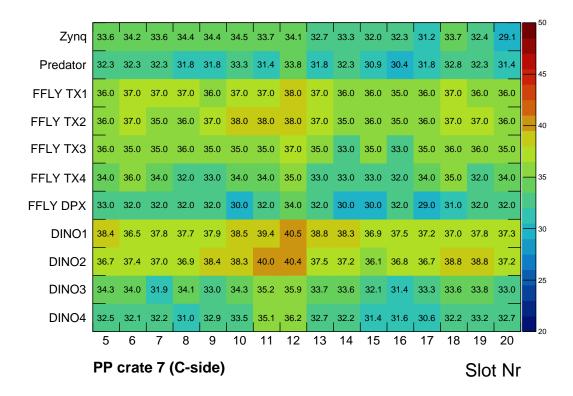

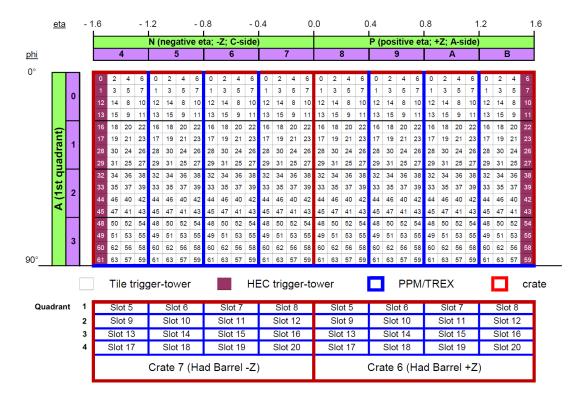

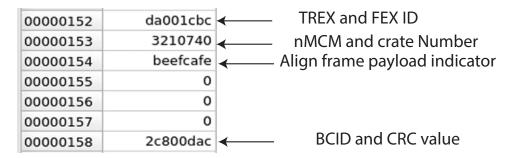

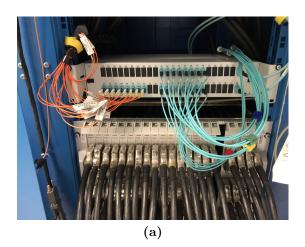

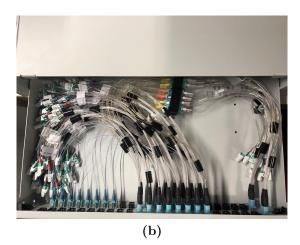

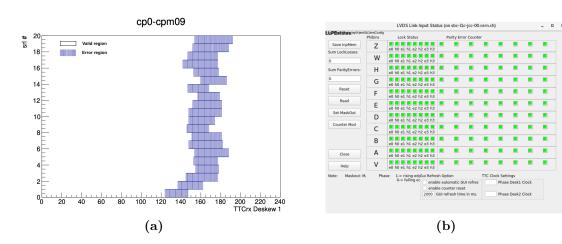

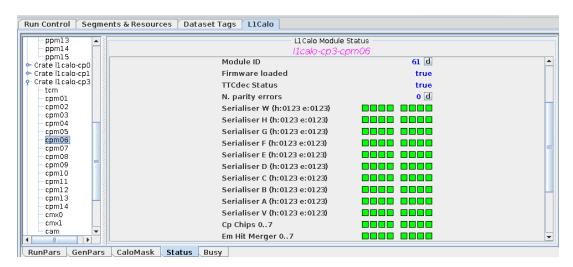

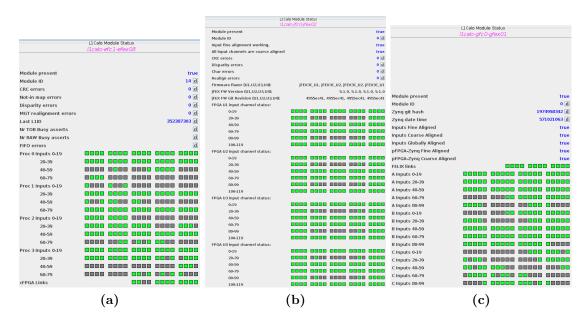

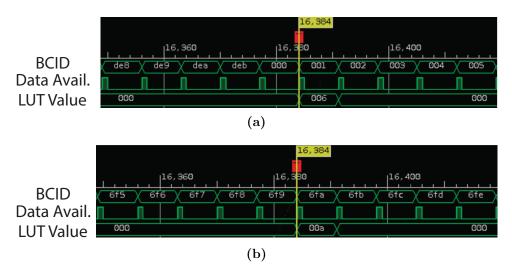

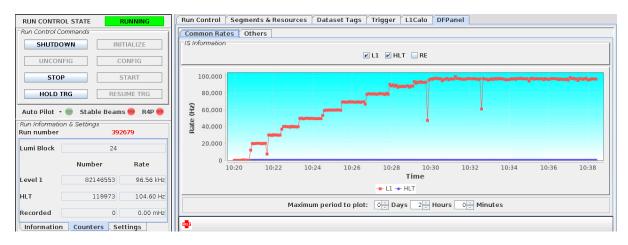

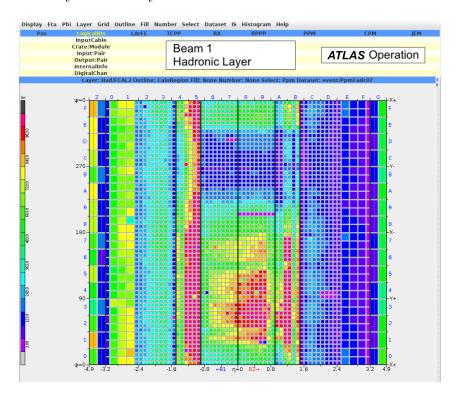

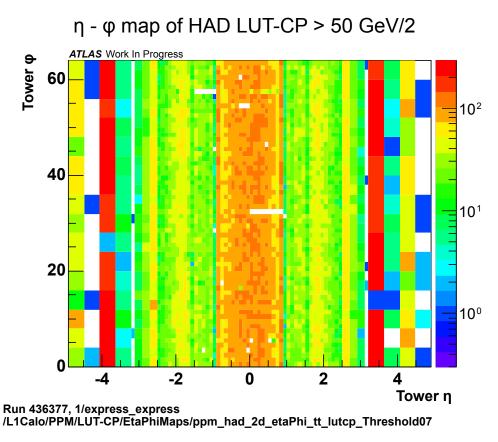

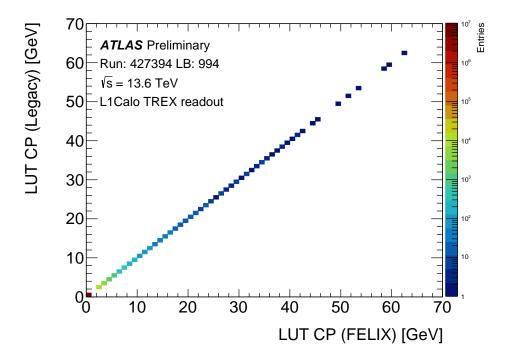

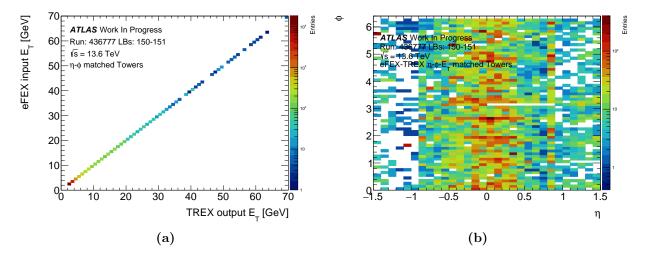

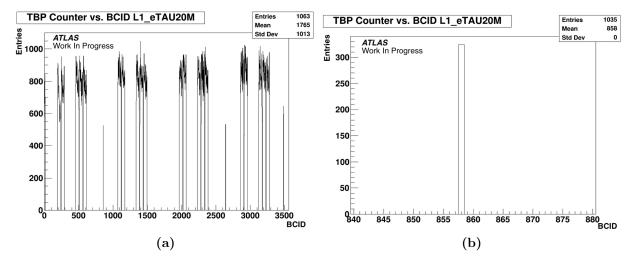

The first 2 MB are dedicated to the control and status registers of the PPM CPLDs. The next 4 MBs are allocated for mapping an entire on-board static RAM (SRAM) module to extend the ExtReM memory capabilities and access the registers of on-board devices such as the TTCdec mezzanine, the An-Ins and the nMCMs. In Run-2, it was used to carry out large block transfers between the ExtReM and the nMCMs while also providing storage space for read-back purposes of other peripherals. The remaining 2MB are designated for internal registers within the ExtReM FPGA.