## RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Jan Jongmanns

The Upgrade of the PreProcessor of the ATLAS Level-1 Calorimeter Trigger for LHC Run-2

Dissertation

HD-KIP 17-65

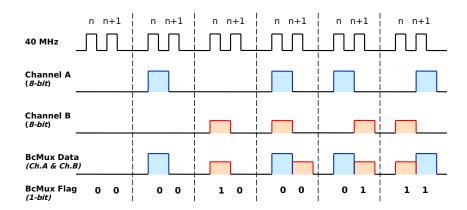

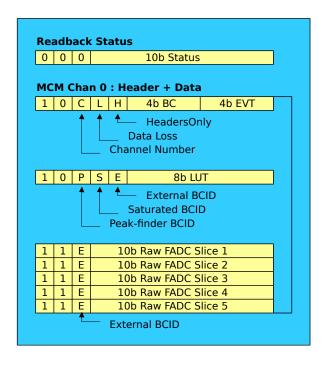

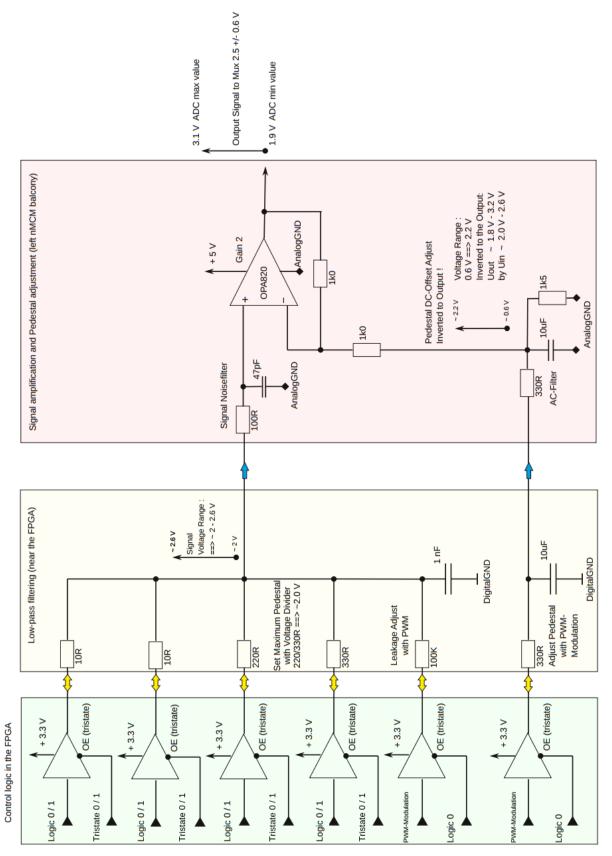

# Dissertation submitted to the

# Combined Faculties of the Natural Sciences and Mathematics of the Ruperto-Carola-University of Heidelberg, Germany for the degree of

Doctor of Natural Sciences

Put forward by Jan Jongmanns born in Nettetal

Oral examination on July 27, 2017

# The Upgrade of the PreProcessor of the ATLAS Level-1 Calorimeter Trigger for LHC Run-2

Referees: Prof. Dr. Hans-Christian Schultz-Coulon

Prof. Dr. Norbert Herrmann

#### Zusammenfassung:

Die erste Stufe des Kalorimeter-Triggers des ATLAS Experiments am CERN untersucht innerhalb von  $\sim 2$  µs 7200 analoge Kalorimeter-Signale, um Objekte mit hoher transversaler Energie zu identifizieren und Energiesummen zu erstellen. Er besteht aus dem PreProcessor, welcher die Kalorimeter-Signale digitalisiert, sie der korrekten Strahlkreuzung des LHC zuordnet und sie bezüglich der transversalen Energie kalibriert, sowie zwei Prozessoren, welche zu jeder Strahlkreuzung die Ergebnisse des PreProcessors analysieren um Elektronen, Photonen,  $\tau$ -Teilchen und Jets zu identifizieren und um die fehlende sowie die gesamte Transversale Energie zu berechnen. Um die für Run-2 erwareten höheren Raten und den erhöhten Pile-Up zu verarbeiten, wurden die ASIC-basierten Multichip Module, welche die Signalverarbeitungsalgorithmen implementieren, im Rahmen des ersten langen Shutdown des LHC durch verbesserte, FPGA-basierte Module ersetzt. Die Signalverarbeitung des neuen Multichip Moduls basiert auf der Run-1 Implementierung und erweitert diese durch verbesserte Rauschfilter, unabhängige Energiekalibrationen für elektromagnetische und hadronische Objekte, Verbesserungen bei der Prozessierung saturierter Signale und eine für jede Strahlkreuzung berechnete Pile-Up Korrektur. In dieser Arbeit wird das neue Multichip Modul beschrieben, mit einem Fokus auf die Verbesserungen der Signalverarbeitungsalgorithmen und der daraus resultierenden verbesserten Performance des Level-1 Kalorimeter-Triggers in Run-2.

#### Abstract:

The Level-1 Calorimeter Trigger of the ATLAS experiment at CERN analyses 7200 analogue signals from the calorimeters within  $\sim 2~\mu s$  to identify objects with high transverse energy and to determine energy sums. It consists of a Pre-Processor, which digitises the signals, assigns them to the correct LHC bunch crossing and calibrates them to transverse energy, and two object finding processors. During the first long shutdown of the LHC, the main processing unit of the PreProcessor, the ASIC-based Multichip Module, was replaced by an improved FPGA-based version to adapt to the increased rates and pile-up that are expected for Run-2. The new Multichip Module builds upon the Run-1 signal processing implementation and expands it with enhanced noise filtering techniques, independent energy calibration for electromagnetic and hadronic objects, improved processing of saturated signals and bunch-crossing-wise pile-up subtraction. This thesis describes the new Multichip Module, focussing on the improvements to the signal processing algorithms and the increased performance gained by their implementation.

## Contents

| 1 | Intro      | oduction                                     | 11 |

|---|------------|----------------------------------------------|----|

| 2 | The        | Standard Model of Particle Physics           | 14 |

|   | 2.1        | Standard Model of Particle Physics           | 15 |

|   | 2.2        | Beyond the Standard Model                    |    |

|   |            |                                              |    |

| 3 |            | ATLAS Experiment at Large Hadron Collider    | 18 |

|   | 3.1        | The Large Hadron Collider                    |    |

|   |            | 3.1.1 LHC Machine                            |    |

|   |            | 3.1.2 Proton Beam Structure                  |    |

|   |            | 3.1.3 Aspects of Proton-Proton Collisions    |    |

|   | 3.2        | ATLAS Detector                               |    |

|   |            | 3.2.1 Coordinate System                      | 23 |

|   |            | 3.2.2 Inner Detector                         | 24 |

|   |            | 3.2.3 Calorimetry                            | 25 |

|   |            | 3.2.4 Muon Spectrometer                      | 30 |

|   |            | 3.2.5 Magnets                                | 31 |

|   |            | 3.2.6 Further Subdetectors                   | 32 |

|   | 3.3        | ATLAS Detector Control System                | 33 |

|   | 3.4        | ATLAS Trigger and Data Aquisition System     | 33 |

|   |            | 3.4.1 Level-1 Trigger                        | 35 |

|   |            | 3.4.2 High Level Trigger and Data Aquisition | 37 |

|   |            | 3.4.3 TDAQ Upgrade in LS1                    | 37 |

|   | 3.5        | ATLAS Operation                              | 38 |

|   | <b>-</b> . | ATLACE II CI I TI                            | 20 |

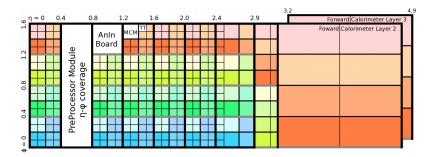

| 4 |            | ATLAS Level-1 Calorimeter Trigger            | 39 |

|   | 4.1        | Functional Overview                          |    |

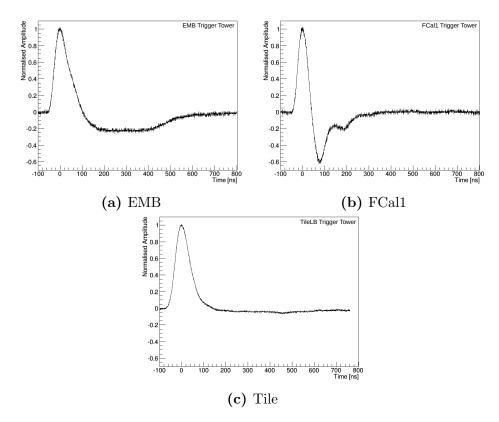

|   | 4.2        | Analogue Input Signals                       |    |

|   |            | 4.2.1 Input Signal Path                      |    |

|   |            | 4.2.2 Signal Shape                           |    |

|   | 4.3        | PreProcessor                                 | 44 |

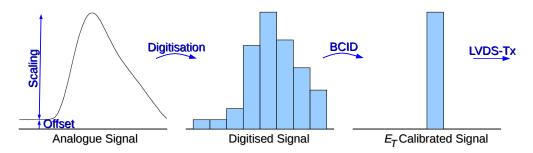

|   |            | 4.3.1 Functionality                          | 44 |

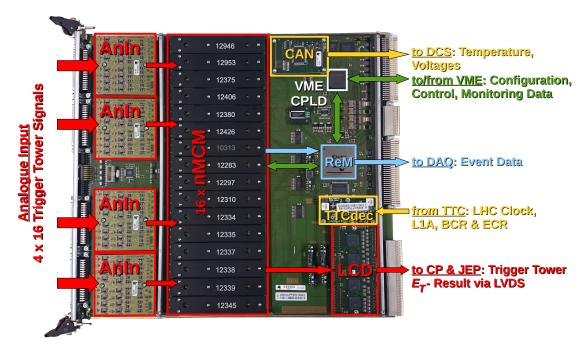

|   |            | 4.3.2 Hardware Implementation                |    |

|   | 4.4        | Cluster Processor                            |    |

|   |            | 4.4.1 Functionality                          | 52 |

|   |            | 4.4.2 Hardware Implementation                | 53 |

|   | 4.5 | Jet-Eı  | nergy Processor                                |  | <br> | . 54  |

|---|-----|---------|------------------------------------------------|--|------|-------|

|   |     | 4.5.1   | Functionality                                  |  |      |       |

|   |     | 4.5.2   | Hardware Implementation                        |  | <br> | . 55  |

| 5 | The | new N   | Multichip Module                               |  |      | 56    |

|   | 5.1 | Hardy   | vare Implementation                            |  | <br> | . 57  |

|   | 5.2 | Digita  | d Signal Processing                            |  | <br> | . 59  |

|   |     | 5.2.1   | ADC Input                                      |  | <br> | . 60  |

|   |     | 5.2.2   | Input Timing                                   |  | <br> | . 62  |

|   |     | 5.2.3   | Bunch-Crossing Identification Logic            |  | <br> | . 64  |

|   |     | 5.2.4   | LVDS Transmission                              |  | <br> | . 69  |

|   |     | 5.2.5   | Event Data Readout                             |  | <br> | . 70  |

|   |     | 5.2.6   | Monitoring                                     |  | <br> | . 72  |

|   |     | 5.2.7   | Testing Facilities                             |  | <br> | . 73  |

|   |     | 5.2.8   | Clock Management                               |  | <br> | . 74  |

|   |     | 5.2.9   | Configuration                                  |  | <br> | . 76  |

| 6 | Fun | ctional | Tests of the new Multichip Modules             |  |      | 79    |

|   | 6.1 |         | Overview                                       |  | <br> | . 79  |

|   | 6.2 | Funct   | ionality Tests                                 |  | <br> | . 80  |

|   |     | 6.2.1   | Test Setups                                    |  | <br> | . 81  |

|   |     | 6.2.2   | Configuration Test                             |  |      |       |

|   |     | 6.2.3   | Rate-Metering Test                             |  | <br> | . 85  |

|   |     | 6.2.4   | LVDS Transmission Tests                        |  | <br> | . 86  |

|   |     | 6.2.5   | Event Readout Test                             |  | <br> | . 87  |

|   |     | 6.2.6   | Analogue Input Tests                           |  | <br> | . 89  |

|   |     | 6.2.7   | Input Timing Tests                             |  | <br> | . 95  |

|   |     | 6.2.8   | Histogramming Test                             |  | <br> | . 101 |

|   | 6.3 | Summ    | nary of Test Results                           |  | <br> | . 101 |

|   | 6.4 |         | lation of nMCMs at CERN                        |  |      |       |

| 7 | lmp | roved   | Bunch-Crossing Identification on the nMCM      |  |      | 103   |

|   | 7.1 |         | d Filter Extension                             |  | <br> |       |

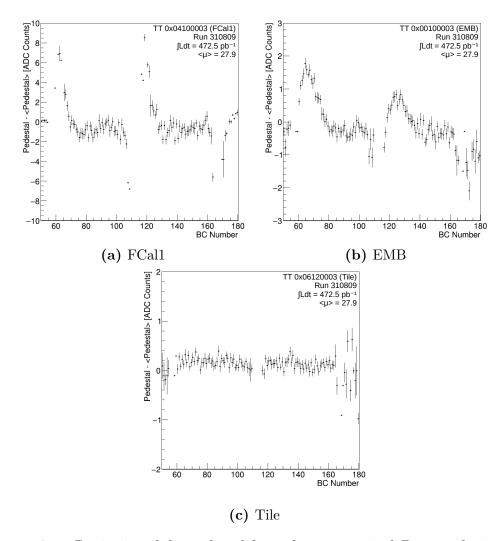

|   | 7.2 | _       | mic Pedestal Correction                        |  |      |       |

|   |     | 7.2.1   | Pile-Up Effects on L1Calo Input Signals        |  |      |       |

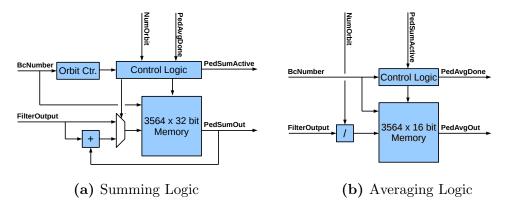

|   |     | 7.2.2   | Pedestal Correction Algorithm                  |  |      |       |

|   |     | 7.2.3   | Pedestal Correction Algorithm Implementation . |  |      |       |

|   |     | 7.2.4   | Synchronisation of the Pedestal Correction     |  |      |       |

|   |     | 7.2.5   | Readback of Pedestal Average Memory            |  |      |       |

|   | 7.3 |         | ate LUTs for CP and JEP Systems                |  |      |       |

|   | 7.4 |         | wed BCID of Saturated Signals                  |  |      |       |

|   |     | 7.4.1   | Updated BCID Decision Logic                    |  |      |       |

|   |     |         | 80 MHz Saturated BCID Algorithm                |  |      |       |

| 8  | Addi  | tional Monitoring and Testing Facilities on the nMCM | 119 |

|----|-------|------------------------------------------------------|-----|

|    | 8.1   | Monitoring Algorithms                                | 119 |

|    | 8.2   | Event Data Readout                                   | 119 |

|    |       | 8.2.1 Additional Readout on the nMCM                 | 120 |

|    |       | 8.2.2 Readout of 80 MHz ADC Data                     | 121 |

|    | 8.3   | Updates to Playback                                  | 122 |

|    |       | 8.3.1 Playback of ADC Data at 80 MHz                 |     |

|    |       | 8.3.2 Separation of Histogramming and Playback       | 123 |

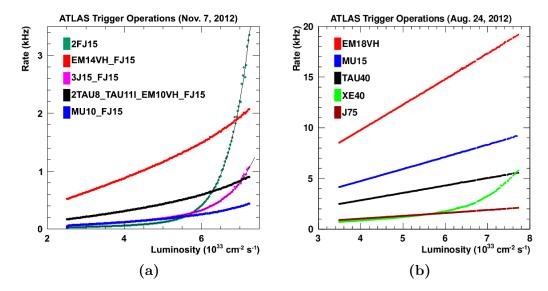

| 9  | Perf  | ormance of the nMCM                                  | 124 |

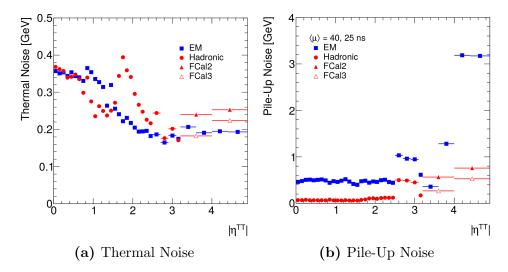

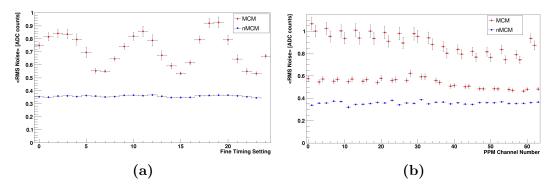

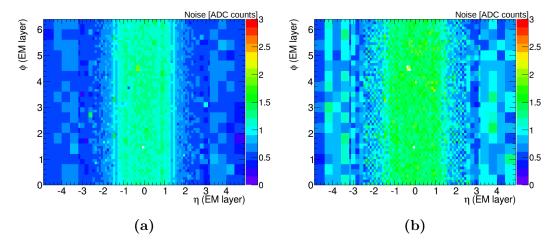

|    | 9.1   | Input Noise                                          | 124 |

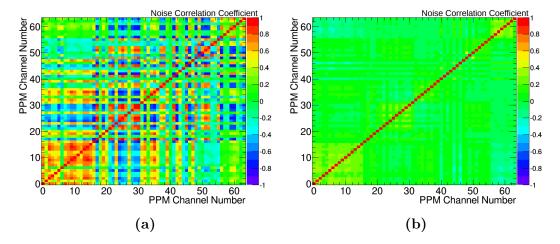

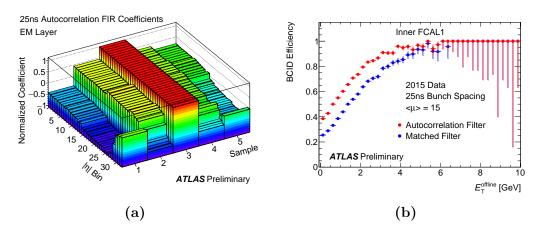

|    | 9.2   | Autocorrelation Filters                              | 127 |

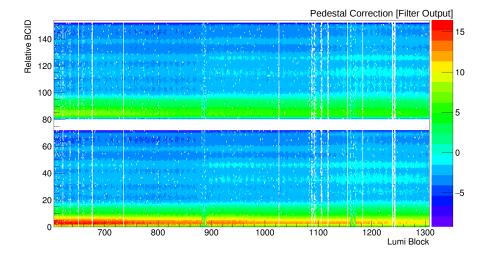

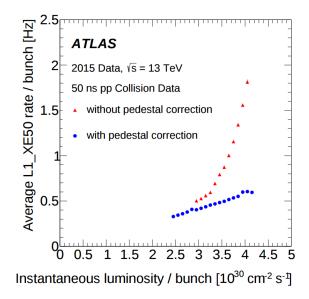

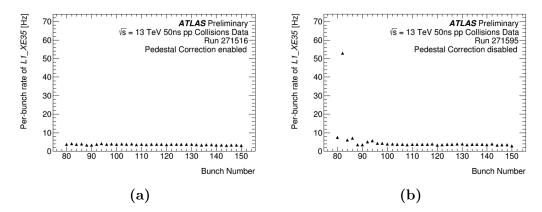

|    | 9.3   | Pedestal Correction                                  | 128 |

|    | 9.4   | Separate Energy Calibration for CP and JEP           | 130 |

|    | 9.5   | BCID of Saturated Signals                            | 130 |

| 10 | Sum   | mary                                                 | 133 |

| Α  | Lists |                                                      | 134 |

|    | A.1   | List of Figures                                      | 134 |

|    |       | List of Tables                                       |     |

| В  | Bibli | ography                                              | 137 |

## 1 Introduction

Particle physics concerns itself with the understanding of nature at the most fundamental level. By analysing the most fundamental and indivisible constituents of matter and their interactions, understanding of the behaviour of physical systems at larger scales can be gained.

To probe the small distance scales of particle physics, high energy scales have to be reached. To do so, modern experiments utilise strong particle accelerators, which use electromagnetic fields to accelerate particles and to subsequently collide them. The prime example for this is the Large Hadron Collider located at the CERN laboratory in Geneva, Switzerland. It is a synchrotron using high frequency cavities to accelerate two beams of protons to energies of up to 13 TeV per particle, with superconducting magnets bending the beams onto a circular path.

The high energy protons are collided in four interaction points along the ring, causing interactions which can produce a plethora of possible final state particles. By measuring these particles and their properties, insights into the processes involved in the high-energy collision is gained. To this end, each of the collision points is equipped with a large particle detector, which detects the particles that are produced in the collision.

One of these is the ATLAS experiment, a general purpose detector that is designed to measure all particles produced in the collisions as inclusively as possible. An integral part of the experiment is the trigger system. Its purpose is to select those events which should be stored for later data analysis, reducing the input rate of 40 MHz to 1 kHz. Within this system the Level-1 Calorimeter Trigger has the task to analyse data from the ATLAS calorimeters to find candidates of highly energetic jets, taus, electrons and photons as well as the missing and total transverse energy. It is organized into several processing stages, with a dedicated PreProcessor finding large energy depositions and calibrating them and two downstream object finding processors which execute sliding window algorithms to identify particle candidates.

The Level-1 Calorimeter Trigger system has been upgraded during the first long shutdown of LHC in 2013 and 2014, both by replacing hardware components and by upgrading the signal processing implementation. On the PreProcessor side this upgrade consists of the replacement of the central processing platform, the Multichip Module, by a new version based on modern and flexible components. Most prominently the ASIC performing the main signal processing has been replaced by an FPGA, offering enough resources to implement the original ASIC algorithms as well as new advanced features.

Within this thesis the upgraded, new Multichip Module is described, with a focus on the signal processing implementation and production tests. The second chapter of this document gives an overview of the Standard Model of Particle Physics. In the third chapter both the LHC and ATLAS machines are described, while chapter four focuses on the Level-1 Calorimeter Trigger system. The fifth chapter describes the hardware implementation of the new Multichip modules and the initial version of the signal processing algorithms. Chapter six describes the production test procedure used to verify the functionality of the new hardware. Chapters seven and eight provide detailed descriptions of the updates of the signal processing algorithms. The performance of the upgraded system during the first two years of operation is described in chapter nine. Finally, chapter ten forms a conclusion and overall summary of the presented material.

### **Author's Contributions**

The development of a system like the one presented in this thesis requires expertise in hardware, firmware and software development, as well as an understanding of the physical processes involved in the production, decay and detection of physics signatures. As such, most of the topics presented here are results of a collaborative effort within a larger group. Nevertheless there are specific parts which the author explicitly contributed to the overall effort.

The author contributed significantly to the planning, design and implementation of the new trigger algorithms included in the new Multichip Module. By improving the digital filter, the author made it possible to use more efficient noise filtering schemes that assure a high efficiency for low energy signals. The author separated the energy calibration for the electromagnetic and hadronic objects, increasing the flexibility for the respective calibration procedures. The author was central to the development of the pedestal correction algorithm at all stages, from the first conceptual design to the details of the final implementation. Furthermore the author implemented the new 80 MHz based bunch-crossing identification logic for saturated calorimeter signals. To further improve the processing of signals in the saturated regime, the author developed and applied the updates of the BCID decision logic.

The author also provided several improvements of the monitoring and testing algorithms on the new Multichip Module. The separation of the energy calibration requires additional monitoring procedures to observe the respective results independently, which the author implemented. To validate the additional functionality in the saturated regime, the author developed and implemented a readout technique for 80 MHz ADC samples. For the same reason, the playback functionality was expanded by the author so that it can be executed at the higher frequency of 80 MHz.

The author also contributed to the production tests of the new Multichip Modules. The author developed several of the software tools described in this thesis, specifically the tests of the monitoring algorithms and the Signal Generator scan and the tests of the input stage of the CALIPPR FPGA. The author also adapted a standalone version of the L1Calo online simulation software to the test environment, improving the flexibility for the input patterns that are used in the test procedure.

The author performed a substantial part of the production tests himself, including both the execution of the tests and the upload of the results to an online database. The author was also involved in one of the installation campaigns at CERN, where part of the system was equipped with the new modules.

Though it is not described in this thesis, the author also implemented the neccessary changes in the ReM FPGA to enable the features of the new Multichip Module described above. The author also provided advice and technical support to the various studies and analyses of the PreProcessor performance. Last but not least the author was involved in the daily operations of the PreProcessor system for most of the time of the thesis, most strongly during a one year stay at CERN.

## 2 The Standard Model of Particle Physics

Particle physics aims to describe nature by analysing the most fundamental constituents of matter and their interactions with each other.

While the idea that matter consists of indivisible particles at the smallest scale had already been proposed by philosophers in ancient cultures like Greece, it took until the early 19th century for a quantifyable theory to emerge. Between 1805 and 1808, the chemist John Dalton, noticing how chemical elements form compounds only in certain ratios, proposed that all elements are made up of indivisible particles calles atoms, with different elements consisting of different kinds of atoms [1]. With the discovery of the electron by Thomson in 1897 [2] and experiments by Rutherford and Royds [3, 4] in the first decade of the 20th century, the structure of atoms as a small, positively charged massive nucleus surrounded by negatively charged electrons was established. Insight into the structure of the nucleus was gained through the investigations of isotopes. Proven through experiments by Soddy [5, 6], Aston [7, 8] and Thomson [9, 10], their existance lead to the model of a nucleus formed of positively charged protons and neutral neutrons. The development of the atomic theory culminated in the proofs for nuclear fission by Hahn [11] and Meitner [12] and nuclear fusion by Oliphant [13] and Bethe [14].

In the second half of the 20th century, the development of particle accelerators and the observation of cosmic rays led to the discovery of many new particles beyond the ones that make up our everyday world (e.g. [15, 16, 17, 18]). With dozens of mesons and baryons discovered in the 1950s, the term 'particle zoo' was brought up to describe the large number of different, apparently fundamental particles. In 1961, Gell-Mann managed to bring order to the zoo, by ordering the particles into octets and decuplets according to their charge and the newly introduced 'strangeness' quantum number [19]. Noticing this symmetry ultimately led to the introduction of the quark model, which describes mesons and baryons as composite particles, with their constituents, the quarks, being truly elementary, indivisible particles [20, 21, 22].

This process of understanding the large number of observed particles as a consequence of the underlying, simpler structure is mirrored by the unification process of the forces that govern the interactions of particles. In 1873, Maxwell published a treatise in which he formulated the electric and magnetic phenomena as consequences of a single electromagnetic force. Glashow [23], Salam [24] and Weinberg [25] managed to unify the electromagnetic force and the weak force, that governs radioactive decay, in a consistent way in the late 1960s. This model has been combined with the theory of Quantum Chromodynamics that describes the strong interactions between quarks to arrive at what is known as the Standard Model of Particle Physics in the following years. Since then, the Standard Model has been successful in accu-

rately predicting the outcome of the majority of particle physics experiments. The most prominent example of the recent past is the discovery of the Higgs Boson at the Large Hadron Collider in 2012 [26, 27]. Nevertheless, some unanswered questions remain that are not solved in the Standard Model, making the search for 'new physics' one of the main drivers for many particle physics experiments.

This chapter gives a brief overview of the Standard Model in section 2.1, and discusses some of the remaining open questions not answered by the Standard Model in Section 2.2.

## 2.1 Standard Model of Particle Physics

The Standard Model of Particle Physics is a relativistic quantum field theory that describes the elementary particles and their interactions. In a quantum field theory, both matter and interactions are modeled by fields, whose quantised excitations are interpreted as particles. For example, all electrons in the universe are excitations of a single electron field, and the photons are similarly represented by the electromagnetic field. The interaction between particles in this picture is realised by the exchange of intermediate particles, explaining e.g. the electromagnetic interaction as an exchange of photons between charged particles.

On a more fundamental level, interactions are described using gauge symmetries. Given that a theory is symmetric under a global transformation<sup>1</sup> of the matter fields, the principle of locality suggests that the fields should be symmetric under local transformations<sup>2</sup> as well. This invariance under local transformations, also called gauge symmetry, can be achieved by introducing additional gauge fields in the theory, whose transformations cancel the effects of the transformations of the matter fields. The resulting theory is invariant under gauge transformations and the gauge fields realise interactions between the matter particles.

A key difference between matter particles and interaction particles is their statistical behaviour. Matter particles are *fermions*, i.e. they obey Fermi-Dirac statistics and no two of them can occupy the same state. Interaction particles are *bosons*, i.e. they obey Bose-Einstein statistics and an arbitrary number of them can occupy the same state. Following the spin-statistics-theorem (REF!!!), all fermions have half-integer spin  $(\frac{1}{2}, \frac{3}{2}, ...)$  while bosons have integer spin (0, 1, ...). The bosons corresponding to a gauge field are called *gauge bosons*.

The SM is built from three such gauge theories:

1. Quantum Electrodynamics is a gauge theory using the U(1) symmetry group. It describes the interaction of charged particles via exchange of photons,  $\gamma$ .

<sup>&</sup>lt;sup>1</sup>A transformation is referred to as global if the transformation parameter is the same at all points in spacetime. A simple example would be a constant phase shift in the field.

<sup>&</sup>lt;sup>2</sup>Following the previous example, in a local transformation the phase shift is different at each point in space and time.

- 2. The weak interaction is a gauge theory of the symmetry group SU(2). All particles take part in the weak interaction, transmitted via the  $W^+$ ,  $W^-$  and Z bosons.

- 3. The strong interaction is described by Quantum Chromodynamics, an SU(3) gauge theory. It describes the strong interaction between quarks, realised as exchange of gluons.

|              |          | Name              | Symbol      | Mass $\left[\frac{\text{MeV}}{c^2}\right]$ | Charge [e] | Spin |

|--------------|----------|-------------------|-------------|--------------------------------------------|------------|------|

|              |          | Electron          | $e^-$       | $5.11 \cdot 10^{-1}$                       | -1         | 1/2  |

|              | _        | Muon              | $\mu^-$     | $1.06 \cdot 10^{2}$                        | -1         | 1/2  |

|              | eptonen  | Tau               | $ 	au^-$    | $1.78 \cdot 10^{3}$                        | -1         | 1/2  |

|              | oto      | Electron Neutrino | $\nu_e$     | $< 2 \cdot 10^{-6}$                        | 0          | 1/2  |

| ns           | Lej      | Muon Neutrino     | $ u_{\mu}$  | < 0.19                                     | 0          | 1/2  |

| Fermions     |          | Tau Neutrino      | $\nu_{	au}$ | $< 1.82 \cdot 10^{1}$                      | 0          | 1/2  |

| ırı          |          | Up Quark          | u           | 2.2                                        | +2/3       | 1/2  |

| $\mathbf{F}$ |          | Charm Quark       | c           | $1.27 \cdot 10^{3}$                        | +2/3       | 1/2  |

|              | ks       | Top Quark         | t           | $1.73 \cdot 10^{5}$                        | +2/3       | 1/2  |

|              | Quarks   | Down Quark        | d           | 4.7                                        | -1/3       | 1/2  |

|              | 0        | Strange Quark     | s           | $9.6 \cdot 10^{1}$                         | -1/3       | 1/2  |

|              |          | Bottom Quark      | b           | $4.18 \cdot 10^3$                          | -1/3       | 1/2  |

| —<br>Ф       | Ñ        | Photon            | $\gamma$    | 0                                          | 0          | 1    |

| Gauge        | Bosons   | Gluon             | g           | 0                                          | 0          | 1    |

| da<br>Ch     | 308      | W-Boson           | $W^{\pm}$   | $8.04 \cdot 10^4$                          | ±1         | 1    |

|              | <u> </u> | Z-Boson           | Z           | $9.12 \cdot 10^4$                          | 0          | 1    |

| -            |          | Higgs-Boson       | Н           | $1.25 \cdot 10^5$                          | 0          | 0    |

**Table 2.1:** List of particles included in the Standard Model. The antiparticles of the fermions are not listed explicitly. Values adapted from [28].

Table 2.1 gives an overview of the elementary particles in the SM.

The fermions are divided into two groups, the leptons and the quarks. The different particle types differ in their behaviour, as only the quarks take part in the strong interaction.

Both the leptons and the quarks are divided into three generations, with each generation consisting of a pair of particles. The particles in the higher generations have the same properties as the ones in the first generation, except for the mass, that rises with the generations.

Each lepton generation consists of a massive, charged particle and an approximately massless neutrino. While the massive partner takes part in both the electromagnetic and the weak interaction, the neutrinos only interact weakly.

The quark generations each consist of one up- and one down-type quark. These have different electromagnitic coupling strengths, with charges of  $+\frac{2}{3}$  and  $-\frac{1}{3}$ , respectively. In contrast to the leptons, all quarks take part in all three interactions.

The properties of the gauge bosons result from the structure of the underlying gauge group. Photons are massless particles that do not couple directly to each other, because the underlying U(1) group is abelian. The gluons, while also massless, do couple to each other, due to the non-abelian nature of the SU(3) gauge group.

The SU(2) symmetry of the SM is spontaneously broken: while the symmetry is present in the theory, the ground state violates the symmetry. This is caused by an additional field, the Higgs field, whose potential energy leads to the asymmetric ground state. As a consequence of the spontaneous symmetry breaking, the SU(2) bosons aquire a non-zero mass and an additional particle is introduced to the model: the Higgs boson H.

## 2.2 Beyond the Standard Model

While all other particles in the standard model had been known to exist for a long time already, the Higgs boson remained the last missing piece until its discovery in 2012. With its discovery, all particles in the Standard Model have been tested experimentally, further solidifying it as the central theory of particle physics.

Nevertheless, open questions remain which the Standard Model does not provide an answer to. These include:

- Astronomical observations show that the *baryonic matter*, i.e. ordinary matter consisting of atoms, only makes up about 5% of the observed universe, with the remainder consisting of *dark matter* and *dark energy* [29]. Neither of these are described by the Standard Model.

- While the Standard Model formulates the electromagnetic, weak and strong interactions in a cohesive framework, no microscopic formulation for the *gravitational force* exists as of yet.

- The asymmetry between matter and antimatter observed in the universe is not reflected in the existing asymmetries in the Standard Model [30]. Thus, additional mechanisms that further this asymmetry have to exist.

To answer these questions conclusively, further particle physics experiments are required. One of these is the ATLAS experiment at the Large Hadron Collider, both of which are described in the next chapter.

# 3 The ATLAS Experiment at Large Hadron Collider

One way to probe particle physics processes is colliding particles at high energies. For this purpose, the Large Hadron Collider (LHC) has been constructed to accelerate two beams of protons and collide them at four interaction points. It is the flagship project of the European Organization for Nuclear Research, CERN<sup>1</sup>, in Geneva, Switzerland.

ATLAS is one of four large experiments situated at the LHC. Installed at one of the four *pp* interaction points, the ATLAS detector records the particles that are produced in the collisions as inclusively as possible.

This chapter provides an overview of the LHC machine and its typical operation parameters (Section 3.1) and gives a detailed description of the ATLAS detector, (Section 3.2).

## 3.1 The Large Hadron Collider

The LHC [31] is a circular particle accelerator with a circumference of 26.7 km. It is installed in the tunnel that previously housed the Large Electron Positron Collider (LEP) between 45 and 170 m underground. It is optimised to collide protons, but can also be operated with heavy ions.

The particles are collided in four interaction points, each of which is equipped with one of four major experiments. The ATLAS [32] and CMS [33] experiments are general purpose detectors that are designed to record pp collisions in a wide phase space. The LHCb [34] experiment is a forward spectrometer optimised for the detection of B mesons. The ALICE [35] experiment focusses on heavy ion collisions to probe the quark-gluon-plasma that forms at the high energy densities produced in these processes.

#### 3.1.1 LHC Machine

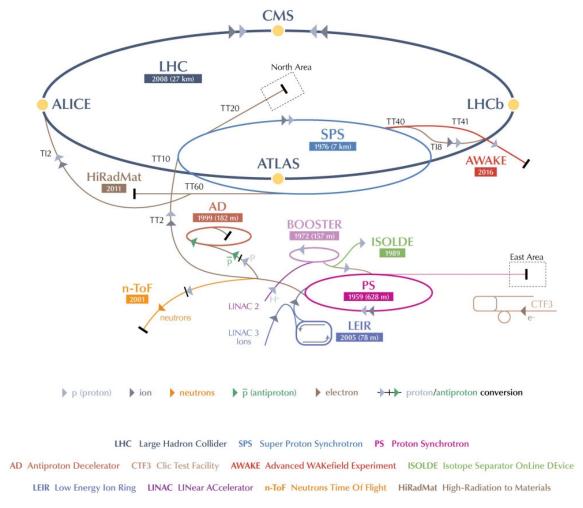

Figure 3.1 shows the CERN accelerator complex. It consists of a chain of preaccelerators that prepare the proton beams for injection into the LHC. The protons are produced by stripping hydrogen atoms of their electrons in a strong electric field. They are then accelerated in a linear accelerator (LINAC2), followed by a series of increasingly stronger circular accelerators: the Proton Synchrotron

<sup>&</sup>lt;sup>1</sup>Conseil européen pour la recherche nucléaire

Figure 3.1: The CERN accelerator complex. [36]

Booster (BOOSTER), the Proton Synchrotron (PS) and the Super Proton Synchrotron (SPS). At injection into the LHC, the protons have an energy of about  $450\,\mathrm{GeV}$

The LHC itself is a circular synchrotron that consists of eight straight sections that are connected by eight curved sections. One of the straight sections is equipped with superconducting radiofrequency cavities that are operated at 400.8 MHz to accelerate the proton beams. The curved sections are equipped with superconducting dipole magnets that produce a magnetic field of up to 8.34 T to bend the proton trajectories and keep them in the ring. At the remaining sections, quadrupole and octopole magnets are installed that focus the proton beams, most strongly at the four interaction points.

The central performance parameters of a particle accelerator are the centre-ofmass energy  $\sqrt{s}$ , that determines which particle physics processes can be effectively probed in a collision, and the luminosity  $\mathcal{L}$ , that describes the number of collisions that are produced. The number of collision events N that result in a final state X is given by

$$N = \mathcal{L} \cdot \sigma_{pp \to X},\tag{3.1}$$

where the cross-section  $\sigma_{pp\to X}$  describes the probability of the process  $pp\to X$  to occur in a collision. The cross-section depends on the underlying physical laws governing the process and the available phase space, both of which depend strongly on the centre-of-mass energy. Achieving a large number of events for rare final states thus depends on both maximizing the luminosity and reaching a sufficiently large centre-of-mass energy.

As it is defined above, the luminosity  $\mathcal{L}$  corresponds to the total amount of events that are accumulated over a defined period of time. For a given point in time, the *instantaneous luminosity*  $\mathcal{L}_{inst}$  gives the rate at which events are produced. It is defined by  $\mathcal{L}_{inst} = \frac{d}{dt}\mathcal{L}$ . In this context,  $\mathcal{L}$  is also referred to as the *integrated luminosity*.

The LHC is designed to collide protons at a centre-of-mass energy of  $14 \,\mathrm{TeV}$ , corresponding to  $7 \,\mathrm{TeV}$  per beam. The design luminosity is  $10^{34} \,\mathrm{cm}^{-2} \mathrm{s}^{-1}$ .

The LHC is operated in a series of *fills*, in which it contains proton beams and collides them. At the start of each fill, protons pass through the accelerator chain described above and are injected into the LHC. Once the LHC is filled, it starts accelerating the protons, until they reach their target energy. The focusing magnets around the collision points are configured such that the beams are brought into collision, to start the luminosity production.

During a fill, the instantaneous luminosity falls as a function of time, as protons are lost from the beams with each collision that occurs. Once it falls below a certain threshold, it is more efficient to restart the operational cycle, by *dumping* the beams and injecting new beams into the LHC. One fill can last many hours, e.g. the longest fill of 2016 operations contains 37 continous hours of luminosity production<sup>2</sup>. Interfill periods usually last for about one to two hours.

After the LHC first started operation in September 2008, a faulty electrical connection between two of the superconducting magnets caused a gas explosion, damaging a section of the accelerator [37]. This necessitated extensive repairs, so that the LHC was only restarted in November 2009. In a conservative approach, the beam energy was slowly increased from 450 GeV up to 3.5 TeV until March 2010. Data was recorded at this energy until November 2011, collecting a dataset of 5.6 fb<sup>-13</sup>. In March 2012, the LHC operation resumed at a centre-of-mass energy of 8 TeV. With luminosities up to  $7.73 \times 10^{33} \, \mathrm{cm}^{-2} \mathrm{s}^{-1}$ , a total dataset of 23.3 fb<sup>-1</sup> was recorded until December 2012. This whole period of data taking is referred to as Run-1 of the LHC [38].

Run-1 was followed by the first long shutdown (LS1) of the LHC, that lasted until early 2015. During this time, the accelerator complex was prepared to provide both higher energies and higher luminosities. In the years 2015 and 2016, LHC success-

$<sup>^{2}</sup>$ Fill 5045

<sup>&</sup>lt;sup>3</sup>The barn (b) is used as a unit for cross sections in particle physics. It is defined as  $1 \, b := 10^{-24} \, \text{cm}^2$ . From Equation 3.1 it follows that the unit for luminosity is the inverse of this,  $b^{-1}$ .

fully provided pp collisions at a centre-of-mass energy of 13 TeV. In 2016, the luminosity surpassed the design goal, with peak luminosities up to  $1.38 \times 10^{34} \,\mathrm{cm^{-2}s^{-1}}$  having been achieved. The total integrated luminosity is  $4.2 \,\mathrm{fb^{-1}}$  in 2015 and  $38.5 \,\mathrm{fb^{-1}}$  in 2016 [39].

The period of operation following LS1 is referred to as Run-2, and is planned to last until the end of 2018. It is to be followed by the second long shutdown (LS2), which will see further improvements to the accelator chain. This is expected to increase the luminosity beyond  $2 \times 10^{34} \,\mathrm{cm}^{-2} \mathrm{s}^{-1}$ .

#### 3.1.2 Proton Beam Structure

The LHC proton beams consist of bunches of protons that typically contain of the order of  $10^{11}$  particles. Each proton beam consists of 3564 possible bunch slots. Due to operational constraints in the filling of the LHC and the dumping of the beams, not all of these slots actually contain bunches. By design, a maximum of 2808 bunches can be *filled*, while the remainder stays *empty*.

The 'collision' of two bunch slots at one of the interaction points is referred to as *Bunch Crossing* (BC). BCs occur at a frequency of 40.08 MHz, i.e. are spaced approximately 25 ns apart. One revolution, or *orbit*, of the LHC corresponds to 3564 BCs, after which the same bunches collide again. Each BC in the orbit is thus assigned a unique BC Number<sup>4</sup> between 0 and 3563.

In a typical data taking run, the protons are organised into *trains* of filled bunches, with *gaps* of empty bunches between them. This results in a similar structure for the BCs. The orbit contains several trains of *paired* BCs, where the bunches are filled in both beams, that are separated by gaps of *unpaired* or *empty* BCs, where either only one or none of the beams contains a filled bunch.

A further distinction is made in the bunch spacing within the trains. In Run-1, bunch trains typically consisted of alternating filled and empty bunches, resulting in a 50 ns spacing between collisions. In Run-2, all bunches in a bunch-train are filled, resulting in a bunch spacing of 25 ns. This has consequences for the detectors that record the collisions, as it changes how events overlap with each other.

This overlap between events is referred to as *pile-up*. It is quantified by the mean number of pp interactions that take place in a collision of two filled bunches,  $\mu$ . It depends on the machine operation and the luminosity: if more protons interact, at the same time, the luminosity increases. While maximising the luminosity is one of the keys to enhance the sensitivity to rare processes, it has to be balanced against the increasing pile-up, which deteriorates the detector performance. In 2016, the average pile-up was measured to be  $< \mu > = 24.9$ .

The magnitude of the pile-up also depends on the bunch spacing. By decreasing the bunch spacing, more filled bunches can be fit into the LHC at the same time. This allows to reach the same luminosity as for larger bunch spacing with less

<sup>&</sup>lt;sup>4</sup>This is also often referred to as BC Identifier, or BCID. To avoid confusion with the BC Identification algorithms discussed later, the term BC Number will be used throughout this document.

focussed beams, and thus reduced  $\mu$ . While this reduces the pile-up originating from the same BC (*in-time pile-up*), the newly introduced collisions in the preceding BC lead to an additional, *out-of-time pile-up*. Depending on the specifics of the detector, either of these can have a larger effect.

With the increasing luminosity, pile-up is thus one of the main challenges for the detectors in their respective upgrade programs.

#### 3.1.3 Aspects of Proton-Proton Collisions

Proton-proton (pp) collisions offer distinct advantages compared to other experiments. As protons have a higher mass than electrons,  $m_p = 938\,\mathrm{MeV}$  compared to  $m_e = 511\,\mathrm{keV}$ , the energy loss due to Bremsstrahlung, which scales as  $P \sim m^{-4}$ , is far less for proton beams than for electron beams. This allows pp colliders to reach much higher centre-of-mass energies than  $e^+e^-$  colliders using the same geometry. Comparing pp to  $p\bar{p}$  colliders, protons are easier to mass produce than antiprotons, allowing for higher statistics in particle collisions.

The main drawback in colliding protons lies in their nature as composite particles. In the low energy limit, each proton consists of a triplet of *valence quarks*, two up quarks and one down quark. At higher energy scales, the deeper structure of the proton becomes apparent, with the gluons that bind the valence quarks together taking part in the interaction, as well as *sea quarks*, that are produced by gluons undergoing pair conversion within the proton. All these constituents of the proton are referred to as *partons*.

The interaction of two protons at high energies is equivalent to the interaction of partons. Because each parton only carries a fraction of the total momentum of the proton, the centre-of-mass energy of the parton-parton interaction is not known a-priori. Furthermore, even in a symmetric pp collision where both protons have the same momentum, the parton-parton collision is typically asymmetric. This has important consquences for the design of particle detectors at pp colliders, because the initial state momentum along the beam axis is not known. Due to this reason, final state particles are usually analysed with regard to their transverse momentum,  $p_T$ , i.e. the momentum component in the plane transverse to the beam axis, which is zero in the initial state.

The type of parton that participates in the interaction depends on the energy scale of the pp collision. At LHC energies, gluons typically have the highest probability of interacting.

## 3.2 ATLAS Detector

ATLAS [32] is one of four large experiments at the LHC. It is a general-purpose particle detector optimised on recording pp collisions as inclusively as possible.

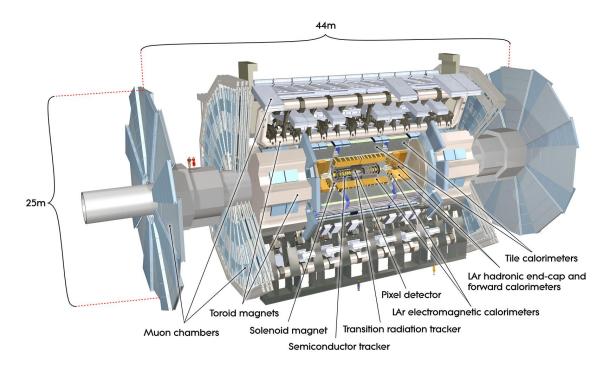

Figure 3.2 shows the ATLAS detector. It consists of three major parts: a cylindrical barrel around the pp interaction point in the centre and two endcaps attached

Figure 3.2: The ATLAS detector. [32]

to the sides of the barrel. It is 44 m long, 25 m high and weighs 7000 t in total.

The detector consists of several layers of sub-detectors. Closest to the interaction point is the *Inner Detector*, which is surrounded by a solenoid magnet. It measures the tracks of traversing charged particles. This allows to reconstruct the momentum of the particles from the track curvature in the magnetic field, and to identify the point of origin of the tracks. The next layer is the *Electromagnetic Calorimeter*. It is built to contain electromagnetic showers that are initiated by incident electrons and photons, thus measuring the energy of these particles. While hadronically decaying particles also initiate showers in the electromagnetic calorimeter, these typically extend much further than electromagnetic showers. The *Hadronic Calorimeter* is thus required to fully contain these showers. The outermost sub-detector is the *Muon Spectrometer*, that detects any charged particles that are not stopped within the calorimeter and measures their momentum in a magnetic field generated by large toroid magnets.

## 3.2.1 Coordinate System

ATLAS uses a right-handed coordinate system with its origin in the nominal interaction point. The x-axis points towards the centre of the LHC ring, the y-axis points upwards towards the surface and the z-axis points along the beam pipe. The azimuth angle  $\phi$  is defined in the x-y-plane from 0 to  $2\pi$  starting from the x axis direction. The polar angle  $\theta$  is defined from 0 to  $\pi$  starting from the z-axis direction.

Typically the polar angle is expressed in terms of the pseudorapidity,

$$\eta = -\ln \tan(\theta/2). \tag{3.2}$$

A pseudorapidity of zero corresponds to the transverse direction, while it approaches  $+/-\infty$  for the positive/negative z-axis direction.

In the high-energy limit, the pseudorapidity is equal to the rapidity,

$$y = \frac{1}{2} \ln \left( \frac{E + p_L}{E - p_L} \right), \tag{3.3}$$

where  $p_L$  is the momentum component along the beam pipe. Differences in rapidity are invariant under lorentz boosts along the longitudinal axis, making it a useful quantity for physics analyses.

#### 3.2.2 Inner Detector

The Inner Detector detects traversing charged particles and is used to reconstruct their trajectories. By measuring the bending radius of these tracks in the solenoid magnetic field, the momentum of the particles is obtained. By extrapolating the tracks, the primary collision vertex as well as decay vertices of secondary particles are identified.

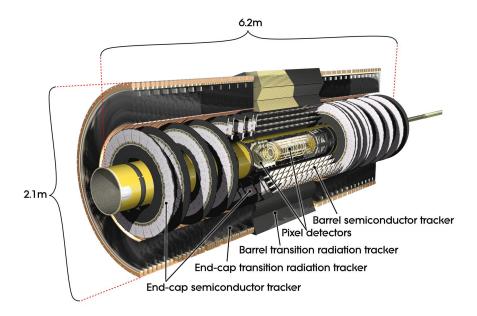

Figure 3.3: Overview of the Inner Detector of the ATLAS experiment. [32]

Figure 3.3 shows an overview of the Inner Detector. It covers the region  $|\eta|$  < 2.5 and consists of three major components. The innermost of these is the Pixel Detector. In Run-1 it consisted of three layers of silicon pixel detectors, in both the barrel and the endcap. The pixel size is  $50 \times 400 \,\mu\text{m}$  in  $\phi \times z$  (R) in the barrel

(endcap). This results in a position resolution of  $10 \,\mu\text{m}$  in the  $R-\phi$  plane and  $115 \,\mu\text{m}$  along the z-axis. In total, the three original pixel detector layers contain  $80.4 \,\text{million}$  readout channels.

In LS1, an additional fourth pixel layer has been installed in the centre of the Pixel Detector to counteract ageing effects in the original innermost layer. This so called *Insertable B-Layer* [40] adds a further 12 million channels to the readout volume. A reduced pixel size of  $50 \times 250\,\mu m$  and a shorter distance to the beam pipe - 3.27 instead of  $5.05\,cm$  - also lead to a better vertex resolution.

Outside the Pixel Detector, the Semiconductor Tracker is installed. It consists of four barrel layers and nine layers in either of the endcaps. Each layer in turn consists of two layers of silicon strip detectors. In the barrel, one layer is arranged parallel to the z-axis and the second layer is tilted by 40 mrad with respect to the first. In this way, both the  $\phi$  and the z coordinate can be measured precisely. In the endcap, one layer is arranged radially, and the two layers are tilted by the same angle. The Semiconductor Tracker provides a resolution of 17 µm in the  $R-\phi$  and 580 µm along the z (R) axis in the barrel (endcap) and contributes 6.3 million channels to the readout volume.

The part of the Inner Detector furthest from the interaction point is the Transition Radiation Tracker. It consists of drift tubes with a diameter of 4 mm. The tubes are filled with a xenon-based gas mixture which is ionised by traversing particles. The produced charges are collected on gold-plated tungsten wires that serve as anodes. The barrel section consists of 73 layers of 144 cm long tubes. They are arranged parallel to the z-axis with an average distance of 7 mm. Each endcap section is eqipped with 160 layers of radially oriented tubes of 37 cm length. Due to this setup, the Transition Radiation Tracker is only sensitive to the  $R-\phi$  plane, where it reaches a resolution of 130 µm.

In addition to the ionisation caused by charged particles, the Transition Radiation Tracker also detects transition radiation photons. These are emitted by charged particles when they pass the boundary between two materials with different dielectric constants. The photons are absorbed in the gas, which induces large signals in the tubes. The energy of the emitted photons is proportional to the Lorentz factor,  $\gamma = E/m$ . The Transisition Radiation Tracker thus contributes to the particle identification by providing information on the mass of charged particles. In particular, it allows to distinguish electrons from heavier particles like charged pions.

## 3.2.3 Calorimetry

The calorimeter absorbs incident particles and determines the energy and position of the resulting particle showers.

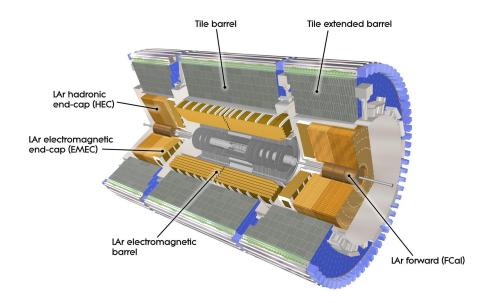

Figure 3.4 shows an overview of the ATLAS calorimeter. It consists of two layers, each of which is further subdivided into a barrel and two endcap regions, and additional forward calorimetry. The inner layer is the electromagnetic calorimeter. It is optimised for the measurement of electrons and photons, which produce electromagnetic showers. The outer layer is the hadronic calorimeter. It contains

Figure 3.4: Overview of the ATLAS Calorimeter. [32]

hadronic showers (jets), that typically extend beyond the electromagnetic calorimeter, and contributes to the measurement of the missing transverse energy. The forward calorimeters also contribute to the hadronic energy measurement. In total, the ATLAS calorimeter covers the region  $|\eta| < 4.9$ .

All ATLAS calorimeters are sampling calorimeters, constructed from alternating layers of absorbers and active material. The absorber layers are constructed from dense material, so that the incident particles interact with it more strongly. This way, the particle showers are contained more effectively in the calorimeter, allowing for a more compact and cheaper construction of the detector. The deposited energy of the particles is measured in the active layers.

Only the part of the total shower energy that is deposited in the active medium is detected. As the shower shape varies statistically, the fraction of energy that is deposited in the active layers also fluctuates. This reduces the energy resolution of sampling calorimeters compared to homogenous calorimeters, where the full detector consists of active material.

The energy resolution achieved by the different layers of the ATLAS calorimeter is shown in table 3.1.

| Calorimeter                 | $\sigma_E/E$                 |

|-----------------------------|------------------------------|

| Electromagnetic Calorimeter | $10\%/\sqrt{E} \oplus 0.7\%$ |

| Hadronic Calorimeter        | $50\%/\sqrt{E} \oplus 3\%$   |

| Forward Calorimeter         | $100\%/\sqrt{E} \oplus 10\%$ |

**Table 3.1:** Energy resolution of the different ATLAS calorimeter layers. [32]

The different calorimeter partitions are described in the following.

#### **Electromagnetic Barrel Calorimeter**

The Electromagnetic Barrel Calorimeter (EMB) consists of two half barrels, one covering the positive and one covering the negative z direction. With a total length of about 6.4 m and a thickness of 0.6 m, it covers the region  $|\eta| < 1.475$ . Depending on  $|\eta|$ , the thickness corresponds to 22 to 33 radiation lengths<sup>5</sup>  $X_0$ , as seen from the interaction point.

The EMB utilises lead plates as absorbers, that are formed in a radially oriented accordion shape. The volume between the plates is filled with liquid argon (LAr) as active medium that is ionised by the secondary particles produced in the electromagnetic showers. Kapton electrodes are placed in the centre between two layers of lead to collect ionisation charges. They follow the accordion shape of the absorber plates at a constant distance of 2.1 mm. This leads to a typical drift time of about 450 ns.

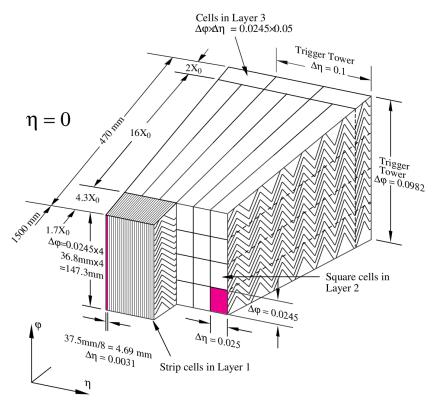

Figure 3.5: Structure of the EMB modules. [32]

Each half barrel consists of 16 modules. Figure 3.5 illustrates the structure of the EMB modules. They consist of three layers of different granularity. The first layer

<sup>&</sup>lt;sup>5</sup>The radiation length is defined as the average distance after which the energy of an incident particle is reduced by a factor  $\frac{1}{e}$  due to electromagnetic interactions with the detector material.

consists of strip cells with a size of  $(0.003 \times 0.1)$  in  $(\Delta \eta \times \Delta \phi)$ , with a thickness of 4.3  $X_0$ . The fine segmentation in  $\eta$  allows for a good discrimination between photons and neutral pions. The second layer is intended to absorb most of the energy deposited by incident particles and to provide a good position measurement. This is achieved by using square cells with a size of  $(0.025 \times 0.0245)$  in  $(\Delta \eta \times \Delta \phi)$  and a depth of 16  $X_0$ . The third layer consists of larger cells,  $(0.05 \times 0.0245)$  in  $(\Delta \eta \times \Delta \phi)$ , that measure the tails of the electromagnetic showers. It has a thickness of 2  $X_0$ .

An additional Presampler layer is installed in front of the EMB modules. It is used to correct for the energy loss in the inactive material between the interaction point and the calorimeter, i.e. the ID, the cryostat wall and the solenoid magnet. It consists of 64 cells of 1.1 cm thickness.

#### **Electromagnetic Endcap Calorimeter**

The two Electromagnetic Endcap Calorimeters (EMECs) are placed symetrically around the z-axis on either side of the EMB. Each EMEC extends from 0.33 m to 2.01 m from the beam pipe and has a thickness of 0.63 m. This corresponds to a coverage of  $|\eta| < 3.2$  and a depth of 24 to 38  $X_0$ , depending on  $\eta$ .

The EMEC uses the same LAr-lead sampling technology with kapton electrodes as the EMB. The accordion geometry is arranged parallel to the z-axis.

Each EMEC consists of two co-axial wheels: the outer wheel covers the region  $1.375 < |\eta| < 2.5$ , while the inner wheel covers  $2.5 < |\eta| < 3.2$ . Each of the wheels is in turn subdivided into eight modules. These are organised similar to the EMB, with several layers if differing granularity. For the region  $1.5 < |\eta| < 2.5$ , three layers with the same granularity as in the EMB are used. For  $1.375 < |\eta| < 1.5$  and  $2.5 < |\eta| < 3.2$  only two layers are installed, which have a coarser granularity of up to  $(0.1 \times 0.1)$  in  $(\Delta \eta \times \Delta \phi)$ .

Similar to the EMB, the EMEC is equipped with a presampler that covers the region  $1.5 < |\eta| < 1.8$ . It is thinner compared to its EMB counterpart, with a thickness of only  $0.5 \,\mathrm{cm}$ .

#### **Hadronic Tile Calorimeter**

The hadronic Tile calorimeter consists of a 5.8 m long barrel (TileLB) section that is placed symetrically around the interaction point and a 2.6 m long extension (TileEB) along both the positive and the negative z direction. The thickness of about 1.97 m corresponds to 7.4 interaction lengths<sup>6</sup>  $\lambda$  in radial direction. The Tile calorimeter covers the region  $|\eta| < 1.7$ .

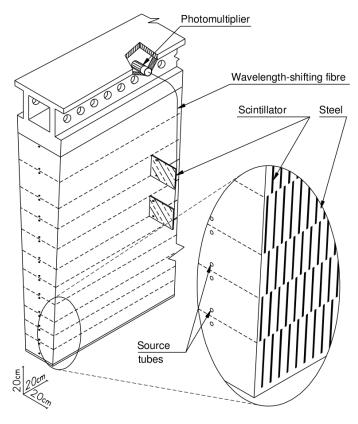

Each of the parts of the Tile calorimeter is divided into 64 modules. The design of one module is shown in Figure 3.6. It is built from stainless steel plates, that

<sup>&</sup>lt;sup>6</sup>The interaction length is the average distance after which the energy of a particle traversing the material is reduced by a factor  $\frac{1}{e}$ . Contrary to the similarly defined radiation length  $X_0$ , the interaction length includes both electromagnetic and strong interactions.

Figure 3.6: Structure of the Tile modules. [32]

function as absorbers, and scintillating tiles as active medium. The thickness of the steel plates is 5 mm, the tiles are 3 mm thick. The scintillation light produced by incident particles is read out by wavelength-shifting fibres that are attached to photomultiplier tubes. The module is organised into three layers of cells, that are formed by grouping the readout fibres of multiple tiles on the same photomultiplier tube. The granularity in  $(\Delta \eta \times \Delta \phi)$  is  $(0.1 \times 0.1)$  in the inner two layers, and  $(0.2 \times 0.2)$  in the outer layer.

#### **Hadronic Endcap Calorimeter**

A Hadronic Endcap Calorimeter (HEC) is installed on both sides of the detector. Each HEC consists of two wheels with an outer radius of 2.03 m and a combined depth of 12  $\lambda$ . They cover the region 1.5 <  $|\eta|$  < 3.2.

The HEC is constructed from copper plate absorbers and uses LAr as active medium. The plates have a thickness of 25 mm in the wheel closer to the interaction point and 50 mm in the wheel further out. The 8.5 mm gap between the plates is equipped with three electrodes, dividing it into four equally sized drift zones of 1.8 mm. The central electrode is used to read out the ionisation charge, while the outer two supply the high voltage. The drift time amounts to 430 ns. The cell granularity is given by the electrode segmentation. It is  $(0.1 \times 0.1)$  in  $(\Delta \eta \times \Delta \phi)$

up to  $|\eta| < 2.5$  and  $(0.2 \times 0.2)$  for larger  $|\eta|$ .

#### **Forward Calorimeter**

The Forward Calorimeters (FCals) are installed between the beam pipe and the endcaps. The FCal consists of three modules of 45 cm thickness on each side of the detector. In total, the FCal covers the region  $3.1 < |\eta| < 4.9$  and a depth of about  $10 \lambda$ .

The first module (FCal1) is optimised for electromagnetic interactions. It consists of copper plate absorbers that are penetrated by equidistant holes. The electrodes are placed within these holes and take the form of cylindrical pipes that run parallel to the z-axis. Each pipe is filled with LAr and contains an axially oriented copper staff. The drift distance between the pipe wall and the staff is about  $0.27\,\mathrm{cm}$ .

The second and third FCal modules (FCal2 and FCal3) function as hadronic calorimeters. Each of them consists of two copper plates of 2.35 cm thickness, between which the electrodes are arranged. These are very similar to the ones used in FCal1, the only differences being the material for the central staff - tungsten - and the drift distance - 0.38 cm in FCal2 and 0.51 cm in FCal3. The remaining volume between electrodes and the plates is filled with tungsten.

Due to the relatively small drift distance, the drift time in the FCal is much smaller than in the other LAr calorimeters used in ATLAS. It is the shortest in FCal1, where it is of the order of 60 ns.

#### 3.2.4 Muon Spectrometer

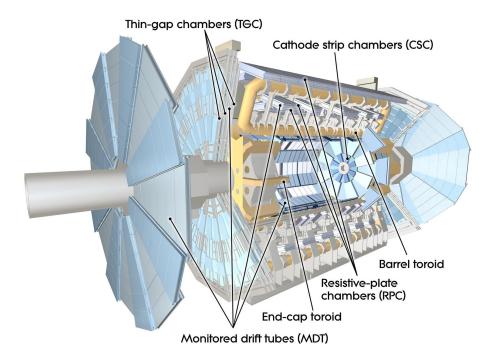

The muon system detects charged particles that are not stopped in the calorimeters. It consists of different gaseous detectors that are divided into two types: highly position sensitive detectors in order to measure the tracks of charged particles in the toroid magnetic field; and very fast detectors used for the trigger. In total, the Muon Spectrometer covers the region  $|\eta| < 2.7$ .

Figure 3.7 shows an overview of the ATLAS muon systems. In the barrel region, three cylindrical layers of Monitored Drift Tube chambers placed in the toroid magnets are used to measure the particle tracks. Each chamber contains three to eight layers of 30 mm diameter drift tubes. The tubes are filled with an argon-based gas mixture, that is ionised by traversing charged particles. In each tube, the charge is collected by a centrally positioned, coaxial tungsten-rhenium wire of 50 µm diameter.

In each endcap, four layers of Monitored Drift Tubes cover the region up to  $|\eta| < 2$ . in the most forward region,  $2 < |\eta| < 2.7$ , the inner-most layer is instead equipped with Cathode Strip Chambers. These are multi-wire proportional chambers with two cathode layers, each of which is segmented into strips. In one cathode, the strips are oriented parallel to the wires, while they are orthogonal on the other plate. This allows for a high position resolution in two dimensions. The main reason to use this type of detector in the forward region is the higher granularity compared to the drift

Figure 3.7: Overview of the ATLAS Muon Spectrometer. [32]

tubes. This alleviates the challenge imposed by the higher rates and backgrounds at larger  $|\eta|$ .

The Monitored Drift Tubes attain a position resolution of about 35  $\mu$ m per chamber, with a total drift time of 700 ns. The Cathode Strip Chambers achieve a position resolution of 40  $\mu$ m orthogonal to the magnetic field and 5 mm parallel to it. Their timing resolution if 7 ns, with a drift time of 40 ns.

The muon trigger information for the barrel is obtained from Resistive Plate Chambers. These consist of two parallel resistive plates, placed 2 mm apart, with a high voltage applied between them. The volume between the plates is filled with gas that is ionised when a particle passes through it. The electric field then causes the production of an avalanche from these primary charges. The signal is read out via metal strips that are placed on the outside of the chamber. They achieve a position resolution of 10 mm and a timing resolution of 1.4 ns.

In the endcaps, Thin Gap Chambers are used for the trigger. These are also multi-wire proportional chambers, but the distance between the wires, 1.8 mm, is larger than the distance from the wires to the plates, 1.4 mm. This leads to short drift times and a good timing resolution of 4 ns. The position resolution is 2-6 mm in radial direction and 3-7 mm in  $\phi$ .

## 3.2.5 Magnets

The ATLAS detector contains four large superconducting magnets. They provide the magnetic fields that are required by the tracking and muon systems.

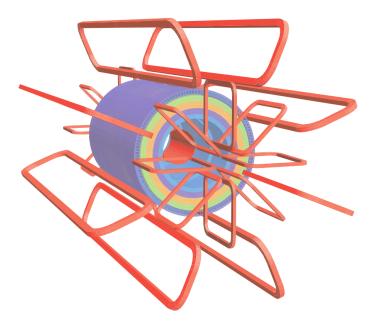

**Figure 3.8:** Overview of the ATLAS magnet systems. The different magnets are shown in red, with the solenoid in the centre and the toroids on the outside of the detector. [32]

Figure 3.8 shows an overview of the ATLAS magnets. In the centre of the barrel part of the detector, a solenoid magnet is installed between the Inner Detector and the Electromagnetic Calorimeter. It consists of a single-layer NbTi coil that produces a 2T field in the Inner Detector that is oriented parallel to the z-axis. The solenoid extends over a length of 5.8 m. As it is positioned before the Electromagnetic Calorimeter, the material contribution of the solenoid has to be minimised to reduce the probability of particles starting to shower before the calorimeter. To achieve this, the solenoid is formed of a single coil and is installed in the same cryostat as the electromagnetic calorimeter. This results in a total of only 0.66 radiation lengths of material in front of the calorimeter.

One barrel toroid and two endcap toroid magnets make up the remainder of the ATLAS magnet systems. All three toroids consist of eight coils each, which are placed symetrically around the beam pipe, producing a cylindrical magnetic field in the Muon Spectrometer. The field strength is 0.5 T in the barrel and 1 T in the endcaps.

#### 3.2.6 Further Subdetectors

Next to the major components described above, ATLAS contains several additional subdetectors for various specialised purposes.

• The Minimum-Bias Trigger Scintillator (MBTS) consists of two rings of 2 cm thick scintillating tiles on each side of the detector. It is used to detect and trigger on non-diffractive pp interactions.

- The Luminosity Measurement with Cherenkov Integrated Detector (LUCID) monitors the luminosity seen by the ATLAS experiment. It consists of gas filled aluminium tubes that are installed close to the beam pipe in the muon endcap region. Particles traversing the gas produce Cherenkov radiation that is detected by photomultiplier tubes.

- Three forward detectors are installed at larger distance from the interaction point to analyse pp interactions in the very forward region: The Zero Degree Calorimeter (ZDC) is situated at 140 m from the interaction point and is optimised to detect neutrons in heavy ion collisions; Absolute Luminosity for ATLAS (ALFA) is located at 240 m from the interaction point and measures elastic pp scattering; ATLAS Forward Protons (AFP) has been newly installed during Run 2 at 210 m distance from the interaction point to complement the ALFA program by measuring diffractive processes.

## 3.3 ATLAS Detector Control System

The Detector Control System (DCS) collects and monitors environmental data from the different ATLAS subsystems. This includes the applied voltages, the temperature of both devices and the environment, gas pressure in the detector etc. . These quantities are continously compared against thresholds which define the safe operating conditions of the different detectors. If a deviation beyond a threshold is detected, appropriate warnings or alarms are raised. For strong deviations, automatic countermeasures are induced, in the worst case shutting down the affected component.

## 3.4 ATLAS Trigger and Data Aquisition System

The signals induced in the detectors are stored in dedicated data buffers in the detector front-end electronics. The ATLAS Trigger and Data Aquisition (DAQ) systems, commonly referred to as TDAQ, extract the event data from the front-end and transmit it to mass storage.

As the event rate of 40 MHz, coupled with an event size of several MB, is far too large to store all events, the trigger is used to reduce the rate by selecting only those events that are of potential interest to physics analysis. If an event is selected by the trigger, the DAQ system collects the data from all ATLAS subdetectors, assembles it into a common event format and stores it on disk.

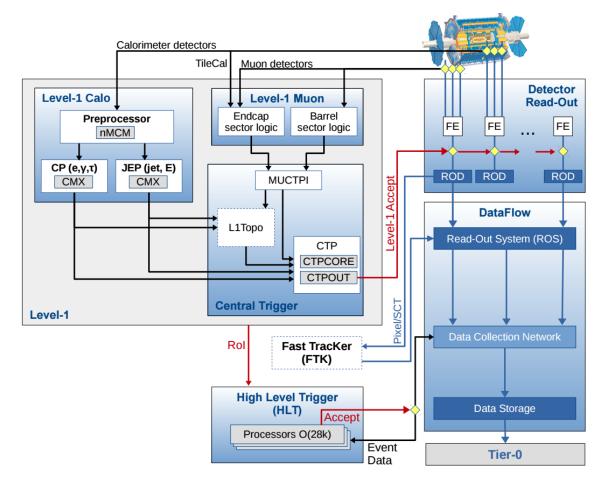

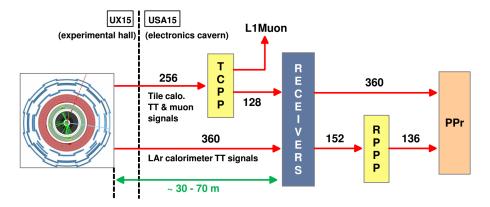

An overview of the TDAQ system is shown in Figure 3.9. It is broadly divided into four parts: the Readout of the Detector, the Level-1 (L1) Trigger, the High Level Trigger (HLT) and the Data Flow system.

The L1 trigger receives reduced granularity data from the calorimeters and the muon systems at 40 MHz. If an event is selected, an L1 Accept (L1A) signal is sent to all ATLAS subdetectors, which initiates the readout of the detector data.

**Figure 3.9:** Overview of the ATLAS TDAQ system. At the time of writing, the L1Topo and FTK system are in a commissioning state and are planned to be used in 2017 data taking. [41]

The time between the transmission of data off the detector and the reception of the L1A is limited to 2.5 µs by the size of the buffers in the detector front end. Due to this constraint, the L1 trigger is implemented entirely in custom hardware. The target L1A rate is 100 kHz, corresponding to a rate reduction by a factor of 400.

Upon receiving the L1A signal, the full granularity data is read out from the detector front-end to a further buffering stage in the DAQ sytem. The data is then analysed by the HLT, using also Regions of Interest (RoIs) received from the L1 trigger that identify the locations of particle candidates found by that system. If an event is selected by the HLT, it is fully reconstructed and transmitted to mass storage. The target event rate at the HLT output is 1 kHz.

The different components of the TDAQ system are briefly discussed in the following.

## 3.4.1 Level-1 Trigger

The L1 trigger analyses reduced granularity data from the calorimeter and muon detectors to identify events that contain highly energetic muons, electrons, photons, jets and hadronically decaying tau leptons as well as large missing transverse energy  $(E_T^{miss})$  and total transverse energy  $(E_T^{tot})$ .

As seen in Figure 3.9, it is divided into several major components: the L1 Calorimeter Trigger (L1Calo), the L1 Muon Trigger (L1Muon), the L1 Topological Trigger (L1Topo) and the Central Trigger Processor (CTP).

### Level-1 Calorimeter Trigger

The L1Calo trigger is a pipelined processing system that analyses about 7200 analogue signals from the calorimeters. It digitises and synchronises these signals, calibrates them to  $E_T$  and identifies particle candidates in the resulting  $E_T$  distribution across the calorimeter. The particle candidates are transmitted to the L1Topo system, and the multiplicity of particle candidates above certain  $E_T$  thresholds is forwarded to the CTP. If a given event is selected by the L1 trigger, the L1Calo trigger provides event data to the readout system and supplies RoI information to the HLT. A detailed description of L1Calo is given in Chapter 4.

### Level-1 Muon Trigger

The L1Muon trigger analyses data from the trigger chambers, i.e. the RPCs in the barrel and the TGCs in the endcaps. It detects muon candidates and estimates their  $p_T$ . The measured  $p_T$  is compared to six programmable thresholds, and the number of muons passing each threshold is provided to the CTP. Upon receiving an L1A from the CTP, the L1Muon trigger also supplies RoI information to the HLT and event data to the DAQ.

The L1Muon algorithm uses coincidences between detector stations in different layers to detect traversing particles. For each  $p_T$  threshold, pairs or triplets of coinciding trigger chambers are defined that indicate a muon candidate above the threshold. These coincidence windows are derived by assuming a muon coming from the nominal interaction point and passing a station in one of the detector layers, referred to as the pivot layer. In the barrel, this is the middle layer of RPCs, while in the endcap it is the back layer of TGCs. Depending on which trigger chamber in the pivot plane is passed by the muon, one or two further stations have to be hit as well in order to satisfy the threshold condition.

### Level-1 Topological Trigger

The L1Topo trigger receives particle candidates from the L1Calo and L1Muon system and applies selection criteria that involve the topology of the event. Among others, this includes cuts on the angular separation between particle candidates or the invariant mass of systems of particles.

### Central Trigger Processor

The CTP receives particle multiplicities from the L1Calo and L1Muon systems as well as the results of the L1Topo trigger. It also receives trigger inputs from the forward detectors and from the MBTS. The inputs are checked against a programmable L1 trigger menu, that contains a list of trigger items. Each trigger item defines certain conditions that have to be satisfied in order to trigger the event. For example, the L1\_J400 trigger item is satisfied if at least one jet above an  $E_T$  threshold of 400 GeV is detected. If at least one item in the trigger menu is met for a given event, the event is accepted and the CTP issues an L1A. In total, the CTP can form 512 possible trigger items from up to 320 inputs.

In order to keep the rates, expecially of low energy trigger items, under control, the CTP applies programmable prescales to each trigger item. The prescale acts as a reduction factor for the trigger rate: with a prescale of n, only every n'th event satisfying the prescaled trigger item is accepted. The prescales can be adapted online during a data taking run, allowing to adjust the L1 trigger output as the luminosity decreases.

As the application of a prescale introduces a statistical bias to the trigger selection, unprescaled trigger items are of special importance. For this reason, the lowest unprescaled trigger items are among the most important ones included in the trigger menu, and usually used as primary triggers for physics analyses.

The CTP also vetoes events according to two deadtime criteria. These are applied to prevent the readout buffers in the detector front-end from overflowing. The simple deadtime vetoes all triggers in a programmable number of BCs after each L1A. The complex deadtime applies a leaky bucket algorithm to model the amount of events stored in the front-end buffers. Each bucket is defined by two programmable numbers: the number of events that can be stored in one derandomiser at the same time and the number of BCs required to transmit one event out of the derandomiser. The bucket contents are incremented by one at each L1A, and reduced by one whenever the programmed number of BCs has passed. As long as the content of the bucket is equal to the programmed limit, all L1As are vetoed. The CTP supports up to four buckets in parallel, providing enough flexibility to cover the wide range of detector readout implementations.

Lastly, the CTP distributes several LHC protocol signals to the ATLAS subdetectors using the Timing and Trigger Control (TTC) system. This inludes the 40.08 MHz BC clock and the ORBIT signal, which indicates the beginning of a new LHC revolution. The latter is also referred to as the Bunch Counter Reset (BCR), as it is used to reset the internal BC number counters of various subsystems. A further TTC signal is the Event Counter Reset (ECR), that is used to reset the internal event counters in all ATLAS subsystems.

## 3.4.2 High Level Trigger and Data Aquisition

If the L1 trigger selects an event, subdetector-specific Readout Drivers (RODs) collect the data and transmit it to the Readout System (ROS), a network of commercial PCs. From there, it is made available to the HLT via the Data Collection Network.

The HLT is a software based trigger implemented in a farm of commercial PCs. It operates in two stages, with a partial event reconstruction in the first stage to reject the majority of the events and a second stage for more detailed selections. In the first stage, full granularity event data for the RoIs found by the L1 trigger is used to reconstruct the particle candidates with a higher precision. If an event passes this stage, the event is fully reconstructed by also retrieving the remaining data. At this stage, more precise selections are applied, that are similar to those used in offline data analysis. Events that also pass this stage are then stored to disk.

## 3.4.3 TDAQ Upgrade in LS1

The ATLAS TDAQ system has been upgraded during LS1 to adapt to the increased centre-of-mass energy and luminosity in Run-2 [42]. Both of these changes increase the rate of many types of physics signatures that are detected by the TDAQ system. In addition, the increased pile-up has a higher probability of *faking* these signatures, leading to an increase in fake rates as well.

The goal of the upgrade is to increase the performance of the TDAQ system such that the high trigger efficiency and low thresholds for unprescaled trigger items achieved in Run-1 are maintained despite these challenges. While the maximum trigger rate is increased from 75 kHz to 100 kHz, this is not sufficient to operate the same Run-1 system.

The upgrade of the different TDAQ systems is summarized in the following:

- The **L1Topo** trigger was added to the L1 trigger system. By changing form single-object  $E_T$  thresholds to multi-object topological selections, the rates of triggers required for several physics signatures can be strongly reduced.

- The upgrade of the L1Calo trigger is described in more detail in the following chapters. In summary, the central processing units of the PreProcessor subsystem was replaced by an upgraded version to enhance the signal calibration and the interface to the central trigger was upgraded to support the new L1Topo system.

- The connectivity of the L1Muon system to the central trigger was upgraded to support the L1Topo system.

- The CTP was similarly upgraded to include the additional inputs provided by the L1Topo system. In total, the number of L1 trigger items was increased from 256 to 512.

- During Run-1, the HLT consisted of two separate computer farms the RoI based Level-2 trigger and the Event Filter that uses fully reconstructed events. These two systems were merged for Run-2, to allow for optimal resource sharing and reduced complexity in the connectivity between the systems.

- The readout system and data collection network were upgraded to improve the detector readout rate and the output rate to the HLT and the data storage system.

## 3.5 ATLAS Operation

The operation of the ATLAS detector is controlled by the TDAQ and DCS systems. A typical run of the experiment starts before protons are colliding in the LHC. It begins with the configuration of all subdetectors and their readout devices with the parameters appropriate to the LHC filling conditions. In this stage, the majority of trigger items are deactivated, with only a minimal set of triggers that are required for monitoring the detector condition being active. Once the beams in the LHC reach their stable collision configuration, the physics triggers are activated and the DAQ system begins to gather the recorded data.

Besides these *data taking runs*, ATLAS also performs regular *calibration runs*. These are used to gather data that is required to calibrate the detector and readout electronics. The are usually performed in interfill periods, with no protons in the LHC.

Each run is divided into *luminosity blocks*, or lumi blocks. These are periods of time during which the operating conditions like the detector configuration, the instantaneous luminosity or the trigger prescales are constant. A lumi block typically lasts for 60 s, but can be shorter if e.g. adjustments of the configuration are performed.

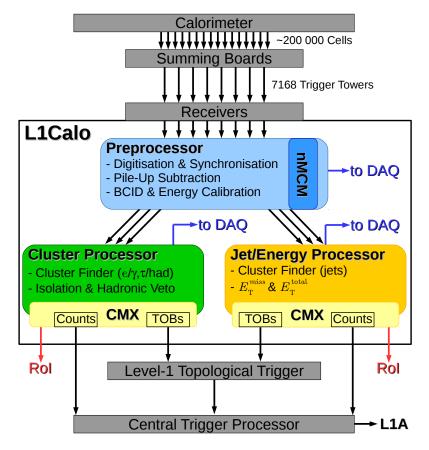

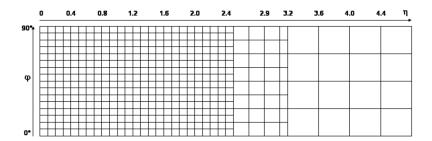

# 4 The ATLAS Level-1 Calorimeter Trigger

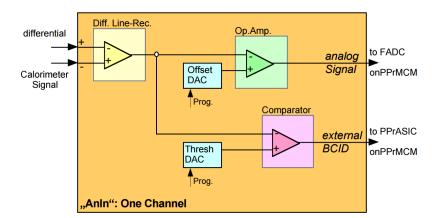

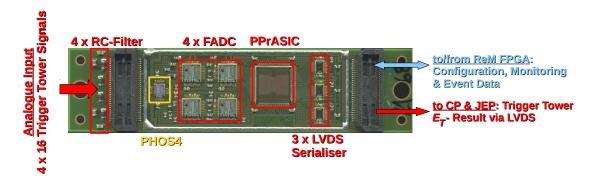

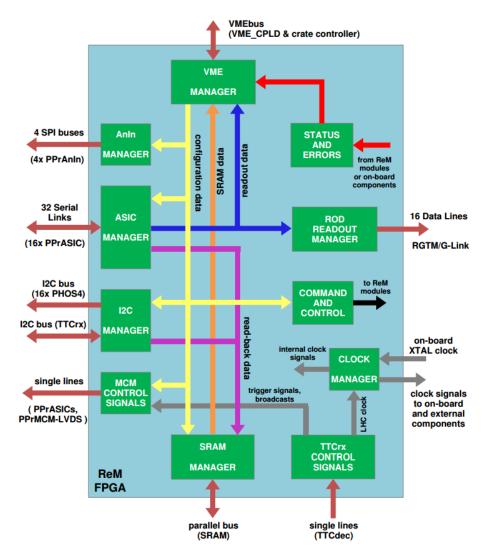

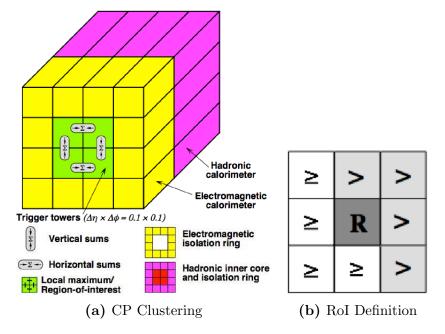

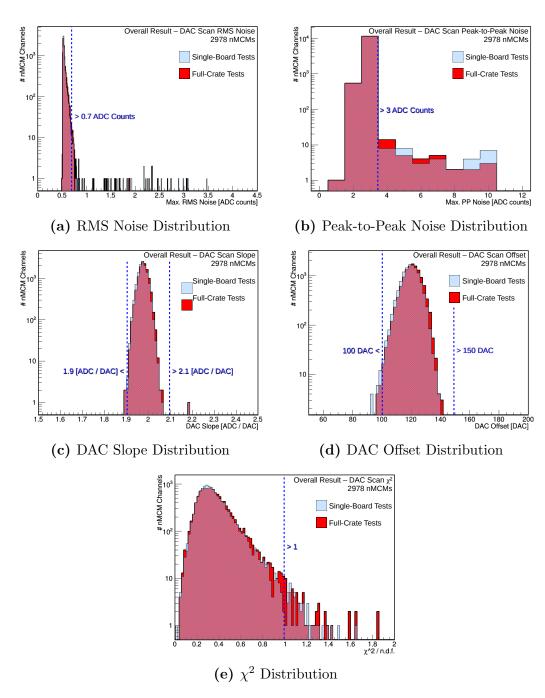

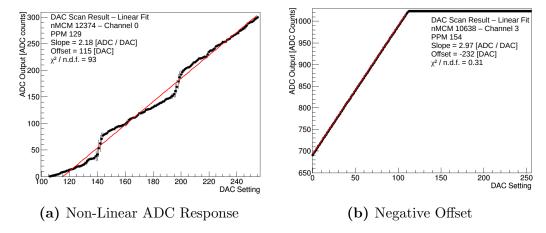

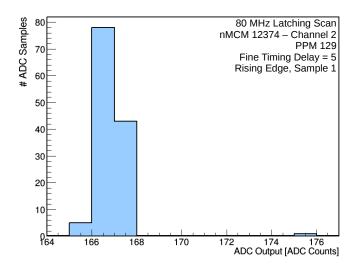

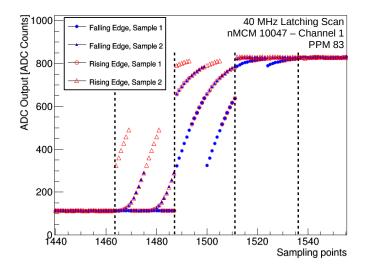

The ATLAS L1Calo trigger [43] is a pipelined, digital system of custom electronics that is operated at 40.08 MHz. It receives analogue input from 7168 trigger towers, each of which is comprised of calorimeter cells in a region of the ATLAS calorimeter, with a typical size of  $(0.1 \times 0.1)$  in  $(\Delta \eta \times \Delta \phi)$ . For each BC, these input signals are analysed to identify candidates for electrons, photons,  $\tau$  particles and jets in the calorimeters, and to compute global energy sums like the missing transverse energy  $E_T^{miss}$  or the total transverse energy  $\sum E_T$ . The identified particle candidates are forwarded to the L1Topo system, and the number of candidates that pass programmable thresholds is transmitted to the CTP.