## Dissertation

submitted to the Combined Faculties of the Natural Sciences and Mathematics of the Ruprecht-Karls-Universität Heidelberg, Germany for the degree of Doctor of Natural Sciences

> presented by Dipl.-Phys. Eric Christian Müller born in Heidelberg, Germany

Date of oral examination: 2014-12-17

## Novel Operation Modes of Accelerated Neuromorphic Hardware

Eric Christian Müller

2014

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Ulrich Brüning

#### Novel Operation Modes of Accelerated Neuromorphic Hardware

The hybrid operation mode relies on a combination of conventional computing resources and a neuromorphic, beyond von Neumann system to perform a joint real-time experiment. The interactive operation mode provides prompt feedback to the user and benefits from high experiment throughput. The performance of a custom transport-layer protocol is evaluated connecting the accelerated neuromorphic system and the computer cluster. Wire-speed performance is achieved between host and eight FPGAs ( $(846.7 \pm 1.2)$  MiB/s, 94% wire speed), and between two hosts using 10-Gigabit Ethernet (> 99%) as well as 40GbE (> 99%) to explore scaling behavior. The software architecture to process neuronal network experiments at high rates is presented including measurements which address the key performance indicators. During hybrid operation, the tight coupling between both resources requires low-latency communication. Using a custom-developed software framework, an average one-way latency between two host computers connected via 10GbE is found to be  $(2.4 \pm 0.2)$  µs and  $(8.5 \pm 0.4)$  µs to the neuromorphic system. A hybrid experiment is designed to demonstrate the hardware infrastructure and software framework. Starting from a conventional neuronal network simulation, the experiment is gradually migrated into a time-continuous experiment which interacts between a host computer and the neuromorphic system in real time. Results of the intermediate steps and the final, hybrid operation are evaluated.

#### Neurartige Betriebsarten beschleunigter neuromorpher Hardware

Der hybride Betriebsmodus beruht auf der Kombination aus konventionellen Rechnern und eines neuromorphen Systems, das nicht auf der von Neumann Architektur beruht, um ein Experiment gemeinsam in Echtzeit durchzuführen. Die interaktive Betriebsart ermöglicht eine schnelle Ergebnisrückmeldung an den Benutzer und profitiert von einem hohen Experimentdurchsatz. Die Leistung eines speziell entwickelten Transportprotokolls, welches das beschleunigte neuromorphe System und den Rechnercluster verbindet, wird evaluiert. Die nominelle Übertragungsgeschwindigkeit wird zwischen Hostrechner und acht FPGAs ( $(846.7 \pm 1.2)$  MiB/s, 94% der Maximalgeschwindigkeit), sowie zwischen zwei Rechnern über 10GbE (> 99%) sowie 40GbE (> 99%) erreicht. Die Softwarearchitektur, die nötig ist um hohe Experimentraten zu erreichen, wird vorgestellt und anhand von Messungen werden die Schlüsselgrößen untersucht. Die enge Kopplung der Resourcen, die der hybride Betrieb benötigt, stellt Anforderungen an die Kommunikationslatenz. Diese wird mittels eines speziellen, selbstentwickelten Softwarepakets gemessen. Für die Interhostlatenz werden  $(2.4 \pm 0.2)$  µs und für die Anbindung des neuromorphen Systems  $(8.5 \pm 0.4)$  µs ermittelt. Ein hybrides Experiment wird entworfen, das als Demonstration der Hard- und Softwareinfrastruktur dient. Beginnend mit einer konventionellen neuronalen Netzwerksimulation wird das Experiment schrittweise in Richtung einer zeitkontinuierlichen Echtzeitinteraktion zwischen Kontrollrechner und neuromorphem System entwickelt. Zwischenschritte sowie das Endresultat werden präsentiert und ausgewertet.

## Contents

| In | trodu | ction                                                                                                   | 13 |

|----|-------|---------------------------------------------------------------------------------------------------------|----|

| 1  | Syst  | em Architecture                                                                                         | 17 |

|    | 1.1   | The Wafer Module                                                                                        | 18 |

|    |       | 1.1.1 Internal Connectivity                                                                             | 18 |

|    |       | 1.1.2 External Connectivity                                                                             | 20 |

|    |       | 1.1.3 The FPGA Communication PCB                                                                        | 21 |

|    |       | 1.1.4 Analog Readout                                                                                    | 23 |

|    |       | 1.1.5 Model and Parameter Domains                                                                       | 23 |

|    |       | 1.1.6 Wafer Module Prototype System                                                                     | 24 |

|    | 1.2   | Cluster Architecture                                                                                    | 24 |

|    |       | 1.2.1 Compute Nodes                                                                                     | 27 |

|    |       | 1.2.2 Storage $\ldots$ | 30 |

|    |       | 1.2.3 Frontend Nodes                                                                                    | 32 |

|    |       | 1.2.4 Software Environment                                                                              | 33 |

|    |       | 1.2.5 Management and Monitoring                                                                         | 33 |

|    | 1.3   | Network Architecture                                                                                    | 33 |

|    | 1.4   | Summary                                                                                                 | 36 |

| 2  | Fast  | Operation                                                                                               | 37 |

|    | 2.1   | Communication Protocols                                                                                 | 37 |

|    |       | 2.1.1 HostARQ                                                                                           | 41 |

|    |       | 2.1.1.1 HostARQ Payload                                                                                 | 48 |

|    |       | 2.1.1.2 Software Implementation                                                                         | 49 |

|    |       | 2.1.1.3 FPGA Implementation                                                                             | 52 |

|    |       | 2.1.2 Performance Measurements                                                                          | 52 |

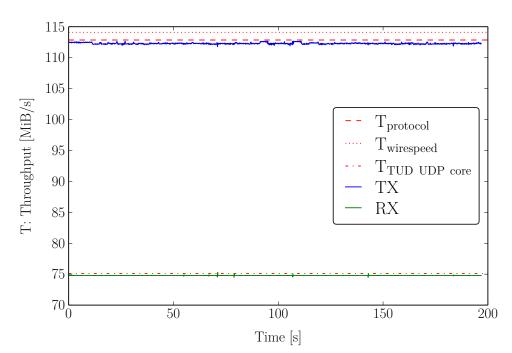

|    |       | 2.1.2.1 Virtex-5 1GbE/UDP Core                                                                          | 56 |

|    |       | 2.1.2.2 Between Host and FCP FPGA                                                                       | 57 |

|    |       | 2.1.2.3 Between Host and Multiple FCP FPGAs                                                             | 62 |

|    |       | 2.1.2.4 Between Host and HICANN                                                                         | 66 |

|    |       | 2.1.2.5 Transport-layer Latency                                                                         | 69 |

|    |       | 2.1.2.6 Inter-host Performance                                                                          | 69 |

|    | 2.2   | Operation Software                                                                                      | 73 |

|    |       | 2.2.1 HALbe                                                                                             | 78 |

|    |       |                | 2.2.1.1 Wafer-global Operations                                                              | 81  |

|----|-------|----------------|----------------------------------------------------------------------------------------------|-----|

|    |       |                | $2.2.1.2  \text{Scheriff}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $  | 83  |

|    |       |                | 2.2.1.3 ESS                                                                                  | 83  |

|    |       |                | $2.2.1.4  \text{SimDenMem}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 83  |

|    |       |                | 2.2.1.5 Real-time Access                                                                     | 84  |

|    |       | 2.2.2          | StHAL                                                                                        | 84  |

|    |       | 2.2.3          | Marocco                                                                                      | 85  |

|    |       | 2.2.4          | PyNN                                                                                         | 85  |

|    |       | 2.2.5          | Connecting Software Pipe-line Components                                                     | 89  |

|    |       | 2.2.6          | Calibration                                                                                  | 92  |

|    |       | 2.2.7          | Automatic Testing                                                                            | 92  |

|    |       | 2.2.8          | BSS Live System                                                                              | 93  |

|    | 2.3   | Resou          | rce Management                                                                               | 94  |

|    |       | 2.3.1          | Measurements using SLURM                                                                     | 98  |

|    |       | 2.3.2          | HBP Unified Platform                                                                         | 99  |

|    | 2.4   | Summ           | nary                                                                                         | 104 |

| 2  |       |                |                                                                                              | 105 |

| 3  | -     | -              | eration                                                                                      | 105 |

|    | 3.1   |                | l-loop Experiments                                                                           |     |

|    | 3.2   |                | Time Closed-loop Operation                                                                   |     |

|    | 3.3   | 3.2.1<br>Handr | Data Exchange                                                                                |     |

|    | ა.ა   | пагау<br>3.3.1 | Latency Requirements                                                                         |     |

|    |       | 3.3.1<br>3.3.2 | Communication Interface                                                                      |     |

|    |       | ə.ə.∠<br>3.3.3 |                                                                                              |     |

|    |       | 3.3.4          | Latency Measurement                                                                          |     |

|    |       | 3.3.4          | NM-PM1                                                                                       |     |

|    |       | 3.3.6          | HMF vs. HICANN Latency                                                                       |     |

|    | 3.4   |                | are Infrastructure                                                                           |     |

|    | 0.1   | 3.4.1          | Comparison to a Standard socket()-based Implementation .                                     |     |

|    | 3.5   | 0              | iment                                                                                        |     |

|    | 0.0   | 3.5.1          | Virtual Environment                                                                          |     |

|    |       | 3.5.2          | Virtual Environment Implementation                                                           |     |

|    |       | 3.5.3          | Software-based Setup                                                                         |     |

|    |       | 3.5.4          | Setup based on HICANN Loopback                                                               |     |

|    |       | 3.5.5          | Real-time Software-based Setup                                                               |     |

|    |       | 3.5.6          | Real-time Setup based on HICANN Loopback                                                     |     |

|    |       | 3.5.7          | Setup using the HMF                                                                          |     |

|    | 3.6   |                | ary                                                                                          |     |

|    |       |                |                                                                                              |     |

| Di | scuss | ion            |                                                                                              | 147 |

|    |       |                |                                                                                              |     |

## Bibliography

## Glossary

| Α | Арр | endix                                                                             | 181 |

|---|-----|-----------------------------------------------------------------------------------|-----|

|   | A.1 | Repositories and Links                                                            | 181 |

|   | A.2 | Cluster & Network Architecture                                                    | 181 |

|   | A.3 | References                                                                        | 182 |

|   | A.4 | Code Listings                                                                     | 184 |

|   | A.5 | ${\it Miscellaneous} \ {\it Measurements} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 191 |

## Acknowledgments

197

### 167

# List of Figures

| 1.1  | Illustration of the HBP NM-PM1 system                                                                                                      | 17 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Schematic of wafer module components                                                                                                       | 19 |

| 1.3  | Image of production-type FPGA communication PCB                                                                                            | 22 |

| 1.4  | Image of HMF cluster and wafer prototype setup                                                                                             | 25 |

| 1.5  | Image of prototype FPGA communication PCB                                                                                                  | 26 |

| 1.6  | Measurements of single-node LINPACK benchmark                                                                                              | 28 |

| 1.7  | Measurements of single-node Graph 500 benchmark                                                                                            | 29 |

| 1.8  | Schematic overview of the data network architecture                                                                                        | 35 |

| 2.1  | Schematic of the NM-PM1 network topology                                                                                                   | 38 |

| 2.2  | Schematic of communication protocol layers                                                                                                 | 40 |

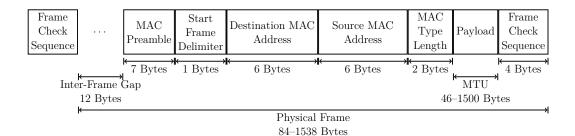

| 2.3  | Frame format of IPv4                                                                                                                       | 41 |

| 2.4  | Frame format of UDP                                                                                                                        | 41 |

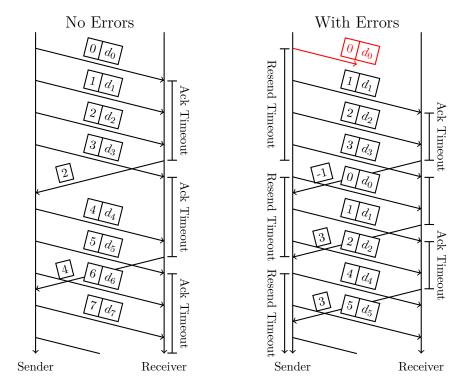

| 2.5  | Schematic of stop-and-wait-type ARQ transmission                                                                                           | 43 |

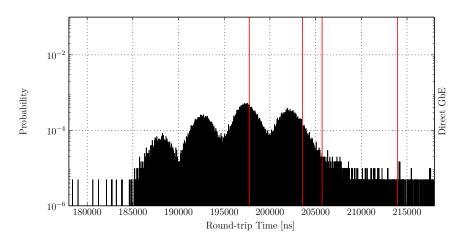

| 2.6  | Measurements of communication latency using GbE                                                                                            | 44 |

| 2.7  | Frame format of Ethernet                                                                                                                   | 44 |

| 2.8  | Schematic of selective-repeat-type ARQ transmission                                                                                        | 46 |

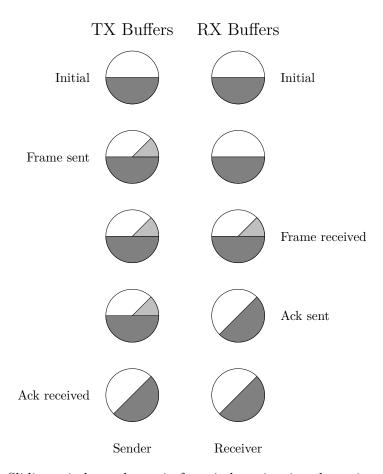

| 2.9  | Schematic of sliding window mechanism using window size 4                                                                                  | 47 |

| 2.10 | Frame format of HostARQ                                                                                                                    | 48 |

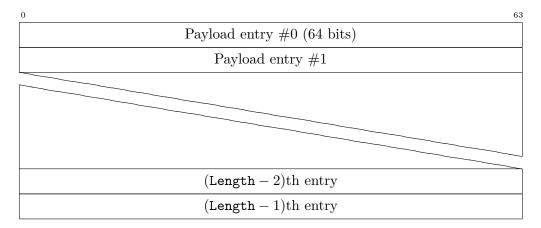

| 2.11 | Frame format of HostARQ payload                                                                                                            | 49 |

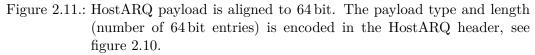

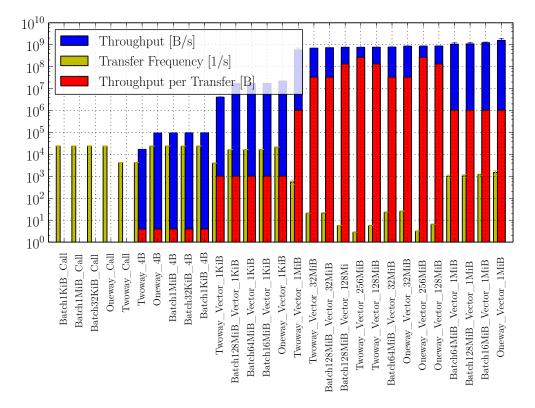

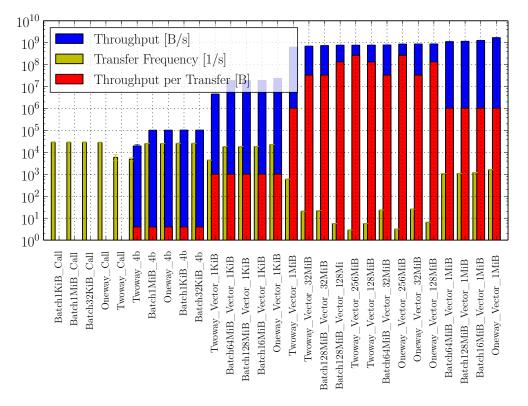

| 2.12 | Measurement of IPC throughput with varying methods                                                                                         | 50 |

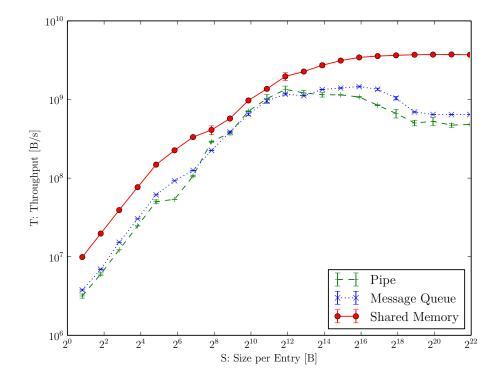

| 2.13 | Schematic of HostARQ software                                                                                                              | 51 |

| 2.14 | Screenshot showing custom Wireshark plugin                                                                                                 | 53 |

| 2.15 | Schematic of HostARQ test setup                                                                                                            | 55 |

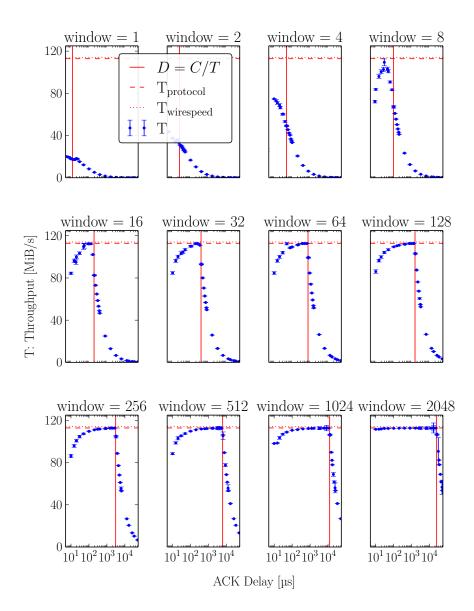

| 2.16 | Measurement of host to FPGA throughput sweeping window size                                                                                | 59 |

| 2.17 | Measurement of host to FPGA throughput sweeping packet size                                                                                | 61 |

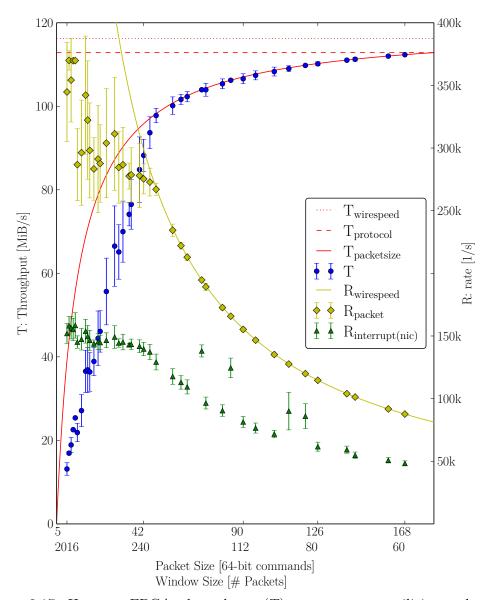

| 2.18 | Measurement of host to FPGA throughput stability (full-duplex)                                                                             | 63 |

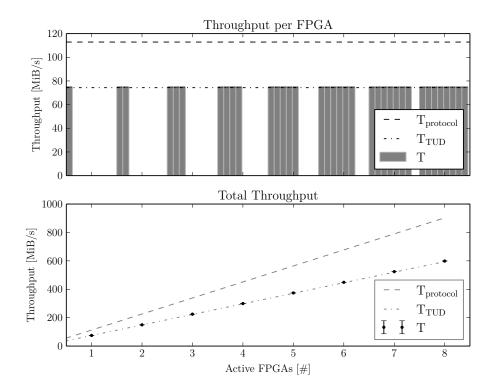

| 2.19 | Measurement of host to multiple FPGAs throughput (full-duplex) .                                                                           | 65 |

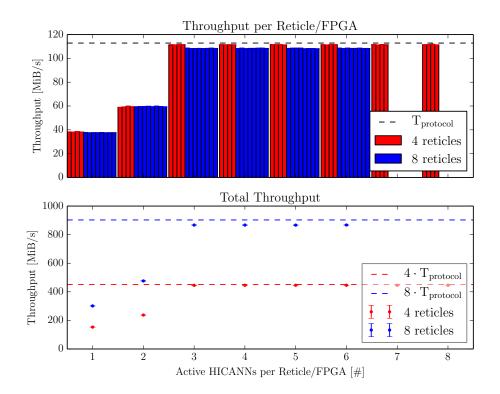

| 2.20 | Measurement of host to multiple HICANNs throughput (half-duplex)                                                                           | 68 |

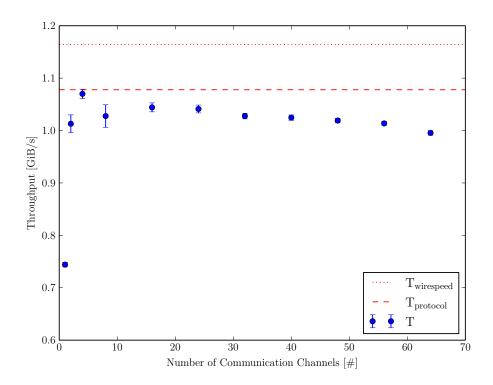

| 2.21 | Measurement of inter-host throughput (10GbE, full-duplex)                                                                                  | 70 |

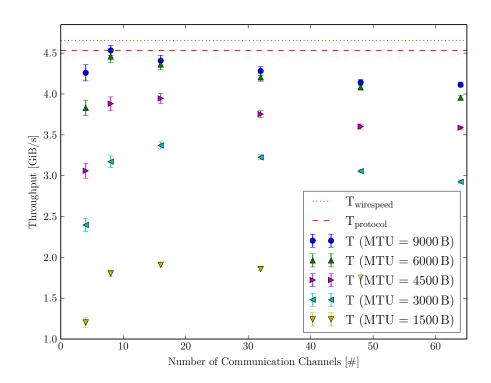

| 2.22 | Measurement of inter-host throughput (40GbE, full-duplex)                                                                                  | 71 |

| 2.23 | Schematic of HMF/NM-PM1 software stack (data-flow-centric) $\ . \ .$                                                                       | 77 |

|      | Schematic of HMF/NM-PM1 software stack (execution-flow-centric)                                                                            | 79 |

|      | Schematic illustrating orchestration of wafer-global operations $% \left[ {{\left[ {{{\left[ {{\left[ {\left[ {{\left[ {{\left[ {{\left[ $ | 82 |

| 2.26 | Schematic illustrating PyNN-supported back ends                                                                                            | 86 |

| 2.27 | Measurement of RCF throughput (boost serialization)                            | 90  |

|------|--------------------------------------------------------------------------------|-----|

| 2.28 | Measurement of PyHMF to mapping input stage throughput                         | 91  |

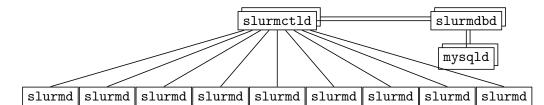

| 2.29 | Overview of SLURM software                                                     | 97  |

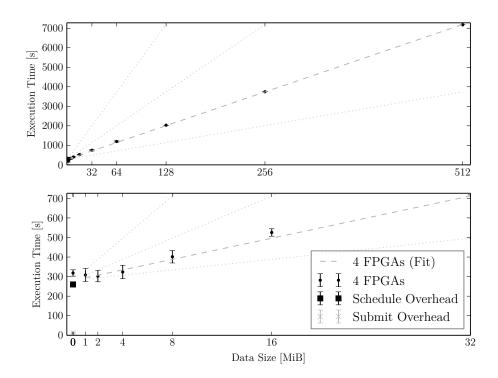

| 2.30 | Measurement of SLURM execution overhead                                        | 100 |

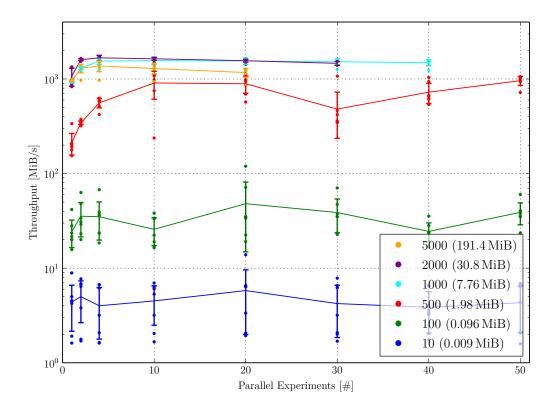

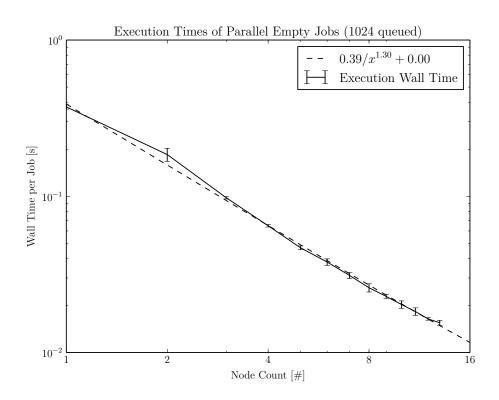

| 2.31 | Measurement of SLURM job throughput (parallel executors)                       | 101 |

| 2.32 | Measurement of SLURM job throughput                                            | 102 |

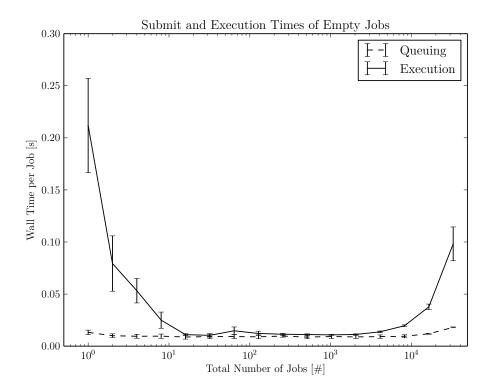

| 2.33 | Schematic of HBP unified portal                                                | 103 |

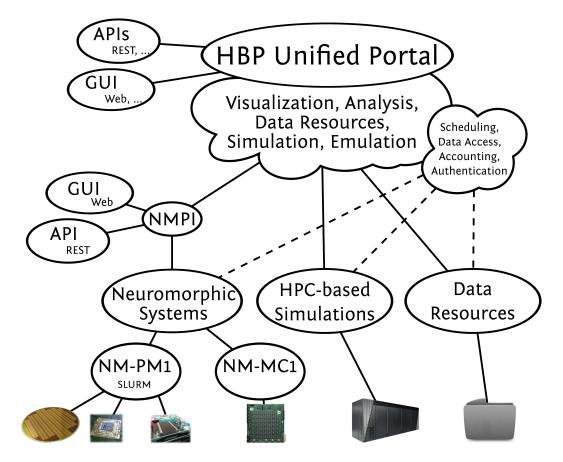

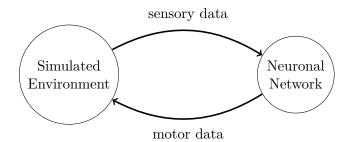

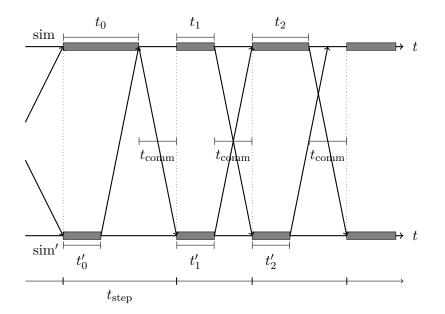

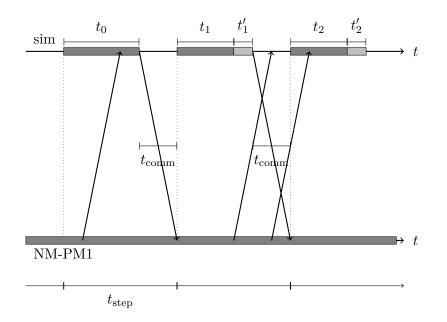

| 3.1  | Schematic of closed-loop experiments                                           | 106 |

| 3.2  | Schematic of conventional closed-loop experiments $\ldots \ldots \ldots$       | 108 |

| 3.3  | Schematic of time-continuous closed-loop experiments $\ldots \ldots \ldots$    | 109 |

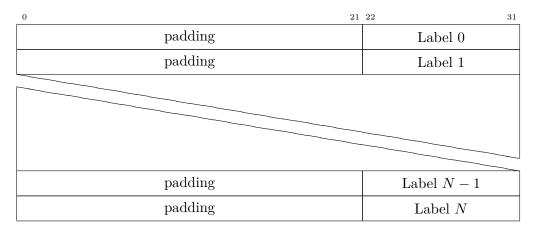

| 3.4  | Frame format of SpiNNaker spike data                                           | 112 |

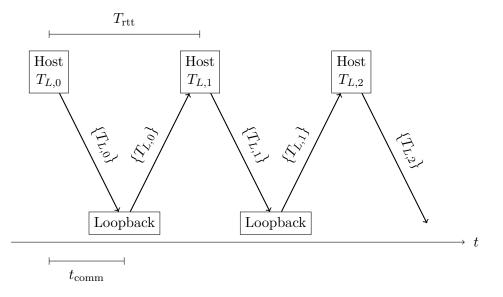

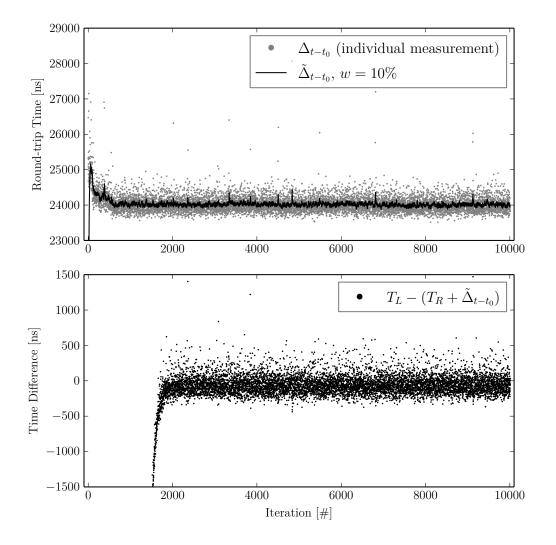

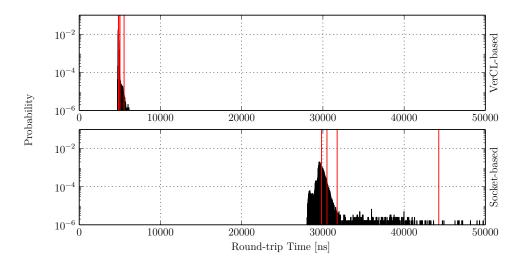

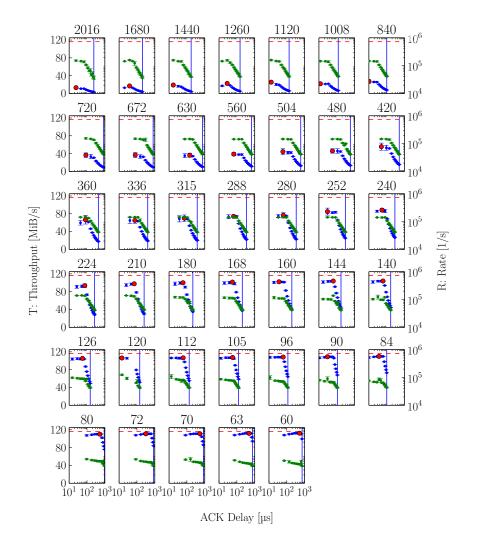

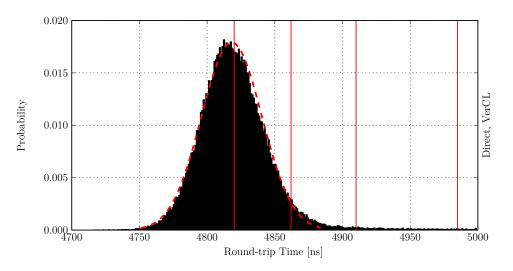

| 3.5  | Measurement of the round-trip time                                             | 113 |

| 3.6  | Measurement of HMF-CP round-trip time                                          | 116 |

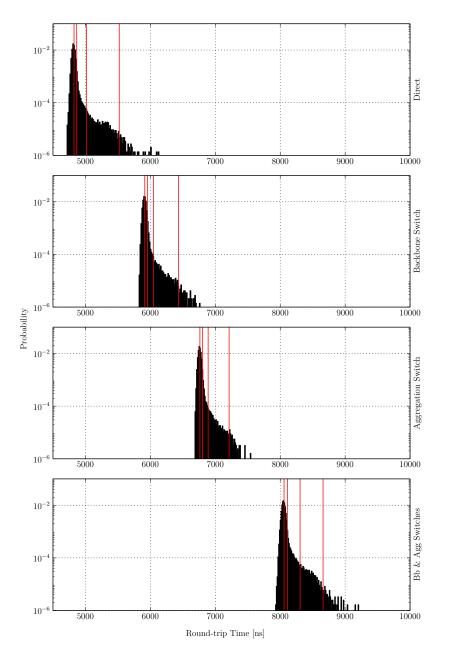

| 3.7  | Measurements of communication inter-node round-trip times $\ldots$ .           | 117 |

| 3.8  | Measurements of communication round-trip time to HICANN chip $% \mathcal{A}$ . | 119 |

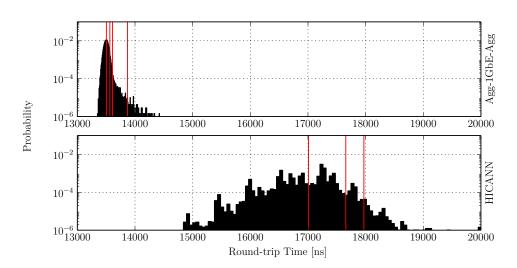

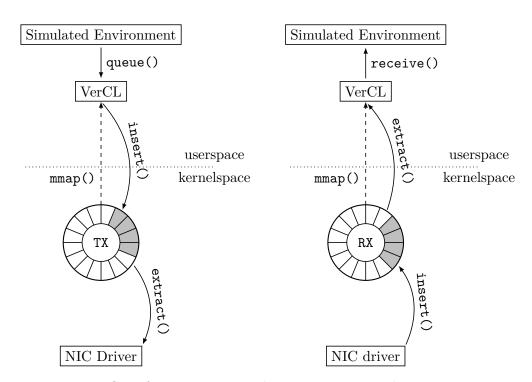

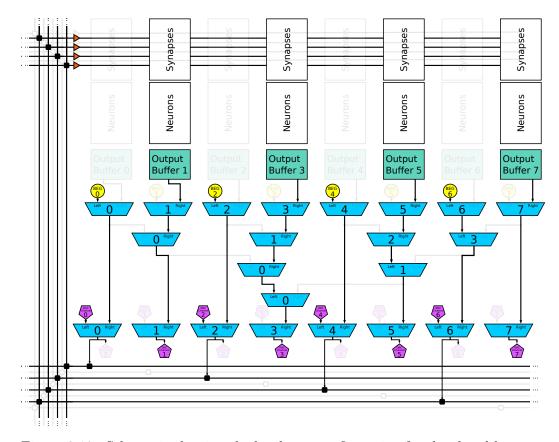

| 3.9  | Overview of VerCL software                                                     | 121 |

| 3.10 | 1 Q                                                                            |     |

|      | 1                                                                              | 122 |

|      |                                                                                | 124 |

|      |                                                                                | 126 |

| 3.13 | Schematic showing software-based closed-loop execution model $\ . \ .$         | 128 |

|      | Simulation of closed-loop experiment using NEST                                |     |

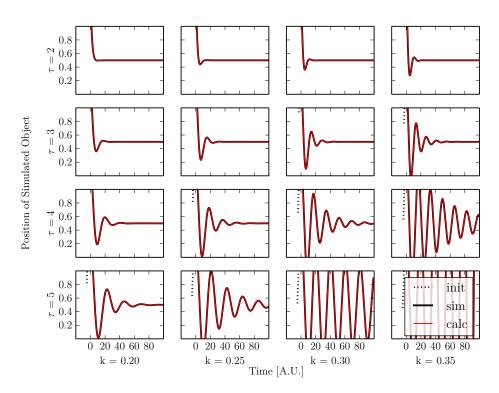

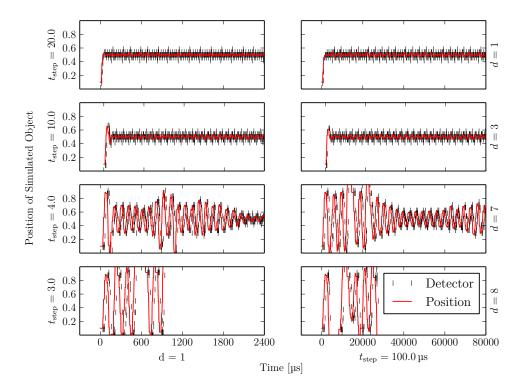

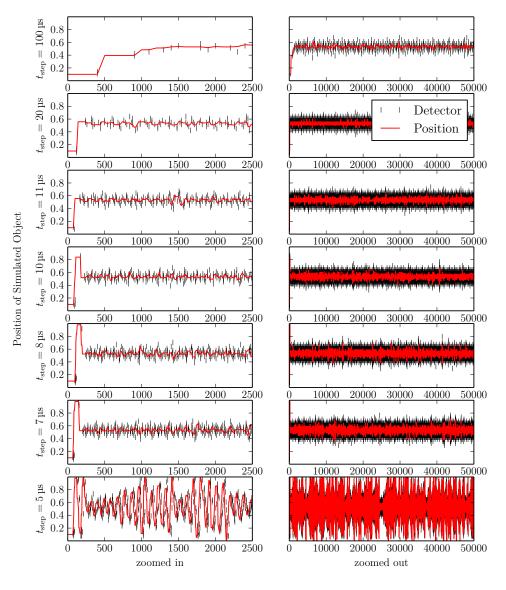

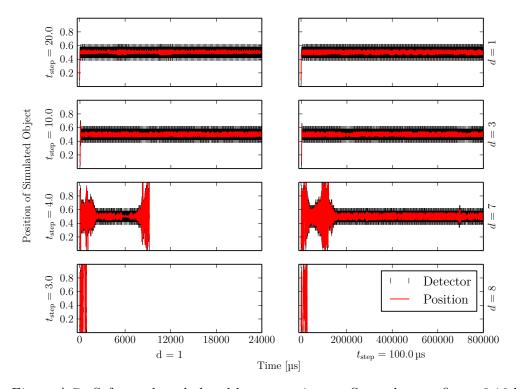

|      | Simulation of custom cLIF implementation                                       | 132 |

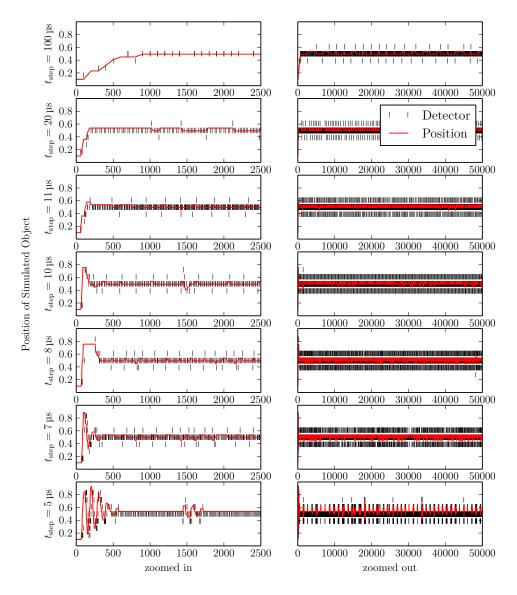

| 3.16 | Measurement of real-time closed-loop experiment using custom cLIF              | 133 |

|      |                                                                                | 135 |

| 3.18 | Measurement of real-time closed-loop experiment using HICANN                   |     |

|      | loop-back mode                                                                 | 137 |

|      | Schematic of hardware configuration for the closed-loop experiment .           | 139 |

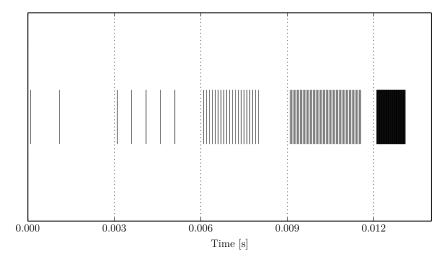

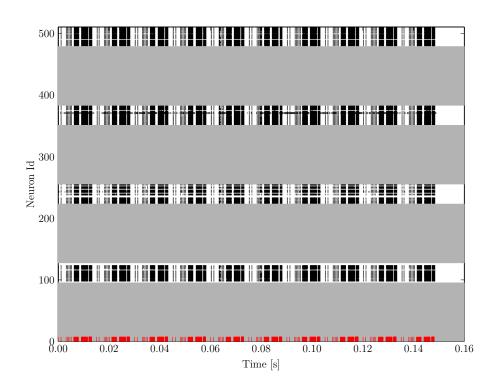

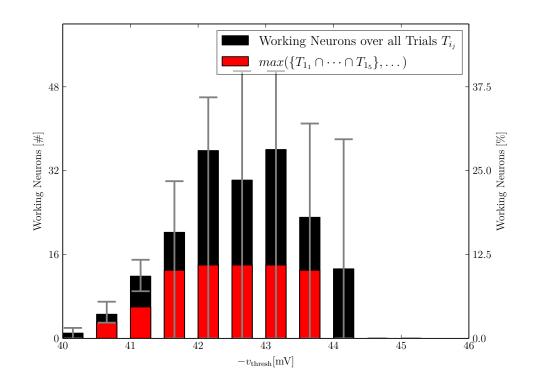

| 3.20 | Schematic showing input spike train for response/gain evaluation $\ . \ .$     | 140 |

| 3.21 | Measurement of neuron response robustness                                      | 142 |

| 3.22 | Measurement of neuron response in relation to varying threshold                |     |

|      | voltage                                                                        | 143 |

| 3.23 | Measurement of real-time closed-loop experiment using hardware                 |     |

|      | neurons on a HICANN chip                                                       | 144 |

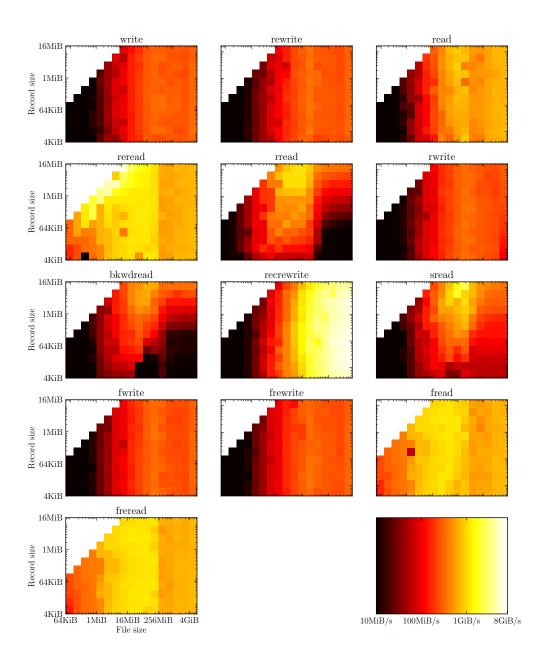

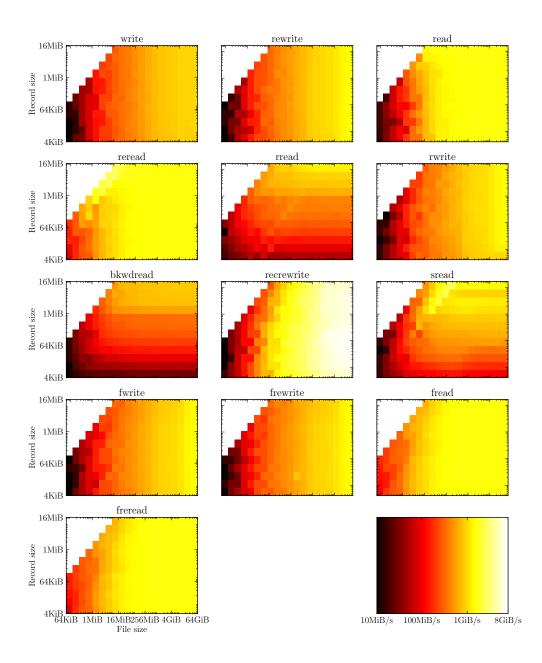

| A.1  | Measurement showing disk performance for the storage node $\ . \ . \ .$        |     |

| A.2  | Measurement showing disk performance for a front-end node $\ldots$ .           |     |

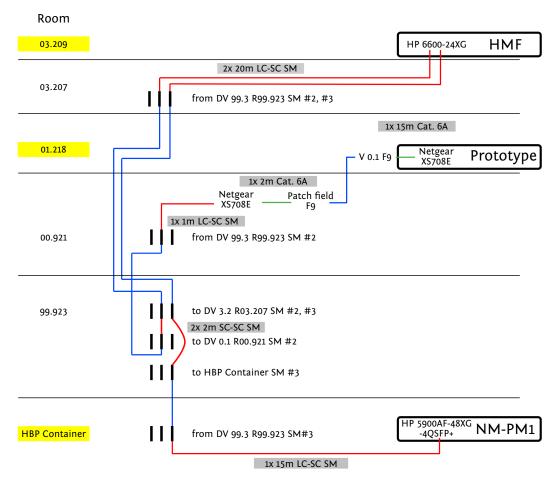

| A.3  | Schematic showing physical connection between BSS and HBP systems              |     |

| A.4  | Measurement of FPGA throughput sweeping packet size (half-duplex)              |     |

| A.5  | Measurement of RCF throughput (internal serialization)                         |     |

| A.6  | Measurement and Gaussian fit of communication latency                          | 193 |

| A.7  | Measurement of real-time closed-loop experiment using custom cLIF              |     |

|      | on HMF-CP (zoomed out)                                                         | 194 |

# List of Tables

| 1.1        | Components of a NM-PM1 compute node                                      |

|------------|--------------------------------------------------------------------------|

| 1.2        | Components of the NM-PM1 storage node                                    |

| 1.3        | Components of a NM-PM1 front-end node                                    |

| 1.4        | Components of the NM-PM1 data network                                    |

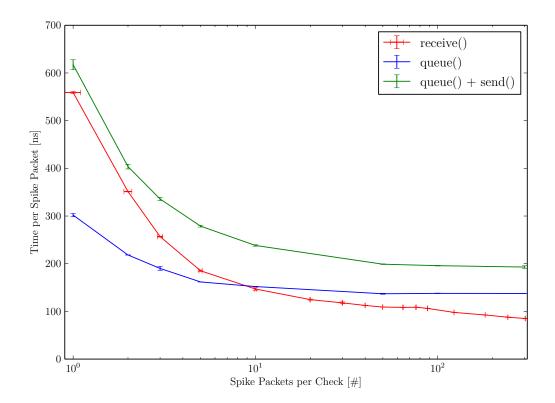

| 3.1        | Measurements of experiment code path components                          |

| A.1        | List of repositories and project links                                   |

| A.2        | Components of a HMF compute node                                         |

| 1 9        |                                                                          |

| A.3        | Reference data for measurement of mapping input stage                    |

|            | Reference data for measurement of mapping input stage                    |

| A.4        |                                                                          |

| A.4<br>A.5 | Reference data for real-time closed-loop experiment using custom cLIF183 |

## Introduction

Understanding the brain is the goal of neuroscience. A commonly used approach in computational neuroscience are software simulations of spiking neuronal networks. Recently, a large-scale simulation<sup>1</sup> – covering one percent of the size of the human brain – was performed on the K computer, a supercomputer<sup>2</sup> which is ranked fourth in the current TOP 500 [2014]. This simulation already reaches three types of technical limitations. Simulating  $O(10^{12})$  synapses exhausts the available memory. The power consumption of such supercomputers is tremendious; the K computer consumes 12.6 MW. Finally, the slow simulation speed – the previously mentioned simulation required 40 min runtime to simulate 1 s, a speed-down of 2400 – limits the number of simulations which can be performed within the assigned maximum computing time.

Yet, there is an alternative to simulation: emulation – neuromorphic hardware systems implementing neurons and synapses emulate the behavior of the biological counterparts. Using mixed-signal VLSI, many neurons and synapses can be assembled on single chips to build neuronal networks. Within the Human Brain Project (HBP), this endeavor is pursued to build multiple interconnected wafer-scale systems, the so-called NM-PM1. The NM-PM1 features almost  $2 \cdot 10^5$  neurons and  $4.4 \cdot 10^7$  synapses per silicon wafer. It implements a leaky integrate-and-fire neuron model enhanced by an exponential term as well as an adaptation term. The synapses are plastic, a long-term learning mechanism is implemented on chip.

However, this approach also faces three limitations. Noise influences analog circuits which induces non-deterministic behavior. Compared to freely programmable software simulations, the configurability of the hardware implementation is limited to a specific model and to certain parameter ranges. Finally, the maximum neuronal network size is limited by the size of the system. The NM-PM1 system consists of twenty wafers, i.e.  $4 \cdot 10^6$  neurons and  $10^9$  synapses which is three orders of magnitude smaller than the simulation mentioned before.

On the other hand, there are clear advantages. The power consumption of neuromorphic systems bridges the gap to biology for the first time. For example, the K supercomputer simulation supported approximately 340 synapses per Watt<sup>3</sup>. In constrast, the NM-PM1 wafer module provides  $440 \cdot 10^6$  synapses per Watt<sup>4</sup>. In these terms, the NM-PM1 is six orders of magnitude more efficient than the K

<sup>&</sup>lt;sup>1</sup>NEST simulation of  $1.73 \cdot 10^9$  neurons with 1 Hz firing rate on average,  $10.4 \cdot 10^{12}$  synapses, 40 min for 1 s simulated time [Eppler, 2014; RIKEN, 2013].

$<sup>^2\</sup>mathrm{LINPACK}\ R_\mathrm{max} = 11\,\mathrm{PFlop/s}$  at  $12.6\,\mathrm{MW}$  power consumption.

$<sup>^3\</sup>mathrm{Power}$  consumption of 12.6 MW, 40 min to simulate  $10^{12}\,\mathrm{synapses}$  for 1 s simulated time.

$<sup>^4\</sup>mathrm{Power}$  consumption of 1 kW, 1 s to simulate  $4.4\cdot10^7\,\mathrm{synapses}$  for 10 000 s emulated time.

#### Introduction

supercomputer.

Secondly, neuromorphic hardware stands for a new computer architecture. In contrast to the conventional von Neumann machines, it inherits properties from biology like fault tolerance and unsupervised learning. This potentially allows for robust and adaptive systems without preprogrammed patterns of behavior.

Finally, the main advantage for the user is the speed of accelerated neuromorphic systems. Compared to the biological time domain, typical large-scale simulations run slower than real-time; the K supercomputer simulation exhibited a speed-down of 2400. In contrast to software simulations, the presented neuromorphic system exhibits a speedup<sup>5</sup> of typically  $10^4$  relative to biology. Due to this highly accelerated operation, a large range of experiment time scales can be explored. On the one hand, large time scales are required for experiments which explore the temporal dynamics of learning (days), development (years) and evolution. On the other hand, parameter sweeps require a large set of short-running experiments; the accelerated operation reduces the overall run time.

However, this hardware feature needs to be conveyed to the user meaning that the support infrastructure needs to be capable of coping with the high emulation speed. Intermediate hardware layers as well as the software stack need to be optimized for this task. The exact requirements depend on the application which can be categorized into three modes of operation.

Neuronal network experiments can be self-contained; that means the individual experiment stimulus is pre-defined and not depending on network output. Such experiments run in larger *batches* or interactively. Both modes benefit from high experiment rates; however, the interactive mode additionally requires a low configureto-result latency to allow for *interactive* updating of the result. For intuition-guided exploration of parameter spaces update rates in the order of 1 Hz, or faster, are required.

Finally, experiments that are not self-contained require some interaction between the neuronal network and the entity which creates the stimulus. This so-called *closed-loop* operation is particularly difficult to achieve on accelerated neuromorphic systems as the speedup increases the visible external reaction delay in the emulation time domain.

The self-contained experiments depend on a fast data flow between the user and the system. The NM-PM1 system provides 1 GiB/s per wafer module. To saturate this bandwidth, multiple requirements have to be met: a fast communication protocol, pipelined software operation, and a software architecture providing efficient data structures. Regarding the closed-loop operation, timing constraints have to be met: a low-latency communication channel that uses low-level operating system methods to provide latencies in the µs range. Lastly, the neuroscientific modeling community can only benefit from this system if user-friendly operation is a matter of course.

Software development does not happen in isolation but in an area of diametral

$<sup>^{5}</sup>$ The time constants can be configured to yield speedups in the range around  $10^{4}$ .

interests. One challenge is the continuous influx of new components enhancing the system. New hardware components always require new software or modifications to existing implementations. Related to the progress of neurocomputational research, the user demands are changing: for example, the user interfaces necessitate continuous development to keep up with the current de-facto standards in computational neuroscience. Other challenges include support for increasingly sophisticated experiments and the integration of external software packages<sup>6</sup>. The Human Brain Project (HBP) aims for a holistic integration of data resources, neuroscientific modeling, data analysis and simulation. A toolkit to bring data providers and users together, with special focus on the aspect of large-scale simulations. In this perspective, the integration of the NM-PM1 system into this toolkit, the so-called *unified portal*, is of primary concern.

## Structure of the Thesis

The thesis at hand is split into three chapters. In the first chapter (chapter 1) the neuromorphic systems are described. Starting with the wafer module, the relevant system components are introduced. Subsequent sections focus on the architecture of the conventional part. Both, the cluster architecture and the data network architecture have been designed by the author. An evaluation of the main properties is provided.

The second chapter (chapter 2) covers efforts to support the typical usage mode of accelerated neuromorphic systems: isolated experiments in quick succession. The figure of merit is the throughput which has two meanings: data throughput (in B/s) and the number of experiments per unit of time.

Finally, the third chapter (chapter 3) concentrates on hybrid operation of the Hybrid Multiscale Facility (HMF). This means the real-time interaction between a conventional software simulation and the neuromorphic hardware. In particular, this mode has requirements regarding communication latencies. The figure of merit has two facets: data communication latency and reaction delay.

Every chapter provides a small summary at the end to collect the essential parts. A final discussion is provided at the end.

## Naming Conventions

This thesis focuses on the neuromorphic hardware systems that have been developed during the BrainScaleS and Human Brain Project projects. The core of the system are the neurons and synapses which are implemented as physical models. In constrast to software *simulations*, the model equations are not numerically solved, but rather *emulated*.

$<sup>^6{\</sup>rm For}$  example, transistor-level simulators to support a common work flow accessing hardware or simulation.

An unique feature of the system is the accelerated operation. That means, the time constants of the model's hardware implementation are smaller when compared to real time. This is called *speedup*.

The ambiguous term *network* is always used in conjunction with *data* to separate its meaning from the *neuronal network*.

**Hardware Components and Abbreviations** The neuromorphic hardware system presented in this thesis is complex. For example, a single Wafer Module comprises over 100 printed circuit boards. This is why only the parts relevant for this thesis have been described; a complete hardware specification is available [HBP SP9 Specification, 2014]. This specification describes the hardware state planned for month 30 of the Human Brain Project (HBP) project. However, the specification will be updated to include later modifications. At the end of this document, a glossary collects all abbreviations used in the text.

**International System of Units** The author adheres to the international system of units. However, in computer science the base-2 notation for units of digital information is popular. To resolve this issue, a set of binary prefixes has been defined by the International Electrotechnical Commission (IEC). The standard SI prefixes are modified by appending *i* to indicate base-2 notation. For example, the author uses  $2^{10} B = 1024 B = 1 \text{ KiB} - \text{the } i$  in kB denotes the non-SI prefix (called *kibi*, i.e. kilo-binary, instead of *kilo*). The same is true for MiB, GiB, and TiB. All data sizes stated without *i* indicate SI-sizes, e.g.,  $1 \text{ MB} = 10^6 \text{ B}$ .

### **Supervised Work**

The author coordinated and supervised the work of Moritz Schilling, Vitali Karasenko, Kai Husmann and David Hinrichs. During his diploma thesis, Moritz Schilling worked on the HostARQ protocol (HostARQ) software implementation presented in section 2.1.1.2. Vitali Karasenko worked on the FPGA implementation of the HICANN-ARQ protocol and HostARQ protocol presented in section 2.1.1.3 and section 2.1.1.3. He performed preparatory work in his bachelor thesis, and implemented both components in his master thesis. Two more bachelors worked on the software stack: Kai Husmann evaluated a key component of the pipelined software architecture presented in section 2.2.5. David Hinrichs worked on the integration of a transistor-level simulation into the software flow presented in section 2.2.1.4.

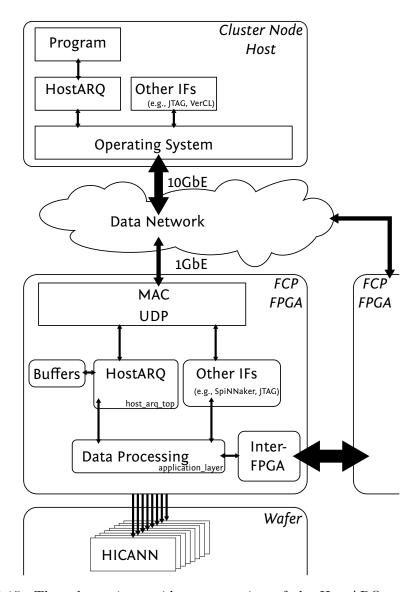

This chapter describes hardware components of the Hybrid Multiscale Facility (HMF) and NM-PM1 systems which are relevant for this thesis. In the first section the neuromorphic part is described. The conventional part – which has been designed by the author – is described in the remaining sections. A complete hardware specification can be found in HBP SP9 Specification [2014].

Figure 1.1 presents an illustration of the Human Brain Project (HBP) NM-PM1 system. At the time of writing, the compute cluster and some parts of the data network have already been installed.

Figure 1.1.: Illustration of the HBP NM-PM1 system. The neuromorphic part is distributed over five racks containing four wafer modules each. A 20node compute cluster including one storage server as well as two frontend nodes is located in the fourth rack (from the left); in the rendering, the compute nodes are located in the fifth cabinet. Communication between the individual wafer modules and compute nodes relies on multiple Gigabit Ethernet links that are aggregated to 10-Gigabit Ethernet. A backbone switch located on top of the compute cluster interconnects the compute nodes, the wafer switches and provides an uplink to the institute. Image by Dan Husmann.

## 1.1. The Wafer Module

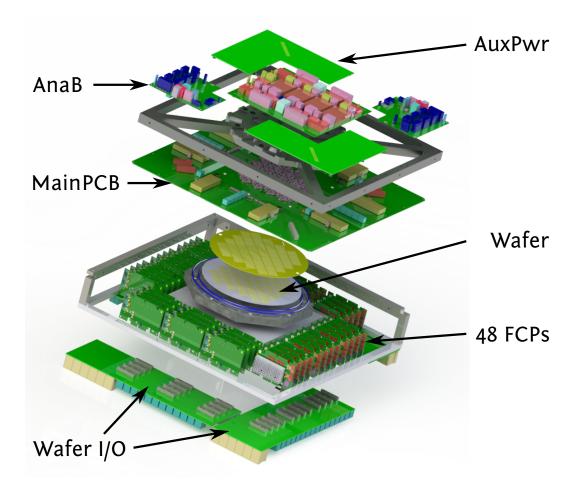

The core of the HMF and NM-PM1 system is the neuromorphic part; its design started during the FACETS project. This *neuromorphic* unit, the so-called Wafer Module, contains a 20 cm wafer produced in a standard 180 nm CMOS process technology. On a single wafer are 48 groups, the so-called *reticles*, of eight HICANN (high-input count analog neuronal network) chips each – 384 HICANN chips in total. In contrast to typical fabrication, the wafer is not cut into many dice but stays complete; an interconnection step during post-processing provides on-wafer connectivity between the reticles. This explains why the system carries the attribute wafer-scale. One HICANN chip provides up to 512 neurons and 224 synapses. This results in approximately  $2 \cdot 10^5$  neurons and  $4.4 \cdot 10^7$  synapses per wafer. Neurons are emulated by an analog circuit that implements the adaptive exponential integrateand-fire neuron model [Brette and Gerstner, 2005]. Up to 64 neuron circuits can be combined to form a single neuron supporting more than 224 synapses. By combining 64 neuron circuits a total number of 14336 synapses can be used. Figure 1.2 presents a schematic, exploded view of a single wafer module. A single wafer module consists of multiple parts. These are support electronics for power monitoring and control as well as the FPGA-based<sup>1</sup> communication printed circuit boards  $(PCBs)^2$ , the so-called FPGA communication PCBs (FCPs). The latter provides inter-wafer and host connectivity. Associated with a single wafer module are two more types of components: power control is performed by power management units (PMUs), and the analog readout modules (AnaRMs) offer analog recording capabilities. All AnaRMs modules of four wafer modules, i.e. a rack, get aggregated by one analog readout module aggregator node (AnaRMAN).

#### 1.1.1. Internal Connectivity

A wafer comprises many identical HICANN chips. During fabrication, the stepand-repeat method cycles through all possible positions and replicates the same physical structures, i.e. groups of eight HICANN chips or reticles, onto the wafer. A later post-processing step adds connections between the otherwise unconnected reticles. These connections are used for a bus network, the so-called Layer 1 (L1) network, providing on-wafer spike-event transport. All HICANN chips of one row or column share 256 *vertical* and 64 *horizontal* buses. Two buses can be interconnected at specific connection points using so-called crossbar switches. However, not every switch position is physically available because the presence of the switch itself increases the parasitic capacity of the bus lane up to a point where successful data transmission is no longer possible. For a detailed description of the bus system see HBP SP9 Specification [2014]. The specified bus event<sup>3</sup> rate at maximum clock

<sup>&</sup>lt;sup>1</sup>field-programmable gate array (FPGA)

<sup>&</sup>lt;sup>2</sup>printed circuit board (PCB)

<sup>&</sup>lt;sup>3</sup>The raw symbol rate is R = 2 Gbit/s, events are encoded using 6 bits plus start and stop bit. After every frame a pause of the same length is inserted.

Figure 1.2.: A single wafer module consists of many components. Core of the wafer module is the wafer which carries neurons, synapses and the on-wafer communication bus. It is located at the center of the hardware stack. Multiple printed circuit boards (PCBs) provide connectivity and power to the wafer; one module comprises approximately 100 PCBs. Links for external communication are provided by the PCBs at the bottom, the I/O boards (wafer I/O PCB). Associated with one wafer module are three analog readout modules for analog recordings, one power management unit and one compute node to control the system. Figure 1.3 presents the FCPs in detail. Hardware details regarding Analog Breakout PCB (AnaB) and Auxiliary Power Supply PCB (AuxPwr) and all other components can be found in HBP SP9 Specification [2014]. Image by Dan Husmann.

frequency (250 MHz) is 125 MEvent/s [Schemmel et al., 2010]. Hence, the bisection bandwidth<sup>4</sup> of a HICANN chip can be calculated as follows:

$$(N_{\text{horizontal}} + N_{\text{vertical}}) \cdot R_{\text{ev}} = (256 + 64) \cdot 125 \,\text{MEvent/s} = 40 \,\text{GEvent/s}$$

(1.1)

However, a single HICANN chip can only inject events on eight horizontal buses. The sending bandwidth is given by:

$$N_{\text{sending}} \cdot R_{\text{ev}} = 8 \cdot 125 \,\text{MEvent/s} = 1 \,\text{GEvent/s}$$

(1.2)

At the time of writing, the chip is operated at a reduced clock frequency of  $100 \text{ MHz}^5$ ; the L1 event rates are reduce by the same factor (2/5).

#### 1.1.2. External Connectivity

To inject and extract spike stimuluses into the on-wafer neuronal network the HI-CANN chip provides another communication layer, the so-called Layer 2 (L2) protocol. In contrast to the time-continuous L1 bus network, the L2 link uses additional time stamps to encode spike times. Optimally packed events can be encoded using 32 + 4 bit<sup>6</sup>. A full-duplex connection between every HICANN chip and the associated FCP field-programmable gate array (FPGA) operates at  $R_{\rm symbol} = 2$  Gbit/s [Schemmel et al., 2010].

Thus, the external event rate of a HICANN chip is:

$$R_{\text{event}} = R_{\text{symbol}}/\operatorname{sizeof}(\text{Event}) = \frac{2 \operatorname{Gbit/s}}{36 \operatorname{bit}} = 55.6 \operatorname{MEvent/s}$$

(1.3)

The total (half-duplex) off-wafer bandwidth:

$$N_{\rm HICANN} \cdot R_{\rm symbol} = 384 \cdot 2 \,\rm Gbit/s = 96 \,\rm GB/s \tag{1.4}$$

The corresponding event rate is:

$$N_{\rm HICANN} \cdot R_{\rm event} = 384 \cdot 55.6 \,\, {\rm MEvent/s} = 21.3 \,\, {\rm GEvent/s} \tag{1.5}$$

The links are capable of operating full duplex. Hence, the full-duplex bandwidth and rates are twice as large.

<sup>&</sup>lt;sup>4</sup>When the chip is split into two equally-sized parts, this is the bandwidth between the two parts. <sup>5</sup>The reduced clock frequency provides more robust on-wafer, i.e L1, communication; higher clock speeds require further tuning of L1 parameters.

<sup>&</sup>lt;sup>6</sup>A double-spike packet requires 48 bit; header and cyclic redundancy check (CRC) consume additional 16 bit. After every packet, a 8 bit pause is required. That means two spikes can be transmitted every 72 bit cycles.

The L2 protocol does not only support spike-event communication but also configuration data. A chip-internal communication bus-structure (not to be confused with the on-wafer spike network) exposes addressable memory to the FCP FPGAs. Due to the non-reliable L2 (i.e. the link does not feature a transport protocol), a dedicated transport layer protocol, the so-called HICANN-ARQ protocol, provides reliability in case of data corruption or packet loss. Configuration data is encoded using 64 bit each; hence, the packet rates are reduced by a factor of approximately two.

In the FCP FPGA, upstream data can be routed to other FCPs via the interwafer connections. Alternatively, it can be routed to the host. The latter introduces a bottleneck in terms of bandwidth as the host link is based on Gigabit Ethernet (1GbE). This means that eight HICANN chips share a 1 Gbit/s host connection. The Gigabit Ethernet (1GbE) links are capable of full-duplex communication, i.e. the same is true for the reverse communication path. Section 1.1.3 provides details regarding the FPGA communication PCB.

The host link uses a 32 bit encoding for a single spike. A optimally packed spike data frame contains 182 double spikes (i.e. 364 spikes per packet). Using equations (2.3) and (2.4), we can calculate the maximum spike throughput using the host link.

$$R_{\rm spike} = \text{Throughput}_{\rm payload}/sizeof(\text{Spike}) = \frac{947.9 \,\text{Mbit/s}}{32 \,\text{bit}}$$

(1.6)

= 29.6 MEvent/s

As stated in the previous section, the chip is currently operated at a reduced clock frequency; the calculated L2 speeds are reduced by the same factor. Notably, the FCP FPGA itself is not affected and the inter-FPGA or host links maintain their speeds.

#### 1.1.3. The FPGA Communication PCB

From the users' point of view, the FPGA communication PCB (FCP) are responsible for almost all tasks related to experiments: 1. processes configuration data describing neuronal network topology and neuron model parameters; 2. recording of spike data and stimulation with spike data; 3. real-time spike data transport; 4. and runtime control. Figure 1.3 shows a FPGA communication PCB which will be used in the production-type HMF and NM-PM1 wafer modules.

The FCP carries 1.25 GiB DRAM. 256 MiB of the total memory are available for buffering Ethernet-based host communication. The remaining 1 GiB is used for buffering experiment input and output data. To a large part, this memory is occupied by input and output spike data as a single wafer configuration only requires approximately 50 MiB. Due to constraints regarding data alignment, the memory consumption in DRAM is larger, approximately 100 MiB distributed over all FCPs.

Figure 1.3.: FPGA communication PCB (FCP) used in the production-type HMF and NM-PM1 systems. The bottom connector is plugged into the Main-PCB. Host connectivity is provided by four wafer I/O PCBs (two horizontal and two vertical versions) that combine 12 FCPs each. Every FCP carries 1 GiB DRAM for spike data and 256 MB for communication buffers. For details see HBP SP9 Specification [2014].

Hence, the memory consumption per FCP is only 2 MiB and the remaining memory can be used for spike data or buffering/pipelining of experiments.

In general, experiments can be categorized as being *non-interactive*/batch-style or *real-time*. The former describes experiments where external stimulus has been pre-calculated – i.e. the input does not depend on the neuronal network response – and the stimulus is *played back* to the system. This operation mode benefits from the real-time capabilities of FPGAs; the FPGA can provide fixed timings that allow for cycle-precise real-time playback and recording of data. Experiments that interact with a software in real-time are covered in chapter 3. The conventional use case, i.e. batch-style usage, is covered in chapter 2.

A complete wafer module comprises 384 HICANN chips that are grouped into 48 reticles; every reticle is governed by one dedicated FCP. These 48 FCPs are located between MainPCB and four wafer I/O PCBs (WIOs) that carry external connectors. Twelve 1GbE links and 48 inter-wafer links are located on every WIO.

Every FCP can be used individually. Networks involving multiple reticles require synchronized interaction between multiple FCP FPGAs. In particular, synchronized clocks are essential to avoid any drift which would yield desynchronized playback and recording of spike data. The NM-PM1 system implements this synchronization using a common clock source.

**Gigabit Ethernet** During the FACETS project, the importance of a reasonably fast and conveniently usable host interface was identified. At that time, 1GbE was state of the art and fulfilled the requirements: it supports 1 Gbit/s = 125 MB/s = 119.2 MiB/s wire speed, it is supported by standard FPGA chips, the physical

connection technology (using twisted pair cat. 5 or 6 cables) is cheap and easily deployable, networking hardware for all use cases and scales is commercially available, and good software support is available. Based on the experiences of the FACETS Stage 1 system [Gutmann, 2007; Schilling, 2010], the HMF and NM-PM1 use Gigabit Ethernet as default data network technology. To ensure fast and reliable communication between FCP and host computer, a transport layer implementation has been developed by the author (see section 2.1).

#### 1.1.4. Analog Readout

Eight HICANN chips, i.e. one reticle, share two analog output channels. This yields 96 channels per wafer module. These channels are fed to analog readout modules that can be used for recording of analog neuron membrane traces. One 19-inch rack contains four wafer modules and twelve AnaRMs connected to one analog readout module aggregator node. Each AnaRM provides a 12 bit analog-to-digital converter (ADC) sampling at 125 MHz. Recording and readout are controlled by an on-board Xilinx Spartan-6 FPGA that is connected via USB 2.0 to a host computer. The traces are buffered in local 512 MiB-DRAM memory. At full sampling rate, this provides a maximal recording time of 2.7 s real time<sup>7</sup>. Conversion to 1GbE is performed by one AnaRMAN per rack; i.e. twelve AnaRMs share a single 1GbE uplink. This protocol conversion is performed for a number of reasons: 1. to allow for a non-static assignment between AnaRMs and compute nodes. 2. to circumvent the maximum physical cable length of USB 2.0; 3. reduce load on control nodes – on the current compute nodes USB 2.0 transfers are computationally more expensive than 1GbE-based communication.

The author suggests to switch from the USB 2.0-based to a 1GbE-based interface as it would not only increase the throughput but also allow to omit the AnaRMAN which, in turn, reduces complexity and increases robustness.

#### 1.1.5. Model and Parameter Domains

The neuron circuits of the HICANN chip implement the adaptive exponential integrate-and-fire (AdEx) neuron model [Millner, 2012]. Model dynamics are presented in Naud et al. [2008], an evaluation of the present hardware implementation can be found in Millner [2012]; Schwartz [2013]. Compared to the leaky integrate-and-fire model, the AdEx model adds two more variables that allow for many known electrophysiological spike patterns; the LIF model supports only a single firing mode, i.e. regular spiking.

**Speed-Up** The analog neuron circuit is a physical implementation of the corresponding adaptive exponential integrate-and-fire (AdEx) model. In contrast to a step-wise simulation, neuron model dynamics are emulated in continuous time. Neuron (and synapse) model parameters are translated into the hardware domain.

<sup>&</sup>lt;sup>7</sup>Assuming a speed-up factor of  $10^4$ , this corresponds to 7.6 h.

In particular, the hardware time constants of the NM-PM1 and HMF are typically  $10^4$  to  $10^5$  times faster compared to biological real time; i.e. biological time is compressed by this *speed-up* factor. The precise speed-up factor depends on the neuron and synapse parameter set. Typically, the membrane time constant is used as a reference.

**Parameter Space** The total parameter space is dominated by synapse data:  $512 \cdot 224$  synapses per HICANN chip store 4 bit weight and 4 bit address data, 112 KiB in total. Neuron-model-specific data<sup>8</sup> accounts for approximately 12% of the total memory [Brüderle et al., 2011]. Thus, the total wafer parameter space is approximately 50 MiB.

#### 1.1.6. Wafer Module Prototype System

At the time of writing, the *production-type*<sup>9</sup> wafer module systems were not yet available. All measurements that interacted with any part of the neuromorphic system relied on the prototype setup shown in figure 1.4.

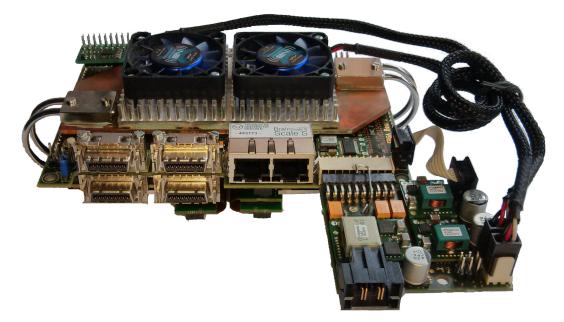

There are some differences between the prototype wafer module and the final HMF or NM-PM1 wafer modules. The main difference is the new MainPCB which increases the number of FCPs from twelve to 48. I.e. the prototype system uses twelve Xilinx Virtex-5 FPGA-based boards (below blue fans in figure 1.4, details in figure 1.5) each controlling four reticles; the production-type systems will use 48 Xilinx Kintex-7 FPGA-based PCBs each controlling a single reticle. Hence, the maximum host bandwidth will be increased by a factor of four. Figure 1.5 shows a picture of the FCP used in the prototype system.

Changes that do not directly affect the usage of the system are: 1. the power management unit will be based on Raspberry Pi replacing an embedded ARM evaluation board; 2. the lab power supplies will be replaced by custom-built supplies based on 48 V DC power supply units (PSUs); 3. the power monitoring and control is improved.

## **1.2. Cluster Architecture**

The properties of the previously described neuromorphic system are unique. In particular, its emulation speed (cf. section 1.1.5) allows for new types of experiments and use cases. Long-term learning experiments can easily cover multiple days in simulated time which translates to only several seconds of real time. Hence, longrunning experiments directly benefit from speedup factor. In contrast, parameter sweeps are typically short but require many runs; this requires an efficient reconfiguration mechanism. Given the large emulation speedup of  $10^4$ , the perceived or real

<sup>&</sup>lt;sup>8</sup>24 analog parameter entries per neuron account for 12288 entries; the specified precision is 10 bit, i.e. 15 KiB per HICANN chip.

<sup>&</sup>lt;sup>9</sup>Production-type system refers to the system as specified in HBP SP9 Specification [2014].

Figure 1.4.: Photograph of the first wafer prototype setup (right) together with the HMF compute cluster (left). All measurements using any part of the wafer module have been performed on this prototype. For a description of the differences between *production-type* and prototype wafer module see section 1.1.6. Details on the non-neuromorphic (or conventional) part, i.e. compute cluster and data network, can be found in sections 1.2 and 1.3.

Figure 1.5.: FPGA communication PCB used in the prototype system. To provide adequate cooling, the FPGA is covered by an heat sink and two fans. Host connectivity is provided by the two centrally located 8P8C jacks (often called RJ45) using 1GbE. On the left side there are four Infiniband-type/CX4 connectors designated for inter-FPGA connectivity. The wafer *connectors* can be vaguely seen (marked by arrows) on the bottom of the PCB just below the right CX4 and the left 8P8C jack. In the lower-right a small PCB acts as a power supply.

speedup is typically not dominated by the emulation time but rather by overhead. Optimizing the over-all speedup is one main topic of this thesis.

The overhead can be examined in the different experiment execution stages: 1. processing of experiment descriptions to compute valid hardware configurations, 2. experiment preparation, 3. hardware configuration, 4. and experiment readout. All overhead categories can be optimized by improving software or hardware. The former – creating a high-performance software stack – is covered in chapters 2 and 3; the latter will be addressed for the conventional hardware parts in the following sections. In particular, the compute node and data network architectures, the conventional part, of both, the HMF and the NM-PM1 systems, was designed by the author.

#### 1.2.1. Compute Nodes

During all experiment phases – configuration, execution, and read-out phase –, a single compute node handles a single wafer, i.e. up to  $48 \times 1$ GbE data streams<sup>10</sup>. To achieve acceptable performance within the financial budget, central processing units (CPUs) designed for server operation are avoided. At the time of writing, the Intel<sup>®</sup> Core<sup>TM</sup> i7-4771 CPU offers state-of-the-art single-thread performance at reasonable cost. Per CPU a LINPACK benchmark<sup>11</sup> performance of approximately 180 GFlops can be reached (see figure 1.6).

Certainly, floating point performance is not a key performance indicator for most layers in the software hierarchy of the HMF or NM-PM1: most software layers involve data intensive tasks. In particular, the computationally most expensive task is the mapping step which translates a neuronal network description to a hardware configuration. This task is more similar to the Graph 500<sup>12</sup> benchmark.

For large-scale mapping jobs it is planned to make use of high-performance computing (HPC) sites that are available within the Human Brain Project. Main task of the compute nodes is experiment control – a programmatically linear task. Assuming a fixed budget, high-clocked *desktop* CPUs are adequate for this job.

Another major requirement is high throughput: the wafer module provides 48 parallel 1GbE links for host communication. At the time of writing, networking interfaces providing 10-Gigabit Ethernet (10GbE) links are state of the art. Concerning the host interface, 40-Gigabit Ethernet (40GbE) is budget-wise in reach, but the remaining network equipment, especially switches, is disproportionately more expensive. See section 1.3 for details on the data network.

For a certain neuronal network experiment class low-latency links are essential. This experiment category relies on a real-time interaction between neuromorphic hardware and host computers. Due to the combination of the conventional computer architecture and the non-von Neumann, neuromorphic architecture, this is

$<sup>^{10}\</sup>mathrm{That}$  is one full-duplex data stream per FCP.

$<sup>^{11}\</sup>mathrm{A}$  benchmark that measures floating point performance [Dongarra, 1988].

<sup>&</sup>lt;sup>12</sup>Supercomputer list based on a benchmark which focuses on data-intensive loads [Murphy et al., 2010].

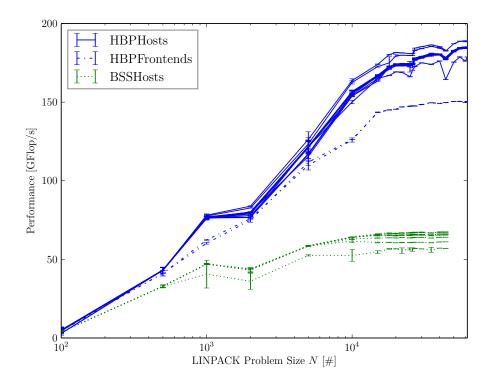

Figure 1.6.: Measurements of single-node LINPACK benchmark runs. The LIN-PACK problem size N is varied up to machine memory limits (i.e. 16 GiB for the HMF, 32 GiB for the NM-PM1 cluster). Floating point performance is plotted on the ordinate. The NM-PM1 cluster nodes are labeled HBPHosts and HMF nodes as BSSHosts. In addition, two NM-PM1 front-end nodes are tested; The quad-core NM-PM1 compute nodes achieve over 180 GFlop/s. In contrast to the hexa-core front-end nodes, the compute node support the AVX2 instruction set which allows for a doubled floating point peak performance per core. The HMF compute nodes are multiple CPU generations older and do not support advanced vector instructions at all. This reduces the percore performance significantly. The errorbars denote the RMSE out of four runs. All hosts use dynamic clock rate adaptation depending on CPU's current thermal budget and power consumption. That means, large errors typically indicate temperature fluctuations. In particular, the runtime of the LINPACK benchmark is one characteristic marker to verify node installation quality. The constant offset of some compute nodes is mostly caused by differences in RAM modules; however, there could be some contributions to dynamic frequency adaption properties caused by differences between individual CPUs originating from manufacturing [Semeraro et al., 2002].

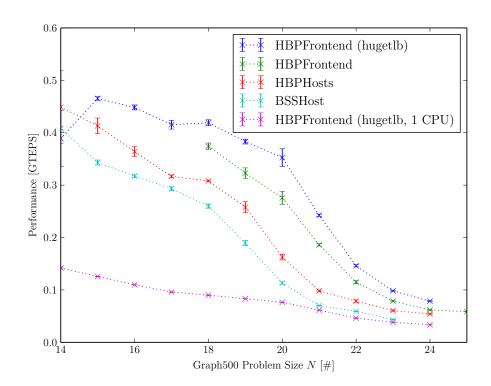

Figure 1.7.: Results of single-node Graph 500 benchmark runs [Murphy et al., 2010]. The problem size N is varied up to machine memory limits (i.e. 16 GiB for the HMF, 32 GiB for the NM-PM1 cluster). The ordinate shows the performance in terms of TEPS (traversed edges per second). Only basic optimizations were performed. On the front-end nodes the page handling of the Linux kernel was optimized for large memory allocations (hugetlb active in blue, disabled in green). There is a slight performance increase between HMF compute nodes and the NM-PM1 compute nodes. The larger gap between NM-PM1 compute nodes and front-end nodes is caused by the increased CPU core count. The measurement was performed in collaboration with Paul Müller.

|                                          | #            | Component                                                     |

|------------------------------------------|--------------|---------------------------------------------------------------|

| CPU                                      | 1            | Intel i7-4771                                                 |

|                                          |              | Haswell, 22 nm                                                |

| RAM                                      | $32{ m GiB}$ | DDR3-1600                                                     |

| Main Board                               | 1            | Intel Q87 chipset-based                                       |

|                                          |              | Remote management via intel AMT                               |

|                                          | 1            | $PCIe \times 16 \text{ Gen3} (16 \text{ lanes}) \text{ slot}$ |

|                                          | 4            | Memory slots, DDR3-1600                                       |

| NIC                                      | 1            | Chelsio T520-LP-CR                                            |

|                                          | 2            | 10GbE ports                                                   |

|                                          |              | Low-latency                                                   |

|                                          |              | MPI with RDMA-support                                         |

| $\operatorname{Case}/\operatorname{PSU}$ |              | 1U including $2 \times$ -redundant PSU                        |

Table 1.1.: Components of a NM-PM1 compute node. The quad-core desktop CPU runs at a base clock speed of 3.5 GHz (turbo speed 3.9 GHz). The dual-port 10GbE NIC supports low-latency operation (evaluation in section 3.3.3). The component list of the predecessor, the HMF compute node, can be found in table A.2. For details about the frontend nodes see table 1.3.

called *hybrid* operation. Details are covered in chapter 3.

The outcome of this budget optimization is presented in table 1.1. It presents a short component list of the NM-PM1 cluster nodes.

### 1.2.2. Storage

Experiments running on the NM-PM1 system can be data-intensive; configuration and result data of single experiments can easily reach into the GiB range. Depending on the exact data network configuration<sup>13</sup>, the inbound and outbound data rates of a single wafer system are between 1 GiB/s and 4 GiB/s (see section 1.1.2). To support recording of experiments at full wire speed, the storage system has been split into different parts: a longer-term storage, and a fast short-term storage system. The former is a single conventional node, called *sto*, equipped with Hard disk drives (HDDs) and providing NFSv4-based network mounts (see table 1.2). Details regarding storage configuration can be found in appendix A.2.

$<sup>^{13}{\</sup>rm The}$  backbone switch does not support 40 Gbit-links for all wafer modules. See section 1.3 for details.

|                                          | #               | Component                                |

|------------------------------------------|-----------------|------------------------------------------|

| CPU                                      | 1               | Intel i7-4770                            |

|                                          |                 | Haswell, 22 nm                           |

| RAM                                      | $16\mathrm{GB}$ | DDR3-1600                                |

| Main Board                               | 1               | Intel Q87 chipset-based                  |

|                                          |                 | Remote management via intel AMT          |

|                                          | 1               | PCIe $3.0 \times 16$ slot                |

|                                          | 1               | PCIe $2.0 \times 4$ slot                 |

|                                          | 4               | Memory Slots, DDR3-1600                  |

| NIC                                      | 1               | Chelsio T580-LP-CR                       |

|                                          | 2               | 40GbE ports                              |

| SAS                                      | 1               | LSI SAS Controller 9211-4i               |

|                                          | 4               | SATA 6G ports                            |

| $\operatorname{Case}/\operatorname{PSU}$ | 1               | $3U$ including $2 \times$ -redundant PSU |

| ·                                        | 16              | hot-swap 3.5" SAS/SATA drive trays       |

|                                          |                 |                                          |

Table 1.2.: Components of the NM-PM1 storage node. At the current stage, sequential reads or writes reach up to 1 GiB/s; increasing the number of HDDs could yield higher throughput. To eliminate this potential bottleneck, the node's uplink supports 40GbE. A file system benchmark is shown in figure A.1.

|                                          | #            | Component                                              |

|------------------------------------------|--------------|--------------------------------------------------------|

| CPU                                      | 1            | Intel E5-2643v2                                        |

|                                          |              | Ivy Bridge EP, 22 nm                                   |

| RAM                                      | $64{ m GiB}$ | DDR3-1600                                              |

| Main Board                               | 1            | Intel C602 chipset-based                               |

|                                          |              | Remote management via integrated IPMI $2.0/\text{KVM}$ |

|                                          | 2 + 2        | PCIe $\times 16$ Gen3 (16 lanes) slot                  |

|                                          | 24           | Memory slots, DDR3-1866 non-ECC                        |

|                                          |              | UDIMM $(\leq 128  \text{GiB})$                         |

|                                          |              | RDIMM ECC ( $\leq 768  \text{GiB}$ )                   |

|                                          |              | LRDIMM ECC ( $\leq 1.5 \text{ TiB}$ )                  |

| NIC                                      | 1            | Chelsio T580-LP-CR                                     |

|                                          | 2            | 40GbE ports                                            |

| SAS                                      | 1            | LSI SAS Controller 9211-4i                             |

|                                          | 4            | SATA 6G ports                                          |

| $\operatorname{Case}/\operatorname{PSU}$ | 1            | $3U$ including $2 \times$ -redundant PSU               |

|                                          | 16           | hot-swap 3.5" SAS/SATA drive trays                     |

Table 1.3.: Components of a NM-PM1 front-end node. The hexa-core server CPU runs at a base clock speed of 3.5 GHz (turbo speed 3.8 GHz). The large number of wide PCIe slots can be used for future upgrades: possibly Xeon Phi for boosting floating-point performance and/or fast PCIe-based solid state disks.

#### 1.2.3. Frontend Nodes

Fast storage is available on the (currently) two server nodes. See table 1.3 for a list of components. The server uplinks use one 40GbE port (dual-port NIC). Each node carries 2 TiB distributed over two Solid-state disks (SSDs). Sequential read and write performance numbers are:<sup>14</sup>

| Sequential Read  | $(515 \pm 3)$ MiB |

|------------------|-------------------|

| Sequential Write | $(458 \pm 5)$ MiB |

Using a striped RAID array yields:

Sequential Read  $(1394 \pm 8)$  MiB Sequential Write  $(1391 \pm 8)$  MiB

A file system benchmark is shown in figure A.2. It is planned to adopt the Ceph distributed file system [Weil et al., 2006].

<sup>&</sup>lt;sup>14</sup>The benchmark numbers were acquired using dd if=/dev/sdX of=/dev/null bs=1M for reads, and dd if=/dev/zero of=/dev/sdX bs=1M conv=fdatasync for writes. Linux employs aggressive caching techniques; to reduce inter-run dependencies, before starting a run echo 3 > /proc/sys/vm/drop\_caches was executed; after writes a final sync was performed.

#### 1.2.4. Software Environment

The disk-less compute nodes boot via preboot execution environment (PXE) from a NFSv4 mount. This file system is provided by the storage node. The operating system is based on Debian Wheezy [Hertzog and Mas, 2014]. Some modifications have been performed: 1. on each node, a memory-based overlay file system is mounted to allow for non-persistent modifications of the local system (*kiosk* mode); 2. the Linux kernel version has been upgraded to 3.14 (due to hardware compatibility issues, and better support for cgroups<sup>15</sup>); 3. an updated OpenFabrics Alliance (OFED) software stack has been installed; 4. message passing interface (MPI)-related software packages have been recompiled due to this new stack. Software packages that are either not included in Debian Wheezy or too old, are provided using the modules environment [Modules, 2014].

Users work in their home directories which are located on another writable NFSv4 mount. All user access is mediated by the SLURM resource manager [LLNL et al., 2014]. An introduction to this resource management tool can be found in section 2.3.

#### 1.2.5. Management and Monitoring

The cluster nodes are managed using Intel AMT. This technology allows for remote low-level hardware control. Functionality ranges from basic power control features to graphical remote access.

All nodes as well as the servers are monitored using Ganglia [Massie et al., 2012] and Nagios [Barth, 2008]. Custom plugins provide temperature sensor data and SLURM-related data.

### **1.3. Network Architecture**

The development of scalable neuromorphic systems makes demands on the interconnection between wafer module (cf. section 1.1) and compute cluster (cf. section 1.2). Previous systems, e.g. Spikey, have been using a dedicated connection between neuromorphic chip and host computer. Another Spikey-based system provided chip interconnections by using a large PCB. In its final version, this system used 1GbE for host communication.

The analog readout system of the NM-PM1 system, AnaRM, and the latest version of the Spikey system are, except for the Spikey neuromorphic network chip, identical. Both use USB 2.0 for the host connection. See section 1.1.4 for hardware details.

When increasing the number of configurable system parts within a neuromorphic system, a scalable network topology and as well as a robust protocol stack becomes more and more important. A standard solution for data networks are Ethernetbased hardware components. The data network equipment is described in the

<sup>&</sup>lt;sup>15</sup>Linux kernel-based isolation mechanism [CGroups, 2014]

following. To support all operation modes of the HMF and NM-PM1 systems, the data network architecture has to provide high throughput for the typical operation as well as low-latency operation for hybrid experiments.

**Experiment Cycle** In general, the experiment cycle of the NM-PM1 system involves different stages: configuration or setup phase, run phase and analysis phase. The configuration phase is dedicated to experiment preparation – the uploading of configuration data for the HICANN Wafer and input data for the FCPs. Depending on the experiment type, the host link is silent during run phase (batch-style experiments) or centered around low-latency data transfer (closed-loop experiments, see chapter 3). By experiment pipelining, the rate of batch-style experiments can be increased, i.e. the FPGA acts as a buffer for experiments – input data and output data has to be stored in FPGA memory. This operation modes is a generalization of the normal batch-style operation. It is planned to implement this mode. However, extensive modifications in the FPGA firmware are required.

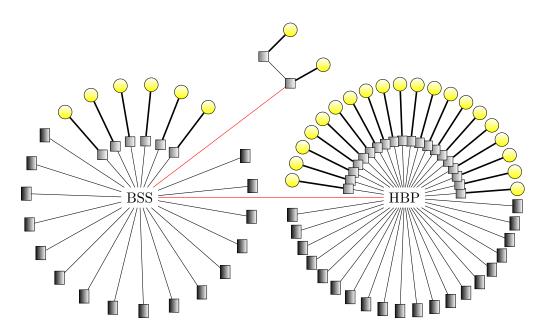

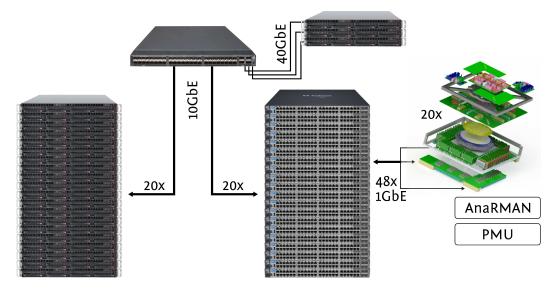

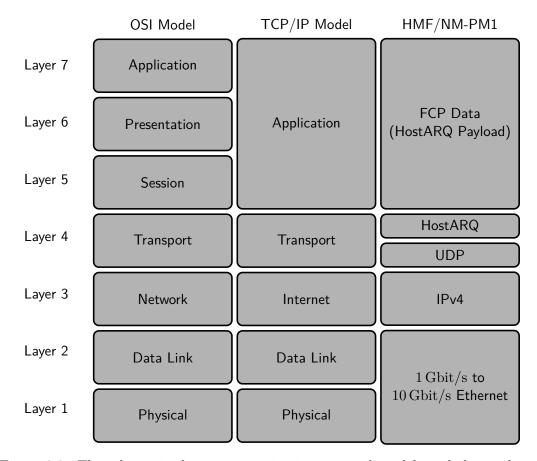

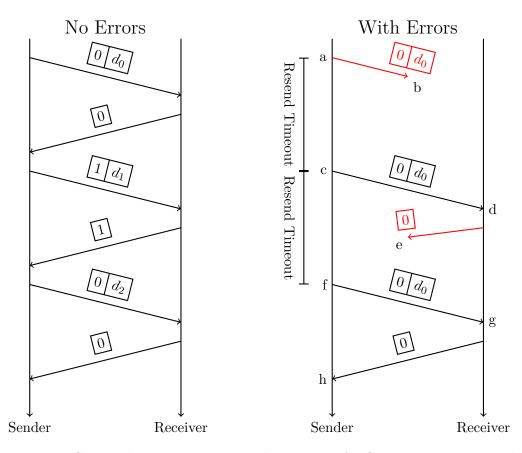

**Overview** Every NM-PM1 or HMF wafer module provides  $48 \times 1$ GbE links, each dedicated to one FCP controlling a specific wafer part. A *wafer* data network switch aggregates these links into one 10GbE link connected to the backbone switch<sup>16</sup>. The compute nodes are connected via one single 10GbE to the backbone switch. Figure 1.8 presents an schematic illustration of the network topology. The BSS HMF and HBP NM-PM1 backbone switches are located at the center of the two large *circles*; compute nodes are represented as shaded rectangles, the shaded squares indicate wafer aggregation switches. Individual 1GbE links of every wafer module (yellow circles) are not shown; only the uplink to the aggregation switches is represented. Both, the HMF and the NM-PM1 systems are connected via 10GbE. The two irregularly-placed wafer (and wafer switches) represent the two lab prototype setups.

Figure 2.1 illustrates the connections within the NM-PM1 system. The central backbone switch provides 10GbE links to every compute node and to every wafer module; 40GbE links are provided to the servers (currently one storage node and two general-purpose servers). The connection to the BSS HMF system is not shown here.

Table 1.4 lists the data switches of the NM-PM1 system.

For all connections between compute node, backbone and wafer module switches Enhanced small form-factor pluggable supporting up to 10 Gbit/s (SFP+) or Quad SFP+ (QSFP) direct-attach copper cables are used. External connectivity for the NM-PM1 system is provided by one single-mode fiber (10GBASE-SR) link to the Kirchhoff-Institute for Physics (KIP); additional fibers are available for future upgrades.

$<sup>^{16}</sup>$  The number of 10GbE switch ports at the backbone switch is limited to 64; i.e. a few wafer modules can be connected using 4  $\times$  10GbE.

Figure 1.8.: Schematic overview of the data network architecture. Compute Nodes are plotted as rectangles, wafer module aggregation switches as squares and wafer module as yellow circles. The thick links between wafer module and wafer switches represent the 48×1GbE links between the FCPs and one wafer switch. All other lines represent 10GbE links: copperbased 10GSFP+Cu wiring within the BSS as well as HBP system, and fibre-based connections (red) between the three different locations. The centers of the two circles represent the backbone switches. The asymmetric configuration of the BSS network is due to a spatial split of the HMF: two wafer modules are located in the lab room (top) while the larger part of the BSS system is located in the server room. The NM-PM1 system is located in the ENI/HBP container building next to the KIP building (for details see figure A.3).

|                 | #  | Component                                                  |

|-----------------|----|------------------------------------------------------------|

| Wafer Switch    | 20 | 48-port 1GbE, $\leq$ 4-port 10GbE [Hewlett-Packard, 2014a] |

| Backbone switch | 1  | 48-port 10GbE, 4-port 40GbE [Hewlett-Packard, 2014b]       |

| Control switch  | 1  | 32-port 1GbE                                               |

Table 1.4.: Components of the NM-PM1 data network. Four experiment switches are located next to four wafer modules within one 19-inch rack. The control switch is used for remote management (e.g., power up or down, reset, remote KVM) of the compute cluster.

## 1.4. Summary

This chapter presented the HMF and NM-PM1 neuromorphic systems. The first section described the composition of a wafer module which has been designed by various hardware developers in Heidelberg and Dresden. Relevant hardware components, like the FCP, as well as basic hardware properties were introduced.

The second section presented the cluster architecture which was designed by the author. In particular, compute nodes, front-end and storage nodes of the NM-PM1 system were specified. Measurements of key performance indicators were presented.

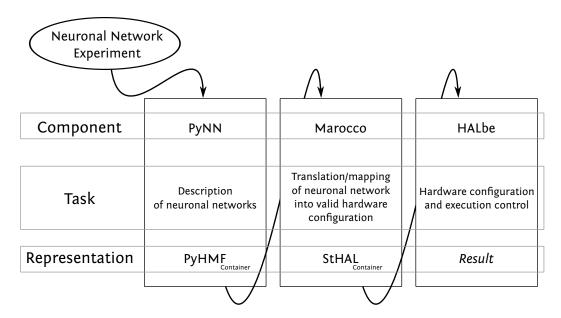

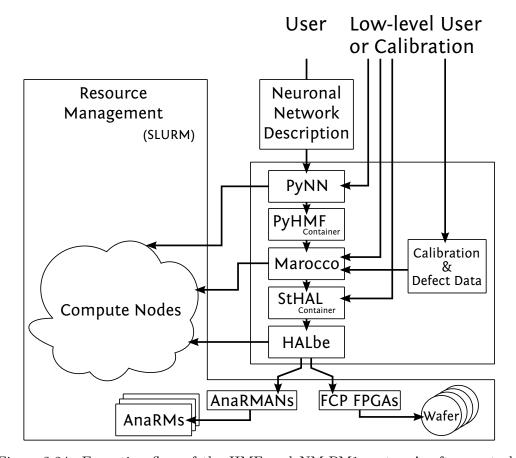

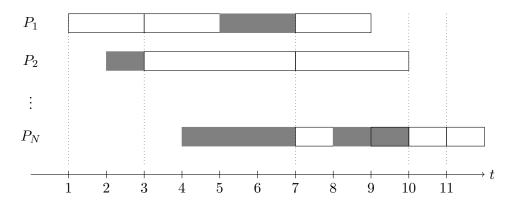

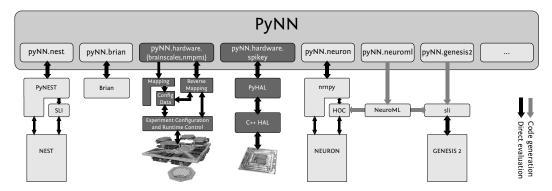

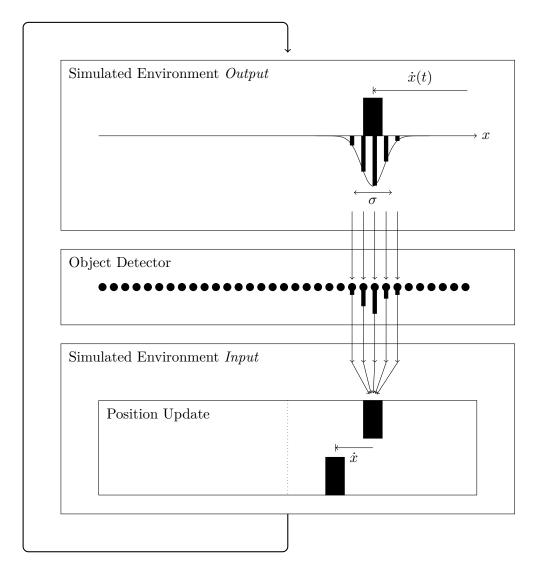

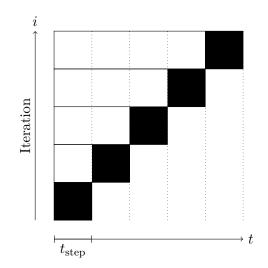

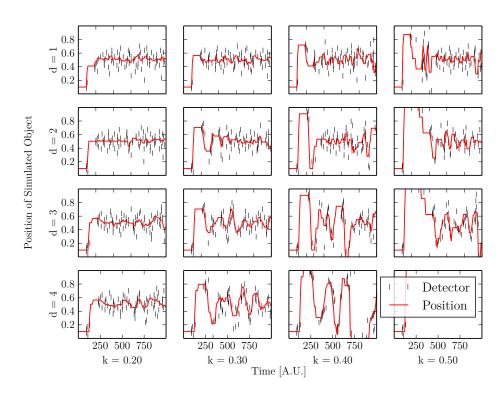

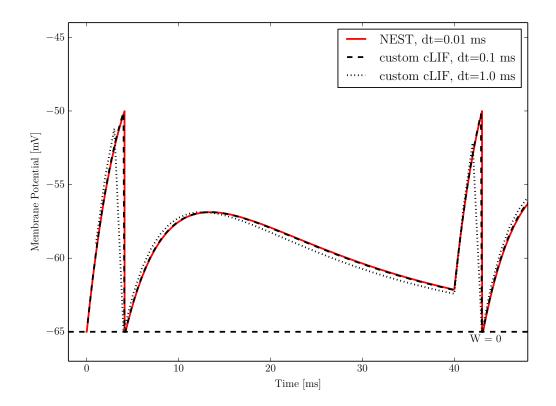

The final section introduced the data network architecture which links wafer modules, compute nodes and all other network-accessible units.