# Dissertation

submitted to the Combined Faculties for Natural Sciences and Mathematics of the Ruperto Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> Presented by Dipl.-Phys. Sebastian Jeltsch born in Ludwigsburg, Germany

Date of oral examination: July 23, 2014

# A Scalable Workflow for a Configurable Neuromorphic Platform

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Bernd Jähne

#### A Scalable Workflow for a Configurable Neuromorphic Platform

This thesis establishes a scalable multi-user workflow for the operation of a highly configurable, large-scale neuromorphic hardware platform. The resulting software framework provides unified low-level as well as parallel high-level access. The latter is realized by an efficient abstract neural network description library, an automated translation of networks into hardware specific configurations and an experiment server infrastructure responsible for scheduling and executing experiments. Scalability, manual guidance and a broad support for handling hardware imperfections render the model translation process suitable for large networks as well as large-scale neuromorphic systems. Networks with local connectivity, random networks and cortical column models are explored to study the topological aptitude of the neuromorphic platform and to benchmark the workflow. Depending on the model, performance improvements of more than two orders of magnitude have been achieved over a previous implementation. Additionally, an automated defect assessment for hardware synapses is introduced, indicating that most synapses are available for model emulation.

In a second study, a tempotron-based hardware liquid state machine has been developed and applied to different tasks, including a memory challenge and digit recognition. The trained tempotron inherently compensates for fixed pattern variations making the setup suitable for analog neuromorphic hardware. The achieved performance is comparable to reference software simulations.

#### Ein skalierbarer Workflow für eine konfiguierbare neuromorphe Plattform

Die vorliegende Arbeit stellt einen skalierbaren Mehrbenutzer-Workflow für den Betrieb einer sehr flexiblen, großskaligen neuromorphen Hardwareplattform bereit. Die entwickelte Software erlaubt einheitlichen, hardwarenahen sowie parallelen, abstrahierten Zugriff. Letzteres ist realisiert mittels einer effizienten Softwarebibliothek für die Beschreibung neuronaler Netze, einer automatisierten Übersetzung von Netzen in hardwarespezifische Konfigurationen und einer verteilten Infrastruktur für die koordinierte Ausführung von Experimenten. Skalierbarkeit, manuelle Kontrolle und eine umfassende Behandlung von Hardwaredefekten ermöglichen das Übersetzen großer neuronaler Netze für großskalige neuromorphe Systeme. Netze mit lokaler Struktur, mit zufälliger Struktur sowie Modelle von kortikalen Säulen wurden verwendet um die Grenzen des neuromorphen Systems zu untersuchen und die Leistungsfähigkeit der Software zu vermessen. Im Vergleich zu einer bestehen Implementierung wurden, abhängig von den Eigenschaften des Netzes, Leistungsverbesserungen von bis zu zwei Größenordnungen erzielt. Weiterhin wurde mittels einer automatisierten Untersuchung der Synapsenschaltungen gezeigt, dass die Mehrzahl der Synapsen funktioniert.

Im zweiten Teil wurde eine tempotron-basierte Liquid State Machine in Hardware realisiert. Unter anderem wurden das Erinnerungsvermögen, sowie die Fähigkeit Zeichen zu erkennen, getestet. Fertigungsbedingte Variationen werden durch das Training kompensiert. Die erzielten Ergebnisse sind vergleichbar mit den Resultaten entsprechender Softwaresimulationen.

# Contents

| Introduction 1 |     |                                                                                                                                                    |  |  |  |  |  |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1              | The | e Neuromorphic Platform 5                                                                                                                          |  |  |  |  |  |

|                | 1.1 | The BrainScaleS Project                                                                                                                            |  |  |  |  |  |

|                | 1.2 | The Hybrid Multi-Scale Facility                                                                                                                    |  |  |  |  |  |

|                | 1.3 | The Wafer-Scale System                                                                                                                             |  |  |  |  |  |

|                | 1.4 | The HICANN Microchip                                                                                                                               |  |  |  |  |  |

|                |     | 1.4.1 Analog Neurons                                                                                                                               |  |  |  |  |  |

|                |     | 1.4.2 Plasticity $\ldots \ldots 9$                                                  |  |  |  |  |  |

|                | 1.5 | On-Wafer Event Network                                                                                                                             |  |  |  |  |  |

|                |     | 1.5.1 Merger Tree $\ldots \ldots $ |  |  |  |  |  |

|                |     | 1.5.2 Buses, Crossbars and Repeaters                                                                                                               |  |  |  |  |  |

|                |     | 1.5.3 Select Switches and Synapse Drivers                                                                                                          |  |  |  |  |  |

|                |     | 1.5.4 Synapse Arrays $\ldots$ 13                                                                                                                   |  |  |  |  |  |

|                |     | 1.5.5 Transmission Reliability $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 14$                                                 |  |  |  |  |  |

|                | 1.6 | Wafer-Scale Integration                                                                                                                            |  |  |  |  |  |

|                | 1.7 | Off-Wafer Communication                                                                                                                            |  |  |  |  |  |

|                |     | 1.7.1 Real-Time Spike Handling                                                                                                                     |  |  |  |  |  |

|                |     | 1.7.2 Host Communication $\ldots \ldots 16$             |  |  |  |  |  |

|                | 1.8 | Future Deployments                                                                                                                                 |  |  |  |  |  |

| 2              | ΑS  | calable Workflow for Neuromorphic Computing 19                                                                                                     |  |  |  |  |  |

|                | 2.1 | Existing Workflow                                                                                                                                  |  |  |  |  |  |

|                | 2.2 | Workflow Redesign                                                                                                                                  |  |  |  |  |  |

|                |     | 2.2.1 Batch Processing                                                                                                                             |  |  |  |  |  |

|                |     | 2.2.2 High-Level User Interface                                                                                                                    |  |  |  |  |  |

|                |     | 2.2.3 Experiment Broker                                                                                                                            |  |  |  |  |  |

|                |     | 2.2.4 The Mapping                                                                                                                                  |  |  |  |  |  |

|                |     | 2.2.5 Executable System Specification                                                                                                              |  |  |  |  |  |

|                |     | 2.2.6 Experiment Server                                                                                                                            |  |  |  |  |  |

|                | 2.3 | Experiment Broker Prototype                                                                                                                        |  |  |  |  |  |

|                |     | 2.3.1 Implementation and Design                                                                                                                    |  |  |  |  |  |

|                |     | 2.3.2 Experiment Throughput                                                                                                                        |  |  |  |  |  |

|                | 2.4 | Summary                                                                                                                                            |  |  |  |  |  |

| 3 | Neu      | ral Net                                                    | work Description                         | 29              |  |  |  |  |  |  |

|---|----------|------------------------------------------------------------|------------------------------------------|-----------------|--|--|--|--|--|--|

|   | 3.1      | The P                                                      | yNN Description Language                 | 29              |  |  |  |  |  |  |

|   |          | 3.1.1                                                      | Model Hierarchy                          | 29              |  |  |  |  |  |  |

|   | 3.2      | A Hier                                                     | rarchical Network Representation         | 31              |  |  |  |  |  |  |

|   |          | 3.2.1                                                      | Hypergraph Reduction                     | 32              |  |  |  |  |  |  |

|   |          | 3.2.2                                                      | Implementation and Design                | 32              |  |  |  |  |  |  |

|   |          | 3.2.3                                                      | Wrapper Generation                       | 34              |  |  |  |  |  |  |

|   |          | 3.2.4                                                      | Interfacing Workflow Components          | 34              |  |  |  |  |  |  |

|   | 3.3      | Summ                                                       | ary                                      | 35              |  |  |  |  |  |  |

| 4 | <b>C</b> |                                                            |                                          | 37              |  |  |  |  |  |  |

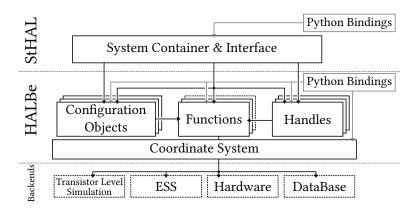

| 4 | -        | tem-Level Software                                         |                                          |                 |  |  |  |  |  |  |

|   | 4.1      |                                                            | Overview                                 | 37              |  |  |  |  |  |  |

|   | 4.2      |                                                            | ess Hardware Abstraction Layer           | 38              |  |  |  |  |  |  |

|   |          | 4.2.1                                                      | Design Concept                           | 39              |  |  |  |  |  |  |

|   |          | 4.2.2                                                      | Type-Rich Interfaces                     | 39              |  |  |  |  |  |  |

|   |          | 4.2.3                                                      | Coordinate System                        | 40              |  |  |  |  |  |  |

|   |          | 4.2.4                                                      | Handles                                  | 42              |  |  |  |  |  |  |

|   |          | 4.2.5                                                      | Stateless Function Interface             | 43              |  |  |  |  |  |  |

|   | 4.3      | Statef                                                     | ul Hardware Abstraction Layer            | 43              |  |  |  |  |  |  |

|   |          | 4.3.1                                                      | Connection Database                      | 43              |  |  |  |  |  |  |

|   |          | 4.3.2                                                      | Python Bindings                          | 44              |  |  |  |  |  |  |

|   | 4.4      | Summ                                                       | ary                                      | 44              |  |  |  |  |  |  |

| 5 | Mar      | apping Neural Networks to Hardware Specific Configurations |                                          |                 |  |  |  |  |  |  |

| 5 | 5.1      | • •                                                        |                                          | <b>47</b><br>47 |  |  |  |  |  |  |

|   | 5.2      |                                                            | rements                                  | 48              |  |  |  |  |  |  |

|   | 0.2      | 5.2.1                                                      | Modularity and Extensibility             | 48              |  |  |  |  |  |  |

|   |          | 5.2.1<br>5.2.2                                             | Objectives and Guidance                  | 49              |  |  |  |  |  |  |

|   |          | 5.2.2                                                      | Defect Handling                          | 49              |  |  |  |  |  |  |

|   |          | 5.2.3<br>5.2.4                                             | Performance                              | 49              |  |  |  |  |  |  |

|   | 5.3      | 0                                                          | fer Mapping                              | 49<br>51        |  |  |  |  |  |  |

|   | J.J      | 5.3.1                                                      | ** 0                                     |                 |  |  |  |  |  |  |

|   |          |                                                            | Optimal Solutions                        |                 |  |  |  |  |  |  |

|   |          | 5.3.2                                                      | Similar Problems                         |                 |  |  |  |  |  |  |

|   |          | 5.3.3                                                      | Feedforward Mapping Approach             | 52              |  |  |  |  |  |  |

| 6 | A S      | Scalable Implementation of a Feedforward Wafer Mapping     |                                          |                 |  |  |  |  |  |  |

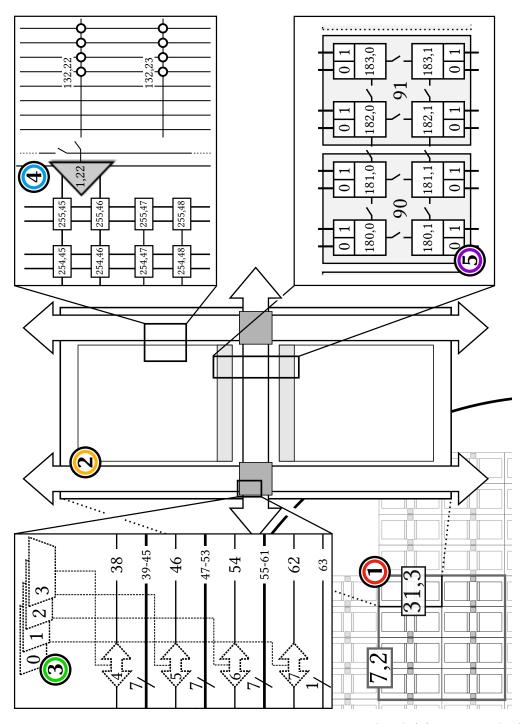

|   | 6.1      | Neuro                                                      | n Placement                              | 58              |  |  |  |  |  |  |

|   | 6.2      | Merger Routing                                             |                                          |                 |  |  |  |  |  |  |

|   | 6.3      |                                                            |                                          |                 |  |  |  |  |  |  |

|   | 6.4      | Wafer                                                      | Routing                                  | 64              |  |  |  |  |  |  |

|   |          | 6.4.1                                                      | Graph-Based Wafer Network Representation | 64              |  |  |  |  |  |  |

|   |          | 6.4.2                                                      | Common Tasks                             | 65              |  |  |  |  |  |  |

|   |          | 6.4.3                                                      | Iterative Shortest Path Routing          | 67              |  |  |  |  |  |  |

|   |       | 6.4.4   | Iterative Horizontal Growth Routing                                                                                                                       |

|---|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       | 6.4.5   | Comparison                                                                                                                                                |

|   | 6.5   | Synaps  | se Driver Routing                                                                                                                                         |

|   |       | 6.5.1   | Requested Synapse Drivers                                                                                                                                 |

|   |       | 6.5.2   | Iterative Best Fit Driver Assignment                                                                                                                      |

|   |       | 6.5.3   | Simulated Annealing Driver Assignment                                                                                                                     |

|   | 6.6   | Synaps  | se Array Routing                                                                                                                                          |

|   |       | 6.6.1   | Synapse Row Assignment                                                                                                                                    |

|   |       | 6.6.2   | Synapse Assignment                                                                                                                                        |

|   | 6.7   | Param   | eter Transformation $\ldots \ldots $             |

|   |       | 6.7.1   | Parameter Framework                                                                                                                                       |

|   |       | 6.7.2   | From Biology to Hardware                                                                                                                                  |

|   |       | 6.7.3   | Shared Parameters                                                                                                                                         |

|   |       | 6.7.4   | Spike Sources                                                                                                                                             |

|   |       | 6.7.5   | Current Sources                                                                                                                                           |

|   | 6.8   | 0       | evel Mapping Interface                                                                                                                                    |

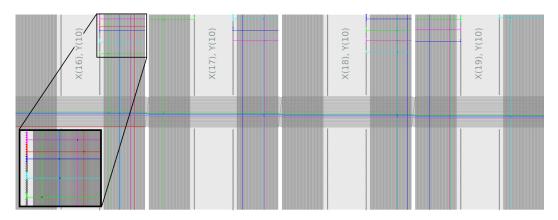

|   | 6.9   |         | g Visualization                                                                                                                                           |

|   | 6.10  | Summ    | ary                                                                                                                                                       |

| 7 | Han   | dling H | ardware Defects 91                                                                                                                                        |

| • | 7.1   | •       | Management                                                                                                                                                |

|   |       | 7.1.1   | Interface                                                                                                                                                 |

|   |       | 7.1.2   | Defect Granularity                                                                                                                                        |

|   |       | 7.1.3   | Defect Description                                                                                                                                        |

|   | 7.2   |         | se Measurement                                                                                                                                            |

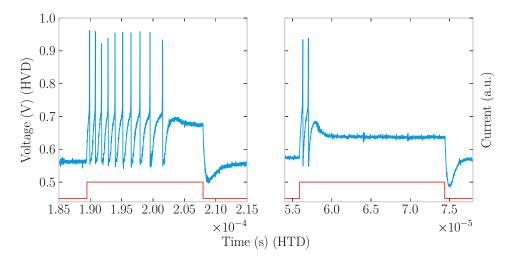

|   | • · - | 7.2.1   | Signal Pathways                                                                                                                                           |

|   |       | 7.2.2   | Analog Parameters                                                                                                                                         |

|   |       | 7.2.3   | Automatic Classification                                                                                                                                  |

|   |       | 7.2.4   | Measurement Protocol                                                                                                                                      |

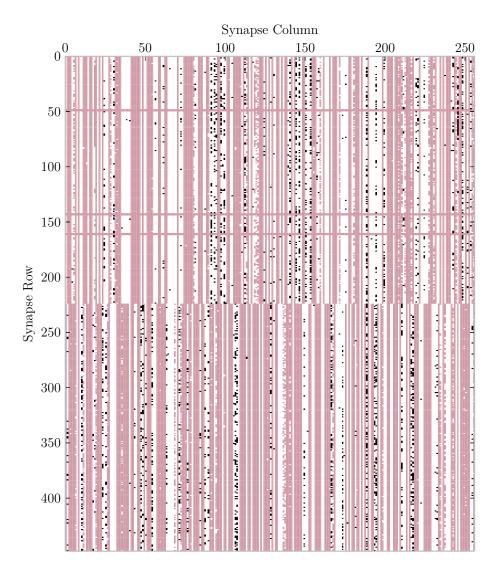

|   |       | 7.2.5   | Distribution of Defects                                                                                                                                   |

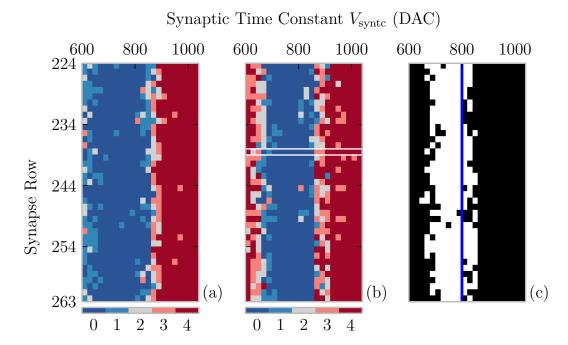

|   |       | 7.2.6   | Synaptic Time Constant                                                                                                                                    |

|   | 7.3   | Estima  | ation of Synapse Availability                                                                                                                             |

|   |       |         |                                                                                                                                                           |

| 8 |       |         | nd Mapping Benchmarks 105                                                                                                                                 |

|   | 8.1   |         | mark Environment $\dots \dots \dots$                      |

|   | 8.2   |         | t Stimulus for Multi-Circuit Neurons                                                                                                                      |

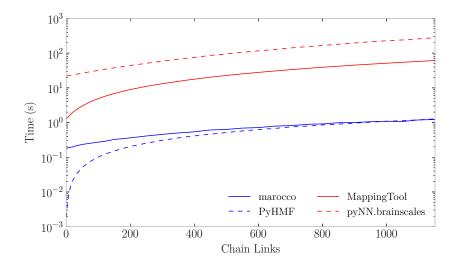

|   | 8.3   |         | $\begin{array}{c} \text{Chain Network} \dots \dots$ |

|   |       | 8.3.1   | Guided Placement $\dots \dots \dots$                      |

|   |       | 8.3.2   | Workflow Performance Comparison                                                                                                                           |

|   | 0.4   | 8.3.3   | Towards a Hardware Implementation                                                                                                                         |

|   | 8.4   |         | geneous Random Networks $\dots \dots \dots$               |

|   |       | 8.4.1   | Workflow Performance Comparison                                                                                                                           |

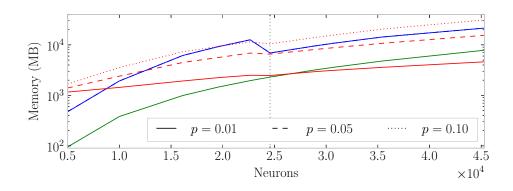

|   |       | 8.4.2   | Persistent Storage of Wafer Configurations                                                                                                                |

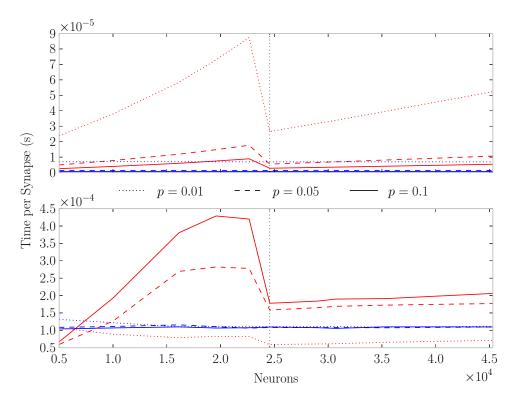

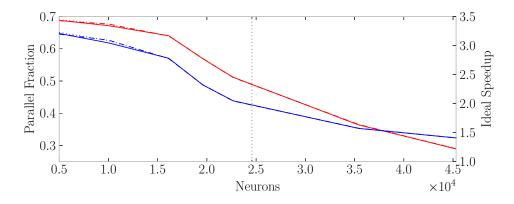

|              |                   |          | Mapping Parallelization                               |       |  |  |  |  |

|--------------|-------------------|----------|-------------------------------------------------------|-------|--|--|--|--|

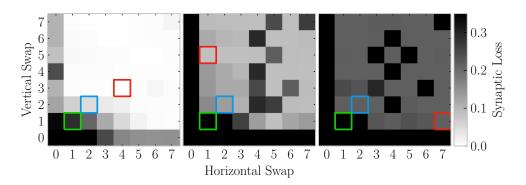

|              |                   |          | Layer 1 Network Optimization                          |       |  |  |  |  |

|              | 8.5               | - ,      | /3 Attractor Model                                    |       |  |  |  |  |

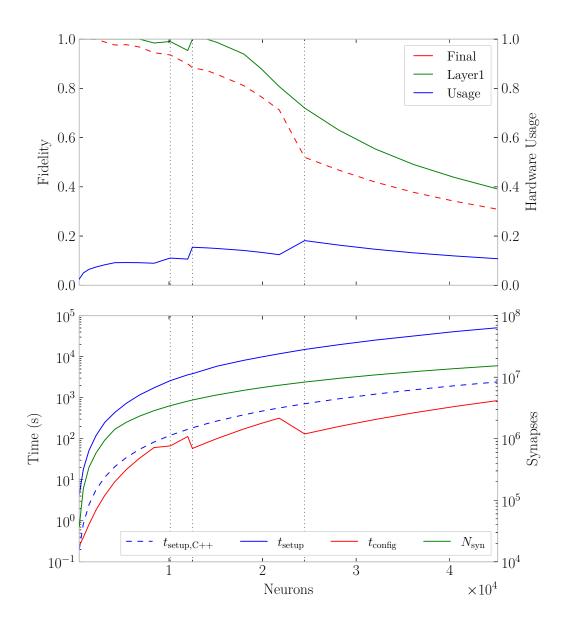

|              |                   |          | Workflow Performance Comparison                       |       |  |  |  |  |

|              |                   |          | Guided Placement                                      |       |  |  |  |  |

|              | 8.6               |          | ortical Column                                        |       |  |  |  |  |

|              | 8.7               |          | Cortical Column                                       |       |  |  |  |  |

|              | 8.8               |          | onous Irregular States                                |       |  |  |  |  |

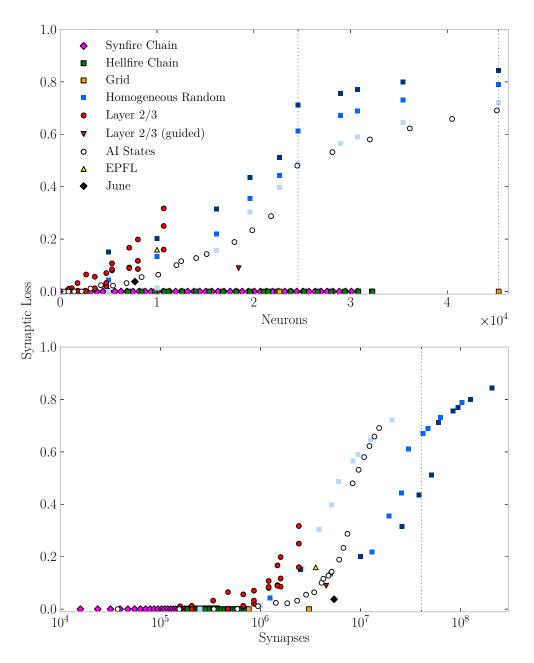

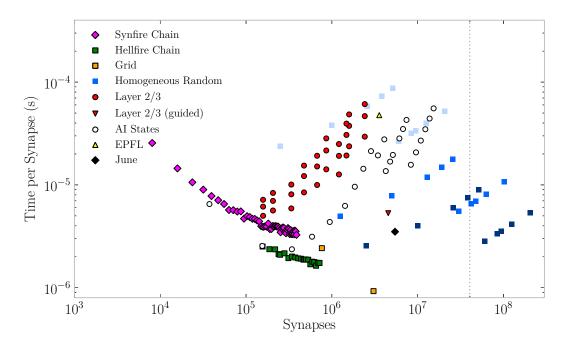

|              | 8.9               |          | Network Topologies                                    |       |  |  |  |  |

|              |                   |          | Synfire Chain Network                                 |       |  |  |  |  |

|              |                   |          | Grid Network Topology                                 |       |  |  |  |  |

|              | 8.10              | Topolog  | y Exploration                                         | . 141 |  |  |  |  |

| 9            | -                 |          | Classification with Accelerated Neuromorphic Hardware | 147   |  |  |  |  |

|              | 9.1               |          | re Platform                                           |       |  |  |  |  |

|              | 9.2               | -        | State Machine                                         |       |  |  |  |  |

|              |                   |          | Tempotron                                             |       |  |  |  |  |

|              | 9.3               |          | re Adaptation                                         |       |  |  |  |  |

|              |                   |          | Conductance-Based Synapses                            |       |  |  |  |  |

|              |                   |          | Limited Weight Resolution                             |       |  |  |  |  |

|              |                   |          | Traceless Learning                                    |       |  |  |  |  |

|              |                   |          | Short Term Plasticity                                 |       |  |  |  |  |

|              | 9.4               | ~ ~      | tions                                                 |       |  |  |  |  |

|              |                   |          | Memory Task                                           |       |  |  |  |  |

|              |                   |          | Demanding Task                                        |       |  |  |  |  |

|              |                   |          | Handwritten Digit Recognition                         |       |  |  |  |  |

|              | 9.5               | Summar   | y                                                     | . 163 |  |  |  |  |

| Dis          | scussi            | on and ( | Dutlook                                               | 165   |  |  |  |  |

| Ар           | pend              | ix       |                                                       | 173   |  |  |  |  |

|              | A.1               | Test Set | up                                                    | 173   |  |  |  |  |

|              | A.2               | Paramet  | ter Sets                                              | 173   |  |  |  |  |

|              | A.3               | Further  | Measurements                                          | . 178 |  |  |  |  |

| Acronyms     |                   |          |                                                       |       |  |  |  |  |

| Bibliography |                   |          |                                                       |       |  |  |  |  |

| ٨٥           | Acknowledgments   |          |                                                       |       |  |  |  |  |

| ΑL           | ACKNOWIEUGINEIIUS |          |                                                       |       |  |  |  |  |

## Introduction

Everyday we are surrounded by powerful computation devices: notebooks, mobile phones and the internet are virtually everywhere. At the same time, computer clusters are used to study our consumer habits and preferences. Despite the different architectures and physical extents, all these systems require high single instruction throughput for efficient computation. However, performance limits of this kind of architectures are approaching. Clock frequencies are limited by power density (Kim et al., 2003) and modern process technologies have reduced transistor gates to merely a few atom layers (Schulz, 1999). Over the last few years, the focus has shifted to concurrent architectures, both with shared and distributed memory. The latter is mostly implemented in terms of computer clusters, which allows for extensive horizontal scaling. Their extent is only limited by cost, heat dissipation and sensitivity to single component failure (Hennessy and Patterson, 2012). Developing efficient algorithms for conventional distributed systems is challenging and problems that cannot easily be partitioned into individual subproblems are often solved more efficiently on a single computer.

Nature, on the other hand, came up with its own distributed computational architecture: the brain. The human brain, in particular, contains approximately  $10^{11}$  neurons, which are interconnected via  $10^{15}$  synapses forming complex networks to carry out massively parallel computation (Azevedo et al., 2009; Drachman, 2005). Information is exchanged via action potentials or spikes, a sparse spatio-temporal code (Attwell and Laughlin, 2001). The resulting design, which evolved over millions of years, is extremely efficient in terms of energy. The human brain consumes only about 20 W of power (Clarke and Sokoloff, 1999). Moreover, the design is extremely robust. It can cope with disturbance by directing attention (Corbetta and Shulman, 2002), adapt to changing environments (Cohen et al., 2007) and in some cases even recover from severe lesions (Robertson and Murre, 1999).

Tasks that can easily be captured in algorithmic descriptions are typically solved more efficiently by computers, like arithmetic and numerics. However, the human brain outperforms state of the art technical solutions in areas like pattern completion, complex body movement and higher order abstractions. Tasks that become more and more important, e.g., for robotics.

Understanding the human brain is one of the great challenges of the 21st century (White House, 2014). An endeavor that is ambitiously pursued among others by the BrainScaleS project (2014) and the Human Brain Project (Markram, 2012b). These projects bring together scientists from different fields, like biology, medicine, psychology, mathematics and computer science to build comprehensive brain maps and to develop a comprehensive theory linking models of limited scope across different

#### Introduction

spatial and temporal scales. Another long-term goal is the establishment of a novel brain-inspired computing paradigm and novel computing architectures to tackle the above mentioned shortcomings of traditional computers.

Detailed biological measurements have built the foundations for the knowledge we have today about the inner workings of the brain. Unfortunately, these measurements always provide access to only a limited number of variables in the system (Stevenson and Kording, 2011) Computational neuroscience has therefore become a second invaluable approach to study neural networks from the bottom up on a very detailed level, reproducing high-level functionality and exploring the frontiers of neural circuitry. However, mapping large neural architectures to conventional computers rapidly becomes infeasible due to the fundamental computational differences limiting the size and complexity of studies. Large computer clusters are necessary to conduct detailed, spike-based simulations for small fractions of the brain over the course of only a few seconds (Markram, 2006). Simulations on more abstract levels can capture larger areas, but cannot account for emergent properties on a microscopic single-cell scale. These limitations are overcome by highly-parallel neuromorphic hardware systems that physically emulate neural building blocks rather than simulating them. Due to the inherent parallelism, these systems can be scaled towards large neural network emulations without slowing down.

The Hybrid Multi-Scale Facility (HMF) developed within the BrainScaleS project is build upon a highly configurable, large-scale neuromorphic hardware platform. Neural networks are realized energy efficiently in a mixed-signal fashion, where spike communication is implemented by a high bandwidth, asynchronous, digital interconnection fabric, while neurons are implemented as analog circuitry. Due to shorter intrinsic time constants, these neurons operate around  $10^3$  to  $10^5$  times faster than biological ones. Therefore, long-term experiments can be conducted in a short period of time. Notably, the energy required per synaptic transmission is about 6 to 10 orders of magnitude less than what is needed for similar simulations on traditional computer clusters (Markram and Meier, 2012). The HMF will provide access to emulations with up to  $10^6$  neurons until the end of the BrainScaleS project. A second installment to be realized within the first 18 month of the Human Brain Project is going to provide up to  $10^9$  neurons (HBP SP9, 2014).

State of the art neuromorphic computing shows many similarities to the advent of both, computers and Field Programmable Gate Arrays (FPGAs). Initially, those systems have been mere subjects to research. The scope was limited by the availability of basic tools for their configuration and operation. Over time, operating systems, compilers and improved user interfaces revolutionized the way people interact with computers. Similarly, advanced design tools have been essential for FPGAs to become the de facto standard for low volume hardware and rapid prototype development.

Setting up large networks on the HMF on a low level is a challenging and error prone task even for hardware experts due to its complexity and size. Following the example of computers and FPGAs, it is important to establish an automated mapping of abstract neural network descriptions to hardware specific configurations that enables novices and experts alike to efficiently operate the system. Moreover, project partners and external users who want to exploit the unique properties of the HMF require remote access. This thesis introduces a novel software infrastructure providing both. After outlining the software design principles and implementation, several benchmarks are presented that measure workflow and mapping performance characteristics including early hardware results. Finally, a spike-based liquid state machine (Maass et al., 2002; Jaeger, 2001) implementation is demonstrated on a smaller chip-based system.

## Structure of the Thesis

This thesis is structured into nine chapters followed by a comprehensive discussion and outlook. The nine chapters are briefly outlined below.

- 1. The Neuromorphic Platform: In this chapter, all major HMF components are introduced, including the HICANN microchip. A special focus is put on the topology and the large configuration space, which build the foundation for subsequent chapters.

- 2. A Scalable Workflow for Neuromorphic Computing: The accelerated, large-scale HMF can no longer be considered a single-user system due to its complexity and vast computational resources. To increase utilization, its resources have to be shared among many users, much like computer clusters. Here, the design and a prototype implementation of such a multi-user setup are presented.

- 3. Neural Network Description: Starting with the introduction of PyNN, the HMF high-level user interface is presented. PyHMF is a PyNN-compatible, high performance and topology preserving C++ implementation with a thin autogenerated Python wrapper on top.

- 4. System-Level Software: This chapter outlines a redesign of the low-level software, which provides unified access to the HMF.

- 5. Mapping Neural Networks to Hardware Specific Configurations: This chapter introduces a modular feedforward mapping strategy, which enables an efficient translation of abstract neural networks into hardware configurations.

- 6. A Scalable Implementation of a Feedforward Wafer Mapping: An actual implementation of the above mentioned feedforward mapping strategy is presented. Scalability towards large networks is achieved by means of efficient algorithms and shared-memory parallelization.

- 7. Handling Hardware Defects: The HMF is explicitly designed to cope with fabrication defects and analog variations. A dedicated defect framework manages defects, which can then be used to implement workarounds during the mapping step. Moreover, the measurement of synapse defects for a HICANN are presented.

## Introduction

- 8. Workflow and Mapping Benchmarks: This chapter explores the suitability of the HMF and the new mapping for a wide range of network topologies, which includes an early attempt of mapping a chain-model to hardware. A comprehensive study of homogeneous random networks is used to compare the novel workflow with its predecessor. The chapter closes with a comprehensive discussion on neural network topologies suitable for the HMF.

- 9. Spike-Based Classification with Accelerated Neuromorphic Hardware: A tempotron-based liquid state machine has been implemented on an accelerated neuromorphic hardware system. Therefore, a hardware adaptation of the tempotron readout is derived, suitable for conductance-based synapse models. The setup is then trained upon three different tasks including handwritten digit recognition.

## **1** The Neuromorphic Platform

The Hybrid Multi-Scale Facility (HMF) is a platform for large-scale neural network simulations that combines the flexibility of conventional cluster computing with the efficiency of neuromorphic hardware systems. The wafer-scale system is the accelerated neuromorphic core and consists of uncut wafers of 384 HICANN chips with 512 neuron circuits each.

This chapter introduces all major components of the HMF on an abstract level. Initially, a brief overview of the wafer-scale system is given, then the individual components are explained following a bottom-up approach, starting with the HICANN microchip and moving towards the inter-chip and host communication networks. A special focus is put on the functional aspects and configurability of the system.

## 1.1 The BrainScaleS Project

The BrainScaleS project (BSP) funded by the European Union started in 2011 and is running over 4 years (BrainScaleS, 2014). Researchers from 19 groups across ten different European countries set out to deepen our understanding of the brain at different spatial and temporal scales. Scales range from in-vivo single-cell measurements on a sub-millisecond level to large-scale network simulations with millions of neurons and long-term learning (Kunkel et al., 2012; Nessler et al., 2013; Pozzorini et al., 2013). The resources necessary to computationally study brain structure are provided by computer clusters (Kunkel et al., 2012; Djurfeldt et al., 2008), many core systems (Furber et al., 2012) and mixed-signal neuromorphic hardware (HBP SP9, 2014). The latter is the central issue of this dissertation.

## 1.2 The Hybrid Multi-Scale Facility

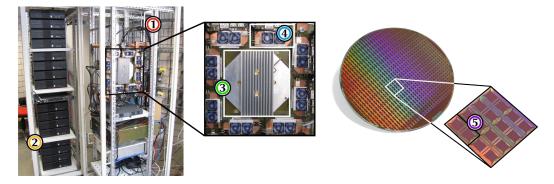

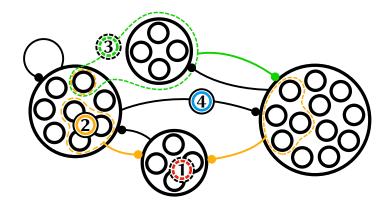

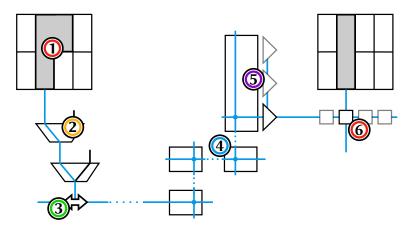

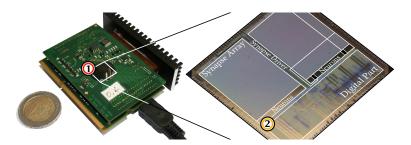

The HMF combines the flexibility provided by conventional cluster computing with the efficiency and performance of accelerated, mixed-signal neuromorphic hardware systems (HBP SP9, 2014). This hybrid approach allows scientists to study networks on the most suitable substrate. A long-term goal is to connect different aspects of a model running on different substrates in a closed loop, e.g., an analog emulation controlling a virtual robot that is simulated on the cluster. A first prototype installation is shown in Figure 1.1.

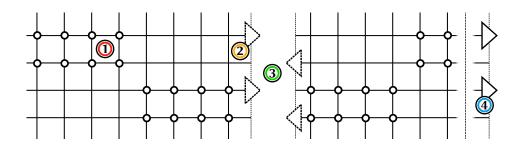

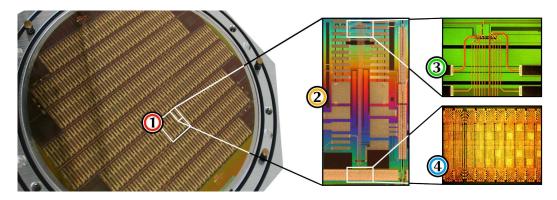

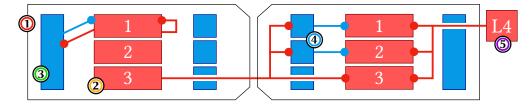

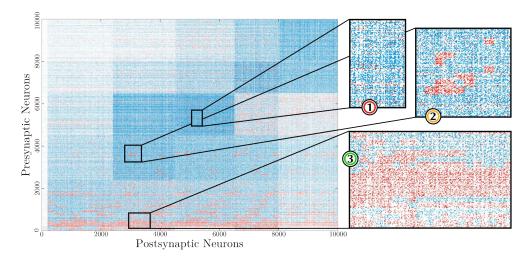

Figure 1.1: The first HMF prototype installation at the Kirchoff-Institute for Physics in Heidelberg. The rack with the wafer system is in the front (1) and a 16 node commodity cluster in the back (2). The actual wafer is installed under the aluminum heat sink (3). Off-wafer communication is established via 12 FPGA communication modules (4). A wafer consists of 384 interconnected HICANN chips (5).

## 1.3 The Wafer-Scale System

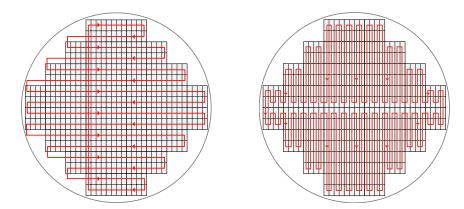

The wafer-scale system is the neuromorphic core of the HMF: an accelerated, large-scale, configurable hardware system developed at the Kirchoff-Institute in Heidelberg and at the TU Dresden. The system is composed of multiple wafer modules. Every wafer implements 384 HICANN chips with up to 512 neurons and 114 688 synapses each. After fabrication, wafers are left intact instead of being cut for the production of single chips. This so-called wafer-scale integration is a unique property of the system, where wafer-wide connectivity is established by means of post-processing, as explained in see Section 1.6. This allows high inter-chip communication bandwidth at low cost and with low power consumption.

## 1.4 The HICANN Microchip

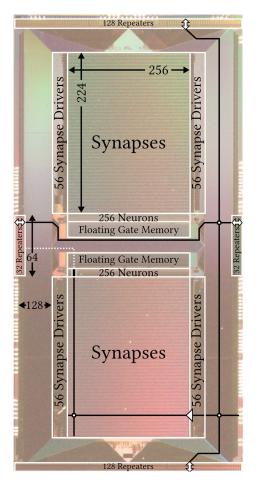

The mixed-signal High Input Count Analog Neural Network (HICANN) microchip is the basic building block of the wafer system. It has a die size of  $5 \times 10 \text{ mm}^2$  and is fabricated in 180 nm CMOS technology. Figure 1.2 shows a micro photograph of the chip. The most prominent features are the two large synapse arrays, covering most of the surface area. They are separated by digital communication structures crossing the chip horizontally in the center and vertically on both sides.

This chapter focuses on the functional aspects of the chip, more detailed technical descriptions are provided by Schemmel et al. (2008, 2010).

Figure 1.2: A micro photograph of the  $5 \times 10 \text{ mm}^2$ HICANN die. Prominently, the synapse arrays cover most of the area. 512 neuron circuits are aligned along the edges of the arrays towards the center of the chip. Layer 1 buses, indicated by black lines, run horizontally through the center and vertically along both sides of the chip. They implement the Layer 1 on-wafer event network for spike communication described in Section 1.5. Repeaters at the chip boundaries restore signal quality, thus enabling long-range connectivity across multiple chips. Events can be relayed from vertical buses to neurons via synapse drivers and synapses, where they finally generate postsynaptic potentials (PSPs) on the analog membrane of the neuron.

#### 1.4.1 Analog Neurons

Every HICANN implements 512 analog neuron circuits (Millner, 2012). Half of which are located on either edge of the synapse arrays towards the center of the chip, as shown in Figure 1.2.

The dynamics of the analog neuron circuits evolve in continuous time and are faster than biological real time due to shorter intrinsic time constants. The speedup can be configured within a range of  $10^3$  to  $10^5$ , i.e., a speedup of  $10^4$  means that the emulation of a 1s experiment takes only  $10^{-4}$  s. This speedup renders the system suitable for learning experiments that would otherwise take long periods of time. The behavior of

#### 1 The Neuromorphic Platform

neurons is characterized by the adaptive exponential integrate-and-fire (AdEx) model (Brette and Gerstner, 2005) with conductance based synapses according to

$$-C_{\rm m} \frac{{\rm d} V_{\rm m}}{{\rm d} t} = g_{\rm l} (V_{\rm m} - E_{\rm l}) - g_{\rm l} \Delta_{\rm t} \exp\left(\frac{V_{\rm m} - V_{\rm t}}{\Delta_{\rm t}}\right) + g_{\rm e}(t) (V_{\rm m} - E_{\rm e}) + g_{\rm i}(t) (V_{\rm m} - E_{\rm i}) + \omega$$

(1.1)

$$-\tau_w \frac{\mathrm{d}\,w}{\mathrm{dt}} = w - a(V_\mathrm{m} - E_\mathrm{l}) \qquad . \tag{1.2}$$

Where  $V_{\rm m}$  and  $C_{\rm m}$  denote the membrane voltage and capacitance of the neuron, respectively. The latter can be set to either 2.16 pF or 0.16 pF in hardware.  $E_{\rm l}$ ,  $E_{\rm e}$  and  $E_{\rm i}$  are reversal potentials for leakage, excitation and inhibition, while  $g_{\rm l}$ ,  $g_{\rm e}$  and  $g_{\rm i}$  are the corresponding conductances. The spike initiation potential  $V_{\rm t}$  and the slope factor  $\Delta_{\rm t}$  control the non-linear dynamics of the exponential term. The right most term  $\omega$ in Equation (1.1) contributes an adaption current. The dynamics of the adaptation are described by Equation (1.2). Here, a is an adaption variable with the units of a conductance and  $\tau_w$  is the adaption time constant. The spiking behavior of the AdEx model is described by

$$\begin{cases} V_{\rm m} \to V_{\rm reset} \\ \omega \to \omega + b \end{cases} \quad \text{if } V_{\rm m} \ge \Theta \qquad .$$

(1.3)

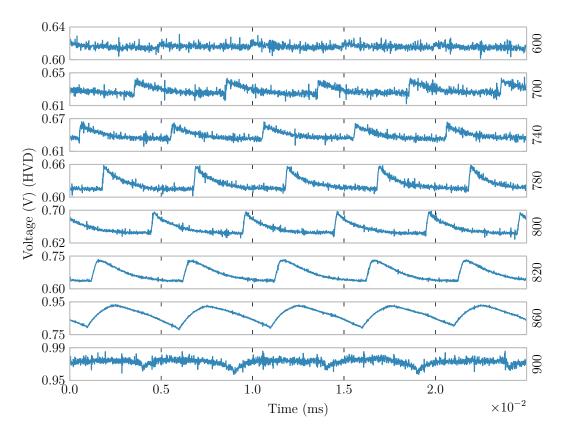

Whenever the membrane voltage  $V_{\rm m}$  crosses the threshold potential  $\Theta$  a spike is detected,  $V_{\rm m}$  is set back to  $V_{\rm reset}$  and  $\omega$  is increased by the constant *b*. The latter is known as spike-triggered adaption. Given a stimulation with a constant current and for positive *b*, the excitability is reduced each time the neuron spikes. Actual hardware recordings of characteristic AdEx spike patterns (Naud et al., 2008) are presented in Figure 8.1.

On hardware, neuron dynamics are controlled by 22 parameters, which also include technical parameters to adjust the operational regime (HBP SP9, 2014). These parameters are stored in analog floating-gate cells, as described by Srowig et al. (2007), and can be set individually for each circuit instance, with exception of  $V_{\text{reset}}$ . During experiments, the floating gate controller can be repurposed to stimulate a single neuron per chip with a configurable current course.

Neighboring neuron circuits within blocks of 64, 32 from the top and the bottom array, can be combined in order to build neurons with higher input counts. Every connected neuron circuit adds 224 synapses, allowing to built neurons with up to  $64 \times 224 = 14336$  individual inputs. Technically, neuron membrane capacitors are connected in parallel, therefore adding the capacitances. The interconnection topology is shown in Figure 4.2 item 5. The spike detection mechanism of connected circuits has to be deactivated for all but one. A configurable routing allows to relay the corresponding spike signal to the other circuits to trigger their local voltage reset mechanisms whenever a threshold crossing of the membrane voltage is detected. Setting up the routing correctly is critical because erroneously routed spike signals can trigger

a reset cascade, which may damage the chip (Millner, 2011). Future revisions of the chip are planned to implement configurable conductances between membranes to build neurons with multi-compartmental dendrites, as explained by Millner et al. (2012).

## 1.4.2 Plasticity

The HICANN chip provides two types of plasticity to dynamically modulate synaptic efficacies: short term plasticity (STP) and spike timing dependent plasticity (STDP).

STP models mobility and limited availability of neurotransmitters in biological synapses according to Tsodyks and Markram (1997). The mechanism and its technical implementation is inherited from the Spikey predecessor chip and is described in more detail by Schemmel et al. (2007) and Brüderle (2009).

STDP, on the other hand, enables long-term learning based on spike correlation. Again, the technical implementation is based on Spikey and is described by Schemmel et al. (2006) and Pfeil et al. (2012). More information on the current development and future implementation is provided by Friedmann (2013).

## 1.5 On-Wafer Event Network

This section introduces the statically switched Layer 1 on-wafer network fabric that implements asynchronous, high-bandwidth communication between chips and has to be configured prior to the experiment. On every HICANN, 64 bus segments run horizontally through the center and 128 vertically on both sides. The bus structure is clearly visible as a distinct H-shape in Figure 1.2. Operated at a clock frequency of 100 MHz, buses provide a bandwidth of 125 MEvents/s resulting in a total throughput of 40 GEvents/s per chip.

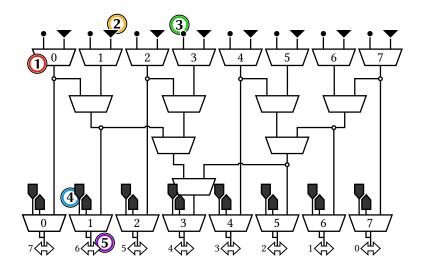

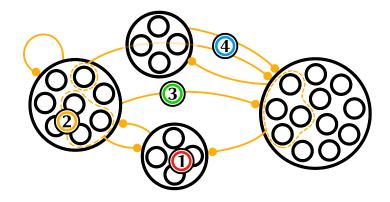

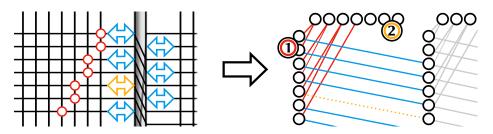

Before introducing the network components, a short overview of the event routing is given from source to targets. The individual components and routing options are explained in more detail in the subsequent sections. Whenever the membrane voltage  $V_{\rm m}$  of a neuron crosses the threshold  $\Theta$ , a digital 6 bit address event is generated. The source address can be set individually for each neuron. Apart from neurons, other spike sources exist, including external FPGAs and on-chip background generators. These events can be combined using the so-called merger tree to increase network utilization, see Figure 1.3. The bottom most mergers relay these events into the Layer 1 network at special synchronous parallel Layer 1 (SPL1) repeaters operating specific horizontal bus segments. Configurable sparse crossbar switches connect horizontal and vertical buses in order to route events across the wafer. Routes always start at a single SPL1 repeater and branch out to target any number of chips. At a target, vertical buses can be connected to synapse drivers via select switches to relay events into the synapse array. A two-stage address decoding scheme selectively activates synapses in order to connect drivers to neurons, where incoming events finally generate PSPs.

Layer 1 events encode spike signals as source addresses (Deiss et al., 1998), thus spike times are implicitly defined by the instant they arrive at the receiver. This also means,

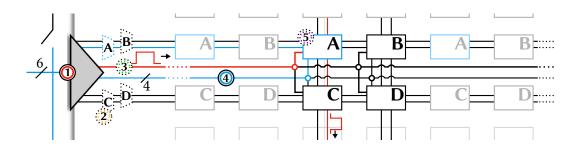

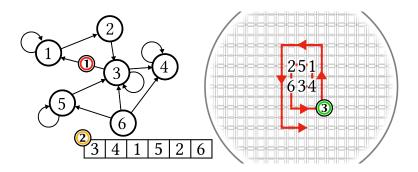

Figure 1.3: An illustration of the HICANN merger tree topology. Events flow from the top to the bottom of the structure. Each merger (1) can be configured to forward either events from one of its inputs or merge both with static priority. In the top row, events from up to 64 neurons (2) and a background generator (3) can be merged. Events from the external FPGA enter the tree at the bottom row of DNC mergers (4). The output of the Digital Network Chip (DNC) mergers interfaces the Layer 1 network via special SPL1 repeaters (5) connected to every 8th horizontal bus.

there are no programmable on-wafer delays. A short, but fixed one is given by the physical transmission delay. It takes in the order of a few milliseconds biological time for a spike to round trip from neuron to neuron on a single HICANN and a speedup of  $10^4$  (Kleider, 2014). In the future, configurable delays can be implemented using the Layer 2 off-wafer network described further below.

#### 1.5.1 Merger Tree

The merger tree, as shown in Figure 1.3, can merge events from different sources into fewer connections to use the Layer 1 routing resources more efficiently. The 6 bit address space provided by the Layer 1 fabric allows to transmit events from up to 64 sources in a single shared connection. In order to distinguish them on the receiving side, sources must have disjoint addresses. The number of spike sources is reduced, for example, whenever neighboring circuits are combined to build larger neurons, i.e., if always 4 circuits are combined only 16 sources exist per neuron block, see Section 1.4.1. Additionally events from the on-chip background generators and external FPGAs can be merged.

The 512 neuron circuits on HICANN are grouped in 8 blocks of 64 neurons, with 32 from the top and bottom synapse array each. In the top most tier, every merger receives events from one block of neurons and one background generator. Background

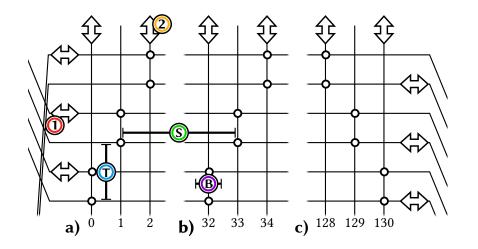

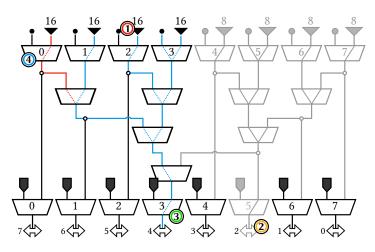

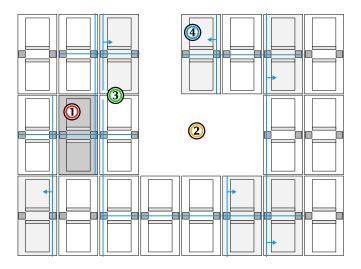

Figure 1.4: Three cutouts of the HICANN crossbar responsible for connecting horizontal and vertical Layer 1 buses. Cutouts **a**) and **b**) illustrate the topology found on the left side of chip and **c**) on the right. The switch layout is mirrored along a vertical axis through the center of the chip. Horizontal repeaters (1) refresh signals for every odd bus address on the left and every even address on the right. Similarly, vertical repeaters (2) refresh signals on every other bus on either the top or bottom of the chip. The sparse matrix can be characterized by three parameters: sparseness (S), offset (T) and block width (B). The respective parameters for the HICANN crossbar are  $S = 32, T = \pm 2, B = 1$ , with + and - for the left and right side, respectively.

generators can be configured to generate either random Poisson spikes at a given rate or elicit periodic events. They are typically used to lock repeater delay-locked loops (DLLs) and are not available for model emulation as explained in Section 1.5.5. Then, 23 mergers are connected in five subsequent tiers according to Figure 1.3. Any merger instance can be configured to forward events from either its left or right input or merge both. In the latter case, the left input is statically prioritized. At the bottom most tier, so-called DNC mergers interface external DNCs (Scholze et al., 2011a,b) that are in turn connected to FPGAs. DNC mergers can therefore combine chip-local events with events from external FPGA spike sources. Furthermore, events can be routed off-wafer to DNCs and FPGAs, where they are timestamped and recorded, respectively. Finally, DNC mergers relay events into the Layer 1 network via special SPL1 repeaters located on every eighth horizontal bus, which corresponds to the bus indices 6, 14, 22, 30, 38, 46, 54, 62.

## 1.5.2 Buses, Crossbars and Repeaters

Connectivity between HICANNs is established via an orthogonal grid of 64 horizontal and 256 vertical buses per chip. This bus topology is clearly visible on the micro photograph in Figure 1.2. Horizontal buses run along the center of the chip, while vertical buses run along both sides.

#### 1 The Neuromorphic Platform

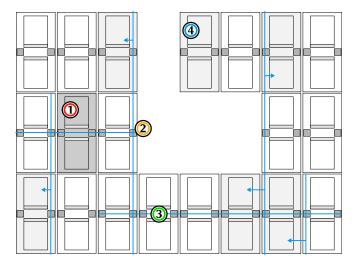

Figure 1.5: An illustration of the HICANN select switches (1), which connect vertical Layer 1 buses and synapse drivers (2). Synapse drivers can relay events into the synapse array (3) from both sides. Switches in every other row connect to synapse drivers on adjacent HICANN chips (4). The select switch topology is characterized by S = 16,  $T = \pm 2$  and B = 4, as defined in Figure 1.4.

Long range communication requires repeaters to refresh events at least once every chip boundary crossing (Schemmel et al., 2008). Repeaters exist for both, vertical and horizontal buses. They are located in alternating order at the top or bottom and left or right edge of the chip, respectively, according to Figure 1.4.

Every 8th horizontal repeater is an SPL1 repeater. These special repeaters can also relay input from the chip-local merger tree as explained in Section 1.5.1. Moreover, horizontal and vertical bus indices are shifted by two at the chip boundaries, which is referred to as bus swap. Thus, SPL1 repeaters on neighboring chips are not directly connected. Adjacent chips can therefore insert events into the Layer 1 network without interfering with each other, making the event routing more flexible.

Crossbars on the left and right side of each chip establish connectivity between horizontal and vertical bus segments. Their switch configuration is sparse to limit capacitive load on the one hand and use the remaining chip area for the interleaving of digital logic on the other (Grübl, 2014a). Consequently, not any two orthogonal buses can be connected. Figure 1.4 depicts the sparse matrix pattern of the HICANN crossbar, which is characterized by three parameters: sparseness S, offset T and block width B. A switch exists for vertical bus x and horizontal bus y if

$$E(x,y) = \left(x + B\left\lfloor \frac{y}{T} \right\rfloor\right) \mod S < B \tag{1.4}$$

evaluates as true.

## 1.5.3 Select Switches and Synapse Drivers

Whenever a route reaches a chip containing target neurons, events have to be relayed into the synapse arrays. For this purpose, vertical buses can be connected horizontally to synapse drivers via select switches as shown in Figure 1.5. The topology allows to connect each vertical bus to 14 drivers on the same and 14 drivers on the adjacent chip.

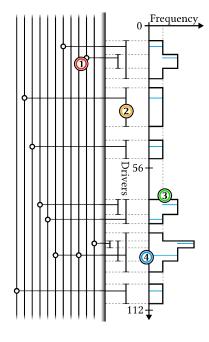

Figure 1.6: The two-stage driver and synapse address decoding scheme. Active signal and address buses are colored in red and blue, respectively. Layer 1 events (6 bit) enter the synapse array via synapse drivers (1). They can receive input either directly from a vertical bus or an adjacent driver. Local 2 bit decoders (2) control strobe lines to selectively activate synapses according to the A, B, C, D pattern. Additionally, drivers generate a rectangular voltage pulse (3) that is sent horizontally into the synapse array together with the remaining 4LSB of the address (4). Active synapses (5) connect horizontal and vertical lines whenever the address and a local 4 bit decoder value match.

Half of the drivers are located in the top synapse array, the other half in the bottom. Beyond direct Layer 1 input, adjacent drivers can be connected to share common input. This feature is explained in more detail in the subsequent section.

## 1.5.4 Synapse Arrays

On HICANN, 224 drivers, 56 on each side of each synapse array (see Figure 1.2), can relay events from vertical Layer 1 buses into the synapse arrays. Every driver operates two rows of 256 synapses each and receives input either directly from a vertical bus or shares a common input with adjacent drivers. The latter yields less capacitive load compared to relaying events directly from vertical buses to several individual drivers. High load deteriorates signal quality, as explained in Section 1.5.5. Thus, sharing inputs allows to connect more synapse drivers and therefore map a larger address space according to the address decoding scheme explained in the following.

In order to route the 6 bit events from the up to 64 sources, synapse drivers and synapses implement a two-stage address decoding scheme, which is illustrated in Figure 1.6. This scheme provides a trade-off between flexibility and area covered by the synapse in order to implement a larger number of synapses per chip.

Whenever an event arrives at the synapse driver, the two most significant bits (MSBs) of the 6 bit address are compared by four local decoders. They control strobe signals to selectively activate synapses in the top and bottom row as well as odd and even neuron columns, resulting in the A, B, C, D pattern in Figure 1.6. Only active synapses are vertically connected to neuron circuits and can therefore relay spike signals. If any of the decoder values matches, the synapse driver generates a rectangular voltage pulse and sends it horizontally into the synapse array alongside the remaining four

#### 1 The Neuromorphic Platform

address bits. The integral of the voltage pulse determines the synaptic base efficacy. The pulse amplitude is a fixed parameter controlled per driver, whereas the pulse length is modulated dynamically to implement STP, see Section 1.4.2.

Active synapses decode the remaining least significant bits (LSBs) of the address and compare them against a configurable local value. If the address matches, row and column are connected and a current pulse is generated, which is sent vertically towards the neuron circuit in the corresponding column via one of two collector lines. The amplitude of the current pulse is controlled by two factors: the integral of the incoming voltage pulse and a local 4 bit digital synapse weight. Note that the collector line connectivity is configured per synapse row and therefore shared by synapses A and B as well as C and D.

Every neuron has two synaptic input circuits, one per collector line. They translate incoming current pulses from any of the 224 synapses within their column into exponential conductance courses that connect the neuron to a configurable reversal potential (HBP SP9, 2014). Depending on the input configuration, the generated PSPs can either be excitatory or inhibitory.

#### 1.5.5 Transmission Reliability

The Layer 1 network is merely a link layer according to the OSI layer model (ISO/IEC 7498-1:1994, 1994). The unidirectional communication is inherently unreliable because transmissions cannot be acknowledged by the receiver. Therefore, no transport layer protects events from being lost. Instead, the network topology and parameters have to be chosen carefully in order to optimize transmission reliability.

Firstly, repeaters and synapse drivers require periodic address 0 events, in order to lock local DLLs. Hence, background generators are set up to provide the necessary activity. These events carry no information and are usually ignored on the receiving side by setting the decoders accordingly. Empirically, rates around 3 Hz in the biological time domain (BTD) are sufficient to retain an established lock (Koke, 2014), however, optimal strategies to acquire the initial lock are under investigation, as of May 2014.

Furthermore, a set of analog parameters ( $V_{\text{ccas}}$ ,  $V_{\text{OH}}$  and  $V_{\text{OL}}$ ) determines transmission properties like power consumption, reliability and delay. Optimal values are subject to calibration. However, within the scope of this thesis it is assumed that the default values work for most experiments. A listing of all corresponding parameters and their default values can be found in Appendix A.2.

Finally, the capacitive load acceptable between repeaters is limited. Connecting components increases the wire capacitance and therefore RC time constants, which deteriorates the digital signal quality. For every Layer 1 bus segment no more than one crossbar and select switch per chip must be set. Similarly, only a limited number of synapse drivers can be connected to vertical buses. This concerns both, primary drivers, which are connected directly to a vertical bus, and drivers connected via neighbors. However, the latter produces less load. Early measurements by Kononov (2011) indicated that for Layer 1 clock frequencies of 100 MHz to 150 MHz up to

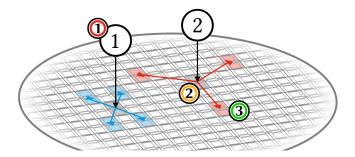

Figure 1.7: Illustration of the post-processing metal layer deposited as part of the wafer-scale integration. An uncut 20 cm wafer contains 48 reticles with 8 HICANN chips each (1). Every post-processed chip (2) provides stripe connector pads (3) to implement off-wafer connections to the main printed circuit board (PCB) and FPGAs. Deposited vertical (4) and horizontal interconnects realize Layer 1 on-wafer connectivity across reticle boundaries.

4 connected neighboring synapse drivers worked reliably in more than  $97\,\%$  of the measurements conducted using the first version of the HICANN chip.

## 1.6 Wafer-Scale Integration

One of the major challenges for implementing accelerated, large-scale neural networks is to provide the necessary connectivity. In biology, neurons typically receive input from  $10^4$  to  $10^5$  other neurons (Drachman, 2005). Assuming a speedup factor of  $10^4$ and an average biological firing rate of 10 Hz this corresponds to an input bandwidth requirement of 1 to 10 GEvents/s per neuron. The cumulative input bandwidth per chip is even higher because different neurons likely receive different input. Wafer-scale integration is the key technique, used for the HMF, to implement the high-bandwidth Layer 1 as well as the off-wafer Layer 2 network described in Section 1.5 and Section 1.7, respectively. Photos of the technical realization are shown in Figure 1.7.

After fabrication, the wafer containing the 384 HICANNs is left intact. A subsequent post-processing deposits metal inter-connectors on the surface, see Figure 1.7 item 4. Therefore, connectivity can be established beyond reticle boundaries, which denotes the connected area captured by a single lithography mask. The high integration density reduces wire impedance leading to more energy efficient systems. Furthermore, off-wafer communication can be established vertically over the whole wafer area by means of deposited connector pads, see Figure 1.7 item 3. These pads are connected to the main PCB of the wafer system via stripe connectors (Zoglauer, 2009).

On the downside, wafer-scale integration causes random defects, resulting from impurities in the manufacturing process, to remain in the system (Stapper et al., 1983). In normal production, a wafer is cut into individual chips, their quality assessed and unsuitable ones dismissed. However, this not an option for wafer-scale systems, instead

#### 1 The Neuromorphic Platform

they need to be tolerant against such defects. The HMF allows to workaround most localized defects via appropriate configurations. For example, Layer 1 connections that would normally pass through a defect region can be routed differently. As a measure of last resort, whole reticles can be cut from power to avert e.g., shorts that otherwise impede the operation of the remaining reticles. Efficiently finding configurations that workaround defects and handle imperfections is important for experiment reproducibility and one of the central issues of this thesis.

## 1.7 Off-Wafer Communication

Beyond recurrent connectivity, neural network experiments require external spike stimulation, the ability to record spike responses and host communication to operate the system. The Layer 2 off-wafer network provides all necessary means. The infrastructure is provided by a hierarchy of host computers connected to FPGAs over ethernet, which are in turn connected to custom DNCs. Every wafer module hosts 12 FPGAs, with four DNCs each. A single DNC is responsible for managing the communication for eight HICANN chips. The Layer 1 and Layer 2 networks interface at the bottom layer of the merger tree as explained in Section 1.5.1. For clock frequencies of 100 MHz, the bandwidth between a DNC and a single HICANN is 25 MEvents/s.

## 1.7.1 Real-Time Spike Handling

External stimulation and spike recording require high-bandwidth communication to cope with the  $10^3$  to  $10^5$  speedup factor of the analog neurons. Therefore, spike input trains are prepared in DRAM on an FPGA board prior to the experiment to achieve high throughput and avoid timing jitter caused by packet delivery over ethernet or process scheduling on the host. Each FPGA can store up to  $2.5 \times 10^8$  events in memory (Grübl, 2014b). Real-time host communication is possible, but with lower throughput and no deterministic timing. Similarly, spike output is recorded to DRAM on the FPGA board and accessed by host computers after the experiment.

Future FPGA firmware versions are going to provide programmable spike delays via the Layer 2 network. Spikes are therefore routed off wafer, buffered in the FPGA and reinserted into the Layer 1 network after a configurable delay has been elapsed.

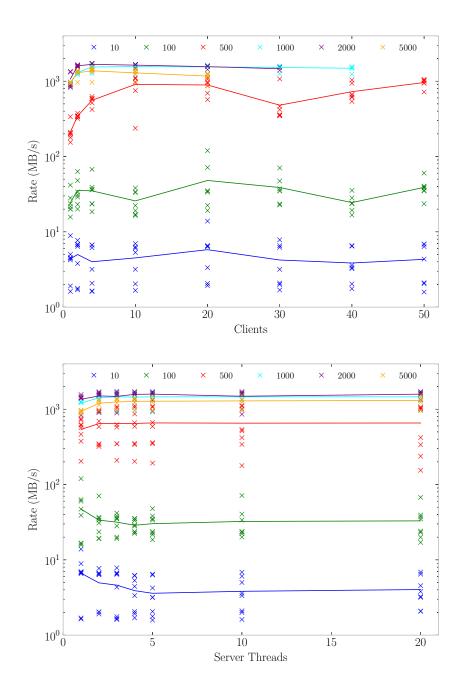

## 1.7.2 Host Communication

Communication between wafer system and the conventional computer cluster is necessary for the initial hardware setup, the subsequent readout of results and interactive experiments. Wafers are therefore connected to an top-of-rack ethernet switch via 12 FPGAs with  $2 \times 1$  Gbit uplinks each. A 10 Gbit ethernet backbone switch aggregates connections from the host computers and the wafer switches. This simple but efficient fat tree topology (Leiserson, 1985) allows communication between any host and FPGA with low latency and high bandwidth. An automatic-repeat-request transport layer protocol (Philipp, 2008; Schilling, 2010) similar to PGM (Speakman et al., 2001) provides reliable communication between FPGAs, DNCs and HICANNs on top of the link layer. Packets lost in transfer are resent after a configurable timeout.

Notably, close-loop experiments and system operation have different performance requirements. Experiment setup and result collection demand high bandwidth, whereas closed-loop experiments require low-latency communication to deliver spike responses within short periods of time. For example, 1 ms of biological time corresponds to  $0.1 \,\mu s$  in the hardware time domain (HTD) for a speedup of  $10^4$ . To realize biologically relevant delays of 10 ms to 100 ms, the system has to respond in less than 10  $\mu s$ , which is challenging in gigabit ethernet terms (Loeser and Haertig, 2004).

## **1.8 Future Deployments**

Within the BSP a system of six wafer modules is built until the end of 2014. Beyond that, another 20 wafer system is built during the first 18 month of the Human Brain Project (HBP) (HBP SP9, 2014). This system is going to provide access to almost  $4 \times 10^6$  accelerated neurons in a system that has an expected power consumption of  $30 \,\mathrm{kW}$ .

An updated 65 nm HICANN successor, ready for production use, is planned for month 30 of the HBP. The new system is going to further improve power efficiency, provide higher bandwidths and implement advanced plasticity mechanisms including a general purpose plasticity processor (Friedmann, 2013).

## 2 A Scalable Workflow for Neuromorphic Computing

The HMF is a powerful but complex computational platform. Development and operation mandate constant monitoring by hardware experts. In order to make its resources available for a broader range of users, a scalable, multi-user workflow is required. Furthermore, batch processing enables the system to work more economically. This chapter proposes a workflow design for the platform and presents a prototype implementation thereof.

Firstly, the existing HMF workflow is introduced, followed by the workflow redesign including brief discussions on all major components. Subsequently, an experiment broker prototype is presented, which is responsible for accounting, dispatching jobs and tying together the other workflow components. The chapter closes with a measurement of experiment throughput for the prototype implementation.

The workflow and prototype implementation presented in this chapter have been developed by Eric Müller and the author.

## 2.1 Existing Workflow

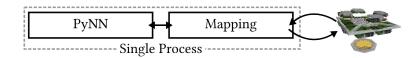

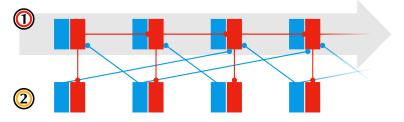

The previously existing HMF workflow has been developed as part of the Fast Analog Computing with Emergent Transient States (FACETS) project. It started as a fork of the Spikey workflow, which has been the first neuromorphic hardware system to feature an abstract PyNN interface (see Section 3.1; Davison et al., 2008; Brüderle et al., 2009). Though, the underlying hardware is different and the translation of neural networks into hardware configurations had to be redesigned in order to cope with the different topology and increased complexity of the system. However, the simple single-user workflow design as sketched in Figure 2.1 remained unchanged. A more detailed introduction is given by Brüderle et al. (2011).

The existing workflow mainly consists of three steps. Firstly, an abstract representation of the PyNN neural network is set up. Secondly, a corresponding hardware configuration is derived from the abstract representation in a process referred to as *mapping* throughout this thesis. The mapping has to find configurations that closely resemble the intended network models within the constraints of the hardware system. Finally, the hardware is configured, the experiment conducted and the results are retuned to the user in PyNN format. The workflow runs in a single process on a single computer and requires privileged, direct access to the wafer system. Although this

### 2 A Scalable Workflow for Neuromorphic Computing

Figure 2.1: The existing HMF single user, single process workflow. PyNN directly controls the mapping process, which is responsible for both, translation of the abstract neural network into a corresponding hardware configuration and experiment execution. The workflow requires immediate and privileged access to the hardware platform.

mode of operation is also supported by the redesign, a more elaborate workflow has to be established to utilize available resources to full capacity and allow multiple users to access the HMF in parallel.

## 2.2 Workflow Redesign

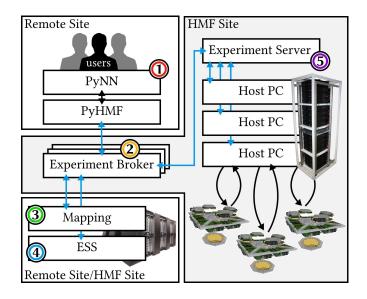

The HMF is a complex platform that requires constant monitoring by hardware experts, similar to conventional computer clusters. This mandatory overhead suggests the use of batch processing to provide simple access for many users and increase resource utilization. In fact, multi-user remote access for project partners is requested by the HBP. The original workflow has never been designed for this use case. Consequently, a redesign became necessary to deal with the up-to-date requirements. The redesigned workflow is presented in Figure 2.2.

Users only need the PyHMF client installed on their local computers to run PyNN scripts. The client transparently handles model construction, serialization and communication with an experiment broker at the HMF site. There, the model is translated into a hardware configuration, which in-turn is scheduled for execution on either the ESS (see Section 2.2.5) or the wafer-scale system. After completing the run, the experiment server collects the results from the host computers and translates them into the biological model domain. Finally, the results are relayed via the experiment broker back to the user. Note that the new approach is PyNN-compatible and allows users to easily switch between different simulation backends, the only difference is that experiments are conducted remotely in the HMF case.

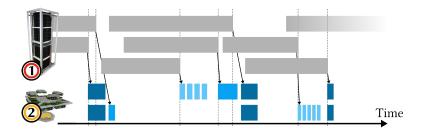

## 2.2.1 Batch Processing

Non-interactive batch processing is used for conventional computer clusters to increase resource utilization (Kubo, 1999). Analogously, batch processing allows to used conventional and neuromorphic resources more economically. Figure 2.3 shows how multiple mapping jobs from different users or from parameter sweeps can be processes by the HMF cluster in parallel using available batch systems. For example, generating hardware configurations is typically slow compared to the actual hardware experiment

Figure 2.2: The redesigned HMF workflow. Users (1) execute PyNN experiments using the PyHMF client, which serializes the network model and sends it to an experiment broker at the HMF site (2). A mapping of the network model to a hardware configuration is subsequently scheduled on the cluster (3). When the broker receives the mapped configuration and the requested resources are available, the experiment is either simulated on the ESS (4) or emulated on the wafer system (5). Afterwards, the results are translated into the biological model domain by the experiment server and sent back to the user. Note that inter process communication (IPC) between components is indicated by blue arrows.

due to the high analog speedup factor. Thus, scheduling available configurations from concurrent mappings in a second batch queue increases hardware utilization.

## 2.2.2 High-Level User Interface

The computational resources of the HMF can be accessed by authorized users via the PyHMF client. It provides a PyNN-compatible (PyNN, 2014) application programming interface (API) to construct neural network representations that can be serialized and sent to the remote experiment broker. Chapter 3 discusses both, PyNN and PyHMF, in more detail.

The redesign uses native PyNN API to dispatch jobs rather than additional interfaces or remote shell access. This design may enable future PyHMF versions to capture parameter sweeps and therefore map this series of experiments more efficiently than unrelated experiments dispatched as individual jobs. Nonetheless, remote shell access can be provided because PyHMF is equally well suited for local access.

The client-server architecture in the redesign further simplifies the distribution and maintenance of software for users and developers alike. Compared to the previous approach, users need only a small fraction of the software stack, namely the hard-

#### 2 A Scalable Workflow for Neuromorphic Computing

Figure 2.3: Experiments on the accelerated neuromorphic system typically take little time due to the high speedup factor. Preparing configurations for multiple experiments and users in parallel helps to utilize the system to its capacity. Both, conventional (1) and neuromorphic (2) resources are scheduled following a batch approach. Parameter sweeps, single and multi-wafer experiments are shown in light, mid and dark blue, respectively.

ware independent PyHMF client. Server-side software and hardware deployments are maintained independently by the developers and hardware experts. Moreover, the same client can be used to transparently access different hardware backends or future hardware revisions. Currently, the client supports access to the wafer system and the ESS.

#### 2.2.3 Experiment Broker

The experiment broker is the central communication hub, which is responsible for connecting all endpoints and progressing experiments.

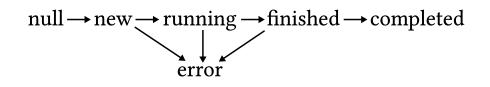

When the broker receives a PyHMF experiment from an authorized user, it creates a local job, spawns a mapping process and relays the network description. The broker keeps track of pending requests. Experiments are expected to take in the order of minutes to hours depending on the load of the HMF. It is therefore necessary to cope with repeated client disconnects and reconnects. After the mapping is completed, the configuration is forwarded to the requested backend i.e., an HMF experiment server or the Executable System Specification (ESS). The broker finally relays experiment results back to the user.

Several brokers can operate in parallel to distribute the work, either at different public addresses or behind load balancers (Bowman-Amuah, 2003). Distributing the load onto several brokers also improves availability by avoiding single points of failure (Piedad and Hawkins, 2001).

#### 2.2.4 The Mapping

The mapping is responsible for translating abstract neural network descriptions into corresponding hardware configurations. The new workflow reassigns many of the tasks previously part of the mapping in order to modularize the system. Flow control, in particular, is now a responsibility of the experiment broker and experiment server. Still, the mapping task is algorithmically the most complex problem and key for high hardware utilization. The mapping step is a central topic of this thesis and discussed in Chapters 5 to 8.

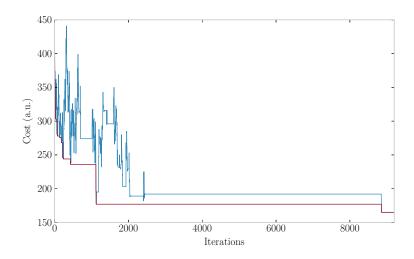

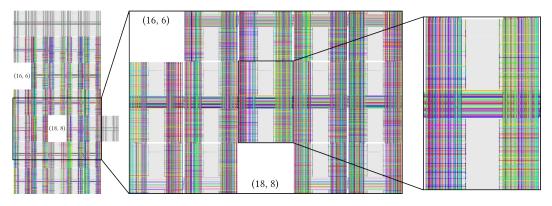

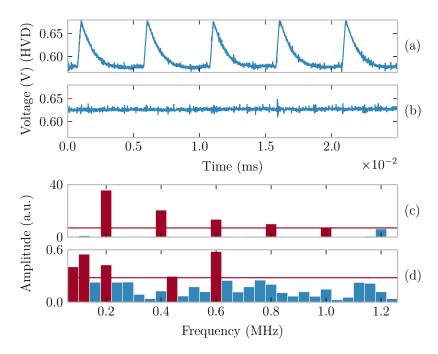

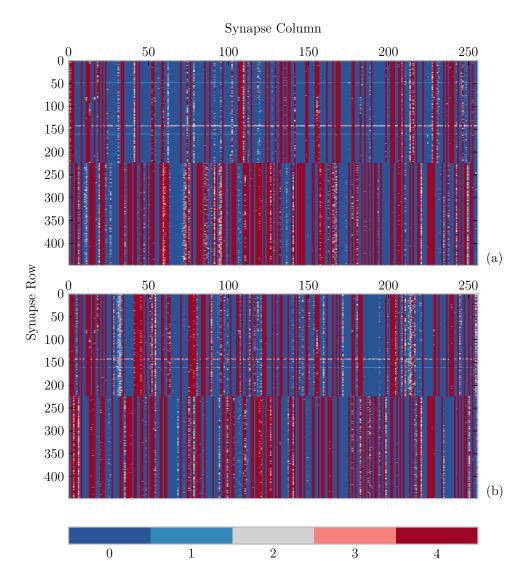

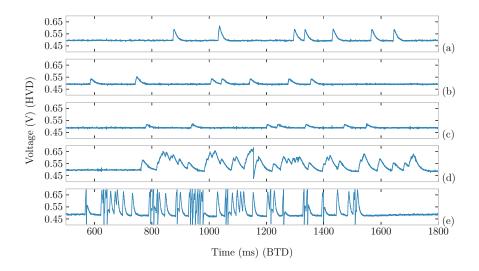

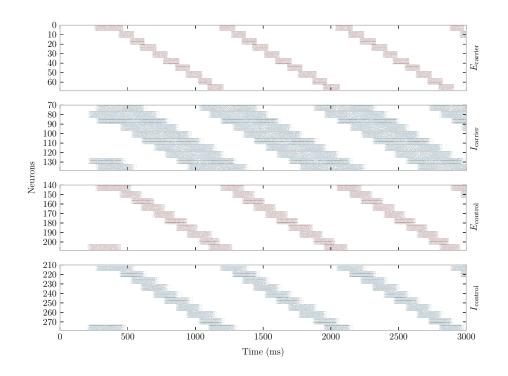

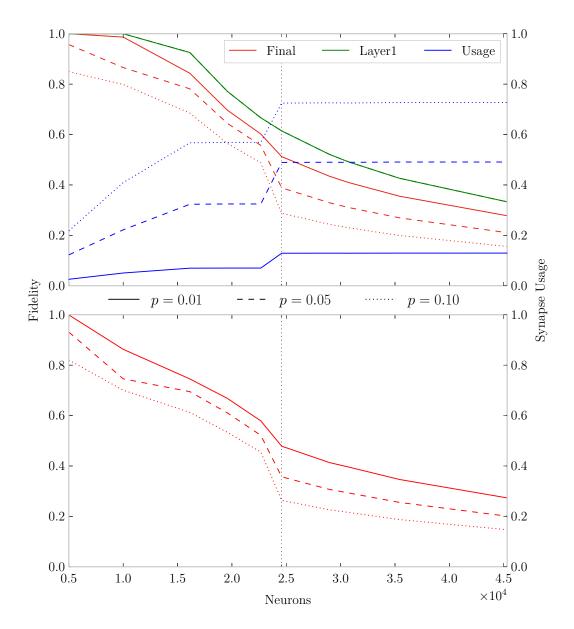

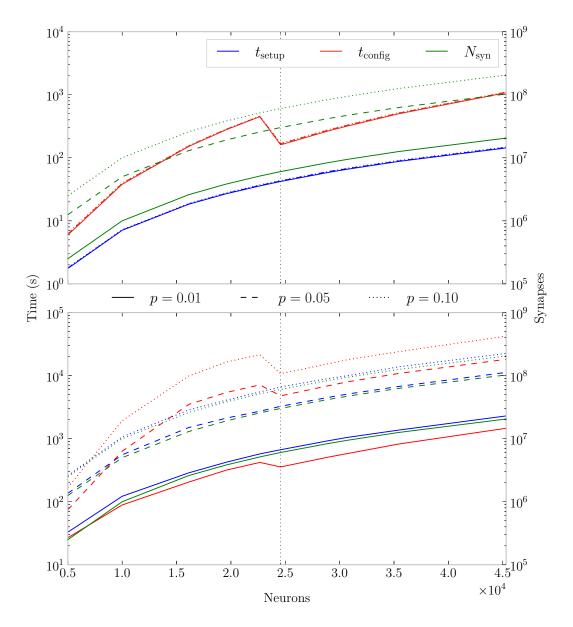

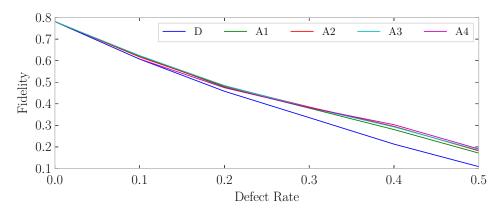

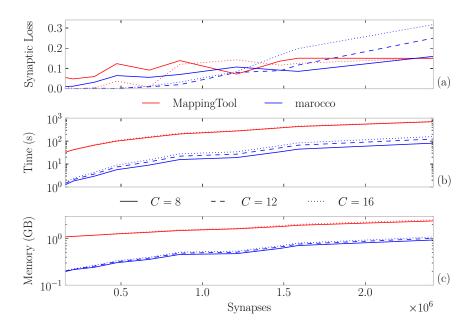

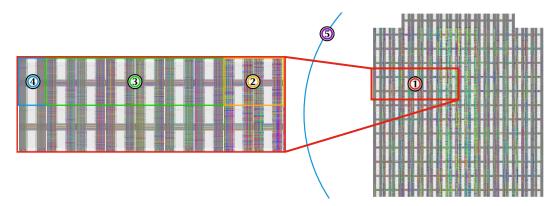

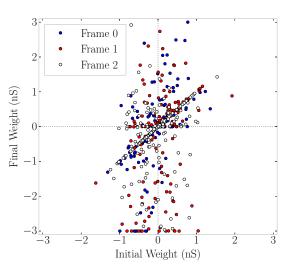

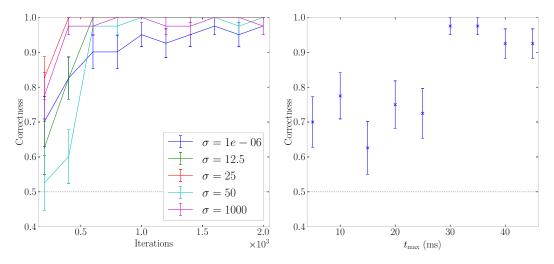

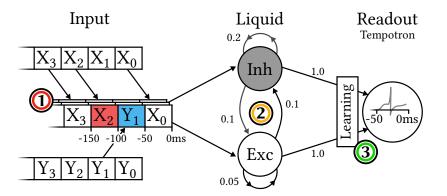

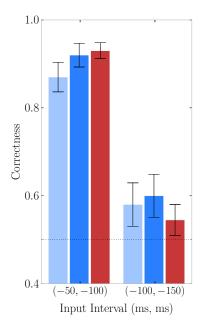

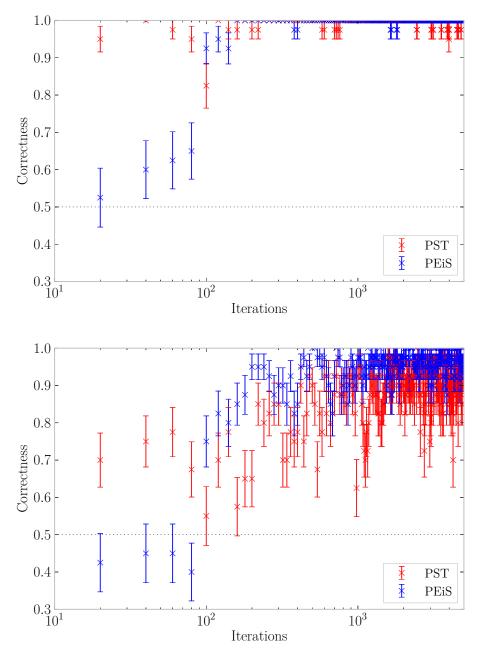

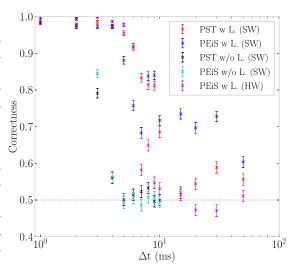

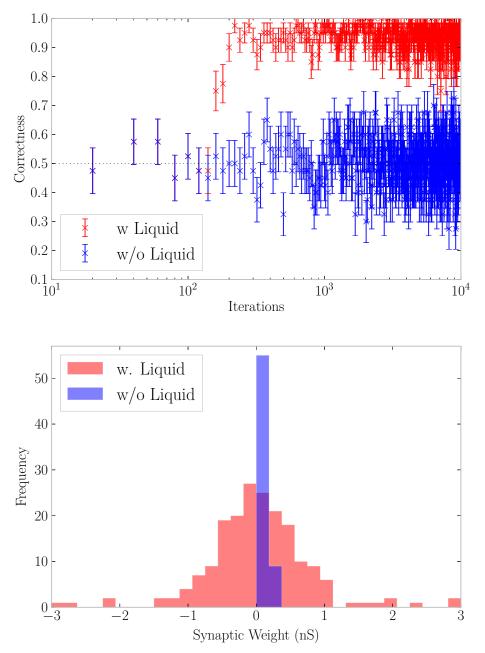

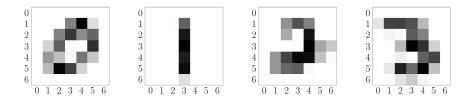

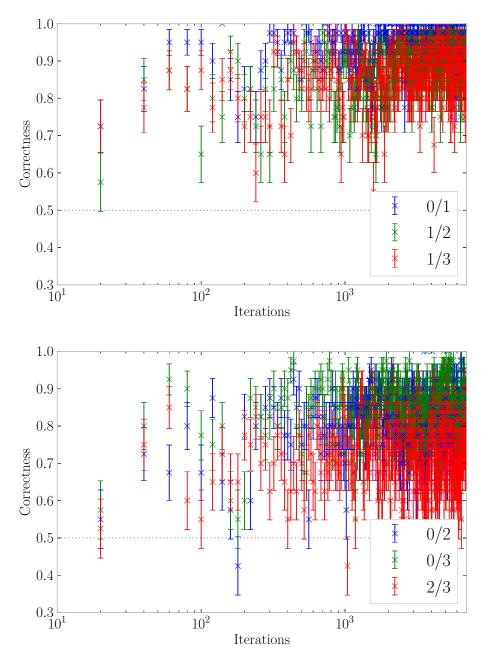

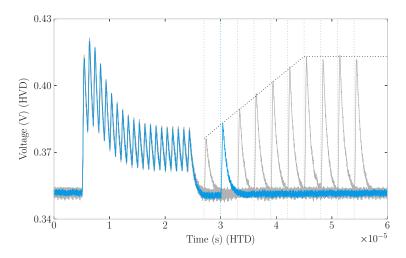

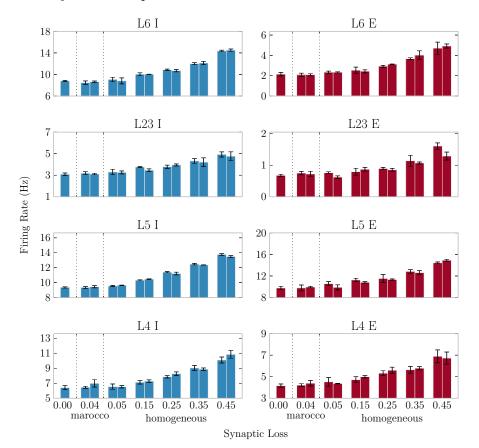

## 2.2.5 Executable System Specification