## RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

KIRCHHOFF-INSTITUT FÜR PHYSIK

## Fakultät für Physik und Astronomie

## Ruprechts-Karls-Universität Heidelberg

Diplomarbeit Im Studiengang Physik

Vorgelegt von **Dominique Kaiser**Aus Konstanz

April 2002

# Der Readout-Merger des Präprozessors des ATLAS Level-1 Kalorimeter Triggers

Die Diplomarbeit wurde ausgeführt von Dominique Kaiser am Kirchhoff-Institut für Physik der Universität Heidelberg unter Betreuung von Herrn Prof. Dr. Karlheinz Meier

# Der RemFPGA des Präprozessors des ATLAS Level-1 Kalorimeter Triggersystems

Thema dieser Arbeit ist der Entwurf und die Entwicklung des Readout-Mergers für den Präprozessor des Level-1 Kalorimeter Trigger des ATLAS-Detektors. Dieser Baustein des Präprozessors wird mit Hilfe FPGA Technologie realisiert. Aufbauend auf den Resultaten des Tests eines Prototyps wurde ein vollständig neues Design entworfen.

Die Aufgabe des so genannten RemFPGA ist die Steuerung und Konfiguration aller anderen Komponenten des Präprozessormoduls wie auch die Kompression und Weiterleitung von Readout-Daten des Präprozessors. Bei dem FPGA handelt es sich um einen Virtex-E 1000 der Firma Xilinx. In der HDL-Sprache Verilog wurde ein komplettes Design für diesen FPGA-Baustein entwickelt und mit Hilfe von Software-Simulationswerkzeugen ausgiebig getestet. Der erstellte Programmcode ist modular aufgebaut, um Anpassungen an zukünftige Gegebenheiten zu erleichtern.

Für die effektive Übertragung der anfallenden Readout-Daten wurde ein in früheren Arbeiten entwickeltes Kompressionsverfahren wesentlich verfeinert und weiterentwickelt.

# The RemFPGA of the pre-processor of the ATLAS Level-1 Calorimeter trigger system

Subject of this work is the planning and implementation of the Readout-Merger that is to be used by the pre-processor of the Level-1 Calorimeter Trigger of the ATLAS-Detector. This part of the pre-processor is to be carried out with the help of FPFA technology. Based on the results of research done in the past with a prototype a totally new design was developed.

The RemFPGA is to control and configure all other components of the pre-processor module as well as to compress and transfer Readout data produced by the pre-processor. The used FPGA is a Virtex-E 1000 from Xilinx. Using the HDL language Verilog a complete design was developed for this FPGA chip und subsequently it was tested thoroughly with the help of software simulation utilities. The produced Sourcecode is very modular to allow easy and effortless adjustments to changed conditions in the future.

To allow for effective transfer of the accumulating Readout data an existing compression schema was refined and improved significantly.

## Inhaltsverzeichnis

| E | inleitung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                      |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1 | LHC und das ATLAS Experiment  1.1 Physikalischer Kontext  1.1.1 Das Standardmodell  1.2 Der Large Hadron Collider LHC  1.3 Das ATLAS-Experiment  1.3.1 Der Innere Detektor  1.3.2 Das Kalorimeter  1.3.3 Das Myon-Spektrometer                                                                                                                                                                                                                                                                                              | 3<br>8<br>8                            |

| 2 | Das ATLAS Triggersystem  2.1 Der Level-1 Trigger  2.1.1 Der Trigger des Kalorimeters  2.1.2 Der Myontrigger  2.1.3 Der Central Trigger Prozessor  2.2 Der Level-2 Trigger  2.3 Der Eventfilter                                                                                                                                                                                                                                                                                                                              | 12<br>13<br>13                         |

| 3 | Der Level-1 Kalorimetertrigger Präprozessor  3.1 Aufgaben des Präprozessors  3.2 Design des Präprozessorsystems  3.2.1 Die Struktur des Präprozessormoduls (PPM)  3.2.2 Das TTC-Modul  3.2.3 Der Crate-Controller des Präprozessorsystems  3.2.4 Der Readout-Driver des Präprozessorsystems  3.3 Schnittstellen des RemFPGA  3.3.1 Das I <sup>2</sup> C Protokoll  3.3.2 Das SPI-Protokoll  3.3.3 Die serielle Schnittstelle des PPrASIC  3.3.4 Die Schnittstelle zum VME-CPLD  3.3.5 Das Pipelinebus Protokoll des RemFPGA | 18<br>22<br>23<br>24<br>24<br>27<br>28 |

| 4 | Field Programmable Gate Arrays FPGA 4.1 Technischer Hintergrund. 4.1.1 Grundstruktur eines FPGA 4.1.2 Der Virtex-E von Xilinx Inc. 4.1.3 Der Entwicklungsprozess                                                                                                                                                                                                                                                                                                                                                            | 37<br>38                               |

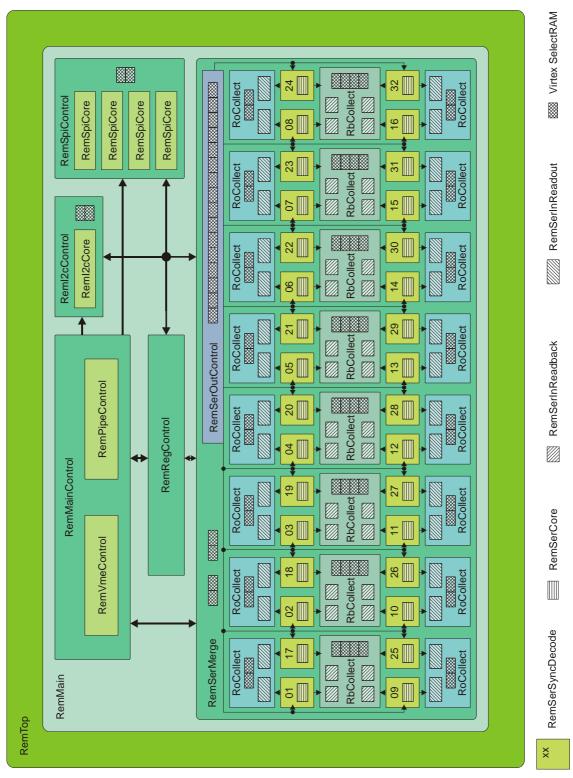

| 5 | Der Readout-Merger FPGA (RemFPGA)  5.1 Grundsätzliche Aufgabenstellung 5.1.1 Notwendigkeit der Kompression der Readout Daten  5.2 Design des RemFPGA Programmcodes  5.3 Module des RemFPGA 5.3.1 RemSerCore 5.3.2 RemSerSyncDecode 5.3.3 RemSerInReadout 5.3.4 RemSerInReadout 5.3.5 RemSerRoCollect 5.3.6 RemSerRbCollect 5.3.7 RemSerOutControl 5.3.8 RemSerMerge                                                                                                                                                         | 40<br>42<br>42<br>43<br>45<br>45       |

|    | 5.3.9 RemI2cControl                                    | 47        |

|----|--------------------------------------------------------|-----------|

|    | 5.3.10 RemSpiCore                                      | 48        |

|    | 5.3.11 RemSpiControl                                   | 48        |

|    | 5.3.12 RemRegControl                                   | 48        |

|    | 5.3.13 RemVmeCore                                      |           |

|    | 5.3.14 RemPipeCore                                     |           |

|    | 5.3.15 RemMainControl                                  |           |

|    | 5.3.16 RemMain                                         |           |

|    | 5.3.17 RemTop                                          |           |

|    | 5.4 Schematische Illustration des Designs des RemFPGA  | 49        |

| 6  | Datenformate und Register des RemFPGA                  | 51        |

|    | 6.1 ReadOUT-Daten und ihre Kompression                 | 51        |

|    | 6.1.1 Untersuchte Kompressionsverfahren                |           |

|    | 6.1.2 Kompressionsverfahren des RemFPGA                | 53        |

|    | 6.1.3 Resultierendes ReadOUT Datenformat               |           |

|    | 6.2 ReadBACK-Daten                                     |           |

|    | 6.2.1 Format der Lookup-Tabelle des PPrASIC            |           |

|    | 6.2.2 Alle anderen ReadBACK-Daten.                     |           |

|    | 6.2.3 Resultierendes ReadBACK Datenformat              |           |

|    | 6.3 Serielle Datenausgabe an die PPrASICs              |           |

|    | 6.4 Datenformat für die I <sup>2</sup> C-Schnittstelle |           |

|    | 6.5 Datenformat für die SPI-Schnittstellen             |           |

|    | 6.6 Register des RemFPGA                               |           |

|    | 6.7 Verwendung des Pipelinebusses                      |           |

|    | 6.7.1 Die Befehle des Pipelinebusses                   |           |

|    | 6.7.2 Konfiguration der Pipelinebus Node Adresse       |           |

|    | 6.7.3 Datenauslese über den Pipelinebus                |           |

|    | 6.7.4 Dateneingabe über den Pipelinebus                |           |

|    | 6.7.5 Besonderheiten und Anwendungsbeispiel            |           |

|    | 6.8 Verwendung der VME-Schnittstelle                   |           |

|    | 6.8.2 Dateneingabe über die VME-Schnittstelle          |           |

|    |                                                        | / /       |

| 7  | $\boldsymbol{\omega}$                                  | <b>79</b> |

|    | 7.1 Synthese des RemFPGA                               |           |

|    | 7.1.1 Kompilation mit FPGA Compiler II                 |           |

|    | 7.1.2 Synthese des Designs                             |           |

|    | 7.1.3 Place-and-Route                                  |           |

|    | 7.2 Simulation und Test des RemFPGA                    | 81        |

| 8  | Zusammenfassung                                        | 91        |

|    | 8.1 Abschätzung der ReadOUT-Datenrate                  |           |

|    | 8.2 Fazit                                              |           |

|    | 8.3 Ausblick                                           | 94        |

| D  | anksagung                                              | 95        |

| Li | iteraturverzeichnis                                    | 97        |

## **Einleitung**

Im Rahmen der Grundlagenforschung der Physik werden immer detailliertere Modelle unseres Universums entwickelt. Diese Modelle und Theorien postulieren physikalische Vorgänge und Gesetzmäßigkeiten, die in "normalen" Experimenten nicht zugänglich und überprüfbar sind, da sie eine sehr hohe Energie der beteiligten und untersuchten Komponenten erfordern. Aus diesem Grund erfindet und baut die physikalische Forschung immer neue und leistungsfähigere Teilchenbeschleuniger, um in immer höhere Energiebereiche vordringen zu können. Auf Grund der so durchgeführten Experimente werden neue Erkenntnisse gewonnen und neue Theorien entwickelt. Diese benötigen für ihre Verifizierung jedoch in vielen Fällen neue Experimente bei noch höheren Energien.

Eine der momentan zu überprüfenden Theorien betrifft die Existenz des so genannten Higgs-Teilchens.

Mit aus diesem Grund wird in Genf am Institut für Hochenergieforschung CERN ein neuer Beschleuniger gebaut. Der *Large Hadron Collider* – LHC wird Protonen mit einer Energie von bis zu 7 TeV zur Kollision bringen. Mit Hilfe von vier komplexen Detektoren, die teilweise die Größe von mehreren Reihenhäusern übertreffen, werden diese Kollisionen untersucht. Einer dieser Detektoren ist der so genannte ATLAS-Detektor.

Selbst bei diesen extrem hohen Energien treten die gewünschten Ereignisse nur sehr selten auf. Ein Higgs-Teilchen wird beispielsweise nur bei einer von 10<sup>11</sup> Kollisionen erzeugt. Der Großteil der anderen Kollisionen erzeugt Resultate, die schon mit schwächeren Beschleunigern ausführlich untersucht werden konnten. Daher verfügen die Detektoren über ein Triggersystem, welches die interessanten Ereignisse identifizieren und zur weiteren Analyse extrahieren soll. Das Triggersystem des ATLAS-Detektors besteht aus drei Stufen. Jede Stufe verringert die zu verarbeitende und zu analysierende Datenmenge und ermöglicht somit den späteren Triggerstufen eine immer ausführlichere Analyse. ATLAS besteht aus mehreren verschiedenen Detektor-Untertypen, welche jeweils andere Messungen vornehmen. Daher bestehen die verschiedenen Triggerstufen auch aus mehreren verschiedenen Unterkomponenten.

Diese Arbeit beschäftigt sich mit einem Teil des so genannten Präprozessors des Level-1 Kalorimeter Triggers, also einem Teil der ersten Triggerstufe. Dieser Präprozessor arbeitet mit 7296 Messsignalen des Kalorimeter-Detektors. Er besteht aus einer Vielzahl von identischen Komponenten, genannt Präprozessormodule, welche jeweils 64 Messsignale verarbeiten.

Jedes dieser Module besitzt einen Baustein zur Steuerung aller Unterkomponenten dieses Moduls und zur Kommunikation mit der Außenwelt. Dieser so genannte Readout-Merger oder RemFPGA ist Gegenstand dieser Diplomarbeit.

Kapitel 1 erläutert die Motivation zum Bau des LHC und die grundlegende Funktionsweise des ATLAS-Detektors. Kapitel 2 erklärt die Funktion des ATLAS Triggersystems. Die Arbeitsweise des Präprozessorsystems wird in Kapitel 3 dargelegt. Kapitel 4 gibt einen Einblick in die für den RemFPGA verwendete Hardware. Kapitel 5 erläutert die Funktionsweise und das im Rahmen dieser Arbeit entwickelte interne Design des RemFPGA. Kapitel 6 beschreibt die Anwendung und Leistung des RemFPGA. Kapitel 7 widmet sich den Tests des entwickelten RemFPGA und Kapitel 8 fasst die Resultate dieser Arbeit zusammen und gibt einen Ausblick auf die weiteren Schritte in der Entwicklung des ATLAS Systems.

## Kapitel 1

## LHC und das ATLAS Experiment

Dieses Kapitel gibt einen Überblick über den physikalischen Kontext für den *Large Hadron Collider LHC* und das *Atlas*-Experiment (<u>A Toroidal LHC Apparatus</u>) entwickelt wird und das Experiment selbst.

## 1.1 Physikalischer Kontext

Die fundamentale Beschreibung unserer Welt und des Universums folgt letztendlich aus dem theoretischen Grundgerüst, welches die fundamentalen Teilchen und ihre Interaktionen beschreibt. Dieses Grundgerüst wird zurzeit durch das so genannte *Standardmodell* repräsentiert.

#### 1.1.1 Das Standardmodell

Das Standardmodell ist das Resultat von ca. 50 Jahren theoretischer und experimenteller Forschung in der Teilchenphysik. Die immer genaueren und neuen experimentellen Befunde der letzten Jahrzehnte konnten letztlich immer mit dem Standardmodell erklärt werden oder das Modell konnte an die neuen Ergebnisse durch Verfeinerungen angepasst werden.

Das Standardmodell vereinheitlicht drei der vier elementaren Wechselwirkungen: Die starke, die schwache und die elektromagnetische. Die Gravitation ist nicht einbezogen, da sie zu schwach ist, um auf die bisher durchgeführten Experimente eine messbare Auswirkung zu haben.

Bis heute wurde noch kein einziges eindeutiges Resultat eines physikalischen Experiments gefunden, welches das Standardmodell widerlegen könnte. Dieser Abschnitt soll lediglich einen groben Überblick vermitteln und auf Schwächen des Standardmodells hinweisen.

#### **Fundamentale Teilchen**

Es gibt zwei grundsätzliche Klassen fundamentaler Teilchen. Es gibt Fermionen (Spin ½) und Vektorbosonen (Spin 1). Dabei vermitteln die Vektorbosonen die drei Grundkräfte, indem sie zwischen Teilchen ausgetauscht werden. Die Fermionen unterteilen sich weiter in Quarks und Leptonen. Diese Fermionen kann man anhand der aufsteigenden Masse der Teilchen in drei so genannte Familien oder Generationen einordnen.

| Vektorbosonen     |                 |                                                                       |          |                   |  |  |  |

|-------------------|-----------------|-----------------------------------------------------------------------|----------|-------------------|--|--|--|

| Wechselwirkung    | koppelt an      | Тур                                                                   | Masse    | rel. Stärke       |  |  |  |

| stark             | Farbe           | 8 Gluonen                                                             | 0        | 20                |  |  |  |

| elektromagnetisch | el. Ladung      | Photon                                                                | 0        | 1                 |  |  |  |

| schwach           | schwache Ladung | $\mathrm{W}^{\scriptscriptstyle\pm},\mathrm{Z}^{\scriptscriptstyle0}$ | ~ 100GeV | $10^{-7}$         |  |  |  |

| Gravitation       | Masse           | Gravitron                                                             | 0        | 10 <sup>-36</sup> |  |  |  |

|      | Quarks  |        |         |             | Lepto   | onen   |              |

|------|---------|--------|---------|-------------|---------|--------|--------------|

| Fam. | Тур     | Ladung | Farbe   | Masse [MeV] | Тур     | Ladung | Masse        |

| 1    | down    | - ?    | r, b, g | 5- 16 MeV   | ?e      | - 1    | 0,05- 1,5 eV |

| 1    | up      | +?     | r, b, g | 2-8 MeV     | e       | 0      | 511 eV       |

| 2    | strange | - ?    | r, b, g | ~ 100 MeV   | ?μ      | - 1    | 0,05- 8.4 eV |

| 2    | charm   | +?     | r, b, g | ~ 1,3 GeV   | μ       | 0      | 105.7 MeV    |

| 3    | bottom  | - ?    | r, b, g | ~ 4,3 GeV   | $?_{t}$ | - 1    | 0,05- 8.4 eV |

| 3    | top     | +?     | r, b, g | ~ 175 GeV   | t -     | 0      | 1777.1 MeV   |

Zu all diesen Teilchen gibt es auch entsprechende Antiteilchen mit gleicher Masse, aber entgegengesetzter elektrischer Ladung, Farbe und schwacher Isospin.

Für die Gravitation fügt man eine vierte Wechselwirkung mit dem Gravitron als Vektorboson hinzu, welches an die Masse koppelt. Es gibt allerdings noch keine eindeutigen Beweise für die Existenz des Gravitrons.

Warum es gerade drei Familien gibt, ist unbekannt. Seit der Entdeckung der Neutrinomasse ist es auch denkbar, dass es noch weitere Familien gibt.

All diese Teilchen werden als fundamental und nicht weiter unterteilbar angesehen, sie besitzen keine innere Struktur und keine Ausdehnung.

#### Eigenschaften der fundamentalen Teilchen und ihre Symmetrien

Alle diese Teilchen werden im Standardmodell (und darauf aufbauenden Modellen) mit verschiedenen Eigenschaften versehen. Zu diesen Eigenschaften gehören die Masse, die elektrische Ladung, die schwache Ladung, der Spin, der schwache Isospin, die Farbe und Weitere mehr. Manche dieser Werte wie zum Beispiel die Masse haben (je nach Teilchen) einen bestimmten Wert aus einem kontinuierlichen Spektrum. Andere Eigenschaften wie zum Beispiel der Spin können lediglich diskrete Werte annehmen.

Diese diskreten Eigenschaften unterliegen speziellen mathematischen Symmetriebedingungen. Diese Bedingungen erlauben es, einen Zusammenhang zwischen verschiedenen fundamentalen Teilchen herzustellen und sie als verschiedene Ausprägungen ein und desselben "Grundobjekts" anzusehen. Diese Ausprägungen werden auch Zustände genannt. Sie können mathematisch als Vektoren in einem multidimensionalen Raum ausgedrückt werden, welche durch Symmetrieoperationen ineinander übergeführt werden können.

Vereinfacht ausgedrückt erfordert zum Beispiel die Existenz eines Teilchens mit schwachem Isospin 1 (das W<sup>+</sup> Vektorboson) auch die Existenz von einem weiteren Zustand mit dem Wert -1 (das W<sup>-</sup> Vektorboson) und einem dritten Zustand mit dem Wert 0 (das so genannte W<sup>0</sup>, zusammen bilden sie ein so genanntes Triplett). Weiterhin legt es auch die Existenz eines vierten Zustands mit nochmals dem Wert 0 nahe (das so genannte B<sup>0</sup>, es bildet ein so genanntes Singulett).

Diese Symmetrieregeln besagen jedoch lediglich, dass es zwei verschiedene Zustände mit schwachem Isospin 0 gibt, also zwei verschiedene unabhängige Vektoren. Nun kann man jedoch aus zwei unabhängigen Vektoren durch eine Drehung (eine Linearkombination) wieder zwei unabhängige, andere Vektoren ableiten. Welche *Drehung* nun zu zwei Teilchen führt, die in der Natur existieren, ist wiederum nicht das Ergebnisse einer mathematischen Operation, sondern muss als weitere Konstante im Standardmodell enthalten sein.

Im hier angeführten Beispiel bestimmt der so genannte Weinberg-Winkel die Mischung aus  $W^0$  und  $B^0$  und beschreibt so das dritte Vektorboson der schwachen Kraft  $Z^0$  und das Vektorboson der elektromagnetischen Kraft, das Photon  $(\gamma)$ .

$$|W^{+}\rangle = |W^{+}\rangle$$

$$|W^{-}\rangle = |W^{-}\rangle$$

$$|Z^{0}\rangle = \cos q_{w}|B^{0}\rangle + \sin q_{w}|W^{0}\rangle$$

$$|g\rangle = -\sin q_{w}|B^{0}\rangle + \cos q_{w}|W^{0}\rangle$$

Gleichzeitig wird auf diese Weise auch ein Zusammenhang zwischen der Einheit der elektrischen und der schwachen Ladung hergestellt und auch zwischen der relativen Stärke der beiden Kräfte. Somit kann die elektromagnetische Kraft und die schwache Kraft in der so genannten elektroschwachen Vereinheitlichung zusammengefasst werden.

#### Das postulierte Higgs-Boson

Leider hat die oben beschriebene *elektroschwachen Vereinheitlichung* einen gravierenden Schönheitsfehler:

Eine Vermischung von verschiedenen Zuständen ist nach den gegebenen Gesetzmäßigkeiten nur möglich, wenn die beteiligten Zustände vergleichbare Massen besitzen. Leider besitzt das  $W^0$  jedoch eine nicht unerhebliche Masse von ca. 100GeV, während das Photon masselos ist.

Der Widerspruch kann durch die Postulierung von vier verschiedenen *Higgs-Feldern* gelöst werden. Jedem der vier Vektorbosonen wird ein solches Feld zugeordnet. Die Kraft des Feldes wird durch jeweils ein weiteres Boson übermittelt. Es gibt somit vier Higgs-Bosonen. Die postulierte Theorie besagt nun, dass unterhalb einer bestimmten Temperatur/Energie (welche jeweils für die vier Felder unterschiedlich sein kann) jeweils ein Higgs-Boson von einem Vektorboson absorbiert wird.

In der Higgs-Theorie sind alle vier Vektorbosonen masselos während alle vier Higgs-Bosonen eine Masse besitzen. Es wird nun weiter postuliert, dass bei der aktuellen "Temperatur" des Universums die drei Higgs-Bosonen von  $W^+$ ,  $W^-$  und  $Z^0$  absorbiert werden und diesen somit eine Masse verleihen. Das Photon hat sein Higgs-Boson jedoch nicht absorbiert und ist daher masselos. Es muss also ein freies Higgs-Boson geben!

Die Masse dieses Higgs-Bosons lässt sich grob abschätzen und liegt in einem Energiebereich, der mit bisherigen Teilchenbeschleunigern nicht erreichbar ist.

Der Beweis der Existenz oder Nichtexistenz des Higgs-Teilchens ist von fundamentaler Bedeutung für die Konsistenz des Standardmodells. Bei einer Nichtexistenz wären völlig neue theoretische Konzepte erforderlich. Eine der Hauptmotivationen für den Bau des *Large Hadron Collider LHC* ist die Produktion und der Nachweis von Higgs-Bosonen.

## 1.2 Der Large Hadron Collider LHC

Der Large Hadron Collider wird gebaut um bei Proton—Proton Kollisionen Schwerpunktsenergien von bis zu 14 TeV bei einer Luminosität<sup>1</sup> von 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> erzeugen zu können. Die Energiebereiche von bisherigen Beschleunigern liegen um Größenordnungen tiefer.

Der LHC besteht aus zwei getrennten Synchotronringen mit einem Durchmesser von 8.6 Kilometern. Er wird am CERN² bei Genf in den schon bestehenden Tunnel des beendeten LEP³ Experiments installiert und wird voraussichtlich 2006 in Betrieb gehen. In den beiden Beschleunigungsringen können entweder Pakete von Protonen oder von Schwerionen beschleunigt und an vier verschiedenen Stellen zur Kollision gebracht werden. Wird der Beschleuniger mit Protonen betrieben, treffen die Pakete⁴ alle 25 ns aufeinander, bei Schwerionen alle 100 ns. Beim Betrieb mit Protonen finden durchschnittlich pro Paketdurchdringung 25 Kollisionen statt. Die vier Kollisionspunkte sind die Standorte von unterschiedlichen Experimenten.

**ATLAS**<sup>5</sup> und **CMS**<sup>6</sup> stellen Mehrzweck-Experimente dar, die ungefähr die gleichen Zielsetzungen haben. Die jeweiligen Detektoren sind von der Technik her jedoch deutlich unterschiedlich konzipiert.

<sup>&</sup>lt;sup>1</sup> Die Luminosität beschreibt die Anzahl an Teilchenkollisionen pro Fläche und Zeiteinheit

<sup>&</sup>lt;sup>2</sup> CERN – Centre Européenne pour la Recherche Nucléaire

<sup>&</sup>lt;sup>3</sup> LEP – Large Electron Proton Collider

<sup>&</sup>lt;sup>4</sup> das Durchdringen der beiden Teilchenwolken nennt man "bunch-crossing"

<sup>&</sup>lt;sup>5</sup> ATLAS – A Torodial LHC Apparatus

<sup>&</sup>lt;sup>6</sup> CMS – Compact Muon Solenoid

**ALICE**<sup>7</sup> ist ein Schwerionen-Experiment und untersucht Kern-Kern-Wechselwirkungen bei sehr hohen Energien. Die Kollisionen finden hier unter Bedingungen statt wie sie mit dem Universum direkt nach dem Urknall vergleichbar sind.

**LHC-B**<sup>8</sup> untersucht CP-Verletzung beim Zerfall von B-Mesonen. Der Detektor untersucht ausschließlich die Vorwärtsstreuung bei sehr kleinen Winkeln, da in diesem Bereich B- und Anti-B-Mesonen besonders zahlreich auftreten.

Eine der Hauptaufgaben von LHC besteht in der Produktion und Detektion von Higgs-Bosonen. LHC wird der erste Detektor sein, der Energien erreicht, die zur Produktion von Higgs-Bosonen in großen Mengen nötig sind. Der Vorgänger von LHC das LEP-Experiment hat erste Indizien von Higgs-Bosonen geliefert, welche darauf hindeuten, dass die Masse des Higgs-Bosonen sich am unteren Ende des vorhergesagten Bereichs befindet. Daher sollte LHC Higgs-Bosonen in sehr großen Mengen erzeugen können.

Weiterhin wird nach bisher unbeobachteten supersymmetrischen Teilchen gesucht, welche einen Beleg für die Erweiterung des Standardmodells durch Supersymmetrie liefern würden.

Außerdem sollen mit Hilfe von LHC-B Präzisionsmessungen von CP-Verletzungen durchgeführt werden, um so einige Naturkonstanten des Standardmodells genauer zu bestimmen (Cabbibo-Kobayashi-Maskawa-Matrix). Darüber hinaus ist bei diesen hohen Energien eventuell auch mit der Produktion von bisher völlig unbekannten Teilchen zu rechnen, die das Standardmodell in seiner jetzigen Form überholen werden.

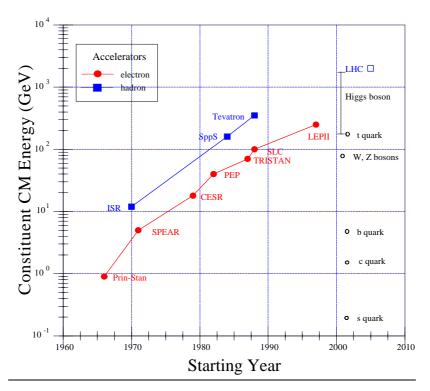

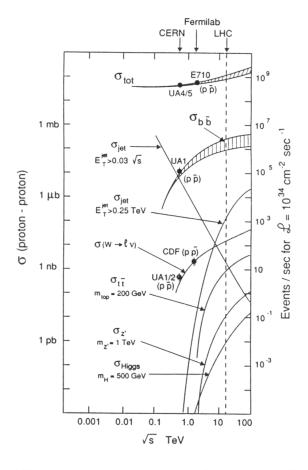

Abbildung 1 zeigt eine einfache historische Übersicht verschiedener Teilchenbeschleuniger und ihren maximalen Energien. Der LHC wird der erste Beschleuniger sein, welchem der gesamte Energiebereich der postulierten Higgs-Masse zugänglich sein wird. Abbildung 2 zeigt die verschiedenen Wirkungsquerschnitte am LHC und macht deutlich, dass nur etwa eine von  $10^{11}$  Kollisionen ein Higgs-Teilchen erzeugen wird (vergleiche totalen Querschnitt  $\sigma_{tot}$  mit Higgs-Querschnitt  $\sigma_{Higgs}$ ). Somit muss viel Sorgfalt auf die Erkennung einiger weniger besonderer Ereignisse innerhalb von vielen eher uninteressanten Ereignissen gelegt werden. Dies ist die Aufgabe eines so genannten Triggersystems (siehe Kapitel 2).

<sup>&</sup>lt;sup>7</sup> ALICE – <u>A</u> <u>L</u>arge <u>I</u>on <u>C</u>ollider Experiment

<sup>&</sup>lt;sup>8</sup> <u>LHC</u> <u>B</u>ottom Quarks Experiment

Abbildung 1 - Geschichte der Teilchenbeschleuniger

Abbildung 2 - LHC Proton-Proton Wirkungsquerschnitt

## 1.3 Das ATLAS-Experiment

Als einer der beiden Mehrzweck-Detektoren wurde ATLAS entworfen um durch Kollisionen erzeugte Teilchen in dem gesamten möglichen Energiebereich messen zu können. Dabei wurde sehr viel Wert auf eine möglichst hohe und genaue Auflösung der gemessenen Orts- und Energiewerte gelegt. Da LHC mit sehr hohen Luminositäten und Energien arbeitet, mussten Detektorkomponenten entwickelt werden, die die hohe entstehende radioaktive Strahlung über Jahre hinweg aushalten können. Vor allem integrierte elektronische Schaltungen sind sehr strahlungsempfindlich. Dies hatte maßgeblichen Einfluss auf das Grunddesign des Detektors.

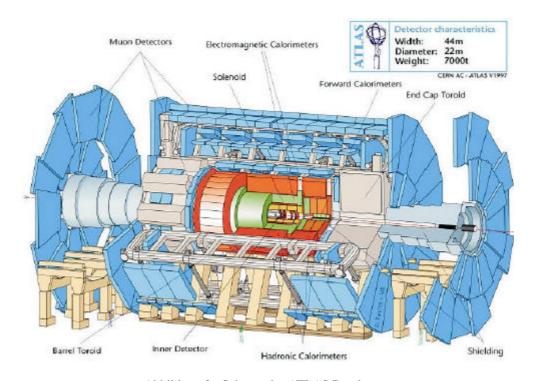

Der Detektor an sich besteht aus mehreren eigenständigen Komponenten, welche im Folgenden kurz erläutert werden. Der Detektor ist in Abbildung 3 schematisch dargestellt.

#### 1.3.1 Der Innere Detektor

Der Innere Detektor hat die Aufgabe, den Ursprungsort einer Kollision und den Weg der dabei produzierten Teilchen mit extrem hoher Genauigkeit zu messen. Da sich der Detektor darüber hinaus auch in einem Magnetfeld parallel zur Strahlachse befindet, können mit Hilfe von Energiemessungen der weiter außen liegenden Kalorimeter auch die Impulse von geladenen Teilchen bestimmt werden.

Der innerste Teil dieses Detektors besteht aus Schichten von Halbleiter-Bausteinen zur punktgenauen Detektion. Etwas weiter außen befinden sich Halbleiterschichten zur Streifen-Detektion, und zum Schluss folgen Gaszähler (Drahtkammern gefüllt mit Xenongas). Halbleiter-Detektoren werden nicht überall eingesetzt, da sie einerseits einen relativ hohen Wirkungsquerschnitt besitzen und somit bei verstärkter Verwendung Energie absorbieren und die Kalorimetermessung verfälschen. Andererseits sind diese Detektoren sehr teuer, und es ist nicht vollständig gesichert wie resistent diese Bauteile gegenüber jahrelanger harter Strahlung sind. Bei einer typischen Kollision durchläuft jedes Streuteilchen drei Punktschichten, acht Streifenschichten und 36 Drahtkammern, was eine sehr hohe Genauigkeit der Orts- und Impulsmessung ermöglicht.

Insgesamt verfügt der Innere Detektor über rund 146 Millionen Kanäle.

## 1.3.2 Das Kalorimeter

Die Aufgabe des Kalorimeters ist die Messung der Energie aller in einer Kollision erzeugten Teilchen. Lediglich Myonen und Neutrinos können nicht gemessen werden, da sie das Kalorimeter durchdringen ohne Spuren zu hinterlassen. Da das Kalorimeter aus mehreren Schichten besteht, können auch die Richtungen der gemessenen Teilchen bestimmt werden.

Diese Schichten bestehen abwechselnd aus einem Absorbermaterial und detektierendem Material. Die zu messenden Teilchen verlieren in den Absorberschichten Energie, was zur Paarproduktion von weiteren Teilchen führt. Diese sekundären Teilchen produzieren auf ihrem Weg durch das Kalorimeter wiederum weiter Teilchen. Auf diese Weise entsteht ein so genannter Teilchenschauer. Je nach Typ der primären Teilchen entstehen unterschiedliche Arten von Schauern. In den detektierenden Schichten erzeugen all diese Teilchen Signale proportional zu ihrer Energie. Die Detektionsschichten sind in eine Vielzahl von einzelnen Zellen unterteilt, was die räumliche Auflösung innerhalb des Kalorimeters ermöglicht. Jede dieser Zellen liefert ein Signal, dessen Stärke proportional zur Energie des gemessenen Teilchens ist.

Eine Teilaufgabe des Kalorimeters ist also die möglichst starke Absorption und Paarproduktion von Teilchen. Dies bedeutet, dass das gesamte Kalorimeter einer sehr starken Strahlung ausgesetzt ist, wodurch sehr hohe Anforderungen an die verwendeten Materialen und elektronischen Schaltungen gestellt werden.

Das Kalorimeter des ATLAS Experiments besteht aus drei verschiedenen Einheiten:

#### Das elektromagnetische Kalorimeter

Das EM Kalorimeter dient der Messung von Elektronen und Photonen. Als Absorptionsmaterial wird Blei verwendet, welches von Hadronen relativ ungehindert durchdrungen wird, Elektronen und Photonen dagegen erzeugen starke Bremsstrahlung. Als Detektionsmaterial wird flüssiges Argon verwendet, welches gute Messeigenschaften und hohe Unempfindlichkeit gegenüber der starken Strahlung in sich vereint.

Das elektromagnetische Kalorimeter besteht aus über 200.000 einzelnen Zellen, was eine extrem hohe räumliche Auflösung erlaubt.

#### Das hadronische Kalorimeter

Als Absorptionsmaterial für Hadronen wird Eisen (Stahl) verwendet, zur Detektion werden Plastikszintillatoren eingesetzt.

Die Absorption von hadronischen Teilchen ist wesentlich schwächer als im Vergleich die von Elektronen oder Photonen. Daher ist das hadronische Kalorimeter wesentlich dicker als das EM Kalorimeter.

Die Szintillatoren bestehen aus etwa 35.000 einzelnen Zellen.

#### Das Vorwärts-Kalorimeter

Für Teilchen mit Bahnen nahe an der Strahlachse gibt es das so genannte Vorwärts-Kalorimeter. Da in diesem Streubereich eine besonders starke Strahlung herrscht, wird als Detektionsmaterial wieder flüssiges Argon eingesetzt. Etwa 11.000 Zellen dienen der räumlichen Auflösung.

## 1.3.3 Das Myon-Spektrometer

Da Myonen nur elektroschwach wechselwirken, durchdringen sie das gesamte Kalorimeter fast ungehindert.

Das gesamte Kalorimeter ist von supraleitenden Magneten umgeben, welche ein zylindersymmetrisches (toroidales) Magnetfeld erzeugen. Die von dem Feld abgelenkten Myonbahnen werden durch Driftkammern detektiert.

Da der größte Teil der restlichen Teilchen im Kalorimeter absorbiert wird, ist das Myon-Spektrometer nur einer wesentlich schwächeren Strahlung ausgesetzt. Dies macht die Verwendung von wesentlich komplexeren elektronischen Schaltungen möglich.

Die Driftkammern des Myon-Spektrometers produziert Messdaten aus ungefähr 440.000 einzelnen Kanälen.

Abbildung 3 - Schema des ATLAS Detektors

## Kapitel 2

## Das ATLAS Triggersystem

Alle Kanäle aller Detektorkomponenten des ATLAS Experiments produzieren alle 25ns<sup>9</sup> Daten, die komplett zur weiteren Verarbeitung und Speicherung ausgelesen werden müssen. Dies ergibt ungefähr 6×10<sup>15</sup> Einzelsignale pro Sekunde. Eine solche extreme Datenmenge kann weder mit heutigen noch mit für die nähere Zukunft absehbaren Technologien auf Datenträgern abgespeichert werden. Da wegen der starken Strahlung direkt am Detektor nur einfache und robuste elektronische Komponenten verwendet werden können, ist es sogar unmöglich die gesamte Datenmenge mit der nötigen Geschwindigkeit vom Detektor zu einer weiteren Verarbeitungseinheit zu übertragen.

Nicht jede Proton-Proton Kollision erzeugt jedoch Ergebnisse von physikalischem Interesse.

Aus diesem Grund verwendet man einen so genannten Trigger, um aus der großen Menge von Ereignissen nur diejenigen von Interesse auszufiltern. Nur im Falle einer positiven Triggerentscheidung werden sämtliche Kanäle des ATLAS Detektors ausgelesen und zur späteren Analyse gespeichert.

Eine solche Triggerentscheidung kann nicht innerhalb von 25ns getroffen werden und daher müssen die Daten aller Kanäle in Pipeline-Memories auf dem Detektor zwischengespeichert werden. Aus Kostengründen und aus Gründen der technischen Machbarkeit dieser Pipeline-Memories muss die Latenzzeit des Triggersystems möglichst kurz gehalten werden.

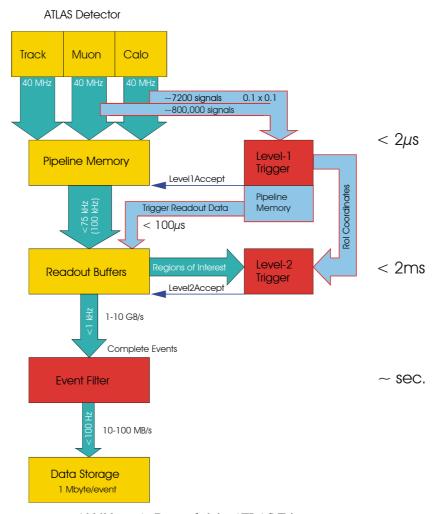

Das Triggersystem des ATLAS Experiments besteht aus drei nacheinander geschalteten Entscheidungsschritten: Der Level-1 Trigger, der Level-2 Trigger und der Eventfilter. Jeder der drei Einzeltrigger verringert die Datenmenge für die folgenden Triggersysteme.

Der Level-1 Trigger arbeitet auf der vollen LHC Rate von 25ns. Diesem Triggersystem steht eine fest definierte Zeit (Latenz) zur Entscheidung zur Verfügung. Bei einem positiven Resultat werden die Detektordaten bis zur Entscheidung des Level-2 Triggers aus den Pipeline-Memories in einen Readout Speicher übertragen. Auf diese Weise wird die Größe der kostspieligen Pipeline-Memories minimiert. Der Eventfilter schließlich rekonstruiert und analysiert das komplette ATLAS Event und entscheidet, ob dieses von physikalischem Interesse ist und abgespeichert werden soll.

Der Level-1 Trigger hat die Aufgabe, die Datenrate von 40MHz auf maximal 100kHz zu reduzieren. Der Level-2 Trigger reduziert die Rate nochmals auf maximal 1kHz. Der Eventfilter schließlich akzeptiert Ereignisse mit einer Höchstrate von 100Hz. Die verbleibende Datenmenge ist noch immer sehr groß, kann jedoch mit der verfügbaren Hardware bewältigt werden.

## 2.1 Der Level-1 Trigger

Die Aufgabe des Level-1 Triggers ist es, mithilfe einer möglichst schnellen Entscheidungslogik die Datenrate um den Faktor 400 zu reduzieren. Der Entscheidungslogik steht dabei ein Zeitraum von 2µs zur Verfügung (inklusive Verzögerung durch Länge von Leitungen) was 80 bunch-crossings (Proton-Proton-Durchdringungen) entspricht.

Um diesen Zeitrahmen einhalten zu können arbeitet der Level-1 Trigger mit Messdaten von reduzierter Genauigkeit des Myon-Spektrometers und des Kalorimeters. Die Entscheidungslogik wird von spezieller Hardware implementiert, wofür hauptsächlich ASICs<sup>10</sup> und FPGAs<sup>11</sup> eingesetzt werden.

<sup>&</sup>lt;sup>9</sup> 25 ns beim Betrieb mit Protonen, 100 ns beim Betrieb mit Schwerionen

$<sup>^{10}</sup>$  ASIC – <u>Application Specific Integrated Circuit</u>, eigens entwickelte Hardware Chips

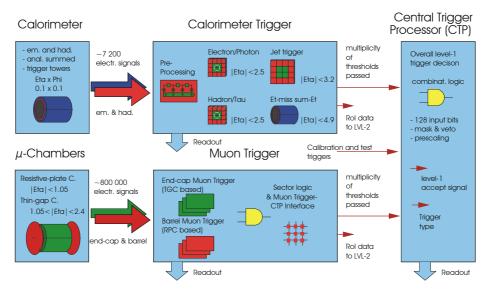

Der Level-1 Trigger ist in mehrere unabhängige Untereinheiten unterteilt. Die Entscheidungen der einzelnen Subsysteme werden vom Central Trigger Prozessor (CTP) zusammengeführt und verarbeitet.

## 2.1.1 Der Trigger des Kalorimeters

Um die Eingangsdatenmenge zu reduzieren werden die Daten der etwa 250.000 Zellen des hadronischen und elektromagnetischen Kalorimeters zu 7296 gröberen Zellen summiert. Dies geschieht mit analogen Schaltungen direkt auf dem Detektor. Die summierten Signale werden analog elektrisch über rund 60m Kabel zur Level-1 Trigger Elektronik übertragen. Der Kalorimeter Trigger erfüllt folgende Aufgaben:

- Vorverarbeitung der Eingangssignale (Pre-processing, siehe Kapitel 3)

- Triggerentscheidung für Elektronen und Photonen

- Triggerentscheidung für einzelne Hadronen und Tau-Teilchen

- Triggerentscheidung für Teilchen-Jets

- Berechnung der gesamten Energie im Kalorimeter um eine Entscheidung aufgrund der fehlenden Transversalenergie zu treffen

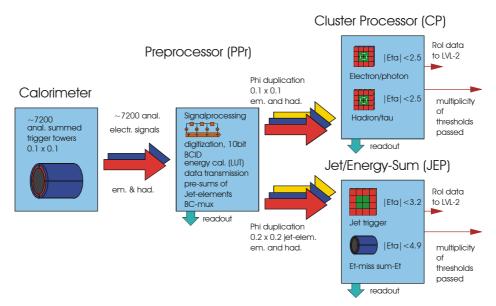

Die Vorverarbeitung erfolgt im so genannten Präprozessor. Hier werden die Signale digitalisiert und kalibriert. Außerdem analysiert der Präprozessor die Eingangssignale um das bunchcrossing zu identifizieren, welches das Signal verursacht hat. Diese Daten werden weitergeleitet an den Cluster Prozessor und den Jet/Energy-Sum Prozessor. Eine genauere Erläuterung des Präprozessors folgt in Kapitel 3.

Der Cluster Prozessor (CP) erkennt einzelne Elektronen, Photonen und Hadronen oberhalb einer definierbaren Energie. Hierzu wird eine 4x4 Nachbarschaftsmatrix mit der Matrix der 7296 Eingangssignale multipliziert und auf diese Weise nach isolierten Energiemessungen gesucht. Der Jet/Energy-Sum (JEP) Prozessor erkennt Jets und berechnet die fehlende transversale Energie. Hierzu wird eine größere Matrix mit der Eingangsmatrix multipliziert. Die Matrix ist so gewählt, dass nur Zellen erkannt werden in deren direkter Nachbarschaft sich weitere Zellen mit positiver Energiemessung befinden.

Die Anzahl der erfüllten Bedingungen (z.B. überschrittene Mindestenergien) wird an den Central Trigger Prozessor übermittelt, welcher die Level-1 Trigger Entscheidung trifft. Bei einer positiven Level-1 Entscheidung (Level-1 Accept Signal) werden Regions-of-Interest (RoI) Informationen an den Level-2 Trigger übertragen. Dies sind die Regionen, die zum Level-1 Accept geführt haben und vom Level-2 Trigger weiter analysiert werden.

Um die korrekte Funktionsweise und Kalibrierung des Kalorimeter Level-1 Triggers gewährleisten zu können, liefern alle drei Subsysteme zusätzlich zu den direkten Entscheidungsdaten noch so genannte Readout Daten. Der Präprozessor ermöglicht die Auslese von Rohdaten direkt nach der Digitalisierung und Daten nach der Vorverarbeitung. CP und JEP liefern ihre jeweiligen Eingangsdaten und die Ergebnisse der Analyse.

Der Datenpfad des gesamten Level-1 Kalorimeter 'Triggers ist in Abbildung 4 dargestellt.

<sup>&</sup>lt;sup>11</sup> FPGA – Field Programmable Gate Array, siehe Kapitel 4

Abbildung 4 - Schema der Level-1 Kalorimeter Triggers

## 2.1.2 Der Myontrigger

Auch der Myontrigger arbeitet nicht mit der vollen Granularität des Detektors. Die Eingangsdaten des Myontriggers stammen jedoch im Gegensatz zum Kalorimetertrigger nicht vom normalen Myondetektor (Driftkammern), sondern von spezieller Detektorhardware, die nur für die Triggerentscheidung verwendet wird (Resistive-Plate Chambers und Thin-Gap Chambers).

Der Myontrigger verfügt über sechs verschiedene programmierbare Grenzwerte für Myonimpulse. Wie auch beim Kalorimetertrigger wird die Anzahl der erfüllten Bedingungen an den Central Trigger Prozessor übertragen und im Falle eines Level-1 Accept Signals die RoI Informationen an den Level-2 Trigger.

## 2.1.3 Der Central Trigger Prozessor

Der Central Trigger Prozessor (CTP) erfasst sämtliche Entscheidungsdaten des Kalorimetertriggers, des Myontriggers und einer optionalen externen Datenquelle. Diese Daten werden mit 96 verschiedenen programmierbaren Bedingungen verglichen. Erfüllen die Daten mindestens einen der 96 Bedingungen wird ein Level-1 Accept Signal generiert.

Eine einzelne Bedingung kann zum Beispiel erfordern, dass zwei bestimme Myon-Grenzwerte nicht erfüllt sein dürfen, aber bestimmte Elektron- oder Hadron-Grenzwerte überschritten sein müssen.

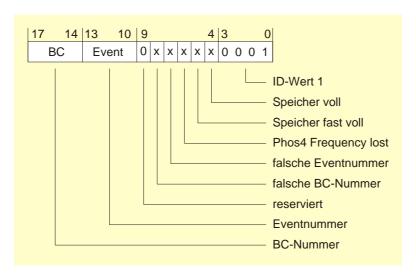

Ein positives Level-1 Accept wird über das globale ATLAS Timing, Trigger and Control System (TTC) im gesamten System verteilt. Es enthält Informationen des ausgelösten Trigger Typs, der identifizierten bunch-crossing Nummer und der fortlaufenden Nummer des Level-1 Events. Auch die untergeordneten Level-1 Trigger Subsysteme erhalten diese Informationen und nutzen diese unter anderem um Readout Daten zur optionalen Auslese verfügbar zu machen, so dass die Trigger-Entscheidung nachträglich auf Ihre Richtigkeit überprüft werden kann.

Abbildung 5 - Schema der ATLAS Level-1 Triggers

## 2.2 Der Level-2 Trigger

Die Aufgabe des Level-2 Triggers ist es, die Datenrate um den Faktor 100 auf 1kHz zu reduzieren. Hierzu erhält der Level-2 Trigger Region-of-Interest (RoI) Informationen von der Level-1 Trigger Logik. Mit der Hilfe dieser Informationen wählt der Level-2 Trigger die entsprechenden Zellen des ATLAS Detektors und liest diese aus dem Readout Speicher mit der vollen Genauigkeit aus.

Die Logik verwendet diese Daten um, so weit als möglich Bahn, Impuls, Masse und Typ von Teilchen zu bestimmen. Dies ist nicht immer vollständig möglich, da auch hier die zur Verfügung stehende Zeit stark begrenzt ist. Die auf diese Weise identifizierten Teilchen werden dann ähnlich wie im Level-1 Central Trigger Prozessor mit einer Anzahl von Sätzen von Bedingungen verglichen und bei Erfüllung mindestens einer Bedingung erfolgt das Level-2 Accept Signal. Eine Bedingung könnte zum Beispiel ein auftretendes Higgs-Teilchen sein.

Auch für den Level-2 Trigger wird dedizierte Hardware in Form von FPGAs eingesetzt.

## 2.3 Der Eventfilter

Die Aufgabe des Eventfilters ist eine weitere Reduktion der Datenrate um den Faktor 10. Der Eventfilter wird aus einer Farm von kommerziell erhältlichen Prozessoren bestehen. Er wird über ausreichend Rechenkraft verfügen, um anhand der kompletten ATLAS Detektordaten das erfolgte Event vollständig zu rekonstruieren. Das analysierte Event wird dann wiederum mit mehreren Sätzen von Bedingungen verglichen und bei Übereinstimmung zur späteren offline Analyse abgespeichert.

Der Eventfilter befindet sich momentan noch in der Planungsphase, da die Prozessorfarm mit der leistungsfähigeren Hardware der Jahre 2005 und 2006 implementiert werden soll. Heutige Hardware kann die erforderliche Rechenkraft mit den verfügbaren Geldmitteln nur schwer bis gar nicht leisten. Bei weiterer Gültigkeit von Moores Gesetz wird die nötige Leistung bis zum Jahr 2005 allerdings problemlos erhältlich sein.

In Abbildung 6 ist der gesamte Datenpfad des ATLAS Experiments dargestellt.

Abbildung 6 - Datenpfad der ATLAS Triggersystems

## Kapitel 3

## Der Level-1 Kalorimetertrigger Präprozessor

Der Präprozessor erhält als Eingang alle 25 Nanosekunden 7296 analoge Signale vom ATLAS Kalorimeter. Diese 7296 Signale werden direkt auf dem Detektor durch analoge Summation aus den Signalen der über 200.000 Zellen des elektromagnetischen und hadronischen Kalorimeters generiert. Nur durch diese stark reduzierte Granularität ist es dem Level-1 Trigger möglich mit einer ausreichenden Geschwindigkeit Entscheidungen zu treffen.

Der Präprozessor ist die erste signalverarbeitende Instanz und hat als solche die Aufgabe die eingehenden analogen Signale zu digitalisieren und zu kalibrieren. Darüber hinaus liefert der Präprozessor über Readout-Daten die Möglichkeit die Integrität des Level-1 Trigger Systems zu überprüfen. Insbesondere können die unverarbeiteten Rohdaten direkt nach der Digitalisierung ausgelesen werden. Hiermit kann man die korrekte Funktion der analogen Summation und die korrekte Kalibrierung der Daten überprüfen. Auch die Zuverlässigkeit der Algorithmen zur Identifikation des Bunch-Crossings kann getestet werden.

Im Folgenden hat der Präprozessor folgende Detailaufgaben:

## 3.1 Aufgaben des Präprozessors

Wie erwähnt ist die gesamte, alle 25 Nanosekunden vom ATLAS Detektor generierte Datenmenge zu groß um direkt bewältigt werden zu können. Daher kommt dem gesamten Level-1 Trigger System eine besonders wichtige Bedeutung zu. Es ist die erste Instanz in der gesamten Triggerkette und *muss* ordnungsgemäß arbeiten. Sollte der Level-2 Trigger oder der Eventfilter ausfallen, kann man als Notbehelf den Level-1 Trigger mit hohen Energiegrenzwerten betreiben. Die auf diese Weise stark reduzierte Level-1 Accept Rate kann dann als behelfsmäßiges endgültiges Triggersignal verwendet werden. Umgekehrt jedoch sind ohne Level-1 Trigger der Level-2 Trigger und der Eventfilter völlig nutzlos.

Grundsätzlich existieren die folgenden Teilaufgaben des Präprozessors:

## • Empfang des differentialen analogen Signals

Das Signal muss in ein unipolares Signal umgewandelt werden. Ein programmierbarer 10-Bit DAC erlaubt die Justierung des Nullniveaus.

#### Digitalisierung des analogen Signals

Ein kommerzieller 10-Bit Flash ADC wird verwendet um das Signal mit der globalen LHC-Frequenz von etwa 40MHz zu digitalisieren.

#### · Phasenjustierung des Eingangssignals

Mit einem ASIC (Phos4) der CERN Microelectronics Group kann die Clock des FADCs gegenüber der LHC-Clock in Schritten von einer Nanosekunde in der Phase verschoben werden.

## · Identifikation des Bunch-Crossings<sup>12</sup>

Das eingehende Signal muss einem bestimmten Bunch-Crossing zugeordnet werden, damit bei einem Level-1 Accept die Detektordaten des korrekten Events ausgelesen werden.

Dies erfolgt mit Hilfe zweier verschiedener Algorithmen, einer für gesättigte und einer für ungesättigte Signale. Diese Analyse wird von einem dedizierten ASIC durchgeführt, dem Pre-Processor ASIC (PPrASIC).

Zusätzlich kann ein so genanntes "External BCID" Signal zur Identifikation verwendet werden.

## · Kalibrierung des digitalisierten Signals

Über eine frei konfigurierbare Lookup-Tabelle wird das 10-Bit Rohsignal (RAW) auf einen 8-Bit Wert abgebildet (nach der BC Identifikation)

### · Berechnung von Jetelementen

Der Jet/Energy-Sum Trigger arbeitet mit nochmals gröberen Eingangsdaten. Hierzu werden jeweils 4 der 7296 vorverarbeiteten Signals aufsummiert.

## · Serielle differentielle Datenübertragung

Die vorverarbeiteten Daten werden über eine serielle LVDS<sup>13</sup>-Verbindung an den Cluster Prozessor und den Jet/Energy-Sum Prozessor zur weiteren Verarbeitung übertragen.

### · Readout von Trigger Daten

Um die korrekte Funktion des Präprozessors zu überprüfen können die unverarbeiteten Rohdaten (RAW) ausgelesen werden.

#### · Readout von Histogramm- und Ratemeter-Informationen

Der PPrASIC verfügt zusätzlich über die Möglichkeit ein Histogramm und Ratenmessungen zu erstellen. Auch diese Informationen müssen bei Bedarf ausgelesen werden.

## 3.2 Design des Präprozessorsystems

Dem gesamten Level-1 Trigger stehen 80 Bunch-Crossings ( $2\mu s$ ) an Zeit zur Verfügung um eine Einscheidung zu treffen, dies beinhaltet Signalverzögerungen durch Kabelverbindungen. Dem Präprozessor des Triggers stehen maximal 18 Bunch-Crossings zur Verfügung. Diese sehr kurze Zeitspanne macht den Einsatz von hochintegrierten Schaltungen wie dem PPrASIC (Pre-Processor ASIC) nötig.

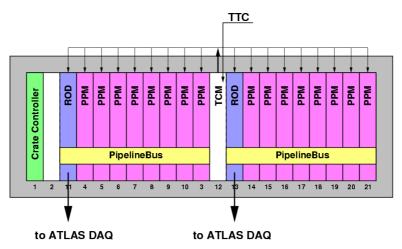

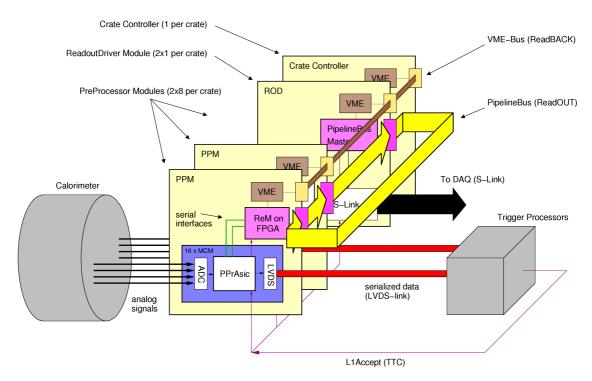

Der Hauptteil der Aufgaben des Präprozessorsystems wird von so genannten Präprozessormodulen (PPM) ausgeführt. Jedes einzelne PPM kann 64 analoge Eingangssignale verarbeiten. Das gesamte System verwendet 128 identische PPMs, welche somit insgesamt bis zu 8192 Kanäle anbieten. Jeweils 16 PPMs werden in einem Elektronik-Crate untergebracht, zusammen mit 4 weiteren Kontrollmodulen. Ein Kontrollmodul beherbergt einen AMD Athlon Personal Computer, der als Kontroll- und Steuerungsinstanz für das gesamte Crate dient. Ein weiteres Modul empfängt das globale TTC-Signal und verteilt es an alle anderen Module des Crates. Wie im vorigen Kapitel erwähnt, übermittelt das TTC-Signal unter anderem das Level-1 Accept Signal. Die beiden letzten Kontrollmodule sind identisch und dienen dem Empfang und Weitertransport von Readout Daten von jeweils 8 PPMs (siehe Abbildung 7). Im Folgenden werden die einzelnen Einschübe dieses Crates näher erläutert.

<sup>&</sup>lt;sup>12</sup> bunch-crossing – das Aufeinandertreffen zweier Protonenwolken (erfolgt alle 25 ns)

<sup>&</sup>lt;sup>13</sup> LVDS – low-voltage differential signaling

Abbildung 7 - Layout eines Präprozessor Crates

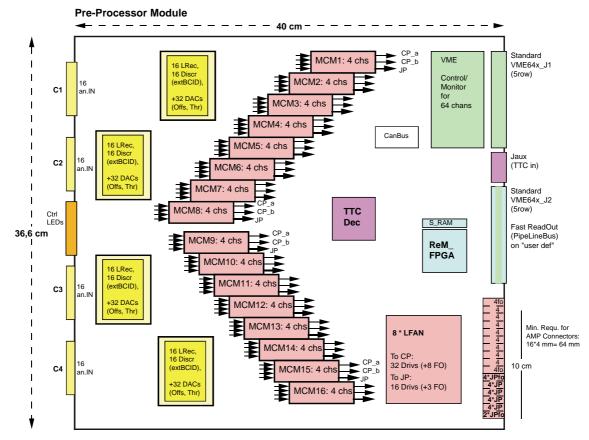

## 3.2.1 Die Struktur des Präprozessormoduls (PPM)

Ein Präprozessormodul besteht aus einem mehrschichtigen 9U<sup>14</sup> Printed-Circuit-Board (PCB) mit einer Vielzahl von so genannten Tochtermodulen. Ein Tochtermodul ist ein Multi-Chip-Modul (MCM), welches ebenfalls ein (kleines) PCB darstellt, auf welchem eine Anzahl von Chips in Die<sup>15</sup>-Form untergebracht sind. Diese Tochtermodule werden auf das große PPM aufgesteckt.

Die Verwendung von MCMs bringt den Vorteil größerer Flexibilität bei gleichzeitig einfacherer Herstellung. Sollte bei der Fertigung ein fehlerhafter Chip verwendet werden oder während des Betriebs ausfallen, so muss nur das eine betroffene MCM gegen ein funktionierendes Exemplar ausgetauscht werden anstatt des gesamten Präprozessormoduls. Auf diese Weise sinken der Ausschuss und damit die Kosten deutlich. Auch ist die Herstellung und Bestückung eines so großen PCBs durchaus nicht trivial, weshalb die Unterbringung fast aller vitalen Bauteile auf wesentlich kleineren Tochtermodulen sicherer ist.

Die einzelnen Komponenten des abgebildeten PPMs und ihre Funktion sollen im Weiteren kurz dargestellt werden (siehe auch Abbildung 8). Die für diese Diplomarbeit entscheidenden Komponenten werden im Anschluss noch einmal genauer erläutert:

15 die: ein roher Silikonchip ohne Verpackung oder Gehäuse (dadurch sehr klein)

-

<sup>&</sup>lt;sup>14</sup> 9U: U ist hier ein Größenstandard für PCBs und Crates, 9U entsprechen 36,6cm

Abbildung 8 - Schema der Präprozessormoduls PPM

## Das Analog-Input Modul (4 Stück pro PPM)

Dieses Modul nimmt jeweils 16 differentiale analoge Signale entgegen und wandelt sie in unipolare Signale um (gelbe Module in Abbildung 8). Dabei kann für jedes einzelne Signal eine individuelle Nullstellenkorrektur durchgeführt werden. Außerdem wird für jedes Signal bei Überschreiten einer ebenfalls individuell konfigurierbaren Schwelle ein digitales, so genanntes "externes BCID" Signal erzeugt.

Für die Konfigurierung der Nullstellenkalibrierung und des BCID Schwellenwertes werden pro Kanal zwei DAC<sup>16</sup>s verwendet. Als DACs im Speziellen werden vier kommerzielle MAXIM MAX529 verwendet. Jeder MAX529 stellt acht 8Bit DACs zur Verfügung, die über die so genannte SPI<sup>17</sup>-Schnittstelle programmiert werden können.

## Das Präprozessor Multi-Chip-Modul (16 PPrMCMs pro PPM)

Dieses Modul enthält die wichtigsten Komponenten des Präprozessors. Jedes PPrMCM verarbeitet vier Kanäle. Die vier analogen Eingangssignale werden von einem der Line-Receiver Module vorverarbeitet und danach direkt zu einem der 16 PPrMCMs weitergeleitet.

Das PPrMCM verrichtet angefangen bei der Digitalisierung der analogen Signale alle Aufgaben die in Kapitel 3.1 erwähnt werden.

-

<sup>&</sup>lt;sup>16</sup> DAC – Digital-Analog-Konverter

<sup>&</sup>lt;sup>17</sup> SPI – serielles Datenprotokoll mit 3 Leitungen, näheres sie Kapitel 3.3.2

Hierzu befinden sich auf dem PPrMCM mehrerer Chips in "Die"-Form:

- 4 Flash-ADCs zur Digitalisierung der Eingangssignale

- **3 LVDS-Bausteine** zur differentiellen Weiterleitung der seriellen Ausgangssignale. Diese Daten sind die Eingangsdaten für den Cluster Prozessor (2 LVDS-Bausteine) und den Jet/Energy-Sum Prozessor (1 LVDS-Baustein) des Level-1 Triggers.

- 1 Phos4-Chip zur Feinjustierung der Phase der LHC-Clock, welche als Digitalisierungssignal für die FADCs fungiert. Der Phos4-Chip wird über ein I<sup>2</sup>C-Interface<sup>18</sup> programmiert

- 1 PPrASIC (Präprozessor ASIC). Der PPrASIC wurde am Kirchhoff Institut in Heidelberg entwickelt und erbringt die eigentliche Vorverarbeitungsleistung des Präprozessors. Er verarbeitet gleichzeitig die Signale von vier Kanälen. Der PPrASIC liefert auch die in Kapitel 3.1 erwähnten Readout Daten über zwei spezielle serielle Schnittstellen (siehe Kapitel 3.3.3).

#### Das LFAN Modul (1 Stück pro PPM)

Aufgabe dieser speziellen ASIC-Chips ist die Übertragung der von den LVDS-Ausgängen der PPrMCMs empfangenen Daten an die entsprechenden Module des Cluster Prozessors und des Jet/Energy-Sum Prozessors der Level-1 Triggers. Die Verbindung zu diesen Modulen erfolgt über Kabel mit einer Länge von bis zu 20 Metern. Die Signale müssen daher mit entsprechender Stärke getrieben werden, was für die kleinen LVDS-Chips auf dem PPrMCM nicht möglich ist. Hierzu werden acht so genannte LFAN ASICs verwendet, welche in Packageform (nicht als "Die") auf einem Tochtermodul platziert werden. Der LFAN ist ein speziell in Heidelberg entwickelter ASIC-Chip der jeweils 8 Ausgangskanäle mit einer Datenrate von bis zu 480 Megabyte pro Sekunde realisiert.

Von den PPrMCMs werden insgesamt 32 LVDS-Signale für den Cluster Prozessor und 16 LVDS-Signale für Jet/Energy-Sum Prozessor erzeugt. Allerdings müssen einige dieser Signale doppelt an zwei verschiedene CP oder JP Module gesendet werden, weshalb sechs LFANs nicht ausreichen und acht Chips verwendet werden müssen.

Die neueren Entwicklungen auf dem FPGA Sektor führen auch zu Überlegungen, eventuell statt relativ teuren LFAN-Chips neue günstige FPGAs einzusetzen, die ebenfalls in der Lage sind differentielle Signale mit der entsprechenden Stärke zu erzeugen. Während jedoch die Eignung der LFAN-Chips schon ausführlich getestet wurde [1], muss die Eignung der FPGAs noch ausgiebig analysiert werden.

## Das TTCdec Modul (1 Stück pro PPM)

Das "Timing, Trigger and Control" Modul (TTC-Modul, siehe Kapitel 3.2.2) empfängt über eine optische Verbindung Signale, die über die gesamte ATLAS Architektur verteilt werden. Diese optischen Signale werden vom TTC Modul empfangen und über die Backplane elektrisch an die anderen Crate-Module verteilt, wo sie von jeweils einem TTCdec Tochtermodul empfangen werden. Dazu von Bedeutung für das PPM ist unter anderem die so genannte LHC-Clock, welche die Protonen Bunch-Crossings taktet und das Level-1 Trigger Accept Signal. Die TTC Signale sind die einzige Möglichkeit Module und verschiedene Crates miteinander zu synchronisieren.

Dieses Tochtermodul wurde nicht speziell für den Präprozessor entwickelt, sondern es findet Verwendung in fast allen Modulen des ATLAS Experiments.

<sup>&</sup>lt;sup>18</sup> I<sup>2</sup>C – serielles Datenprotokoll mit 2 Leitungen (Industriestandard), siehe Kapitel ???

#### Das CAN-Bus Modul (1 Stück pro PPM)

Das CAN-Bus Protokoll ist ein Industriestandard und wird im ATLAS Experiment für die Überwachung des Zustands der verschiedenen Crates, Module und Chips auf dem Modulen verwendet. Es werden Parameter wie Spannung, Stromaufnahme, Lüftergeschwindigkeit und Temperatur übermittelt. Dabei steht es jedem Modul frei, welche Parameter es über den CAN-Bus verfügbar macht.

## Das VME-Bus Modul (1 Stück pro PPM)

Der VME-Bus ist ein Industriestandard zur asynchronen Datenübertragung. Jedes einzelne Modul der verschiedenen Präprozessor Crates kann über VME angesprochen werden. Der VME-Bus dient hierbei vor allem der Steuerung und Konfiguration der einzelnen Komponenten der verschiedenen Präprozessor Module. Jedes Crate-Modul besitzt eine eindeutige Adresse im Adressraum des VME-Busses.

Der VME-Bus des PPM wird von einem Xilinx CPLD implementiert. Das VME-Modul ist weiterhin für die Konfiguration des RemFPGA zuständig. Mit der Hilfe eines Flash-RAM kann das CPLD den RemFPGA mit einer von zwei möglichen Konfiguration laden (siehe auch das Kapitel über FPGA Technologien).

Das CPLD kümmert sich um alle Detailaspekte des komplizierten VME-Bus Protokolls und stellt dem RemFPGA einen stark vereinfachten Zugang zur VME-Kommunikation zur Verfügung.

#### Der Readout-Merger FPGA (1 Stück pro PPM)

Dieser FPGA, der Gegenstand dieser Diplomarbeit ist, befindet sich direkt auf dem PPM und nicht auf einem Tochtermodul. Es handelt sich um einen Xilinx Virtex-E 1000 in einem Ball-Grid-Array Package (BGA560) [2]. An der Virtex direkt angeschlossen ist ein 2 MB Speicherchip, er wird jedoch von dem in dieser Diplomarbeit vorgestellten Programmcode nicht benötigt. Er steht für spätere Erweiterungen zur Verfügung.

Der RemFPGA ist mit beinahe allen anderen Modulen des PPM verbunden und kontrolliert und steuert diese. Die Kommunikation mit der Außenwelt erfolgt einerseits über den VME-Bus (mit Hilfe des VME Moduls) und über den speziell entwickelten Pipeline-Bus, welcher vom RemFPGA direkt gesteuert wird.

Seine Hauptaufgaben bestehen in der Konfiguration des gesamten PPM und der Übertragung von Readout Daten über wahlweise den VME-Bus oder den Pipeline-Bus. Die genaue Funktion wird in den folgenden Kapiteln dargestellt.

### 3.2.2 Das TTC-Modul

Für die Synchronisation des gesamten ATLAS Experiments dienen eine Reihe von globalen ATLAS Signalen, die über optische Verbindungen an die einzelnen Komponenten des ATLAS Systems verteilt werden. Zum Empfang dieser Daten und der Konvertierung in elektrische Signale dient das TTC-Modul. Die empfangenen TTC-Signale werden an alle anderen Module des jeweiligen Crates verteilt. Jedes Crate des Level-1 Triggers verfügt über ein solches Modul.

Zu den Signalen gehören unter anderem:

- LHC-Clock: Dieses Signal taktet die einzelnen Bunch-Crossings des LHC-Beschleunigers. Dieses Signal ist für die Synchronisation des gesamten ATLAS Systems unerlässlich.

- Level-1 Kalorimeter Accept: Dieses Signal zeigt eine positive Entscheidung des Level-1 Kalorimeter Triggers an. Viele Triggerkomponenten erzeugen daraufhin Readout Daten zur Kontrolle der Performance des Triggers.

- Reset der BC-Nummer: Bei jedem LHC-Clock Signal inkrementieren Komponenten wie zum Beispiel der PPrASIC einen internen Zähler. Mit Hilfe dieses Signals wird die so genannte BC-Nummer zurückgesetzt und so gewährleistet, dass alle Komponenten des ATLAS Systems global und synchron mit derselben Nummer arbeiten.

- **Reset der Level-1 Event-Nummer:** Ebenso wie für die obige BC-Nummer existiert auch ein Reset-Signal für die so genannte Event-Nummer. Jede positive Level-1 Trigger Entscheidung inkrementiert diese Zahl.

## 3.2.3 Der Crate-Controller des Präprozessorsystems

Bei diesem Crate-Einschub handelt es sich um einen am Kirchhoff Institut in Heidelberg entwickelten AMD Athlon PC mit angeschlossenem VME-Interface. Der PC verfügt über eine Festplatte einen Ethernet Netzwerk Anschluss.

Sämtlich Kommunikation über den VME-Bus wird von diesem Crate-Controller gesteuert.

## 3.2.4 Der Readout-Driver des Präprozessorsystems

Für jedes Präprozessor-Crate werden zwei Readout-Driver Module (ROD) verwendet. Jeweils acht PPMs sind über den am Kirchhoff Institut entwickelten Pipeline-Bus mit jeweils einem ROD verbunden. Der ROD verfügt darüber hinaus über einen Anschluss an den VME-Bus. Jedoch wird dieser nicht für die Kommunikation zwischen ROD und PPM verwendet, sondern ausschließlich für Datenverkehr zwischen Crate-Controller und ROD.

Die von den verschiedenen PPrASICs generierten Readout-Daten werden vom ROD Modul empfangen und über eine Anzahl von so genannten S-LINK Verbindungen an das Datenverarbeitende System des ATLAS Level-1 Kalorimeter Triggers weitergeleitet. S-LINK Verbindungen existieren in verschiedenen Geschwindigkeitsausführungen und die genaue Zahl und Art der zu verwendenden Verbindungen war zum Zeitpunkt dieser Diplomarbeit noch nicht endgültig festgelegt.

Der Großteil der Funktionalität des ROD wird ebenfalls von einem Xilinx Virtex-E 1000 implementiert werden. Zum Zeitpunkt dieser Arbeit existiert lediglich eine ältere Version des Programmcodes des ROD-FPGAs, welcher für einen Prototyp des Readout-Mergers entwickelt wurde. Dieser Prototyp war in einem ASIC implementiert (RemASIC).

Der neue RemFPGA, der im Rahmen dieser Arbeit entwickelt wurde ist mit dem Interface des RemASIC nicht mehr kompatibel. Der noch zu erstellende neue Code des ROD-FPGA kann jedoch voraussichtlich zu weiten Teilen von dem bestehenden Programmcode abgeleitet werden.

Abbildung 9 - Verbindungen der einzelnen Crate-Module (TTC nicht dargestellt)

## 3.3 Schnittstellen des RemFPGA

Im Folgenden sollen die Strukturen und Protokolle der verschiedenen Schnittstellen erläutert werden, die mit dem RemFPGA verbunden sind.

Dabei ist grundsätzlich zu unterscheiden zwischen Protokollen, die von verwendeten anderen Chips (z.B. Phos4 oder PPrASIC) festgelegt werden und Schnittstellen deren Implementierung teilweise oder ganz von der Programmierung des RemFPGA bestimmt werden.

## 3.3.1 Das I<sup>2</sup>C Protokoll

Dieses Protokoll ist ein von Philips entwickelter Industriestandard [3]. Das I<sup>2</sup>C Protokoll benötigt lediglich zwei Leitungen und ermöglicht die Kommunikation von einer großen Anzahl von Slaves mit mehreren Mastern.

Ein *Master* ist hierbei definiert als ein angeschlossenes beliebiges Gerät (ASIC, FPGA, Mikroprozessor), welches einen Datentransfer aktiv einleitet. Ein *Slave* ist eine Instanz, die sich auf dem I<sup>2</sup>C-Bus passiv verhält bis sie von einem Master zur Kommunikation aufgefordert wird. Dabei ist jedem Slave je nach verwendetem optionalem Zusatzprotokoll eine eindeutige Adresse von 7 oder 10 Bit Länge zugeordnet. Die Datenübermittlung erfolgt in Bytes von 8 Bit Länge.

Das I<sup>2</sup>C-Protokoll ist definiert für drei verschiedene Geschwindigkeitsstufen von 100kBit (Normal), 400kBit (Fast) und 3,4MBit (Highspeed) pro Sekunde. Dabei ist der 400kBit Modus abwärtskompatibel zum Normalmodus, während der Highspeed-Betrieb einer hierzu inkompatiblen Spezifikation folgt.

Im Falle der PPM wird lediglich der 100kBit-Modus verwendet und der RemFPGA fungiert als einziger Master. Daher werden im Folgenden nur die vom PPM benötigten I<sup>2</sup>C-Funktionalitäten kurz erläutert. Für eine ausführlichere Darstellung sei auf die Spezifikation von Philips verwiesen [4].

#### Die I<sup>2</sup>C-Datenleitungen und Master-Server Kommunikation

Die beiden Leitungen des I<sup>2</sup>C-Busses bestehen aus bidirektionalen Leitungen, die an einen Pull-Up Widerstand angeschlossen sind. Wenn kein Gerät den I<sup>2</sup>C-Bus anspricht, ist der Zustand der beiden Leitungen somit HIGH.

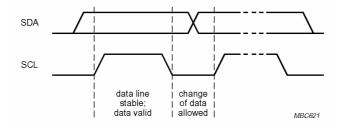

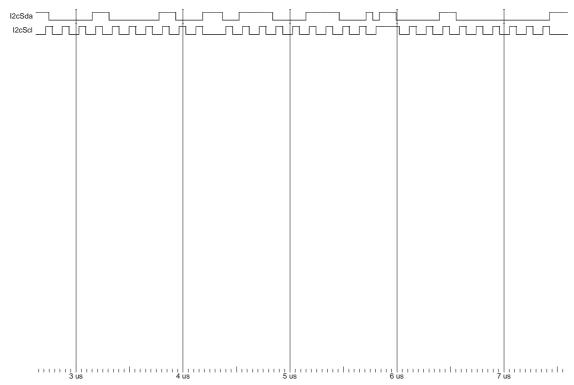

Eine Leitung fungiert als Clocksignal (*SCL*) und die zweite Leitung als Datensignal (*SDA*). Bei dem Transfer von Datenbits muss der Zustand von SDA während der HIGH-Periode von SCL stabil sein. Für jedes zu übertragende Bit wird vom I<sup>2</sup>C-Master ein Clocksignal generiert (siehe Abbildung 10).

Abbildung 10 - Datentransfer auf dem I<sup>2</sup>C-Bus

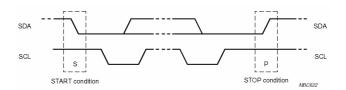

Zusätzlich definiert der I<sup>2</sup>C-Bus die Generierung zweier spezieller Befehlssignale namens START und STOP. Diese werden durch einen HIGH-LOW (START) bzw. einen LOW-HIGH (STOP) Übergang auf SDA generiert während SCL HIGH ist (siehe Abbildung 11).

Abbildung 11 - START und STOP Bedingungen

Der Master initiiert einen Datentransfer durch das Generieren eines START-Signals. Hierzu zieht der Master SDA auf LOW während SCL HIGH ist. Danach wird SCL ebenfalls auf LOW gezogen.

Benötigt ein an den I²C-Bus angeschlossenes Gerät Zeit, um auf Aktivität auf dem Bus zu reagieren, so kann es ein vom Master auf LOW gezogenes SCL-Signal ebenfalls aktiv auf LOW ziehen. Dadurch bleibt SCL LOW, selbst wenn der Master die Leitung wieder freigibt. Der Master erkennt dies und wartet auf eine Freigabe des SCL Leitung durch das andere Gerät. Auf diese Weise kann jedes I²C-Gerät einen Wartezustand auf dem Bus erzwingen. Bei einer nicht ordnungsgemäßen Funktion eines angeschlossenen Geräts kann dies andererseits aber auch den kompletten Bus dauerhaft blockieren.

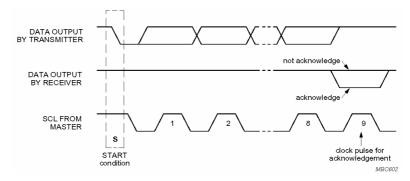

Nach der START-Bedingung sendet der Master 8 Bits auf den Bus und generiert anschließend einen neunten Clockimpuls auf SCL. SDA wird während dieses neunten Impulses jedoch nicht vom Master getrieben. Stattdessen ist es die Aufgabe des angesprochenen Slave-Gerätes, die SDA-Leitung auf LOW zu ziehen um den Empfang zu bestätigen, im I<sup>2</sup>C Jargon "Acknowledgement" genannt (siehe Abbildung 12).

Abbildung 12 - I<sup>2</sup>C Acknowlegement

Die übermittelten 8 Bits des Masters enthalten die Adresse des angesprochenen Slaves und die Richtung für den darauf folgenden Datentransfer.

Im Anschluss generiert der Master weitere 9 Impuls auf SCL. Je nach Datenrichtung sendet oder empfängt der Master hierbei Daten von bzw. zu dem angesprochenen Slave. Der neunte Clockimpuls dient wieder der Bestätigung des Empfangs – falls der Master Daten von einem Slave ausgelesen hat wird dieses Acknowledgement-Signal vom Master generiert. Beliebig viele weitere 9Bit-Zyklen schließen sich optional an.

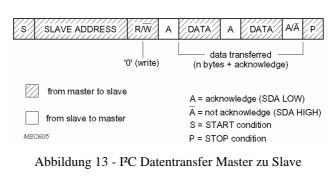

Um den Datentransfer zu beenden, sendet der Master ein STOP-Signal nach einer 9Bit Datenübertragung. Alle Geräte müssen daraufhin auf dem I²C-Bus zurück in den Bereitschaftszustand gehen. Um statt dessen einen weiteren Datentransfer anderer Richtung oder Adresse einzuleiten, sendet der Master statt des STOP-Signals ein neues START-Signal mit nachfolgend gesendeter Adresse des neuen Slaves. Siehe auch Abbildung 13 und Abbildung 14.

Abbildung 14 - I2C Datentransfer Slave zu Master

### I<sup>2</sup>C Adressierungsschema und Besonderheiten des Phos4 Chips

Einige Adressen des I<sup>2</sup>C-Busses haben spezielle Bedeutungen, sie sind im Folgenden ohne weitere Erläuterungen aufgeführt:

| Adresse   | R/W Bit | Bedeutung      |

|-----------|---------|----------------|

| 0000 0000 | 0       | "General-Call" |

| 0000 0000 | 1       | START byte     |

| 0000 001  | X       | CBUS Adresse   |

| 0000 010 | X | Reserviert für andere Busformate          |

|----------|---|-------------------------------------------|

| 0000 011 | X | Reserviert für zukünftige Erweiterungen   |

| 0000 1xx | X | verwendet von High-Speed I <sup>2</sup> C |

| 1111 1xx | X | Reserviert für zukünktige Erweiterungen   |

| 1111 0xx | X | 10 Bit Slave Adresse                      |

Tabelle 1 - I<sup>2</sup>C Sonderadressen

Einer "General-Call" Adresse folgt ein weiteres Byte mit spezieller Bedeutung. Erwähnenswert ist hier der Wert 00000110, welcher einen Reset an alle angeschlossenen Geräte signalisiert. Die Beachtung dieses Resetsignals ist jedoch für jedes I<sup>2</sup>C-Gerät optional.

Der Phos4 Chip [5] besitzt einige Besonderheiten in seiner Implementierung des I<sup>2</sup>C-Busses. Falls in zukünftigen Versionen des PPMs andere Chips außer dem Phos4 an I<sup>2</sup>C angeschlossen werden sollen, müssen einige Einschränkungen beachtet werden.

Der Phos4 Chip besitzt nur vier Pins um die I<sup>2</sup>C-Adresse zu definieren, die restlichen drei Bits sind teilweise statisch definiert und werden teilweise ignoriert. Darüber hinaus kann der Chip nur beschrieben, aber nicht ausgelesen werden.

| Adressbit | <b>A6</b> | A5    | A4    | A3    | <b>A2</b> | A1 | <b>A0</b> | R/W |

|-----------|-----------|-------|-------|-------|-----------|----|-----------|-----|

| Bedeutung | 0         | Pin20 | Pin21 | Pin22 | Pin23     | X  | X         | 0   |

Tabelle 2 - Adressschema des Phos4

Zusammen mit Tabelle 1 ergibt sich somit zwingend die Einschränkung, dass für jeden Phos4 zumindest eines der drei Bit A5, A4 und A3 gesetzt sein muss, da der Chip ansonsten auch auf einige Sonderadressen reagieren würde. Es empfiehlt sich auch eventuelle weitere I²C-Geräte nur mit Adressen mit gesetztem A6-Bit zu versehen. Werden diese beiden zusätzlichen Randbedingungen beachtet, so bleibt der I²C-Standard weiterhin gewahrt.

#### 3.3.2 Das SPI-Protokoll

Bei dem SPI-Protokoll handelt es sich um ein äußerst einfaches Protokoll, welches drei Datenleitungen verwendet. Die SPI-Schnittstelle wird ausschließlich von den DAC-Chips MAX529 von Maxim [6] auf den Analog-Input Modulen verwendet.

Es handelt sich um ein serielles Schiebeprotokoll, bei dem mehrere MAX529 optional hintereinander geschaltet werden können. Im Falle des Einsatzes auf den Analog-Input Modulen werden jeweils vier MAX529 zusammen geschaltet (daisy-chaining). Die drei Leitungen übertragen das Datensignal DIN, die Clock CLK und das Ladesignal CS. Jeder MAX529 verfügt zusätzlich über einen Pin DOUT, der mit dem DIN Eingang des nächsten MAX529 verbunden wird.

Jeder MAX529 implementiert ein 16 Bit Schieberegister. Bei jedem Clocksignal wird der Wert von DIN in das unterste Bit des Schieberegisters geschoben. Das oberste Bit wird auf DOUT ausgeben und dient so als Eingangssignal für den nächsten MAX529 in der Kette.

Bei einer Kettenlänge von Vier kann jedes Bit in jedem MAX529 auf einen eindeutigen Wert gesetzt werden, indem nacheinander 64 Bits auf dem SPI-Bus ausgegeben werden. Ein nachfolgendes Ladesignal CS veranlasst alle MAX529 den momentanen Inhalt ihrer Schieberegister als neue Programmierung zu übernehmen.

Die Geschwindigkeit des SPI-Busses beträgt im Falle des PPM 1 MHz.

#### 3.3.3 Die serielle Schnittstelle des PPrASIC

Jeder PPrASIC verfügt über zwei identische serielle Schnittstellen. Jede steuert zwei der vier Kanäle der PPrASIC. Somit sind auf dem gesamten PPM 32 serielle Schnittstellen vorhanden. Diese werden mit einer Geschwindigkeit von 40MHz betrieben, wobei das Taktsignal vom RemFPGA zu erzeugen ist.

Das Protokoll ist spezifisch für den PPrASIC und verwendet vier Datenleitungen namens Clock, Frame, DataIn und DataOut. Die Bitlänge beträgt 13 Bit. Durch die getrennten Leitungen für Eingabe und Ausgabe können verschiedene Daten in beide Richtungen gleichzeitig übertragen werden. Der Beginn eines neuen Datenwortes wird dabei durch das Frame-Signal angezeigt, welches somit zusammen mit jedem dreizehnten Clocksignal erzeugt wird. Hier soll im Folgenden lediglich das Datenformat der übertragenen 13 Bit Worte kurz erläutert werden.

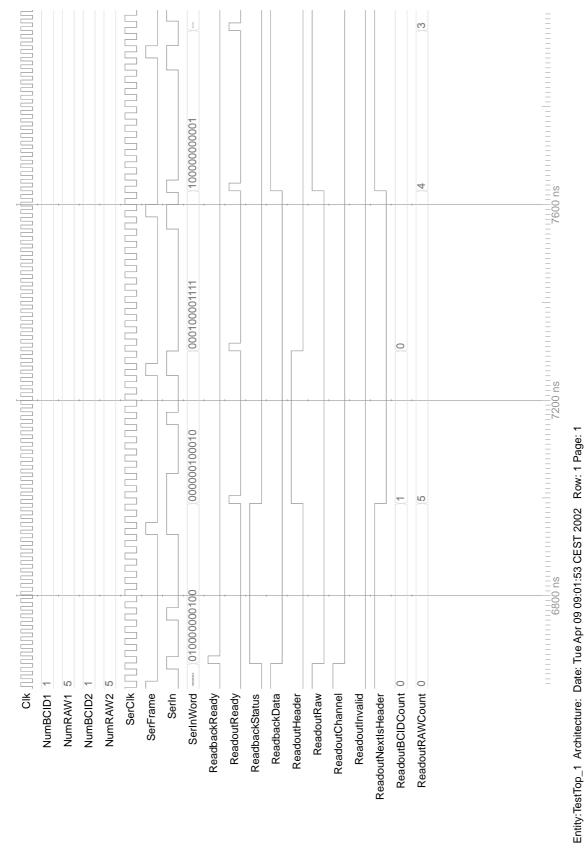

Für eine eingehendere Beschreibung der seriellen Schnittstelle siehe das Benutzerhandbuch des PPrASICs [7] und die Diplomarbeit zum PPrASIC [12].

### Eingabewörter des PPrASIC

Über die serielle Schnittstelle können sowohl Befehle wie auch Daten für die internen Speicherbereiche und Register an den PPrASIC übermittelt werden. Der Wert des höchsten Bits entscheidet dabei, um welche Art von Eingabe es sich handelt. Der RemFPGA dieser Diplomarbeit erzeugt und sendet keine eigenen Befehle oder Daten über die serielle Schnittstelle zum PPrASIC. Es werden lediglich Datenblöcke über die VME-Schnittstelle (siehe Abschnitt 3.3.4) oder den Pipelinebus (siehe Abschnitt 3.3.5) entgegen genommen und unverändert an die angeschlossenen PPrASICs geschickt (siehe Abschnitt 6.3).

#### Ausgabewörter des PPrASIC

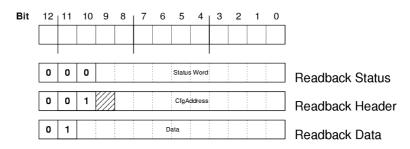

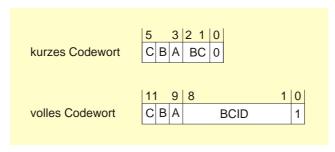

Abhängig vom Wert des höchsten Bits überträgt der PPrASIC ReadOUT- oder ReadBACK-Daten. Als ReadOUT bezeichnet man Daten, die zur Überprüfung des Verhaltens des Triggers bei jedem Level-1 Accept generiert werden und die über die beiden ROD (Readout Treiber) weitergeleitet werden. Als ReadBACK werden Daten aus den internen Registern und Speicherbereichen des PPrASIC bezeichnet.

Wird zum Beispiel der PPrASIC mit Hilfe des Eingabe-Befehls *StartReadback 0010000100011* zur Auslese des Registers Nummer 2 aufgefordert, so sendet der PPrASIC den Registerinhalt als ReadBACK Daten.

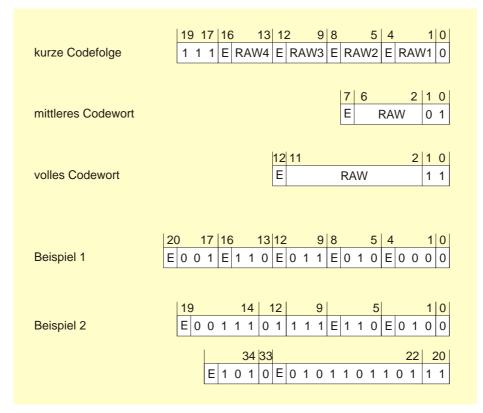

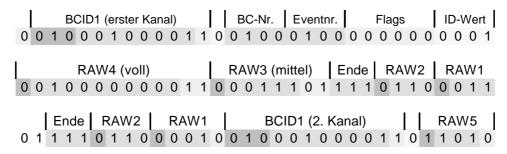

ReadOUT-Daten dagegen setzen sich aus so genannten RAW- und BCID-Werten in Verbindung mit einem vorangehenden Header zusammen. Ein solches Paket aus Header-, BCID- und RAW-ReadOUT-Datenwörtern wird von dem PPrASIC bei jedem Level-1 Accept für jeden der vier Kanäle generiert und ohne Aufforderung über die beiden seriellen Schnittstellen ausgegeben.

Bei den RAW-Werten handelt es sich um die unverarbeiteten Rohdaten, die von dem PPrASIC als 10 Bit Worte von den FADCs empfangen werden. Aus jedem RAW-Wert wird über mehrere Algorithmen ein 8 Bit BCID-Wert abgeleitet. Diese BCID-Daten sind das Endresultat des PPrASIC und werden auch (in leicht veränderter Form) über den so genannten Echtzeitdatenpfad an den Cluster Prozessor und den Jet/Energy-Sum Prozessor des Level-1 Triggers weitergeleitet. Die einzelnen BCID-Werte werden dabei nicht nur von einem RAW-Wert abgeleitet, sondern sind auch abhängig von vorangegangenen RAW-Daten.

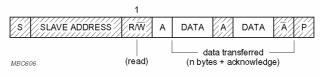

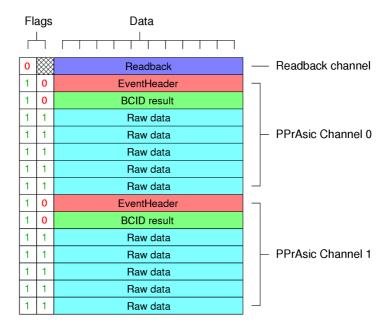

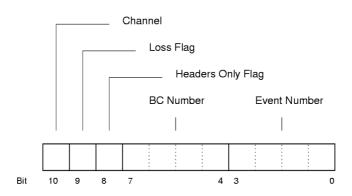

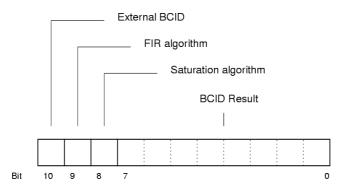

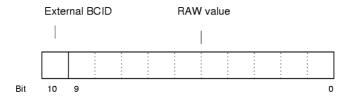

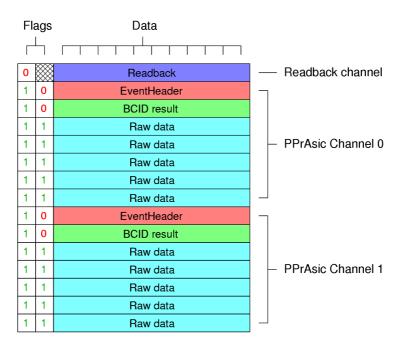

ReadOUT-Daten und ReadBACK-Daten werden in einer unveränderlich definierten Reihenfolge gesendet (siehe Abbildung 15). Zuerst wird ein einzelnes ReadBACK-Wort gesendet. Dieses wird gefolgt von einem EventHeader-Wort für den ersten Kanal, welches weiter gefolgt wird von einem oder mehreren BCID-Werten (bis zu 31 Stück, Standardeinstellung: 1 BCID-Wort). Nach dem/den BCID-Werten folgen 0 bis 7 RAW-Werte (Standardeinstellung: 5 RAW-Werte). Anschließend folgen die ReadOUT-Daten des zweiten Kanals.

Abbildung 15 - Abfolge der seriellen Datenausgabe

Die Anzahl zu sendender BCID- und RAW-Werte kann für jeden Kanal einzeln über interne Register des PPrASIC eingestellt werden. In der Grundeinstellung werden für jeden Kanal 1 BCID- und 5 RAW-Werte übertragen. Ein RAW-Wort besteht aus einem 10 Bit-Wert und einem Flagbit namens "External BCID". Ein BCID-Wort besteht aus einem 8 Bit Wert und 3 Flagbits. Jedes Header-Wort enthält die jeweils unteren 4 Bits des PPrASIC-internen Event- und Bunch-Crossing-Zählers. Bei einer ordnungsgemäßen Synchronisation des Präprozessorsystems sind diese Werte für alle 7296 Kanäle identisch. Für eine nähere Beschreibung der Bedeutung der einzelnen Daten siehe die Spezifikation des PPrASIC [7].

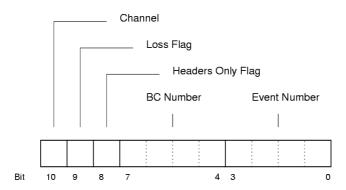

Abbildung 16 - serieller ReadOUT Header

Abbildung 17 - serieller ReadOUT BCID-Wert

Abbildung 18 - serieller ReadOUT RAW-Wert

Falls mangels eines Level-1 Accept Signals keine ReadOUT-Daten gesendet werden sollten, werden einfach nur ReadBACK-Worte direkt nacheinander gesendet. Falls keine ReadBACK-Daten zu senden sind (unabhängig von eventuell zwischen einzelnen ReadBACK-Worten eingefügten ReadOUT-Worten), wird als ReadBACK fortlaufend ein so genanntes ReadBACK-Statuswort gesendet. Dieses gibt über Flagbits Auskunft über einige grundlegende Zustände des PPrASICs.

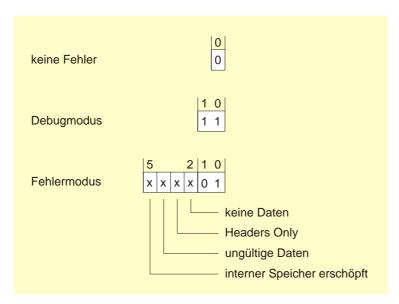

Abbildung 19 - serielle ReadBACK Daten

Abbildung 20 - serielles ReadBACK Statuswort

Die genaue Bedeutung der verschiedenen Bits dieser seriellen Datenwörter wird in [12] und in [7] eingehend erläutert.

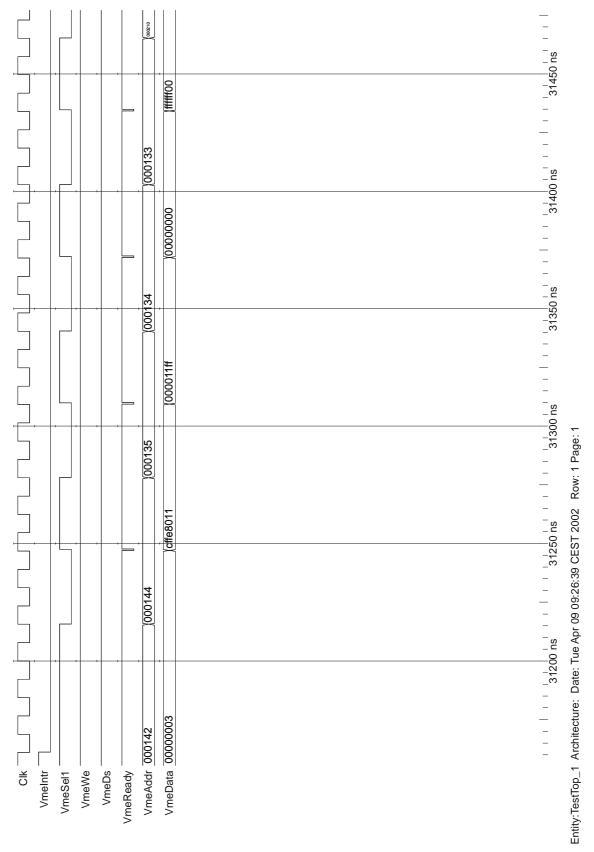

#### 3.3.4 Die Schnittstelle zum VME-CPLD

Die eigentliche Implementation der VME-Schnittstelle erfolgt durch das CPLD des VME-Moduls. Die über VME zu übermittelnden Daten werden allerdings vom RemFPGA generiert bzw. entgegengenommen. Die Kommunikation zwischen CPLD und RemFPGA erfolgt über eine VME-CPLD spezifische Schnittstelle namens "Easy VME". Darüber hinaus liefert das CPLD auch das Clocksignal und das Resetsignal für den RemFPGA.

Der VME-Bus wird im Fall des PPM mit einer Datenbreite von 32 Bit und einer Adresstiefe von 22 Bit betrieben. Hinzu kommen eine Reihe von Steuersignalen die im folgenden aus der Sicht des RemFPGA näher beschrieben werden sollen (siehe Tabelle 1). Alle Steuersignale sind grundsätzlich low-aktiv.

| Signal    | Richtung | Bedeutung                                                             |

|-----------|----------|-----------------------------------------------------------------------|

| Interrupt | out      | Programmierbares Interruptsignal des RemFPGA                          |

| Select 1  | in       | Ein gültiger Wert liegt an der Adressleitung an                       |

| Select 2  | in       | reserviert für zukünftige Verwendung                                  |

| R/W       | in       | Schreib/Lese-Zugriff                                                  |

| DS        | in       | Ein gültiger Wert liegt an der Datenleitung an (bei Schreiboperation) |

| RDY       | out      | Ein gültiger Wert liegt an der Datenleitung an (bei Leseoperation)    |

Tabelle 3 - Steuersignale von "Easy VME"

Eine **Leseoperation** funktioniert schrittweise wie folgt:

- VME-CPLD legt einen 22 Bit Wert auf die Adressleitung

- VME-CPLD setzt R/W HIGH (Leseoperation)

- VME-CPLD zieht Select 1 auf LOW

- RemFPGA verarbeitet die Anfrage

- RemFPGA legt einen 32 Bit Wert auf die Datenleitung

- RemFPGA zieht RDY auf LOW

- VME-CPLD verarbeitet die Eingabe

- VME-CPLD setzt Select 1 zurück auf HIGH

- RemFPGA setzt RDY zurück auf HIGH

#### Eine **Schreiboperation** funktioniert schrittweise wie folgt:

- VME-CPLD legt einen 22 Bit Wert auf die Adressleitung

- VME-CPLD legt einen 32 Bit Wert auf die Datenleitung

- VME-CPLD zieht R/W auf LOW (Schreiboperation)

- VME-CPLD zieht DS auf LOW (Daten stehen bereit)

- VME-CPLD zieht Select 1 auf LOW

- RemFPGA verarbeitet die Eingabe

- RemFPGA zieht RDY auf LOW

- VME-CPLD setzt Select 1 zurück auf HIGH

- RemFPGA setzt RDY zurück auf HIGH

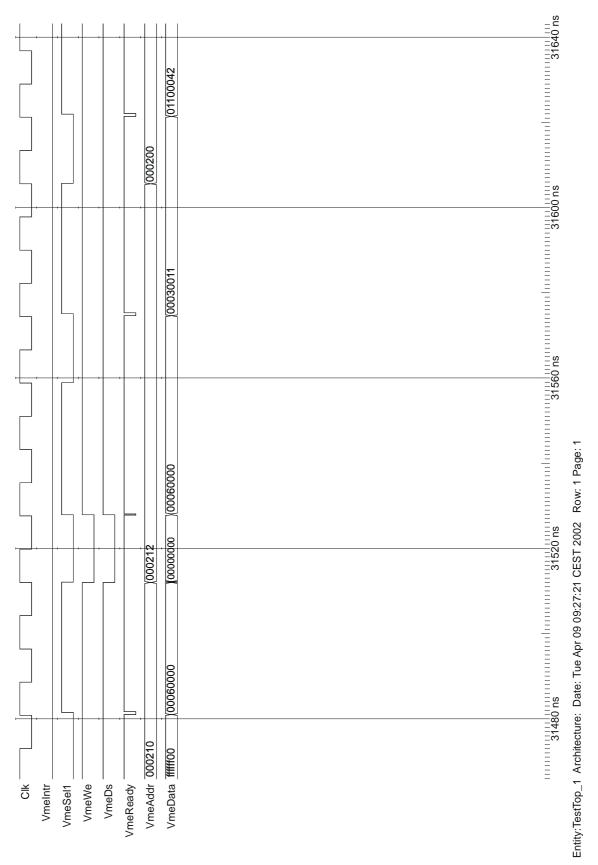

Sämtliche Signale sind vollständig asynchron. Das Interruptsignal des RemFPGA wird über interne Register des FPGA gesteuert. Eine Beschreibung der Adresszuordnung der VME Schnittstelle folgt in Kapitel 6.8.

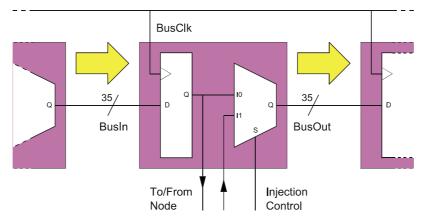

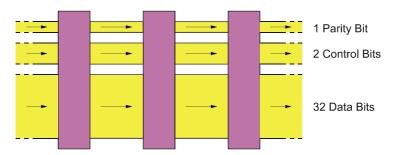

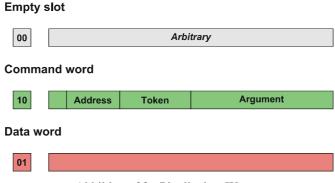

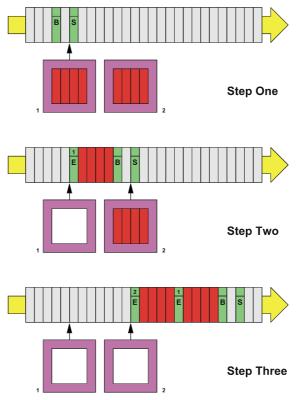

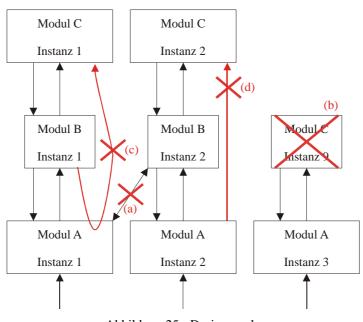

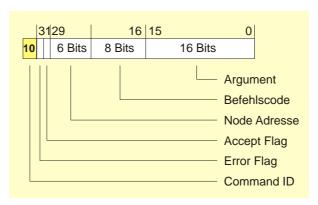

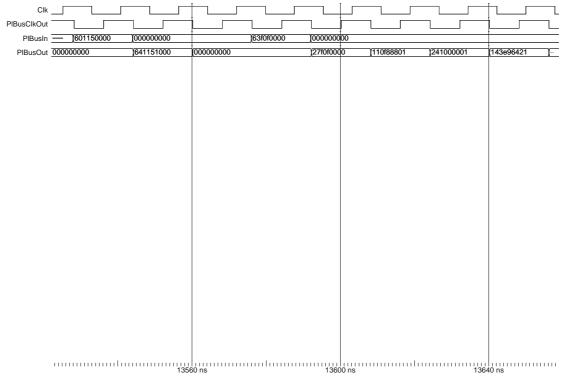

# 3.3.5 Das Pipelinebus Protokoll des RemFPGA

Der Pipelinebus wurde speziell für den Transport von ReadOUT Daten des Präprozessors entwickelt. Er vereint eine hohe Durchsatzrate bei geringer Störanfälligkeit mit einer relativ einfach zu implementierenden Schnittstelle und speziell auf den Bedarf des Präprozessors zugeschnittene Steuersignale.