### Ruprecht-Karls-Universität Heidelberg Fakultät für Physik und Astronomie Max - Planck - Institut für Kernphysik

IHEP 96-15 HD-ASIC-25-0996

# Entwicklung einer Testumgebung für einen ASIC im Rahmen des ATLAS Level-1-Triggers

Diplomarbeit von Gregor Wagner

# Inhaltsverzeichnis

| 1 | Ein | Einführung                         |                                                          |  |  |  |  |  |

|---|-----|------------------------------------|----------------------------------------------------------|--|--|--|--|--|

|   | 1.1 | Der La                             | arge-Hadron-Collider (LHC)                               |  |  |  |  |  |

|   |     | 1.1.1                              | Der Beschleuniger                                        |  |  |  |  |  |

|   |     | 1.1.2                              | Proton-Proton-Streuung                                   |  |  |  |  |  |

|   |     | 1.1.3                              | Bunch-Crossing-Rate und Luminosität                      |  |  |  |  |  |

|   |     | 1.1.4                              | Forschungsschwerpunkte am LHC                            |  |  |  |  |  |

|   | 1.2 | Der A                              | TLAS-Detektor                                            |  |  |  |  |  |

|   |     | 1.2.1                              | Innerer Detektor                                         |  |  |  |  |  |

|   |     | 1.2.2                              | Kalorimeter                                              |  |  |  |  |  |

|   |     | 1.2.3                              | Myonsystem                                               |  |  |  |  |  |

| 2 | Der | ATLA                               | AS Level-1-Kalorimetertrigger 20                         |  |  |  |  |  |

|   | 2.1 |                                    | r- und Auslesesystem des ATLAS-Detektors                 |  |  |  |  |  |

|   |     | 2.1.1                              | Level-1-Trigger                                          |  |  |  |  |  |

|   |     | 2.1.2                              | Level-2-Trigger                                          |  |  |  |  |  |

|   |     | 2.1.3                              | Level-3-Trigger                                          |  |  |  |  |  |

|   | 2.2 | Level-                             | 1-Triggeralgorithmen                                     |  |  |  |  |  |

|   |     | 2.2.1                              | $e^{\pm}/\gamma$ -Algorithmus                            |  |  |  |  |  |

|   |     | 2.2.2                              | Jetalgorithmus                                           |  |  |  |  |  |

|   |     | 2.2.3                              | $E_t^{miss}$ -Algorithmus                                |  |  |  |  |  |

|   | 2.3 |                                    |                                                          |  |  |  |  |  |

|   | 2.4 | evel-1-Kalorimetertriggerprozessor |                                                          |  |  |  |  |  |

|   |     | 2.4.1                              | Implementation des $e/\gamma$ -Algorithmus               |  |  |  |  |  |

|   |     | 2.4.2                              | Implementation des Jetalgorithmus im kompakten Design 31 |  |  |  |  |  |

|   |     | 2.4.3                              | Implementation des Jetalgorithmus im TP-Design           |  |  |  |  |  |

|   |     | 2.4.4                              | Simulation                                               |  |  |  |  |  |

|   |     | 2.4.5                              | Hardware Realisierung des Prozessor-ASICs                |  |  |  |  |  |

|   | 2.5 | Der T                              | ASIC                                                     |  |  |  |  |  |

|   |     | 2.5.1                              | Überblick                                                |  |  |  |  |  |

|   |     | 2.5.2                              | Der Clock Generator                                      |  |  |  |  |  |

|   |     | 2.5.3                              | Programmierbares Delay                                   |  |  |  |  |  |

|   |     | 2.5.4                              | Die Demultiplexerschaltungen                             |  |  |  |  |  |

|   |     | 2.5.5                              | Die CMOS-Schieberegister                                 |  |  |  |  |  |

|   |     | 2.5.6                              | Verwendung des internen Testmustergenerators             |  |  |  |  |  |

| $\mathbf{B}$ | Der                                      | nultipl               | exer für Chip-Tester-Einlese                   | 101             |  |  |  |  |  |  |

|--------------|------------------------------------------|-----------------------|------------------------------------------------|-----------------|--|--|--|--|--|--|

| $\mathbf{A}$ | Rat                                      | enverv                | vierfachung                                    | 97              |  |  |  |  |  |  |

| 5            | Zusammenfassung                          |                       |                                                |                 |  |  |  |  |  |  |

|              |                                          | 4.2.3                 | Biasstrom                                      | 94              |  |  |  |  |  |  |

|              |                                          | 4.2.2                 | Testprogramm                                   | 92              |  |  |  |  |  |  |

|              |                                          | 4.2.1                 | Montage der Interposer-Fassung                 | 91              |  |  |  |  |  |  |

|              | 4.2                                      | $\operatorname{Test}$ |                                                | 91              |  |  |  |  |  |  |

|              |                                          | 4.1.4                 | Layout des Adapterboards                       | 87              |  |  |  |  |  |  |

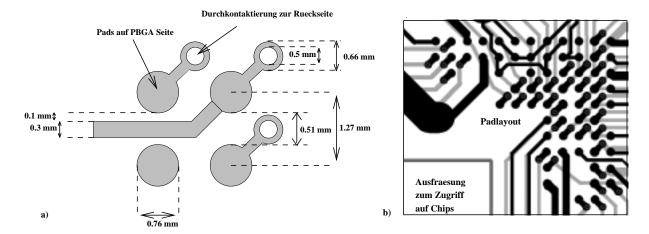

|              |                                          | 4.1.3                 | Die Interposer Fassung                         | 85              |  |  |  |  |  |  |

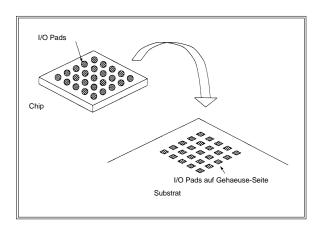

|              |                                          | 4.1.2                 | Das Ball-Grid-Array Gehäuse des TASICs         | 83              |  |  |  |  |  |  |

|              |                                          | 4.1.1                 | HP82k-Board                                    | 82              |  |  |  |  |  |  |

|              | 4.1 Testaufbau                           |                       |                                                |                 |  |  |  |  |  |  |

| 4            | Testaufbau und Test des TASIC 8          |                       |                                                |                 |  |  |  |  |  |  |

|              |                                          | 3.6.5                 | Test der Mikrostreifenleiter-Teststrecken      | 80              |  |  |  |  |  |  |

|              |                                          | 3.6.4                 | Kabeltests                                     | 78              |  |  |  |  |  |  |

|              |                                          | 3.6.3                 | Zeitstabilität                                 | 74              |  |  |  |  |  |  |

|              |                                          | 3.6.2                 | Messung der Signalanstiegszeit                 | 73              |  |  |  |  |  |  |

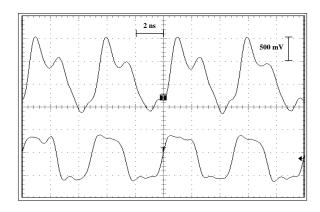

|              | 3.0                                      | 3.6.1                 | Messungen der Signale                          | 70              |  |  |  |  |  |  |

|              | 3.6                                      |                       | ngen                                           | 69              |  |  |  |  |  |  |

|              | 3.5                                      |                       | ste Testplatine                                | 68              |  |  |  |  |  |  |

|              | 3.4                                      |                       | plan der Ratenverdoppelungsschaltung           | 67              |  |  |  |  |  |  |

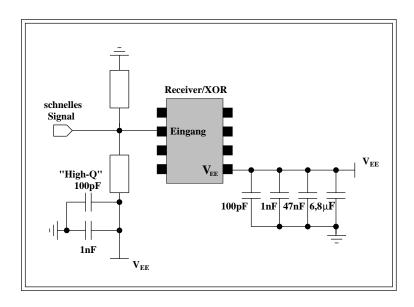

|              |                                          | 3.3.6                 | Stabilisierung der Versorgungsspannung         | 66              |  |  |  |  |  |  |

|              |                                          | 3.3.5                 | Signaldämpfung                                 | 65              |  |  |  |  |  |  |

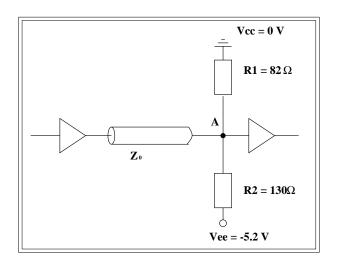

|              |                                          | 3.3.4                 | Terminierung der Leiterbahnen                  | 65              |  |  |  |  |  |  |

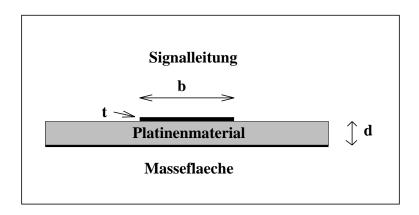

|              |                                          | $3.3.2 \\ 3.3.3$      | Mikrostreifenleiterbahnen                      | $\frac{62}{63}$ |  |  |  |  |  |  |

|              |                                          | 3.3.1                 | Signalreflektionen                             | 60              |  |  |  |  |  |  |

|              | 3.3                                      |                       | u von HF Schaltungen                           | 59              |  |  |  |  |  |  |

|              |                                          | 3.2.1                 | ECL - Logik                                    | 57              |  |  |  |  |  |  |

|              | 3.2                                      |                       | equenzverdoppelung                             | 56              |  |  |  |  |  |  |

|              | 3.1                                      |                       | P82000 Chip Tester                             | 54              |  |  |  |  |  |  |

| 3            | Erzeugung serieller 800 Mbit/s Signale 5 |                       |                                                |                 |  |  |  |  |  |  |

|              |                                          | 2.0.0                 | Donaing and General Triville Triville Triville | 0_              |  |  |  |  |  |  |

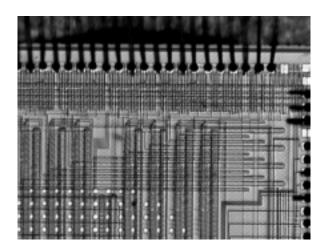

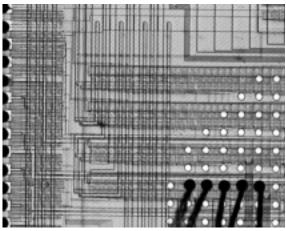

|              |                                          | $\frac{2.5.1}{2.5.8}$ | Bonding und Gehäuse                            | 51              |  |  |  |  |  |  |

|              |                                          | 2.5.7                 | Spannungsversorgung                            | 51              |  |  |  |  |  |  |

## Einleitung

Am Large-Hadron-Collider (LHC) werden Protonenpakete mit einer Frequenz von 40 MHz zur Kollision gebracht. Die dabei in einem Detektor auftretenden hohen Datenmengen müssen von einem Triggersystem verarbeitet werden. Nach der Digitalisierung werden die Signale zur Reduzierung der Datenkanäle serialisiert, was zu einer Erhöhung der Ubertragungsrate pro Datenkanal führt. Ein Ansatz der ersten Triggerstufe des ATLAS-Detektors sight vor, alle Komponenten des Level-1-Kalorimetertriggeralgorithmus für einen eingeschränkten Raumwinkelbereich auf einem Application Specific Integrated Circuit (ASIC) zu implementieren. Dieser erhält Eingangsdaten vom Kalorimeter mit einer Datenrate von 800 Mbit/s. Die vorliegende Diplomarbeit hatte zum Ziel, einen Test-ASIC (TASIC), der eine Vorstufe zum Triggerprozessor-ASIC darstellt, zu testen. Wie der Prozessor-ASIC benötigt auch der TASIC Testsignale mit einer Datenrate von 800 Mbit/s. Der HP82000 Chip-Tester, mit dem die Tests durchgeführt wurden, erzeugt digitale Signale mit einer Datenrate von 400 Mbit/s. Als Grundvoraussetzung für den Test wurde eine Platine zur Verdoppelung der Datenrate entwickelt. Um die Testsignale zum TASIC zu leiten und Signale aus diesem auslesen und mit dem Chip-Tester auswerten zu können, wurde ein Adapterboard für den TASIC entworfen. Zum Jettriggeralgorithmus, der auf dem Prozessor-ASIC implementiert wird, sind Monte-Carlo-Simulationsstudien zum Vergleich mit einer weiteren Implementierung des Jetalgorithmus durchgeführt worden.

Nach einem einleitenden Kapitel, das die physikalischen Grundlagen am LHC und den ATLAS-Detektor kurz beschreibt, wird in Kapitel 2.1 die erste Triggerstufe des ATLAS-Triggersystems vorgestellt. Es werden die Triggeralgorithmen und ihre konkrete Implementierung auf dem Prozessor-ASIC beschrieben. Die Ergebnisse der Jettrigger-Simulationen finden sich im Anschluß an die Darstellung der beiden Jetalgorithmen. Eine detaillierte Funktionsbeschreibung des TASICs in Hinblick auf die zu erfolgenden Tests schließt dieses Kapitel ab. Im dritten Kapitel, das einen Schwerpunkt der Arbeit darstellt, sind die Ratenverdoppelungsschaltung und Messungen der so erzeugten Signale beschrieben. Der eigentliche Aufbau zur Durchführung der Tests findet sich in Kapitel 4. Die Arbeit wird durch eine Zusammenfassung (Kapitel 5) abgeschlossen.

## Kapitel 1

## Einführung

### 1.1 Der Large-Hadron-Collider (LHC)

### 1.1.1 Der Beschleuniger

Mit dem Bau des Large-Hadron-Colliders am Europäischen Zentrum für Teilchenphysik (CERN) bei Genf, der im Jahre 2005 seinen Betrieb aufnehmen soll, dringen Physiker in einen bisher unerforschten Bereich der Physik ein. Protonen werden in zwei getrennten Strahlrohren auf eine Energie von jeweils 7000 GeV beschleunigt, wobei die Umlaufrichtung der Protonen in beiden Ringen gegenläufig ist. An vier Wechselwirkungspunkten werden die Protonstrahlen zusammengeführt, so daß es dort zu Streuungen zwischen den Protonen beider Strahlen bei einer Schwerpunktsenergie von  $\sqrt{s}=14~TeV$  kommen kann.

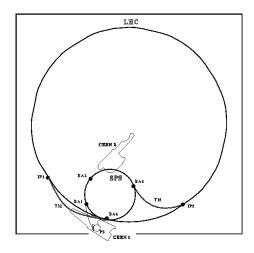

Abbildung 1.1: Schematischer Aufbau der Beschleunigerkette am CERN. Nicht zu sehen sind der Linearbeschleuniger und Booster, die die erste Stufe des Beschleunigungsprozesses durchführen

Zur Beschleunigung der Protonen werden die bereits existierenden Einrichtungen am CERN so weit wie möglich genutzt. So wird der LHC in dem Tunnel des LEP- Beschleunigers errichtet, nachdem dieser seinen Betrieb eingestellt hat und abgebaut worden ist. Zur Vorbeschleunigung der Protonen wird eine Kette bereits auf dem CERN-Gelände bestehender Beschleuniger verwendet. Abbildung 2.3 [1] zeigt den LHC-Ring und seine Vorbeschleuniger.

In einem Linearbeschleuniger werden Protonen auf eine Energie von 50 MeV gebracht und anschließend in den Booster des PS eingespeist, der eine weitere Beschleunigung auf 1.4 GeV bewirkt. Im PS-Ring werden die Protonen auf 26 GeV und nach Überleitung in den SPS-Beschleuniger auf eine Energie von 450 GeV beschleunigt. An zwei Stellen des SPS-Ringes werden die Protonen ausgekoppelt und in jeweils einen der gegenläufigen Ringe des LHCs überführt, wo die Energie auf 7000 GeV erhöht wird.

### 1.1.2 Proton-Proton-Streuung

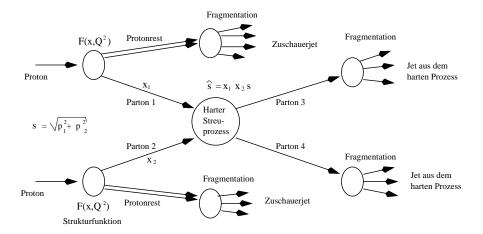

Bei Streuungen von Hadronen dominiert im Gegensatz zur Lepton-Lepton-Streuung der sehr hohe Wirkungsquerschnitt der starken Wechselwirkung. Die starke Wechselwirkung zwischen Hadronen wird beschrieben durch die QCD. Das Proton ist aus farbtragenden Partonen (Quarks und Gluonen) zusammengesetzt, die durch Farbkräfte zusammengehalten werden, welche durch den Austausch von Gluonen übertragen werden. Bei der Kollision zweier Protonen kann es zur Wechselwirkung zwischen den Quarks und Gluonen der beiden Protonen kommen, wobei ein Impulsübertrag von dem einen Parton auf das andere stattfindet. Zwischen den gestreuten Partonen und den Protonresten bauen sich Farbfelder auf. Mit zunehmendem Abstand der Partonen wächst die Energie der Farbfelder, bis die Energiedichte zur Erzeugung von Quark-Antiquark-Paaren ausreicht. Diese Prozesse wiederholen sich, bis die Energiedichte der Farbfelder zwischen den Quarks so weit gesunken ist, daß es nicht mehr zur Bildung weiterer Quark-Antiquark-Paare kommt. Die Partonen schließen sich wieder zu farbneutralen Hadronen zusammen. Im Detektor beobachtet man Hadronenjets, falls der übertragene Impuls bei der Streuung groß gegenüber der Hadronenruhemasse ist (siehe Bild 1.2).

Abbildung 1.2: Schematische Darstellung eines inelastischen Streuprozesses in der Proton-Proton-Wechselwirkung

in eine der Strahlrichtungen geboostet. der Streuung und x den Impulsanteil des beteiligten Partons angibt. geben. Die Verteilung der Anteile am Longitudinalimpuls - der zur Strahlachse paral-Proton-Streuungen dar. der Teilchenimpulse die entscheidende physikalische Größe in der Analyse der Protonfür einen einzelnen Prozeß nicht bekannt. Damit stellen die nen in Schwerpunktsenergie bei der Streuung der beiden Partonen ist daher gegeben durch durch die Strukturfunktion  $F_1(x,Q^2)$  beschreiben, wobei  $\sqrt{Q^2}$  den Impulsübertrag bei lelen Impulskomponente - des Protons, der von einem Parton getragen wird, läßt sich **√**ŝ Die Schwerpunktsenergie des Proton-Proton-Systems ist durch  $\sqrt{s} =$  $x_1x_2s$ . der Regel voneinander abweichen, ist das Schwerpunktssystem der Streuung Weil die Impulsanteile der beiden an der Streuung beteiligten Parto-Die Größe dieser Longitudinalbewegung ist Transversalkomponenten Die reduzierte  $\sqrt{p_1 + p_2^2}$  ge-

Polarwinkels wird in den meisten Fällen die Als Koordinaten dienen der Azimutwinkel  $\phi$  und der Polarwinkel  $\theta$ . Pseudorapidität 7 verwendet. Anstatt des Sie ist

$$\eta = -\ln \tan \frac{\theta}{2} \tag{1.1}$$

mit dem Azimutwinkel:

$$\theta = \arctan \frac{|\vec{p_t}|}{|\vec{p_t}|} \tag{1.2}$$

und

$$|p_{\perp}| = \sqrt{p_x^2 + p_y^2} \tag{1.3}$$

$\operatorname{Der}$ dementsprechend eine Pseudorapidität von  $\eta=0$  zugeordnet.  $(180^{\circ})$  gezählt.  $p_t$  und  $p_l$  stellen die transversale bzw. longitudinale Komponente des Impulses dar Polarwinkel wird von der einen Strahlachse (0°) bis zur anderen Strahlrichtung  $\operatorname{Der}$ Querschnittsebene, die den Wechselwirkungspunkt enthält, ist

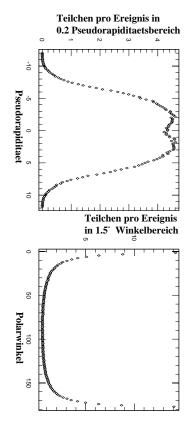

Abbildung (links) und des Polarwinkels  $\theta$  (rechts). Carlo Simulation. 1.3: Die Teilchenanzahl pro Die Kurven zeigen Ergebnisse einer Monte-Ereignis als Funktion der Pseudorapidität

Entsprechend bedeuten große Beträge der Pseudorapidität Winkelbereiche in Richtung der Strahlachsen. Der Grund für die Verwendung der Pseudorapidität liegt darin, daß die Teilchendichte in einem großen zentralen Pseudorapiditätsbereich annähernd konstant ist (siehe Abbildung 1.3). Ein weiterer Vorteil liegt in ihrem einfachen Transformationsverhalten unter Lorentztransformationen. Im Grenzwert  $\frac{v}{c} \rightarrow 1$  sind Pseudorapiditätsdifferenzen invariant unter einem Lorentz-Boost.

Eine weitere bedeutsame Größe ist der fehlende Beitrag in der Vektorsumme aller Transversalimpulse  $\sum \vec{p_{i\perp}}$ . Aufgrund der Erhaltung des Gesamtimpulses sollte diese Summe verschwinden. Teilchen, die keine Energie im Detektor deponieren, führen jedoch zu einem von Null abweichenden Wert in der Vektorsumme. Auf diese Weise lassen sich beispielsweise Rückschlüsse auf die Transversalimpulse von Neutrinos machen. Gleichbedeutend mit dem Transversalimpuls wird auch der Begriff der Transversalenergie  $E_{\perp} = |\vec{p_\perp}|$  verwendet. Dies bringt zur Geltung, daß mit einem Kalorimeter Energien gemessen werden. Ebenso spricht man daher auch von der fehlenden Transversalenergie  $E_t^{miss}$ , womit die Vektorsumme aller Transversalimpulse gemeint ist.

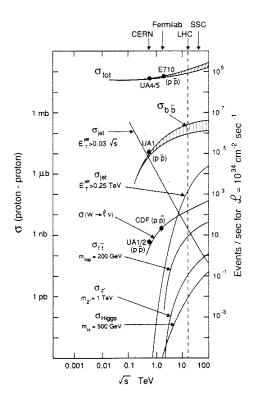

Abbildung 1.4: Totaler Wirkungsquerschnitt für Proton-Proton-Streuung im Vergleich zu den Wirkungsquerschnitten von physikalisch interessanten Prozessen in Abhängigkeit von der Schwerpunktsenergie

In Abbildung 1.4 [2] sind Wirkungsquerschnitte für Proton-Proton-Streuung als Funktion der Schwerpunktsenergie aufgetragen. Für die beim LHC geplante Schwerpunktsenergie von 14 TeV beträgt der totale Wirkungsquerschnitt ungefähr 100 mb.

Zum Vergleich sind die Wirkungsquerschnitte einiger möglicher Prozesse<sup>1</sup>, die von besonderem physikalischen Interesse sind, dargestellt. Diese sind zum Großteil elektroschwache Prozesse, so daß die Wirkungsquerschnitte für diese sehr klein sind. Sie sind daher von einer um einige Größenordnungen höheren Rate an inelastischen Proton-Proton-Streuungen überlagert.

### 1.1.3 Bunch-Crossing-Rate und Luminosität

Der Teilchenstrom im LHC ist nicht kontinuierlich. Vielmehr sind die Protonen in Paketen, Bunches, gebündelt. Der zeitliche Abstand zwischen zwei aufeinanderfolgenden Bunches beträgt 25 ns, womit man eine Bunch-Crossing-Rate<sup>2</sup> von 40 MHz erhält.

Ein Maß für die Intensität der Teilchenstrahlen ist die Luminosität eines Beschleunigers. Sie gibt an, wie viele Teilchen sich am Wechselwirkungspunkt pro Zeiteinheit und Querschnittsfläche durchdringen und ist bei einer Kollision zweier Teilchenstrahlen in einem Speicherring gegeben durch [3]:

$$\mathcal{L} = \frac{N_a N_b n v / U}{A} \tag{1.4}$$

$N_a$  und  $N_b$  sind die Anzahl der Teilchen in einem Bunch des jeweiligen Strahls, n gibt die Anzahl der Bunches im Speicherring mit dem Umfang U an, v ist die Geschwindigkeit der Teilchen und A die Querschnittsfläche der Strahlen am Kollisionspunkt. Das Produkt aus Luminosität und Wirkungsquerschnitt ergibt direkt die Anzahl der Reaktionen, die man pro Zeiteinheit beobachten kann.

Sollen Reaktionen mit einem sehr geringen Wirkungsquerschnitt untersucht werden, ist es wünschenswert, eine möglichst hohe Luminosität zu erreichen, damit die Aufnahme einer Datenmenge mit ausreichender Statistik in einem akzeptablen Zeitraum durchgeführt werden kann. Für den LHC ist eine Luminosität von  $10^{34}cm^{-2}s^{-1}$  vorgesehen. Auf der anderen Seite steigt auch die Rate der inelastischen Proton-Proton-Streuungen mit der Luminosität. Mit einem totalen Wirkungsquerschnitt für Proton-Proton-Streuung von  $\sigma_{tot}=100mb$  ergibt sich so eine Ereignissrate von  $10^9$  Wechselwirkungen pro Sekunde, was eine durchschnittliche Anzahl von 25 Proton-Proton-Streuungen in jedem Bunch-Crossing ergibt. Diese Ereignisse stellen in den Detektoren am LHC einen Untergrund dar. Die Signaturen der interessanten Ereignisse im Detektor sind von den Teilchenspuren dieser weichen Streuungen überlagert. Aufgabe des Triggersystems eines LHC-Detektors ist es, diesen Untergrund zu unterdrücken und interessante Ereignisse mit physikalischem Gehalt zu selektieren.

Für die Selektion von Ereignissen mit komplizierten Signaturen im Detektor, z.B.  $\tau$ -Zerfällen oder Zerfällen schwerer Quarks, stellt ein hoher Untergrund ein großes Hindernis dar. Bei einer Erniedrigung der Luminosität wird der Untergrund im Detektor entsprechend gesenkt und eine Auswertung der Signaturen auf Kosten der Ereignisrate

<sup>&</sup>lt;sup>1</sup>Hierbei handelt es sich teilweise um Prozesse, welche neue Physik beinhalten und deren Auftreten daher ungewiß ist.

<sup>&</sup>lt;sup>2</sup>Unter der Bunch-Crossing-Rate versteht man die Frequenz, mit der die gegeneinanderlaufenden Teilchenpakete sich an den Wechselwirkungspunkten kreuzen. Bei dem LHC geschieht dies alle 25 ns.

erleichtert. Im Anfangsbetrieb des LHCs wird der Beschleuniger bei einer niedrigeren Luminosität von  $\mathcal{L}=10^{33}cm^{-2}s^{-1}$  betrieben, was zur Untersuchung komplizierter Ereignissignaturen ausgenutzt werden kann.

### 1.1.4 Forschungsschwerpunkte am LHC

Die zentrale Frage, die mit dem LHC geklärt werden soll, ist die Existenz des Higgs-Bosons (kurz: H). Das Standardmodell der Teilchenphysik fordert dieses Teilchen zur Erklärung der Symmetriebrechung in der quantenmechanischen Beschreibung der elektroschwachen Wechselwirkung, um die Teilchenmassen zu erklären. Dieses Higgs-Boson konnte bisher noch nicht entdeckt werden und stellt daher eine der letzten großen Lücken im Standardmodell dar. Die Masse des Higgs-Bosons ergibt sich nicht durch theoretische Überlegungen. Einige Theorien sagen jedoch eine obere Schranke von etwa 1 TeV für die Higgsmasse vorher. Eine untere Grenze der Higgsmasse läßt sich durch die bis heute durchgeführten Experimente, bei denen das Higgs-Boson nicht beobachtet wurde, angeben. So ist der mögliche Massenbereich des Higgs-Bosons zwischen etwa 70 GeV und ungefähr 1 TeV eingeschränkt. Da die Produktion und die möglichen Zerfälle des Higgs-Bosons von seiner Masse abhängen, interessieren in den verschiedenen Higgsmassenbereichen unterschiedliche experimentelle Signaturen für die Suche nach dem Higgs-Boson. Diese sind:

| Zerfallskanal                                                                     | Massenbereich                |

|-----------------------------------------------------------------------------------|------------------------------|

| H 	o b ar b                                                                       | $80 < m_H < 100 \; { m GeV}$ |

| $\mid H  ightarrow \gamma \gamma$                                                 | $90 < m_H^- < 150  { m GeV}$ |

| $H ightarrow ZZ^* ightarrow 4l^\pm$                                               | $130 GeV < m_H < 2m_Z$       |

| $H ightarrow ZZ ightarrow 4l^{\pm}, 2l^{\pm}2 u$                                  | $m_H>2m_Z$                   |

| $igg  H  ightarrow WW, ZZ  ightarrow l^{\pm} u + 2 \; Jets, 2l^{\pm} + 2 \; Jets$ | $m_Hpprox 1~TeV$             |

Ein weiteres Ziel des LHC ist die Suche nach SUSY-Teilchen. Supersymmetrische Theorien stellen eine Vereinheitlichung der in Fermionen und Bosonen unterteilten Welt der Teilchenphysik dar, indem sie zu jedem elementaren Teilchen einen supersymmetrischen Partner mit einem um den Betrag 1/2 unterschiedlichen Spin fordern. Somit besitzt jedes Fermion einen bosonischen SUSY-Partner, während ebenso zu jedem Boson ein Fermion gehört. Da supersymmetrische Teilchen bisher nicht beobachtet worden sind, müssen die Massen der beobachtbaren SUSY-Teilchen sehr groß sein. Beim Zerfall solcher Teilchen entstehen Leptonen und Jets mit hohem Transversalimpuls. Entsteht beim Zerfall ein neutrales stabiles supersymmetrisches Teilchen, so verläßt dieses ohne Energiedeposition den Detektor und erzeugt einen großen  $E_t^{miss}$ -Beitrag.

Ein gerade in jüngster Zeit durch Messungen der CDF-Kollaboration am Tevatron ins Blickfeld gerücktes Thema ist die Substruktur von Quarks [4]. Falls die im Standardmodell als elementar und damit punktförmig angesehenen Quarks aus kleineren Teilchen zusammengesetzte Gebilde wären, würde sich dies in einer Abweichung der von der QCD vorhergesagten Wirkungsquerschnitte für die Jetproduktion bei großem

Impulsübertrag erkennbar machen. Eine genaue Messung der Raten von Jets mit hohem Transversalimpuls ist daher erforderlich.

Die Untersuchung der beim LHC in hohen Raten erzeugten schweren Quarks, beauty- and top-quarks, wird ein weiteres Forschungsgebiet am LHC darstellen. Mit B-Mesonen kann die CP-Verletzung gemessen werden. Für die Analyse solcher Ereignisse ist eine genaue Rekonstruktion der komplexen Signaturen, welche ein Zerfall von schweren Quarks im Detektor hinterläßt, von Bedeutung. Dies wird besonders im LHC-Betrieb mit verringerter Luminosität von  $\mathcal{L}=10^{33}cm^{-2}s^{-1}$  ein Hauptuntersuchungsbereich sein.

Die Liste der Forschungsgebiete der Hochenergiephysik, die mit dem LHC untersucht werden können, ließe sich noch fortsetzen [2],[5]. Es soll aber an dieser Stelle nicht weiter darauf eingegangen werden. Vielmehr dienen die oben genannten Beispiele zur Illustration der Anforderungen, die an einen LHC-Detektor und dessen Datenauslesesystem gestellt werden. Zu diesen gehört die Erkennung und Energiemessung von Elektronen, Photonen, Myonen sowie Jets. Zur Messung der fehlenden Transversalenergie  $E_T^{miss}$  muß der Detektor einen möglichst großen Akzeptanzbereich abdecken. Die passiven Zonen im Detektor sollten klein sein, damit die Bestimmung der fehlenden Transversalenergie nicht durch ungesehene Teilchen verfälscht wird und auch die Messung der Lepton- und Jetenergien nicht zu stark beeinträchtigt wird. Aufgabe des Triggersystems der Detektoren ist es, eine deutliche Reduzierung der hohen QCD-Untergrunddatenrate zu bewirken.

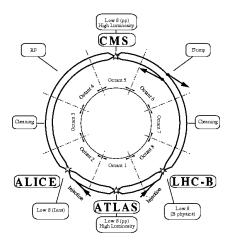

Abbildung 1.5: Schematische Darstellung des LHC mit den vier Experimenten

Am LHC werden vier Experimente aufgebaut. Die Hauptdetektoren CMS und AT-LAS liegen an gegenüberliegenden Wechselwirkungszonen der LHC Protonenstrahlen. Mit dem Alice-Detektor ist ein Spezialdetektor zur Untersuchung von Schwerionenreaktionen³ vorgesehen. Das LHC-B Experiment widmet sich speziell der Untersuchung der CP-Verletzung in B-Meson-Systemen.

<sup>&</sup>lt;sup>3</sup>Zusätzlich zum p-p Betrieb des LHC ist die Beschleunigung schwerer Ionen vorgesehen. Bleikerne werden dabei bei einer Schwerpunktsenergie von 1150 TeV zur Kollision gebracht.

### 1.2 Der ATLAS-Detektor

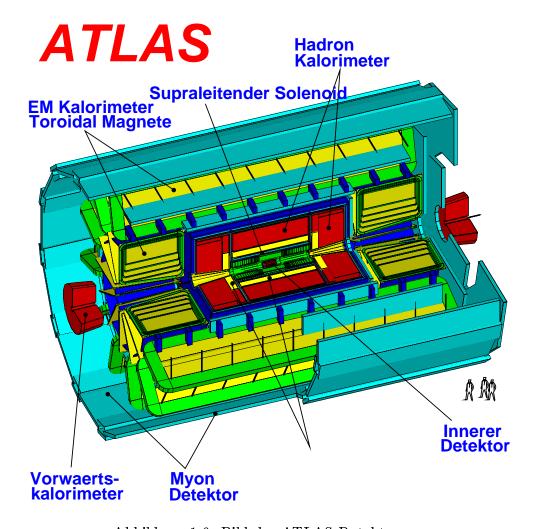

Abbildung 1.6: Bild des ATLAS-Detektors

ATLAS (A Toroidal LHC ApparatuS) ist einer der beiden Universaldetektoren am LHC. Da sich die Kinematik der Proton-Proton-Streuung invariant unter Rotation um die Strahlachse verhält und keine der beiden Strahlrichtungen kinematisch bevorzugt ist, ist auch der ATLAS-Detektor zylindersymmetrisch bezüglich der Strahlachse und spiegelsymmetrisch in Bezug auf die Querschnittsebene, welche den Wechselwirkungspunkt schneidet, aufgebaut. Der ATLAS-Detektor erstreckt sich jeweils auf eine Länge von 21 m auf beiden Seiten des Wechselwirkungspunktes und nimmt eine Höhe von 22 m ein. Das Gewicht des kompletten Detektorsystems beträgt 7000 t.

Abbildung 1.6 zeigt eine Darstellung des ATLAS-Detektors. Im Zentrum in Nähe des Wechselwirkungspunktes befindet sich der Innere Detektor für die hochauflösende Rekonstruktion von Teilchenspuren. Umgeben ist dieser von einem Solenoid-Magneten, der im Innenraum ein homogenes Magnetfeld mit einer Feldstärke von 2T erzeugt, welches die Teilchen in Ebenen senkrecht zur Strahlachse ablenkt. Die Transversalimpulse

der Teilchen können aus den Bahnradien bestimmt werden. Das Kalorimeter dient zur Messung der Teilchenenergien und ist unterteilt in ein elektromagnetisches Kalorimeter für Elektronen und Photonen und das in seinen geometrischen Dimensionen größere hadronische Kalorimeter. Die Erkennung von Myonen und die Messung des Myonenimpulses erfolgt mit separaten Myonkammern, die das hadronische Kalorimeter umgeben. Magnetspulen erzeugen in den Myonenkammern ein toroidales Magnetfeld, das die Myonen in Ebenen, die die Strahlachse enthalten, ablenkt und so eine Impulsmessung ermöglicht.

#### 1.2.1 Innerer Detektor

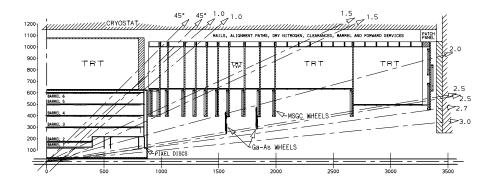

Abbildung 1.7: Aufbau des Inneren Detektors. In der linken unteren Ecke befindet sich der Wechselwirkungspunkt. Die im Bild eingezeichneten Pfeile dienen zur Abgrenzung von Pseudorapiditätsbereichen

Abbildung 1.7 zeigt den Aufbau des Inneren Detektors, der einen Pseudorapiditätsbereich von  $|\eta| < 2.5$  überdeckt. Die Aufgabe des Inneren Detektors besteht in einer möglichst genauen Rekonstruktion der Teilchenspuren, die zur Bestimmung der Teilchenimpulse, Teilchensorte und Vertexrekonstruktion verwendet werden. Zu diesem Zweck benutzt man Halbleiterdetektoren mit einer hohen Ortsauflösung (im Mikrometerbereich). Um genügend Platz für Elektronik, Stromzuführung und Kühlungssysteme für die Halbleiterdetektoren zu haben, können die Detektoren nicht beliebig dicht um den Wechselwirkungspunkt angeordnet sein. Dem Wechselwirkungspunkt am nächsten befinden sich Pixeldetektoren, die ein hohes Ortsauflösungsvermögen besitzen und Informationen in zwei Dimensionen zur Spurrekonstruktion bereitstellen. Diese sind von Siliziumstreifendetektoren umgeben. Hierbei ist jede Streifenlage zwei- oder dreifach ausgeführt, wobei die einzelnen Streifen der verschiedenen Ausführungen kleine Winkel zueinander aufweisen. Mit dieser Anordnung kann auch hier eine Ortsinformation in zwei Koordinaten erzielt werden, wobei jedoch Mehrdeutigkeiten bei der Zuordnung der Koordinaten auftreten können. Im Bereich größerer Radien werden Drahtkammern, die gleichzeitig als Übergangsstrahlungsdetektoren (TRT) benutzt werden, verwendet, welche eine Bestimmung des Radius und Azimutwinkels  $\phi$  erlauben. Mit Hilfe der Übergangsstrahlung können Elektronen identifiziert werden. Auf diese Weise werden pro Teilchenspur, die in einem Bereich mit  $|\eta| < 2.5$  verlaufen, sechs hochpräzise Raumpunktmessungen durch die zentralen Halbleiterdetektoren und mindestens 36 Treffer der Drahtkammern aufgenommen, aus denen sich die Teilchenspur rekonstruieren läßt.

#### 1.2.2 Kalorimeter

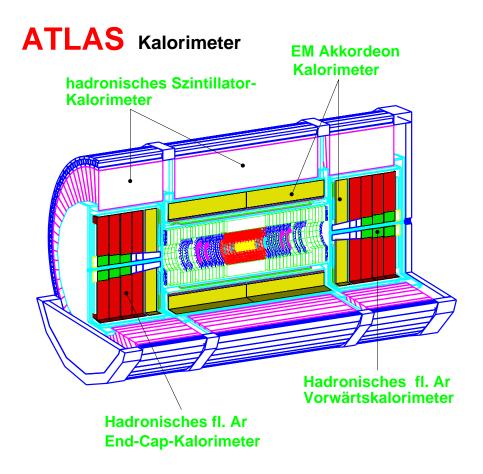

Abbildung 1.8: Darstellung des ATLAS-Kalorimeters mit dem Inneren Detektor

Der Innere Detektor wird bis auf kleinere Rapiditätslücken vom Kalorimeter umschlossen (siehe Abbildung 1.8). Es ist unterteilt in ein elektromagnetisches und ein hadronisches Kalorimeter. Das elektromagnetische Kalorimeter setzt sich aus dem zentralen Barrel-Bereich und den End-Cap-Kalorimetern in den Strahlrichtungen zusammen. Das elektromagnetische Barrel und die End-Cap-Kalorimeter überdecken zusammmen einen Pseudorapiditätsbereich von  $|\eta| < 3.2$ . Das größere hadronische Kalorimeter, welches das elektromagnetische Kalorimeter umgibt, besteht wie das elektromagnetische aus einer Barrel und zwei End-Cap-Komponente mit einer Ausdehnung längs der Strahlachse von  $|\eta| < 3.2$ . Zusätzlich befinden sich auf jeder Seite

ein hadronisches Vorwärtskalorimeter, das den Pseudorapiditätsbereich des hadronischen Kalorimeters bis  $|\eta| < 5$  ausdehnt. Anforderungen an ein Kalorimetersystem für einen LHC-Detektor sind u.a.:

- Ein gutes Energieauflösungsvermögen

- Eine gute Ortsauflösung durch eine genügend feine Segmentierung (Granularität) des Detektors. Die Segmentierung sollte hierbei mindestens so fein sein, daß eine Trennung von relativ schmalen elektromagnetischen Schauern durch isolierte Elektronen oder Photonen von den Schauern, die durch vergleichbar breite Jets hervorgerufen werden, ermöglicht wird.

- Ein hoher dynamischer Bereich in der Energiemessung, der von einigen hundert MeV bis zu 1.5-3 TeV pro Zelle reicht.

- Zur genauen Messung der fehlenden Transversalenergie ist ein möglichst großer Überdeckungsbereich in  $\eta$  erforderlich. (vgl. hierzu Abbildung 1.3)

#### Elektromagnetisches Kalorimeter

Der zentrale Barrel-Bereich des elektromagnetischen Kalorimeters erstreckt sich in einem Pseudorapiditätsbereich von  $|\eta| < 1.4$ . Die elektromagnetischen End-Cap-Kalorimeter erweitern die  $|\eta|$ -Überdeckung um  $|\eta| = [1.4, 3.2]$ . Sowohl Barrel als auch End-Cap-Kalorimeter sind als sogenannte Sampling-Kalorimeter aufgebaut. Bei Sampling-Kalorimetern ist, im Gegensatz zu homogenen Kalorimetern, das sensitive Detektormaterial, in dem die Teilchenenergien durch Ionisation in elektrische Impulse umgesetzt werden, vom passiven Absorbermaterial getrennt. Im Absorbermaterial lösen die hochenergetischen Elektronen und Photonen durch Bremsstrahlung bzw. Paarbildung elektromagnetische Teilchenschauer aus und verteilen so ihre Energie auf mehrere Sekundärteilchen. Auch Hadronen geben einen Teil ihrer Energie im elektromagnetischen Kalorimeter durch Ionisation und Kernwechselwirkungen ab. Die Absorberplatten sind dabei in einer akkordeonähnlichen Form angeordnet. Diese Geometrie ermöglicht es, die einzelnen Segmente ohne Lecks nebeneinander anzuordnen. Als Absorber wird Blei verwendet, da Blei eine große Ordnungszahl Z besitzt und der Wirkungsquerschnitt für Bremsstrahlung und Paarbildung proportional zu  $\mathbb{Z}^2$  ist. Die Dicke des Absorbermaterials beträgt an der dünnsten Stelle ( $\eta = 0$ )  $26X_0^4$  und im ausgedehntesten<sup>5</sup> Bereich 28X<sub>0</sub>. Als aktives Detektormaterial befinden sich schmale (3.88 mm) mit flüssigem Argon gefüllte Lücken zwischen den Bleiplatten. Flüssiges Argon wird wegen seiner strahlungsharten Eigenschaften verwendet. Die Energieauflösung läßt sich durch Gleichung 1.5 beschreiben. Diese Abschätzung stellt hierbei eine obere Grenze dar, die der Fehler des elektromagnetischen Kalorimeters nicht überschreiten darf.

$<sup>^4</sup>X_0$  ist die Strahlungslänge des Absorbermaterials. Die Energie eines Elektrons ist im Mittel nach Durchdringen einer Absorberschicht der Dicke  $X_0$  auf den 1/e-ten Bruchteil der Anfangsenergie abgesunken. Die Strahlungslänge von Blei beträgt 0.56 cm.

<sup>&</sup>lt;sup>5</sup>Man beachte hier, daß die Absorberdicke, die vom Wechselwirkungspunkt aus gesehen wird, in Richtung der Strahlachsen zunimmt.

$$\frac{\Delta E}{E} = \frac{10\%}{\sqrt{E/GeV}} \oplus 0.7\% \tag{1.5}$$

Der energieabhängige erste Term wird durch statistische Fluktuationen in der Schauerbildung verursacht, die von der geometrischen Anordnung der Absorber- und Flüssig-Argon-Schichten abhängig ist. Der konstante Beitrag in Gleichung 1.5, der bei der Messung von Teilchen mit hoher Energie dominiert, wird durch Inhomogenitäten im Kalorimeter und lokale Variation der Eichparameter hervorgerufen [6]. In der Tiefe ist das elektromagnetische Kalorimeter in drei Schichten eingeteilt, wobei die erste Schicht eine feinere Ortsunterteilung besitzt als die beiden folgenden (siehe Tabelle 1.1). Die hohe Ortsauflösung der ersten Lage wird zur Trennung von isolierten Photonen und Photonen, die aus  $\pi^0$ -Zerfällen stammen, benötigt. Im Bereich des Barrels befinden sich vor der ersten Kalorimeterlage die Spule und die mechanische Halterung des Solenoidmagneten. Da dieses für geladene Teilchen und Photonen ein Absorbermaterial darstellt und es dort daher zur verfrühten Bildung von elektromagnetischen Schauern kommen kann, ist im Barrel-Bereich unmittelbar hinter dem Solenoidmagneten eine erste Detektorlage, der sogenannte presampler, angebracht. Die transversale Ausdehnung eines elektromagnetischen Schauers läßt sich durch den Molière-Radius beschreiben, der proportional zur Strahlungslänge des Detektormaterials ist. Der Molièr-Radius ist der Radius eines Zylinders um die Schauerachse, in dem 95% der Schauerenergie enthalten sind. Bei Blei liegt dieser in der Größenordnung von einigen cm.

| elektromagnetisches Kalorimeter              |                                       |                                                                                      |  |

|----------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------|--|

|                                              | $\operatorname{Barrel}$               | End-Cap                                                                              |  |

| $ \eta $ -Bereich                            | 1.4                                   | 1.4-3.2                                                                              |  |

| Tiefen Lagen                                 |                                       |                                                                                      |  |

| Presampler                                   | 1                                     | -                                                                                    |  |

| Kalorimeter                                  | 3                                     | 3                                                                                    |  |

| Granularität $\Delta \eta 	imes \Delta \phi$ |                                       |                                                                                      |  |

| Presampler                                   | $0.025 	imes 0.100 \; ( \eta  < 0.8)$ | -                                                                                    |  |

|                                              | $0.003 	imes 0.100 \; ( \eta  > 0.8)$ | -                                                                                    |  |

| Kalorimeter                                  |                                       |                                                                                      |  |

| $1.\mathrm{Lage}$                            | $0.003\times0.100$                    | $igg \ 0.003 	imes 0.100 \ ( \eta  < 2.4) \ igg $                                    |  |

| $2. { m Lage}$                               | $0.025\times0.025$                    | $\left  	ext{ } 0.025 	imes 0.025 	ext{ } (\left  \eta  ight  < 2.4) 	ext{ }  ight $ |  |

| $3.\mathrm{Lage}$                            | $0.025\times0.050$                    | $igg  \ 0.025 	imes 0.050 \ ( \eta  < 2.4) \ igg $                                   |  |

| alle Lagen:                                  |                                       | $igg \ 0.050 	imes 0.050 \ ( \eta  > 2.4) \ igg $                                    |  |

| Auslesekanäle                                |                                       |                                                                                      |  |

| Presampler                                   | 32000                                 | -                                                                                    |  |

| Kalorimeter                                  | 100000                                | 82000 (beide Seiten)                                                                 |  |

Tabelle 1.1: Gliederung und Segmentierung des elektromagnetischen Kalorimeters

#### Hadronisches Kalorimeter

Aufgabe des hadronischen Kalorimeters ist die Energiemessung von Hadronen. Es muß zusammen mit dem elektromagnetischen Kalorimeter die Identifizierung und Messung von Jetenergien ermöglichen und einen möglichst großen  $\eta$ -Bereich zur Messung der fehlenden Transversalenergie überdecken. Die Elektron- und Photonidentifizierung durch das elektromagnetische Kalorimeter soll durch Isolationsmessungen (siehe hierzu Kapitel 2.2.1) unterstützt werden. Da Jets ausgedehnte Objekte darstellen und auch die transversale Ausdehnung hadronischer Schauer im Kalorimeter größer als bei elektromagnetischen Schauern ist, genügt beim hadronischen Kalorimeter eine Segmentierung in  $0.1 \times 0.1$  Zellen in  $\Delta \eta \times \Delta \phi$  und für den Vorwärtsbereich eine Segmentierung von  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$ . Der Barrel-Bereich gliedert sich in einen zentralen Bereich,  $|\eta| < 1$ , und einen erweiterten Barrel-Bereich auf beiden Seiten,  $1 < |\eta| < 1.6$ . Wie in Abbildung 1.8 zu erkennen ist, befindet sich zwischen dem zentralen und dem erweiterten Barrel-Bereich eine Lücke, die sich auch auf den Zwischenbereich von elektromagnetischem Barrel und End-Cap-Kalorimeter ausdehnt. Diese tote Zone wird benötigt, um die Kalorimeterauslese unterzubringen und die Verkabelung der inneren Detektorkomponenten durchführen zu können. Hinter den elektromagnetischen End-Cap-Bereichen befinden sich beidseitig die hadronischen End-Cap-Kalorimeter,  $1.5 < |\eta| < 3.2$ . Um die Verfälschung der  $E_t^{miss}$ -Messung durch Teilchen, deren Flugbahn in kleinen Winkeln zur Strahlachse verlaufen, möglichst gering zu halten, befinden sich um die Strahlachse in einem Pseudorapiditätsbereich von  $3.1 < |\eta| < 4.9$  die beiden hadronischen Vorwärtskalorimeter.

Im Gegensatz zu leichten Elektronen ist der Energieverlust von Hadronen durch Bremsstrahlung beim Durchgang durch Materie sehr gering. Stattdessen können Hadronen, stoßen sie zufällig auf einen Atomkern, mit diesem stark wechselwirken. Die longitudinale Ausdehnung eines hadronischen Schauers ist daher nicht durch die Strahlungslänge  $X_0$ , sondern durch die Absorptionlänge  $\lambda_a$ , die die mittlere freie Weglänge eines Hadrons in Materie bis zur ersten Kernwechselwirkung angibt, bestimmt. Da die Absorptionslänge  $\lambda_a{}^6$  in der Regel deutlich länger als die Strahlungslänge  $X_0$  ist, haben hadronische Kalorimeter eine größere Ausdehnung als elekromagnetische. Durch die starke Wechselwirkung eines Hadrons mit einem Atomkern des Detektormaterials kommt es zur Produktion zahlreicher sekundärer Teilchen. Ein bedeutender Anteil unter diesen wird durch Pionen gebildet. Die neutralen  $\pi^0$ 's zerfallen in Photonen, die durch elektromagnetische Schauerbildung ihre Energie im Kalorimeter deponieren. Geladene Pionen verlieren ihre Energie durch Ionisation oder streuen erneut an Atomkernen. Ein Teil der Hadronenergie wird jedoch nicht vom Detektor erfaßt. Diese ungesehene Energie wird durch die Aufbrechung von Kernbindungen bei der starken Wechselwirkung der Hadronen mit den Atomkernen des Absorbermaterials verursacht [6]. Auch sekundäre Neutrinos tragen zu diesem Energieverlust bei. Der gesamte Energieverlust wird durch das  $e/\pi$ -Verhältnis ausgedrückt, welches das Verhältnis zwischen der vom Kalorimeter im Mittel detektierten Energie eines geladenen Pions und eines

<sup>&</sup>lt;sup>6</sup>Die Absorptionslänge in Eisen beträgt  $\lambda_a=16.76cm$ , die Strahlungslänge hingegen nur  $X_0=1.76cm$ . Für Blei ist:  $\lambda_a=17.1cm$  und  $X_0=0.56cm$

Elektrons mit gleicher Energie wiedergibt. Für das ATLAS-Kalorimeter wird dieser Wert auf 1.3 [8] abgeschätzt. Der Anteil der nicht detektierten Energie variiert jedoch für jede Einzelmessung stark, so daß die Energieauflösung für Messungen von Hadronenergien im hadronischen Kalorimeter vergleichsweise schlechter als die Bestimmung der Elektron- bzw. Photonenergie im elektromagnetischen Kalorimeter ist. Das Energieauflösungsvermögen des hadronischen Kalorimeters im Barrel- und End-Cap-Bereich wird abgeschätzt auf:

$$\frac{\Delta E}{E} = \frac{50\%}{\sqrt{E/GeV}} \oplus 3\% \tag{1.6}$$

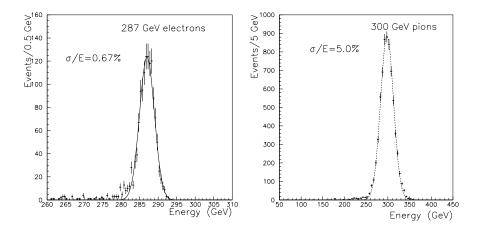

Abbildung 1.9 [5] zeigt das Energiespektrum von Messungen mit Prototypen beider Kalorimetertypen. Für das elektromagnetische Kalorimeter wurde ein monoenergetischer Elektronenstrahl mit einer Energie von 287 GeV verwendet. Die Energie der Pionen, mit denen das hadronische Kalorimeter getestet wurde, betrug 300 GeV.

Abbildung 1.9: Energiemessung mit Prototypen des elektromagnetischen (links) und hadronischen (rechts) Kalorimeters

Für den Barrel-Bereich des hadronischen Kalorimeters werden Plastikszintillatoren mit Eisenabsorberplatten verwendet. Die Tiefe beträgt zusammen mit dem vorgelagerten elektromagnetischen Barrel-Bereich ca.  $9.5\lambda_a$ . Aufgrund der erhöhten Strahlenexposition in Nähe der Strahlachsen und der feiner strukturierten Bauweise sind die hadronischen End-Cap und Vorwärtskalorimeter wie das elektromagnetische Kalorimeter in der aufwendigeren Flüssig-Argon Technik ausgeführt. Im End-Cap-Bereich wird Kupfer als Absorbermaterial verwendet, im Vorwärtsbereich eine Wolframlegierung. Die Dicke beträgt im End-Cap-Kalorimeter  $13\lambda_a$  und für das Vorwärtskalorimeter  $12\lambda_a$ .

Aufgrund der gröberen Segmentierung besitzt das hadronische Kalorimeter nur 21100 Auslesekanäle. Das fein segmentierte elektromagnetische Kalorimeter besitzt hingegen 214000 Auslesekanäle, die alle aus dem ATLAS-Detektor zur Ausleseelektronik herausgeführt werden müssen.

| hadronisches Kalorimeter                     |                             |                        |  |  |

|----------------------------------------------|-----------------------------|------------------------|--|--|

| Szintillator Kalorimeter                     |                             |                        |  |  |

|                                              | $\operatorname{Barrel}$     | erweiteter Barrel      |  |  |

| $ \eta $ -Bereich                            | 1.0                         | 1.0-1.6                |  |  |

| Tiefen Lagen                                 | 3                           | 3                      |  |  |

| Granularität $\Delta \eta 	imes \Delta \phi$ | 0.1 	imes 0.1               | 0.1 	imes 0.1          |  |  |

| Auslesekanäle                                | 6000                        | 4000 (beide Seiten)    |  |  |

|                                              | fl. Ar. End-Cap             | fl. Ar. Vorwärtskal.   |  |  |

| $ \eta $ -Bereich                            | 1.5 - 3.2                   | 3.1-4.9                |  |  |

| Tiefen Lagen                                 | 4                           | 3                      |  |  |

| Granularität $\Delta \eta 	imes \Delta \phi$ | $0.1	imes0.1\;( \eta <2.4)$ | $\sim 0.15 	imes 0.15$ |  |  |

| Auslesekanäle                                | 8600 (beide Seiten)         | 1500 (beide Seiten)    |  |  |

Tabelle 1.2: Gliederung und Segmentierung des hadronischen Kalorimeters

### 1.2.3 Myonsystem

Eine qualitativ hochwertige Messung von Myonen stellt eine der wichtigsten Anforderungen für einen LHC-Detektor dar. Da Myonen als Leptonen nicht der starken Wechselwirkung unterliegen und die zu Elektronen vergleichsweise hohe Myonenmasse<sup>7</sup> eine Energieabgabe über Bremsstrahlung im Kalorimeter stark unterdrückt, erreichen die meisten Myonen ohne wesentlichen Energieverlust die Myonenkammern, die das hadronische Kalorimeter umgeben. Das Myondetektorsystem sollte eine gute Messung der Transversalimpulse der Myonen in einem Bereich von 5 GeV bis hin zu 1000 GeV, die bei Myonen, die aus SUSY-Zerfällen stammen, auftreten können, ermöglichen.

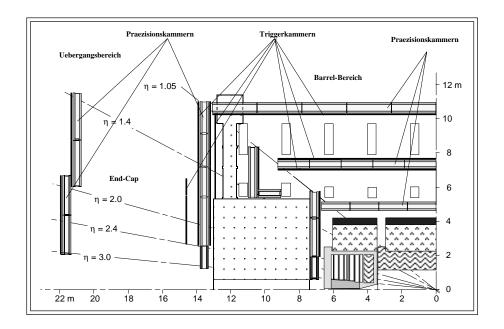

Das Myonkammersystem überdeckt einen  $\eta$ -Bereich von  $|\eta| \leq 3.0$  und ist in einen Barrel-, einen Übergangs- und einen End-Cap-Bereich zu beiden Seiten der Strahlachse gegliedert. Die Kammern befinden sich in einem toroidalen Magnetfeld. Die vom Wechselwirkungspunkt kommenden Myonen werden je nach Ladungsvorzeichen zum Strahl hin - bzw. vom Strahl weg abgelenkt. Das Myonenkammersystem besteht über den gesamten Pseudorapiditätsbereich  $|\eta| < 3.0$  aus drei Lagen hochauflösender Präzisionskammern. In einem Bereich von  $|\eta| \leq 2.2$  befinden sich schnell auszulesende Triggerkammern, die mit ihrer Zeitinformation eine Zuordnung einer Myonensignatur zu einem Bunch-Crossing liefern. Die Impulsmessung der Myonen erfolgt über den Krümmungsradius der Flugbahn im toroidalen Magnetfeld, die aus den drei Messungen der Präzisionskammern rekonstruiert wird. Die Impulsauflösung wird auf  $\frac{\Delta p_T}{p_T} \approx 0.05$  bei 100 GeV und  $\frac{\Delta p_T}{p_T} \approx 0.1$  bei 1000 GeV abgeschätzt. Die Präzisionskammern sind in Form von Driftkammern (MDTs<sup>8</sup>) und in Strahlnähe ( $|\eta| > 2.4$ ) durch strahlungsharte Katodenstreifenkammern (CSCs<sup>9</sup>) realisiert. Als Triggerkammern werden Wi-

<sup>&</sup>lt;sup>7</sup>Die Masse eines Myons beträgt  $m_{\mu}=105.66 MeV$ . Da der Energieverlust infolge von Bremsstrahlung beim Durchgang durch Materie proportinal zu  $\frac{1}{m^2}$  ist, ist der Energieverlust von Myonen im Kalorimeter sehr gering.

<sup>&</sup>lt;sup>8</sup>Monitored Drift Tube Chambers

<sup>&</sup>lt;sup>9</sup>Cathode Strip Chambers

Abbildung 1.10: Schematische Darstellung des Myonkammer Systems. Die Linien des toroidalen Magnetfeldes verlaufen senkrecht zur Zeichenebene.

derstandsplattenkammern (RPCs $^{10}$ ) im Barrel Bereich und TGCs $^{11}$  in den Übergangsund End-Cap-Bereichen verwendet.

<sup>&</sup>lt;sup>10</sup>Resistive Plate Chambers

<sup>&</sup>lt;sup>11</sup>Thin Gap Chambers

## Kapitel 2

# Der ATLAS Level-1-Kalorimetertrigger

## 2.1 Trigger- und Auslesesystem des ATLAS-Detektors

Die vollständige Datenauslese des ATLAS-Detektors kann bei einer Bunch-Crossing-Rate von 40 MHz nicht bei jedem Bunch-Crossing durchgeführt werden. Dies würde zu einer hoffnungslosen Überlastung der Ausleseelektronik und Speichermedien führen. Aufgabe eines Triggersystems ist es, die Detektorauslese zu steuern, indem nur Daten derjenigen Bunch-Crossings ausgelesen werden, die interessante physikalische Signaturen (siehe Kapitel 1.1.4) enthalten.

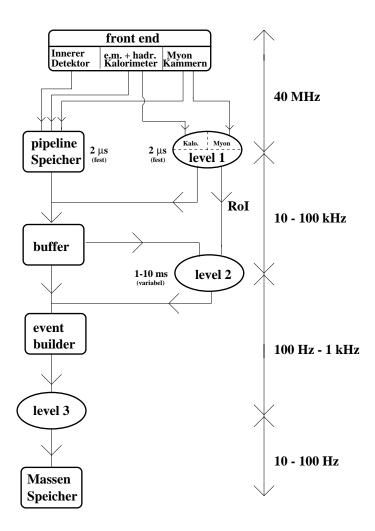

Das Triggersystem des ATLAS-Detektors ist in drei Stufen aufgebaut. Mustererkennungsalgorithmen überprüfen die Daten nach physikalischen Gehalt, wobei die Komplexität der Algorithmen von Stufe zu Stufe zunimmt, was durch die zur Verfügung stehende Entscheidungszeit, die mit jeder Stufe anwächst, ermöglicht wird. Wird ein Ereignis von einer Triggerstufe akzeptiert, so werden die zugehörigen Daten zur nächsten Stufe weitergereicht und eine detailliertere Ereignisrekonstruktion durchgeführt. Wird ein Ereignis von allen drei Triggerstufen akzeptiert, wird es für die spätere off-line-Analyse abgespeichert. Auf diese Weise läßt sich die Rate der akzeptierten Ereignisse von Stufe zu Stufe sukzessive erniedrigen (siehe Figure 2.1).

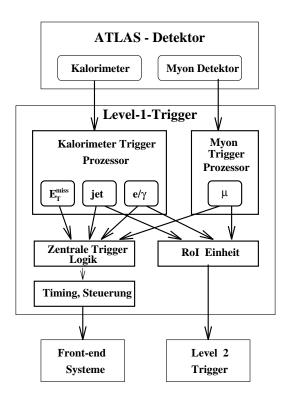

### 2.1.1 Level-1-Trigger

Nach jedem Bunch-Crossing werden Daten vom Detektor zum Level-1-Trigger, der ersten der drei Triggerstufen, geleitet, der mittels einfacher Selektionskriterien die Ereignisrate von der 40 MHz Bunch-Crossing-Rate auf 100 kHz erniedrigen soll. Wie in Kapitel 1.1.3 beschrieben, finden pro Bunch-Crossing durchschnittlich 25 Proton-Proton-Streuungen mit kleinem Impulsübertrag statt. Dies entspricht einer Anzahl von 10<sup>9</sup> Ereignissen pro Sekunde. Die erste Triggerstufe muß deshalb die Ereignisrate um den Faktor 10<sup>4</sup> bis 10<sup>5</sup> auf eine Rate von 100 kHz reduzieren, die durch die Ein-

gangsrate des Level-2-Triggers vorgegeben ist. Um die hohe Datenrate bewältigen zu können, verwendet der Level-1-Trigger Daten aus dem Kalorimeter und den Myonkammern mit reduzierter Granularität. Die Energien, die in einem Bereich von  $0.1 \times 0.1$  in  $\Delta \eta \times \Delta \phi$  im Kalorimeter deponiert sind, werden zu sogenannten Triggertowern zusammengefaßt und summiert. Die Triggerentscheidungen beruhen hierbei auf Schwellen, die auf die Transversalenergie von Jets, isolierten elektromagnetischen Schauern im elektromagnetischen Kalorimetern, Myonen sowie auf den fehlendem Transversalimpuls in der globalen Vektorsumme gesetzt werden. Informationen über Teilchenspuren aus dem Inneren Detektor werden für den Level-1-Trigger nicht herangezogen.

Abbildung 2.1: Schema des dreistufigen Aufbaus des ATLAS-Triggersystems. Am rechten Bildrand ist die Ereignisrate zwischen den einzelnen Triggerstufen aufgeführt.

Die kurze Zeit, die für eine Level-1-Triggerentscheidung zur Verfügung steht, erfordert es, daß die Triggeralgorithmen auf dieser Triggerstufe als elektronische Schaltungen implementiert sind. Die Daten aus den Kalorimetern und den Myonkammern

werden in unterschiedlichen detektorspezifischen Prozessoren verarbeitet. Die dort gewonnenen Informationen werden an eine zentrale Level-1-Triggereinheit weitergegeben, die daraus eine Triggerentscheidung fällt. Die Latenzzeit, die benötigt wird, um die Daten aus den Detektoren auszulesen, zum Level-1-Trigger zu senden und dort zu verarbeiten, beträgt  $2\mu s$ . Während dieser Zeit werden die kompletten Daten aller Subdetektoren ausgelesen und in Pipeline Speichern zwischengespeichert. Die Latenzzeit von  $2\mu s$  erfordert es, daß Daten aus 80 aufeinanderfolgenden Bunch-Crossings in Pipeline-Speichern gespeichert werden, was die Länge der Pipeline-Speicher festlegt<sup>1</sup>. Hat der Level-1-Trigger ein Bunch-Crossing akzepiert, so werden die Daten aus den Pipeline-Speichern ausgelesen und in einem Level-2-Buffer abgelegt. Eine zweite Aufgabe der ersten Triggerstufe besteht darin, sogenannte Regions-Of-Interest (ROIs) zu bestimmen und an den Level-2-Trigger weiterzugeben. Es handelt sich hierbei um die Ortsangabe der Detektorbereiche, die interessante Signaturen enthalten.

### 2.1.2 Level-2-Trigger

Hat ein Bunch-Crossing die erste Triggerstufe erfolgreich passiert, werden die Daten aus den Level-2-Buffern, die zu den vom Level-1-Trigger identifizierten ROIs gehören, ausgelesen und an die zweite Triggerstufe übergegeben. Nur diese Daten werden für die Level-2-Triggerentscheidung herangezogen. Dies erlaubt die Verwendung von verfeinerten Mustererkennungsalgorithmen, die mit Daten mit maximaler Granularität arbeiten. Es werden jetzt auch Spurinformationen aus dem Inneren Detektor verwendet. Die Level-2-Triggeralgorithmen sind als Programme auf parallel arbeitenden Prozessoren implementiert. Da die Triggerentscheidungen auf lokalen Kriterien, die aus den ROIs gewonnen werden, basiert, können nicht nur Ereignisse, die zu unterschiedlichen Bunch-Crossings gehören, sondern auch ROIs eines Ereignisses auf verschiedenen Mikroprozessoren des Level-2-Triggers parallel verarbeitet werden. Die Entscheidungszeit, die der Prozessor-Cluster benötigt, variiert je nach Komplexität der Signaturen zwischen 1 und 10 ms. Insgesamt muß die zweite Triggerstufe eine Reduzierung der Ereignisrate um den Faktor 100 auf ca. 1 kHz erreichen.

### 2.1.3 Level-3-Trigger

Ist ein Ereignis auch von der zweiten Triggerstufe akzeptiert, wird der komplette Datensatz, der zu dem betreffenden Bunch-Crossing gehört, aus den Level-2-Buffern an den Event-Builder des Level-3-Triggers weitergegeben. Dieses Schalt-Interface ermöglicht es, die Daten von beliebigen Subdetektoren zu allen Prozessoren der Level-3-Prozessor-Farm zu leiten. Dort geschieht eine vollständige Rekonstruktion des Ereignisses. Die Selektion erfolgt nach Kriterien ähnlich den Algorithmen der off-line-Analyse, die auf relevanten physikalischen Größen wie beispielsweise Jetenergien, Teilchen-4er-Impulse und invarianten Massen beruhen. Die Datenreduzierung kann auf dieser Triggerstufe

<sup>&</sup>lt;sup>1</sup>Die Pipeline-Speicher bieten Platz zur Speicherung der Daten von 100 aufeinanderfolgender Bunch-Crossings. Der Überlapp von 20 Bunch-Crossings bietet Sicherheit bei Änderungen der Level-1-Latenzzeit.

auf zwei Weisen erfolgen. Zum einen wird wie in den vorhergehenden Triggerstufen anhand der neu gewonnenen Information die Rate der akzeptierten Ereignisse erneut reduziert, zum anderen kann der Datenumfang eines akzeptierten Ereignisses verringert werden, da nicht immer die Auslese des vollständigen Datensatzes von ca. 1 MByte Umfang von Interesse ist. Eine Speicherrate auf Magnetband zur späteren off-line-Analyse von 10 bis 100 Mbyte/s wird als durchführbar angesehen, womit die Ereignisrate, die auch die dritte Triggerstufe erfolgreich durchlaufen darf, entsprechend auf maximal 100 Hz begrenzt ist. Die Latenzzeit darf auf dieser Stufe bis zu einer Sekunde betragen. Dies ist möglich, weil wie auf der zweiten Triggerstufe Ereignisse verschiedener Bunch-Crossings parallel verarbeitet werden können.

Die Algorithmen der zweiten und dritten Triggerstufe sind zu jeder Zeit der Entwicklung des ATLAS Triggers und Detektors sowie während des späteren LHC-Betriebes modifizierbar.

## 2.2 Level-1-Triggeralgorithmen

Die erste Triggerstufe muß eine Reduzierung des Untergrundes um einen Faktor  $10^4 - 10^5$  bewirken. Um dies zu erreichen, wird nach Teilchen mit hohem Transversalimpuls gesucht. Zu diesen gehören einzelne Leptonen und Photonen, die einen Schauer im elektromagnetischen Kalorimeter erzeugen, Teilchenjets und neutrale Teilchen, die keine Energie im Kalorimeter hinterlassen und so zu einem fehlenden Anteil in der globalen Vektorsumme des Transversalimpulses führen (siehe Kapitel 1.1.2). In Tabelle 2.1 sind einige Beispiele für interessante Ereignisse mit ihren Selektionskriterien im Level-1-Trigger aufgelistet.

| Prozeß                                                  | Signatur im Level 1 Trigger                        |

|---------------------------------------------------------|----------------------------------------------------|

| $H^0 \longrightarrow \gamma \gamma$                     | $1\gamma, E_T > 40 GeV$                            |

|                                                         | $2\gamma, E_T > 20 GeV$                            |

| $H^0 \longrightarrow ZZ^* \longrightarrow l^+l^-l^+l^-$ | $2e, E_T > 20 GeV$                                 |

| oder                                                    | $2\mu, E_T > 6 GeV$                                |

| $H^0 \longrightarrow ZZ \longrightarrow l^+l^-l^+l^-$   | $1e, E_T > 30 GeV$                                 |

|                                                         | $1\mu, E_T > 20 GeV$                               |

| $W', Z' \longrightarrow jets$                           | $1jet, E_T > 150 GeV$                              |

| QCD Studien, Multijets                                  | $3jets, E_T > 150 GeV$                             |

| $SUSY \longrightarrow jets$                             | $\mid 3jets, E_T > 150 GeV + E_T^{miss} > 200 GeV$ |

Tabelle 2.1: Beispiele für interessante erwartete Ereignisse mit den zugehörigen für den Level-1-Trigger relevanten Signaturen

Myonimpulse werden mit dem Myonkammersystem gemessen. Die Spurrekonstruktionen beruhen dort auf Koinzidenzen verschiedener Myontriggerkammern, woraus die Impulse der Myonen abgeschätzt werden können. Die Informationen werden zu einer separaten Myontriggerelektronik geleitet. Die Suche nach Elektronen, Photonen und

Jets sowie die Summierung der Transversalenergien für die  $E_t^{miss}$ -Berechnung wird von dem Level-1-Kalorimetertrigger übernommen. Sowohl im Myontrigger als auch im Kalorimetertrigger werden die Energien der jeweiligen physikalischen Objekte mit Schwellen verglichen und auf diese Weise Energieklassen zugeteilt. Diese kompakte Klasseninformation wird an eine zentrale Level-1-Triggerlogik weitergegeben, die die Triggerentscheidung fällt.

Abbildung 2.2: Blockschaltbild des Level-1-Triggers

Wie in Tabelle 2.1 zu erkennen ist, sind die Energieschwellen, die isolierte Elektronen oder Photonen erfüllen müssen, deutlich niedriger als die Schwellen für Jets. Ein Triggeralgorithmus muß daher einzelne Photonen und Elektronen von Jets trennen können. Außerdem sollte ein Triggeralgorithmus in der Lage sein, die Multiplizitäten der physikalischen Objekte zu bestimmen, da bei höheren Multiplizitäten (> 1) niedrigere Energieschwellen sinnvoll sind.

### 2.2.1 $e^{\pm}/\gamma$ -Algorithmus

Elektronen und Photonen dringen, wie in Kapitel 1.2.2 erklärt wurde, nicht allzu tief in das Kalorimeter ein und deponieren daher ihre Energie vollständig im elektromagnetischen Kalorimeter, indem sie elektromagnetische Schauer auslösen. Die Elektronen und Photonen, die bei den interessierenden Zerfällen schwerer Teilchen entstehen, treten isoliert auf. Sie sind von den Elektronen und Photonen, die in Teilchenjets enthalten sind

oder von Photonen, die aus dem Zerfall neutraler Pionen stammen, zu unterscheiden. Ebenso müssen sie auch von isolierten Hadronen, die ebenfalls beim Durchgang durch das elektromagnetische Kalorimeter einen Teil ihrer Energie abgeben, getrennt werden. Die transversale Ausdehnung eines elektromagnetischen Schauers ist deutlich kleiner als die Ausdehnung eines hadronischen Schauers und ebenfalls kleiner als der relativ große Öffnungswinkel eines Teilchenjets. Wenn nun gefordert wird, daß die Energie, die im elektromagnetischen Kalorimeter gemessen wird, auf eng begrenzte Bereiche in  $\eta \times \phi$  beschränkt ist, außerhalb derer die Energiedeposition gering ist, können elektromagnetische Schauer, die durch isolierte Elektronen bzw. Photonen ausgelöst worden sind, von den Schauern getrennt werden, die durch zu Jets gehörende Teilchen oder Photonen, die aus Pionzerfällen stammen, ausgelöst wurden. Elektronen und Photonen werden in der Regel bereits im elektromagnetischen Kalorimeter vollständig absorbiert, während Hadronen meist den Hauptanteil ihrer Energie erst im hadronischen Kalorimeter abgeben. Ein weiteres Unterscheidungsmerkmal für isolierte Elektronen und Photonen ist deshalb, daß im Bereich des hadronischen Kalorimeters, der sich hinter den Zellen des elektromagnetischen Kalorimeters befindet, in denen eine Energiedeposition gemessen wurde, nur sehr wenig Energie deponiert ist. Der Algorithmus besteht also aus der gleichzeitigen Erfüllung folgender Bedingungen:

- 1. Die Energiedeposition in einem eng begrenzten Bereich des elektromagnetischen Kalorimeters muß eine Triggerschwelle übersteigen.

- 2. Die Energie, die in einem Bereich des elektromagnetischen Kalorimeters um dieses Zentrum herum gemessen wird, muß unterhalb eines Energiewertes liegen. (1. Isolationskriterium)

- 3. Die Energiesumme, die in dem entsprechenden Bereich des hadronischen Kalorimeters deponiert ist, muß ebenfalls sehr gering sein. (2. Isolationskriterium)

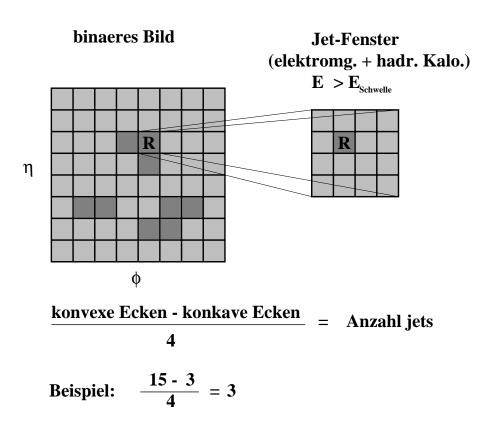

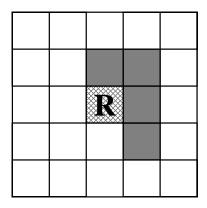

### 2.2.2 Jetalgorithmus

Jets stellen aufgrund des hohen Wirkungsquerschnittes der starken Wechselwirkung den dominierenden Prozeß dar. Der Jettrigger ist daher untergrundfrei. Wichtigste Aufgabe eines Jettriggers ist es, eine möglichst genaue Abschätzung der gesamten Jetenergie zu ermitteln. Hierzu werden die Energien in Bereichen des elektromagnetischen und hadronischen Kalorimeters zunächst für beide Kalorimetertypen getrennt aufsummiert und anschließend beide Werte addiert. Bei der letzten Addition müssen beide Beiträge entsprechend dem  $e/\pi$ -Verhältnis gewichtet werden. Die Energiesumme, die man hieraus erhält, muß eine Triggerschwelle übersteigen. Die Güte eines Jettriggers, d.h. die Effizienz, Jets, die über der Schwelle liegen, zu akzeptieren und Jets mit geringerer Energie zu unterdrücken, ist nun durch die Genauigkeit bestimmt, mit der die Jetenergie abgeschätzt werden kann. In der  $(\eta, phi)$ -Ebene besitzt ein Jet eine annähernd runde Querschnittsfläche. Der entscheidende Parameter, der in die Energieabschätzung eingeht, ist die Größe des Fensters, in dem die Energien summiert werden. Ein zu kleiner Bereich würde zu einer Unterschätzung der Jetenergie führen,

während bei einem zu groß gewählten Fenster zu viel Untergrund fälschlicherweise mit zur Jetenergie gezählt würde.

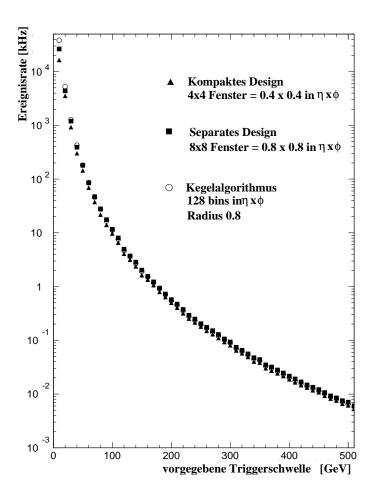

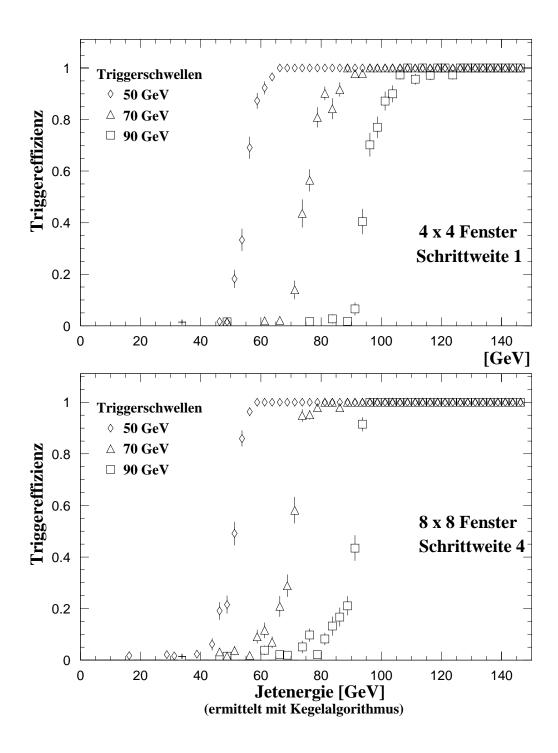

Ein weiterer Faktor, der die Effizienz des Jettriggers mitbestimmt, ist der Überlappungsgrad benachbarter Bereiche. Ist dieser zu gering oder überschneiden sich die Fenster überhaupt nicht, so kann es dazu kommen, daß ein Jet, dessen Energie eigentlich über der Triggerschwelle liegt, auf zwei oder mehr Bereiche aufgeteilt wird, deren Energiesummen sich alle unterhalb der Schwelle befinden und daher das Ereignis abgewiesen wird. Auf der anderen Seite reduziert eine große Überschneidung der Fenster die Geschwindigkeit des Algorithmus, weil die Anzahl der Summenbildungen steigt und auch die Bestimmung der Jetmultiplizität erschwert wird. Ein Problem nämlich, das durch den Überlapp der Summationsbereiche auftaucht, ist die Mehrfachzählung eines einzelnen Jets, der in mehreren sich überlappenden Fenstern genügend Energie deponiert hat. Die Bestimmung der ROI-Koordinaten ist in diesem Fall ebenfalls nicht mehr eindeutig. Eine Beschreibung der Declustering-Algorithmen, die diese Probleme beheben, befindet sich in den Kapiteln 2.4.2 und 2.4.3. Da die Jetrate stark mit abnehmendem Transversalimpuls zunimmt, ist die richtige Wahl der Triggerschwelle von großer Bedeutung. Eine zu kleine Schwelle kann zu unakzeptierbar hohen Triggerraten führen. Um eine optimale Wahl dieser Parameter zu finden, sind Simulationsstudien durchgeführt worden. Eine Bescheibung dieser Untersuchungen findet sich in Kapitel 2.4.4.

## 2.2.3 $E_t^{miss}$ -Algorithmus

Zur  $E_t^{miss}$ -Bestimmung müssen alle Transversalenergien, die aus den Energiedepositionen in den Kalorimeterzellen berechnet werden, durch Multiplikation mit dem Sinus bzw. Cosinus des Azimutwinkels  $\phi$  in eine  $E_x$  und eine  $E_y$  Komponente aufgespalten werden. Diese Werte werden getrennt summiert und die beiden Summen quadratisch addiert.

Zu den Faktoren, die die Effizienz des  $E_t^{miss}$ -Triggers beeinflussen, zählt in erster Linie der Pseudorapiditätsbereich, der zur Summation hinzugezogen wird. Jets, die in kleinen Winkeln zur Strahlrichtung liegen und daher nicht mehr in die  $E_t$ -Summation mit einbezogen werden, erzeugen einen falschen  $E_t^{miss}$ -Beitrag. Aus diesem Grund ist es von Vorteil, einen möglichst großen Pseudorapiditätsbereich zu überdecken. Weiterhin ist die Behandlung der Rapiditätslücken innerhalb des ATLAS-Kalorimeters infolge passiven Detektormaterials von Bedeutung. Auch die Granularität in  $\phi$  der Segmente, die zur Aufspaltung der Transversalenergie in  $E_x$  und  $E_y$  benutzt werden, nimmt Einfluß auf die Effizienz des  $E_t^{miss}$ -Triggers. Eine zu grobe Granularität führt zu Energieverschiebungen, die die Aufsummierung verfälschen können. Auf der anderen Seite steigt mit kleiner werdender Segmentierung die Aufwendigkeit der Berechnungen. Ein weiterer Untergrund für den  $E_t^{miss}$ -Trigger wird durch kosmische Teilchen und Wechselwirkungen von Strahlteilchen mit Restgasatomen innerhalb der Strahlröhre hervor-

<sup>&</sup>lt;sup>2</sup>Die Sinus- und Cosinus-Bildung erfolgt in den Triggerprozessoren über Look-Up-Tables (LUT), die viel Platz auf dem Chip erfordern. Je kleiner die Segmentierung gewählt ist, desto länger werden diese LUTs.

gerufen. Aus diesen Gründen wird der  $E_t^{miss}$ -Trigger in der Regel in Kombination mit anderen Triggern verwendet. Für eine exklusive Triggerung auf  $E_t^{miss}$  muß die Triggerschwelle genügend hoch gesetzt werden, damit der Untergrund weitgehend unterdrückt wird.

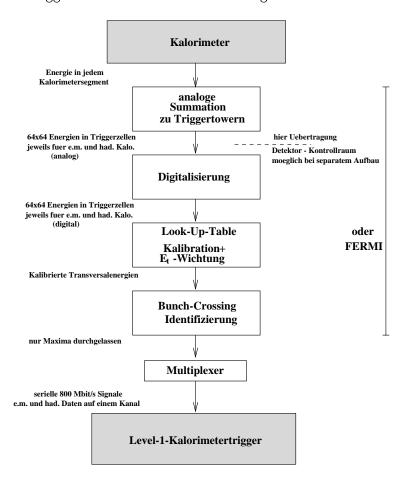

## 2.3 Aufbereitung der Kalorimeterdaten für den Level-1-Kalorimetertrigger

Um die technische Realisierung des Level-1-Triggers zu verstehen, ist es nützlich, sich etwas mit dem Datenformat und der Aufbereitung der Kalorimeterrohdaten für die Level-1-Eingangsdaten zu befassen. Wie schon im ersten Abschnitt dieses Kapitels gesagt, werden die Energiedepositionen innerhalb der Segmente, die in einer Umgebung von  $0.1\times0.1$  in  $\Delta\eta\times\Delta\phi$  liegen, zu Triggertowern addiert. Es wird ein Pseudorapiditätsbereich von  $|\eta|<3.2$  verwendet, womit das gesamte elektromagnetische und das hadronische Kalorimeter bis auf die Vorwärtskalorimeter einbezogen sind<sup>3</sup>. Es ist vorgesehen, die Signale analog für beide Kalorimetertypen getrennt zu summieren.

Erst nach der Summation werden die Signale digitalisiert, wobei noch offen ist, ob die Digitalisierung direkt am Detektor oder im Trigger-Kontrollraum realisiert werden soll. Ein Ansatz sieht beispielsweise vor, die analogen Signale optisch über die ca. 80 m zum Kontrollraum zu übertragen, wo sie wieder in elektrische Signale konvertiert und anschließend digitalisiert werden [9]. Auch der dynamische Bereich der Digitalisierung ist zur Zeit noch in Diskussion. Zur Zeit erscheint ein dynamischer Bereich von 8 Bit technisch realisierbar. Die digitalisierten Signale werden zu Look-Up-Tables (LUTs) geleitet, in denen die Kalibration und die Wichtung von der totalen Energie zur Transversalenergie durchgeführt wird. Man erhält so einen 8-Bit breiten Wert für die Transversalenergie, wobei das LSB<sup>4</sup> einer Energie von 1 GeV entspricht. Ein Nachteil hierbei ist, daß hohe Energiewerte von über 255 GeV bei dieser Energie abgeschnitten werden. Eine z.Z. diskutierte Möglichkeit, um den dynamischen Bereich über diese 255 GeV hinaus zu erweitern, ohne höher auflösende ADCs verwenden zu müssen, besteht darin, eine Verstärkung der analogen Signale mit logarithmischer oder quadratischer Verstärkungskennlinie zu verwenden. Im niedrigen Energiebereich bleibt die hohe Auflösung erhalten. Bei der Kalibration in den Look-Up-Tables werden in diesem Fall die digitalisierten Daten wieder liniarisiert.

Nach der Digitalisierung werden die Daten dem zugehörigen Bunch-Crossing zugeordnet. Die analogen Signalpulse erstrecken sich über einen Zeitraum von bis zu 25 Bunch-Crossings. Hohe Pulse können wegen ihrer langsamen Signalabfallszeit daher Sig/-nale nachfolgender Bunch-Crossings überlagern. In einem BCID<sup>5</sup>-Algorithmus wird für jeden Kanal der Energiewert, der das Maximum des Kalorimeterpulses enthält, herausgesucht und zum Trigger weitergegeben, während die anderen Werte unterdrückt

<sup>&</sup>lt;sup>3</sup>Für den  $E_t^{miss}$ -Algorithmus werden eventuell auch Daten aus den hadronischen Vorwärtskalorimetern hinzugezogen, um den Pseudorapiditätsbereich auf  $|\eta| < 4$  oder 5 auszudehnen.

<sup>&</sup>lt;sup>4</sup>Least Significant Bit

<sup>&</sup>lt;sup>5</sup>Bunch Crossing Identification

werden. Ohne BCID würde ein einziger zu einem Bunch-Crossing gehörender Signalpuls den Level-1-Trigger für mehrere aufeinanderfolgende Bunch-Crossings erreichen.

Abbildung 2.3: Übertragungskette der Signale vom Kalorimeter zum Level-1-Trigger

Bevor die Transversalenergiedaten den Level-1-Trigger erreichen, werden alle Werte unter 1 GeV auf null gesetzt, um den physikalischen Untergrund und das elektronische Rauschen auf der Transversalenergie, das im zentralen Bereich ( $|\eta|=0$ ) ungefähr 300-400 MeV pro Triggerzelle beträgt [8] und zu einer Störung der Isolationsmessungen der Triggeralgorithmen führt, zu unterdrücken. Für die technische Ausführung der beschriebenen Prozesse existieren zwei Konzepte. Eine Lösung sieht vor, die verschiedenen Schritte diskret auf separate Einheiten (FADCs, BCID-ASICs, LUTs ...) zu verteilen, während in der anderen Realisierungmöglichkeit die Datenaufbereitung vollständig auf einem Multi-Chip-Module integriert wird (FERMI, [10]).

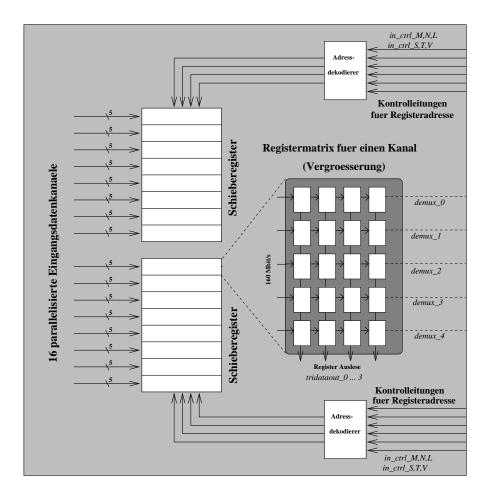

Die Triggeralgorithmen erhalten also jeweils eine 64 × 64 Matrix mit 8-Bit breiten Transversalenergiewerten für beide Kalorimetertypen als Eingangsdaten. Um die Anzahl der Kabel zu reduzieren, werden die Daten serialisiert und für beide Kalorimetertypen auf einen Kanal multiplext. Mit den vier Kontrollbits des Übertragungsprotokolls erhält man so eine Anzahl von 20 Bits pro Bunch-Crossing für jeden Eingangskanal. Die Datenrate pro seriellem Übertragungskanal beträgt somit 800 Mbit/s.

### 2.4 Der Level-1-Kalorimetertriggerprozessor

Zur Umsetzung der Level-1-Kalorimetertriggeralgorithmen gibt es zwei konkurrierende Ansätze. Bei dem im Technischen Proposal [5] vorgestellten Ansatz (kurz: TP-Design) [8] sind die verschiedenen Algorithmen in getrennten Modulen implementiert, wobei die Aufgaben aufgeteilt werden auf Jetmodule, elektromagnetische Cluster-Module,  $E_t^{miss}$ -Module, Decluster-Module für Jet bzw.  $e/\gamma$ -Algorithmus. Das zweite Projekt sieht vor, sämtliche Algorithmen auf einem Prozessor-ASIC zu vereinen. Ein ASIC verarbeitet die Daten, die zu einem  $4\times 8$  Triggerzellenbereich innerhalb der  $64\times 64$ -Matrix gehören. Zur Realisierung der Isolationskriterien und Decluster-Algorithmen benötigt jeder ASIC Informationen aus zwei weiteren Randspalten und Randzeilen, also insgesamt Daten aus einer  $8\times 12$ -Matrix. Da sich diese Diplomarbeit in erster Linie mit Komponenten dieses zweiten kompakten Designs beschäftigt, wird das TP-Design nicht näher beschrieben. Für die Jettriggeralgorithmen, die sich zwischen den beiden Ansätzen unterscheiden, sind Simulationstudien durchgeführt worden. Aus diesem Grund findet sich in Kapitel 2.4.2 neben der Beschreibung des Jettriggers im kompakten Design auch eine Darstellung des konkurrierenden Projekts.

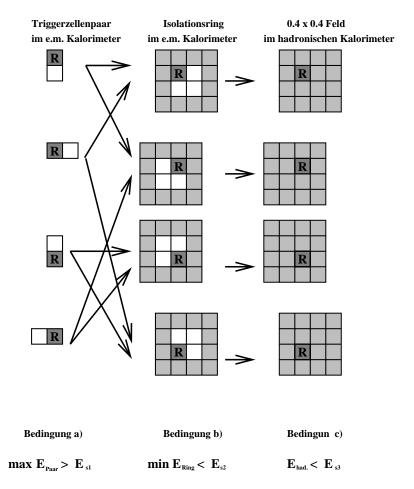

### 2.4.1 Implementation des $e/\gamma$ -Algorithmus

Die Implementation des  $e/\gamma$ -Algorithmus im Kompakten Design ist in Abbildung 2.4 dargestellt. Die drei in Kapitel 2.2.1 aufgeführten Bedingungen zur Erkennung isolierter Schauer im elektromagnetischen Kalorimeter sind hier ausgedrückt durch:

- 1. Die Energiesumme innerhalb eines Triggerzellenpaares dient als Abschätzung der ursprünglichen Elektron- bzw. Photonenergie, womit berücksichtigt wird, daß ein Elektron bzw. Photon den Detektor im Übergangsbereich zwischen zwei Triggertowern treffen kann und seine Energie daher auf zwei benachbarte Zellen aufteilt. Diese Energiesumme muß eine Triggerschwelle übersteigen.

- 2. Erstes Isolationskriterium: Die Summe in einem 4 × 4 Triggerzellenring des elektromagnetischen Kalorimeters, der das Zellenpaar umschließt, muß unterhalb einer Schwelle liegen.

- 3. Zweites Isolationskriterium: Die Gesamtenergie in der 4 × 4 Triggerzellenmatrix des hadronischen Kalorimeters, die hinter dem Isolationring der zweiten Bedingung liegt, darf ebenfalls einen Schwellenwert nicht übersteigen.

Zu jeder Triggerzelle werden die vier Paare mit den benachbarten Zellen gebildet und die Energiesumme dieser Zellenpaare (Abbildung 2.4 a) berechnet. Der maximale Wert dieser vier Summen dient als Abschätzung der Elektron- bzw. Photonenergie. Dieser wird mit sieben programmierbaren Energieschwellen verglichen und entsprechend klassifiziert, was einen 3-Bit-Kode ergibt. Als erstes Isolationskriterium innerhalb des elektromagnetischen Kalorimeters werden die Energien in 4 × 4-Triggerzellenringen aufsummiert. Einem maximalen Zellenpaar können, wie in Bild

2.4 durch Pfeile angedeutet ist, zwei solcher Ringe zugeordnet werden. Der Ring, der die geringere Summe besitzt, wird als Isolationsring verwendet. Die dort deponierte Energie wird mit drei Schwellen (2-Bit-Kode) verglichen und auf diese Weise in vier Energieklassen eingeteilt. Als dritte Bedingung (2. Isolationskriterium) wird die Energiesumme in der  $4 \times 4$ -Triggerzellenmatrix des hadronischen Kalorimeters, die sich genau hinter dem verwendeten Isolationsring befindet, gebildet und ebenfalls in vier Energieklassen eingeteilt (2-Bit-Kode). Zur Vermeidung einer Mehrfachzählung eines einzelnen elektromagnetischen Schauers, dadurch daß das gleiche Zellenpaar zwei verschiedenen Triggerzellen zugeordnet wird oder sich der elektromagnetische Schauer auf mehrere Zellen verteilt, wird eine zusätzliche Bedingung eingeführt. Die Triggerzelle, die einen elektromagnetischen Schauer enthält, muß einen Maximalenenergiewert innerhalb einer  $3 \times 3$ -Triggerzellenumgebung annehmen. Hierdurch wird eine Mehrfachzählung vermieden und eine eindeutige Angabe der ROI-Koordinaten gewährleistet.

Abbildung 2.4: Darstellung der für den Elektron/Photon Triggeralgorithmus relevanten Energiesummen. Die Energie in einem Zellenpaar muß eine Schwelle überschreiten. Die Energiesummen in dem Isolationsring bzw. im entsprechenden Bereich des hadronischen Kalorimeters muß jeweils unterhalb gesetzter Grenzwerte liegen.

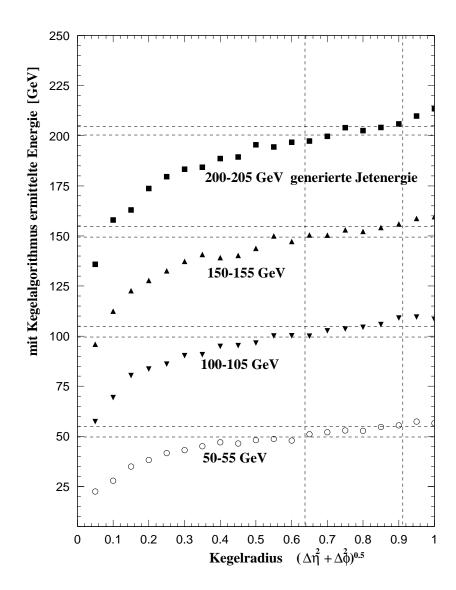

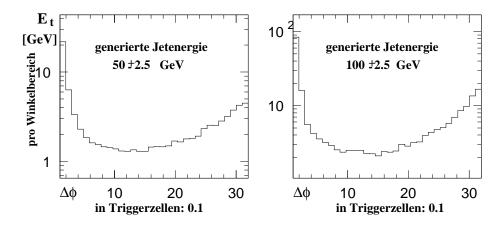

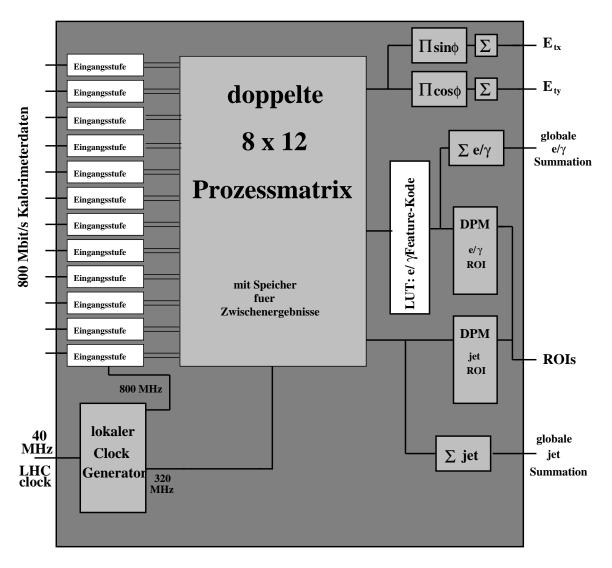

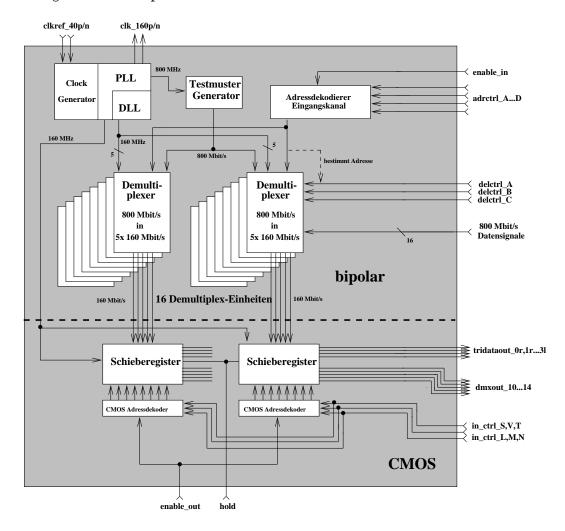

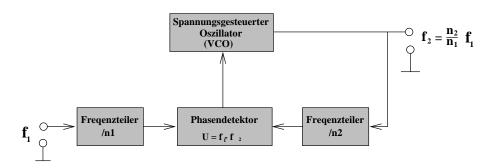

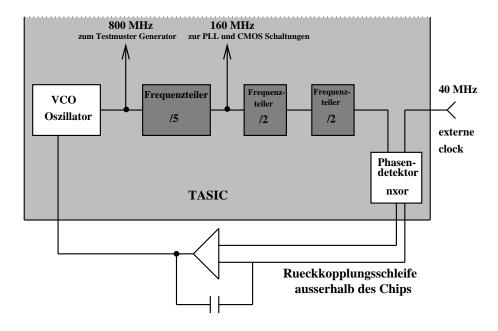

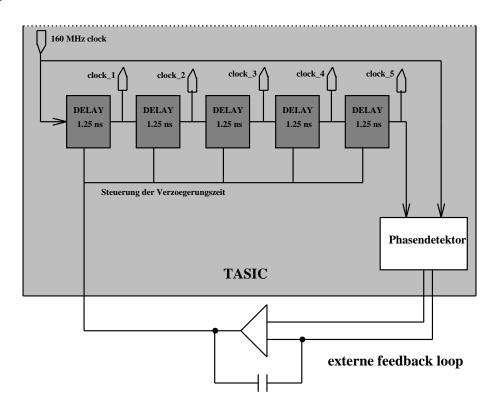

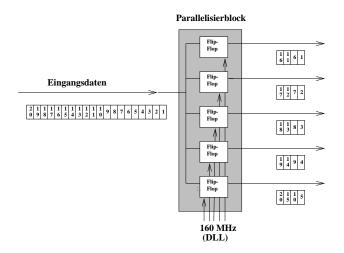

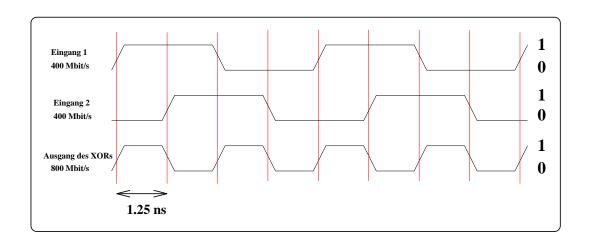

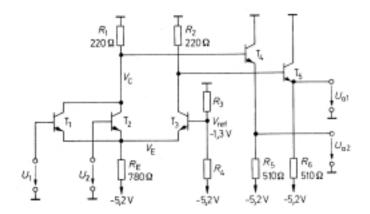

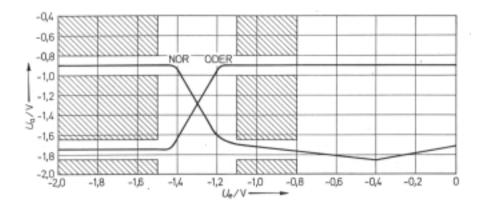

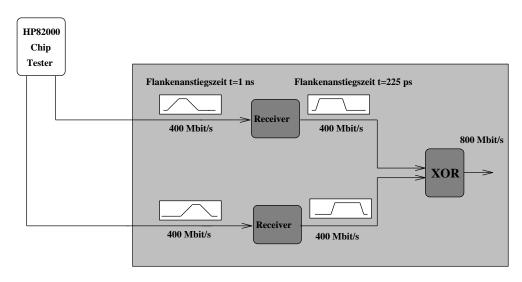

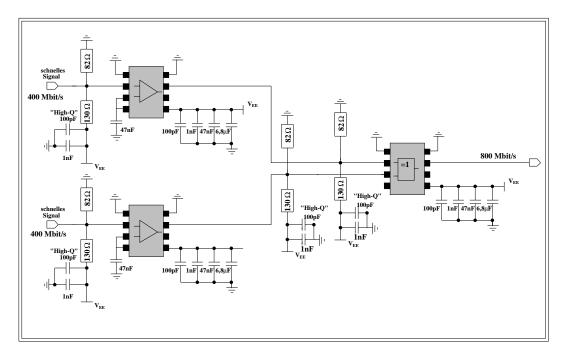

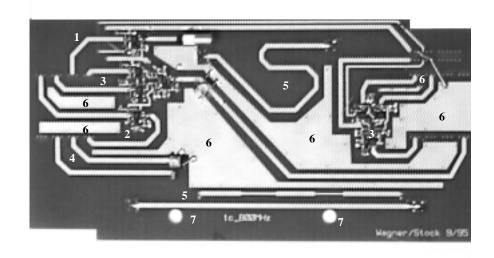

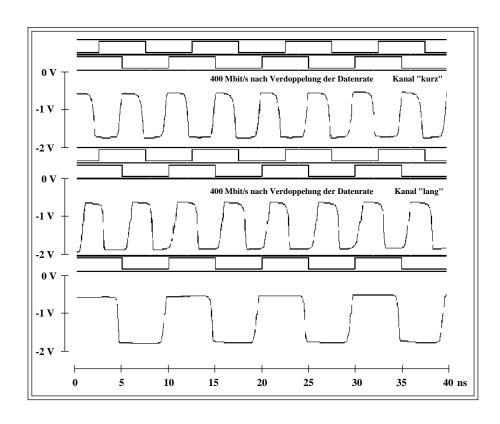

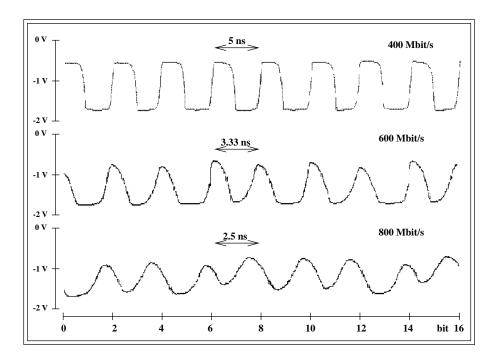

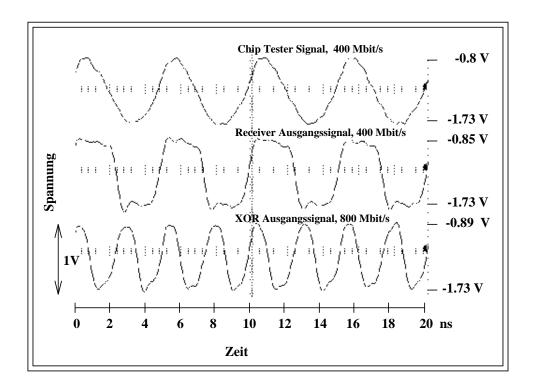

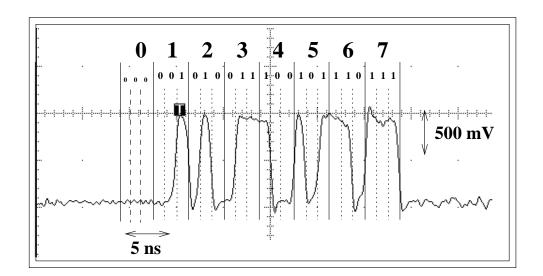

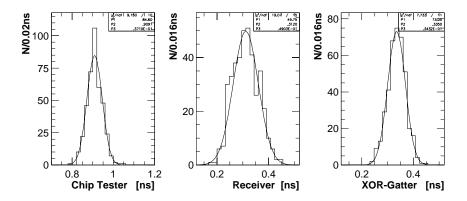

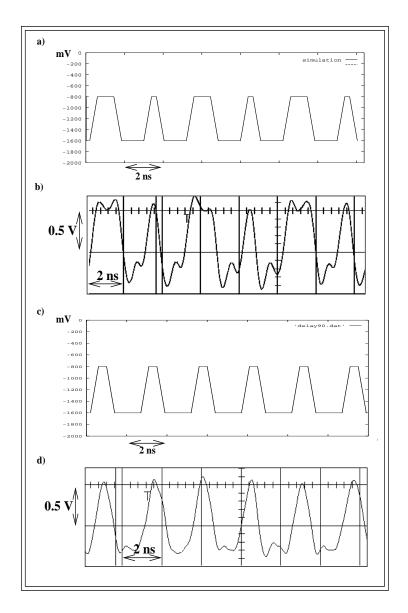

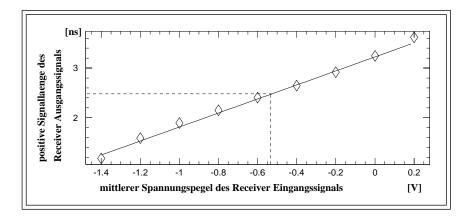

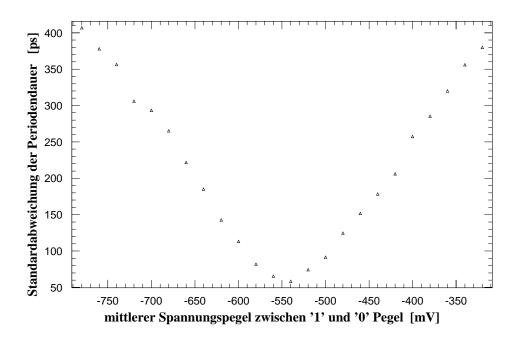

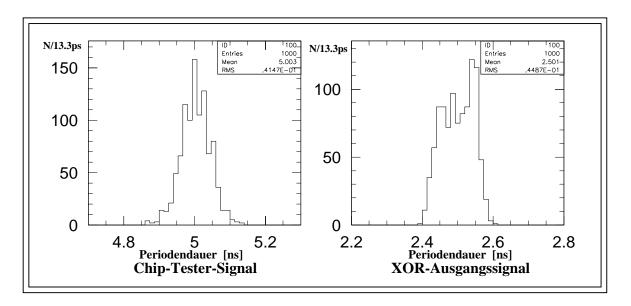

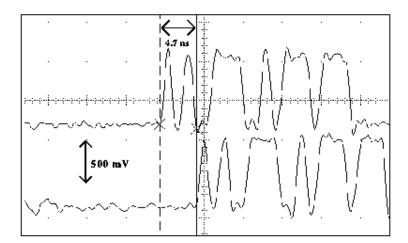

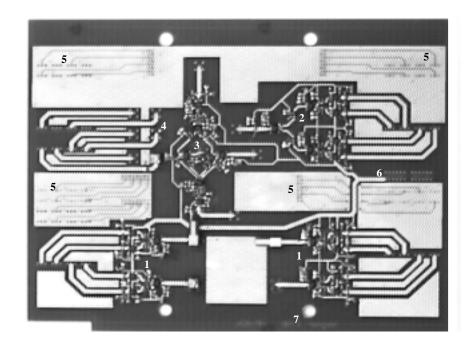

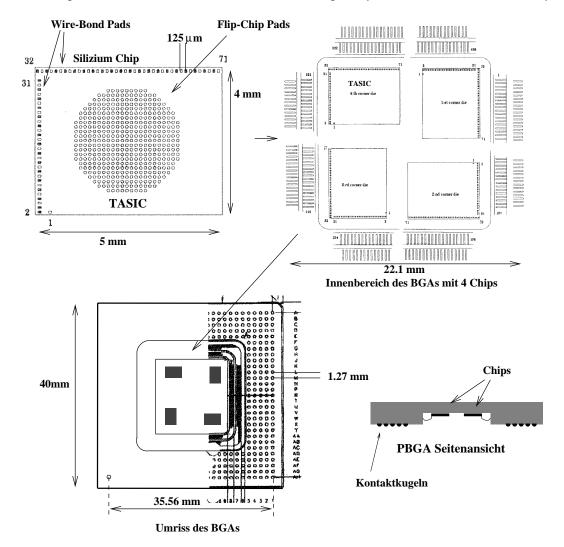

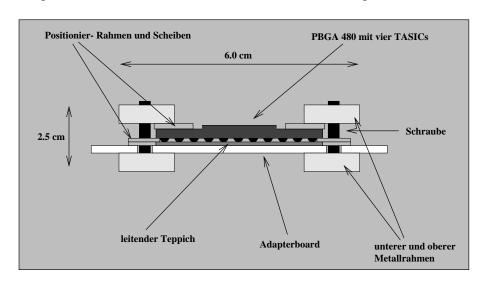

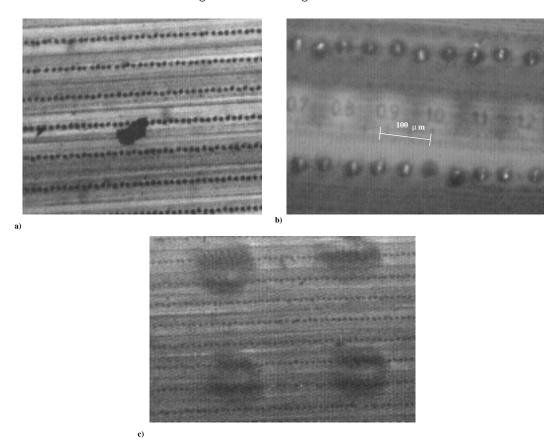

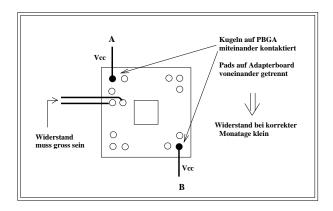

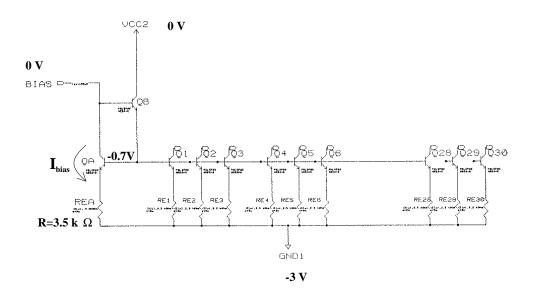

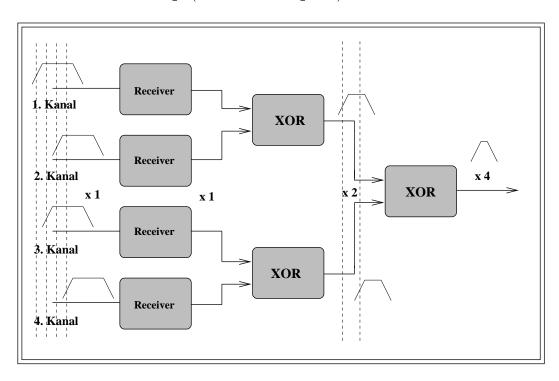

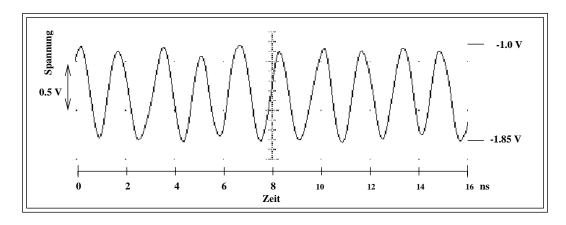

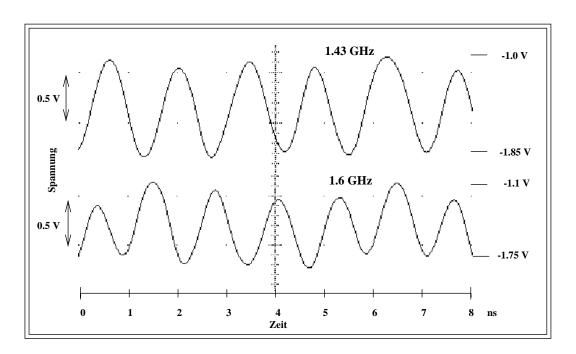

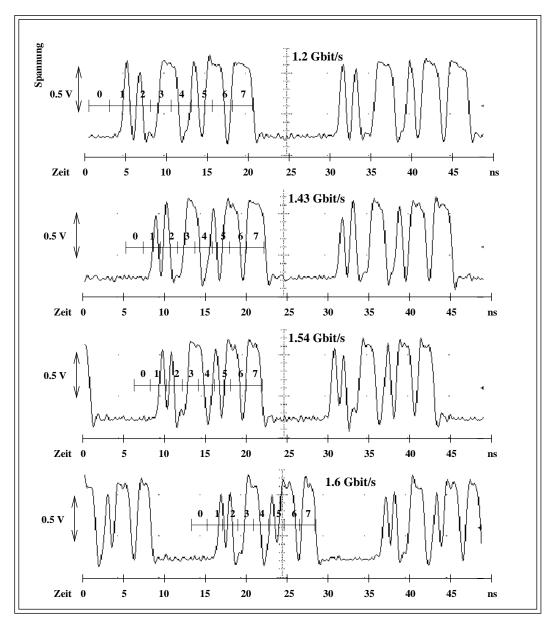

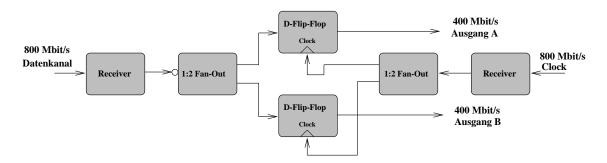

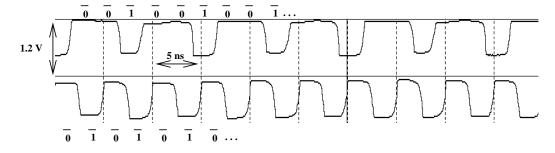

Als Ergebnis dieses Algorithmus erhält man für jede Triggerzelle eine Information von 8 Bits. Insgesamt sieben werden für die Klassifikation der drei eben beschriebenen Energiesummen benötigt. Das achte Bit gibt an, ob die Triggerzelle die Maximumsbedingung innerhalb der  $3\times 3$ -Nachbarschaft besitzt. Diese Information wird, nachdem sie in Look-Up-Tables, die auf dem Triggerprozessor integriert sind, in einen sogenannten Feature-Kode umgewandelt und zur zentralen Triggerlogik weitergeleitet. Der Feature-Kode charakterisiert jede Zelle mit ihrem physikalischen Inhalt, wie z.B.:  $e^{\pm}/\gamma$  mit großer Energie gut isoliert oder  $e^{\pm}/\gamma$  mit mittlerer Energie schlecht isoliert oder ähnliche Information. Die Verwendung verschiedener Energieschwellen innerhalb des Prozessor-ASICs erlaubt eine anpassungsfähige Wahl der Triggerkriterien. So können beispielsweise für Elektronen oder Photonen mit sehr hohem Transversalimpuls die Isolationsbedingungen abgeschwächt werden, da die Ausdehnung elektromagnetischer Schauer mit steigender Energie zunimmt.