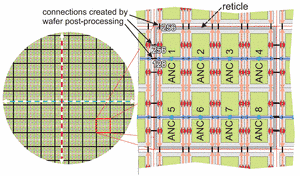

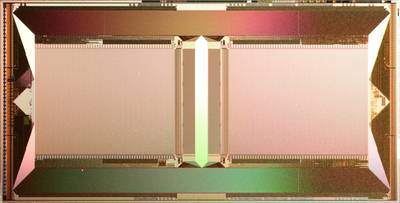

The initial version of the Analog Network Chip (ANC) is called HICANN (High Input Count Analog Neural Network). It is the primary building block for the FACETS wafer-scale system. It contains the mixed-signal neuron and synapse circuits as well as the necessary support circuits and the host interface logic.

Eight HICANN chips will be integrated on a single reticle. The size of the HICANN chip is chosen to be 5x10 mm2. This allows to fully qualify the HICANN in silicon using Multi Project Wafer

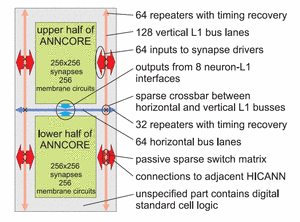

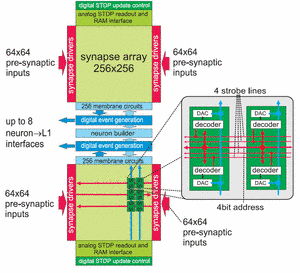

The central functional block of the HICANN chip is the Analog Neural Network Core (ANNCORE) containing 128k synapses and 512 membrane circuits which can be grouped together to form neurons with up to 16k synapses. The interconnections between the HICANN chips run vertically and horizontally through the chip, with crossbar switches at their intersections. Additional switch blocks give the synapses inside of the ANNCORE access to these signals.

The geometry of the analog network core (ANNCORE) is designed for a maximum input count of 16k pre-synaptic inputs per neuron. In this case an ANNCORE block will implement eight neurons. In contrast, using the maximum neuron number of 512 limits the number of inputs per neuron to 256. The high number of different input signals required for a neuron with 16k synapses leads to an excessive bandwidth demand: considering the case of a mean firing rate of 10 Hz, an acceleration factor of 105 and 16k inputs this equals to an average event rate of 164 Giga-events/s, easily crossing the Tera-event/s barrier in periods of bursty neural activity. Using traditional digital coding techniques an event packet would use about 16 to 32 bit, containing target address and delivery time. To make this communication demand feasible the ANNCORE uses a combination of space and time multiplexing. Due to the high density of the connections between the reticles and the on-die wiring between the HICANN chips inside the reticle a large number of signals can be multiplexed spatially. The presented implementation uses 256 bus lanes, consisting of two wires each, running alongside the synapse drivers.

Electronic Vision(s) Group – Dr. Johannes Schemmel

Im Neuenheimer Feld 227

69120 Heidelberg

Germany

phone: +49 6221 549849

fax: +49 6221 549839

email: schemmel(at)kip.uni-heidelberg.de

How to find us