# MULTI-ANODE PHOTON-MULTIPLIER READOUT ELECTRONICS FOR THE LHCb RING IMAGING CHERENKOV DETECTORS

Nigel John Smale St Anne's College

A thesis submitted for the degree of Doctor of Philosophy at the University of Oxford

Michaelmas Term, 2004

#### **Abstract**

A readout system for the Ring Imaging CHerenkov (RICH) detectors of the LHCb experiment has been developed. Two detector technologies for the measurement of Cherenkov photons are considered, the Multi-Anode Photo-Multiplier Tube (MAPMT) and the Hybrid Photon Detector (HPD), both of which meet the RICH requirements. The properties of the MAPMT are evaluated using a controlled single-photon source; a pixel-to-pixel gain variation of ~3 and a typical signal to noise of ~20 is measured. The relative tube efficiency is found to be reduced by ~26 % due to the detailed focusing structure of the MAPMT device.

A radiation hard application-specific integrated circuit (ASIC) chip, the Beetle1.2MA0, has been developed to capture and store signals from a pair of MAPMTs. The Beetle1.2MA0 is built on the architecture of the Beetle family that was designed for silicon strip detectors, the difference being a modified front-end amplifier. The 128 input-channels of the Beetle1.2MA0 have a charge-sensitive pre-amplifier followed by a CR-RC pulse shaper, which is sampled into an analogue memory with a depth of up to 160 time slots at 40 MHz. The internal bias generator module of the Beetle has also been developed and tested. This module generates all the required voltage and currents required internally to the chip, and consists of voltage DACs, current DACs, a current-source and a voltage source. Beetle1.2MA0 evaluation chips were fabricated, and the performance when connected to a MAPMT is demonstrated in terms of pulse profile, noise, pulse spillover and overshoot. The Beetle1.2MA0 ASIC is found to be well suited to LHCb RICH readout requirements.

A demonstrator system of the RICH readout electronics has been developed, which will serve either HPD or, with some small adaptation, MAPMT applications. Multimode fibres driven by vertical cavity surface emitting lasers (VCSEL) devices are used to transmit event-blocks of data in 900ns from the on-detector (Level\_0 region) to the Level\_1 region, which is located off-detector in a non-radiation environment. The data words are captured into 9-Mbit Quad Data Rate (QDR) static RAM at a rate of up to 160 MHz. The scheme for Level\_1 data receipt and buffering is described, and results from a full system test are presented.

## Acknowledgements

Amongst the numerous people who have helped me throughout this D.Phil, I would like to mention but a few that I am particularly indebted to:

Neville Harnew for providing me with the opportunity to work with the LHCb group, for taking care of the administrative side of my D.Phil, for his scientific guidance and for his continuous support.

John Bibby for sharing his wealth of engineering knowledge, for giving up his time to help with the technical detail and for his uplifting personality.

Marco Adinolfi and Stig Topp-Jorgensen, for their help and their combined efforts to construct, maintain, operate and write endless programming code for the hardware in the Oxford LHCb RICH lab.

Johan Fopma, Colin Perry, Barney Brooks and Pete Shield, for supporting my endeavor to gain this D.Phil and for politely answering endless queries.

Everybody at the ASIC lab, Heidelberg Germany, for sharing their extensive technical and theoretical ASIC knowledge, and for their friendship.

I would like to give special thanks to Stefanie, for being my wife and giving a reason to smile every day. To Georgie for giving me the inspiration to start my DPhil. To Mia for giving me the inspiration to finish my DPhil. To my mother and father for always being there and for supporting my alternative route through life.

On a lighter note I would also like to thank Eddie for being the oracle. Niels for sharing his off road jump skills. Martin for the RTFM advice. Sven for having too many beers in his wine, and for all of his help. Daniel for writing in English. Harald for taking me to a garage so that I could get rid of 350 euros. Rainer and Sylvia for supplying an excellent place of study, with the necessary food for thought. Timo for paying my fines. Marco for making my plots blue. Stig for giving the data that I needed. Charlotte for grouping my captions and Mike, and I am sure Lois too, for enjoying my research.

# Table of Contents

| ABSTRA  | СТ                                              | II  |

|---------|-------------------------------------------------|-----|

| Acknow  | WLEDGEMENTS                                     | III |

| TABLE C | OF CONTENTS                                     | IV  |

| LIST OF | Figures                                         | VII |

| PREFACI | E                                               | 1   |

| СНАРТЕ  | CR 1                                            | 3   |

| THE LH  | ICB Experiment                                  | 3   |

| 1.1     | The LHCb detector                               | 3   |

| 1.2     | Triggers                                        | 13  |

| 1.3     | LHCb Global Electronic Scheme                   | 16  |

| 1.3     | 3.1 General scheme and specifications           | 17  |

| 1.4     | Summary                                         | 23  |

| СНАРТЕ  | ZR 2                                            | 24  |

| Тне Ми  | JLTI-ANODE PHOTO-MULTIPLIER TUBE                | 24  |

| 2.1     | Principle of operation                          | 24  |

| 2.2     | The M64 MAPMT family                            | 26  |

| 2.3     | The MAPMT test set-up                           | 27  |

| 2.4     | Characteristics of the M64 MAPMT                | 31  |

| 2.5     | Summary                                         | 36  |

| СНАРТЕ  | ZR 3                                            | 38  |

| INTROD  | NICTION TO THE DESIGN OF AN MADM'T BEADOUT CHID | 20  |

|     | 3.1           | Requirement                                        | 38  |

|-----|---------------|----------------------------------------------------|-----|

|     | 3.1.          | 1 ASIC manufacturing processes                     | 39  |

|     | 3.1.          | 2 Chip selection                                   | 42  |

|     | 3.1.          | 3 The Beetle readout chip                          | 44  |

|     | 3.2           | MOS FET characteristics                            | 48  |

|     | 3.3           | Noise and amplifiers                               | 54  |

|     | 3.4           | Radiation hardened electronics                     | 59  |

|     | 3.4.          | 1 Accumulated radiation effects in MOS transistors | 62  |

|     | 3.4.          | 2 Single event effects (SEE) in MOS transistors    | 68  |

| CHA | <b>PT</b> E   | R 4                                                | 74  |

| BE  | EETLE ]       | Bias Generator                                     | 74  |

|     | 4.1           | Layout techniques                                  | 75  |

|     | 4.2           | Current bias module                                | 77  |

|     | 4.2.          | 1 I-DAC                                            | 80  |

|     | 4.2.          | 2 Current-source and V-ref                         | 86  |

|     | 4.2.          | 3 Small-signal response and noise                  | 92  |

|     | 4.3           | Voltage-bias module                                | 94  |

|     | 4.4           | Summary                                            | 100 |

| CHA | <b>APT</b> EI | R 5                                                | 102 |

| Τŀ  | не Вер        | ETLEMA ASIC                                        | 102 |

|     | 5.1           | Front-end amplifier selection                      | 102 |

|     | 5.2           | Beetle front-end amplifier characteristics         | 106 |

|     | 5.3           | BeetleMA front-end design                          | 113 |

| 5.4 Beetle1.2MA0 submission                              | 122 |

|----------------------------------------------------------|-----|

| 5.4.1 Measurement test set-up                            | 123 |

| 5.4.2 Beetle1.2MA0 results                               | 127 |

| 5.4.3 Beetle1.2MA0 FE simulations                        | 143 |

| 5.5 Conclusions                                          | 145 |

| CHAPTER 6                                                | 146 |

| THE RICH DEMONSTRATOR READOUT SYSTEM                     | 147 |

| 6.1 Overview of the RICH electronics demonstrator system | 148 |

| 6.2 Consequences of detector re-optimisation             | 150 |

| 6.3 The readout system demonstrator                      | 152 |

| 6.3.1 Level_0                                            | 153 |

| 6.3.2 Level_1                                            | 159 |

| 6.3.3 Level_1 buffer                                     | 163 |

| 6.3.4 Delay Lock Loop (DLL)                              | 169 |

| 6.3.5 FPGA-2                                             | 172 |

| 6.3.6 System tests                                       | 172 |

| 6.4 Recent test beam results                             | 174 |

| 6.5 Summary                                              | 175 |

| CHAPTER 7                                                | 176 |

| SUMMARY                                                  | 176 |

| GLOSSARY OF TERMS                                        | 180 |

| Bibliography                                             | 185 |

# List of Figures

| Figure 1-1  | The side view layout of the LHCb spectrometer.                                                | p4  |

|-------------|-----------------------------------------------------------------------------------------------|-----|

| Figure 1-2  | The LHC interaction rate in MHz as a function of the luminosity.                              | p5  |

| Figure 1-3  | A Representation of the LHCb beam pipe.                                                       | p6  |

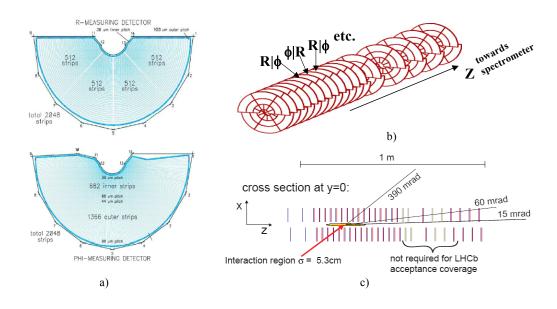

| Figure 1-4  | The 3D view of the VELO detector.                                                             | p7  |

| Figure 1-5  | The R and Phi VELO silicon detectors.                                                         | p8  |

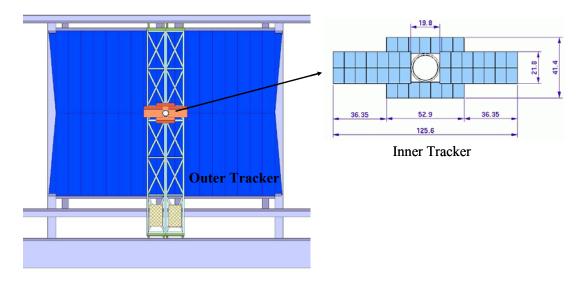

| Figure 1-6  | The IT and OT integration for a single station.                                               | p10 |

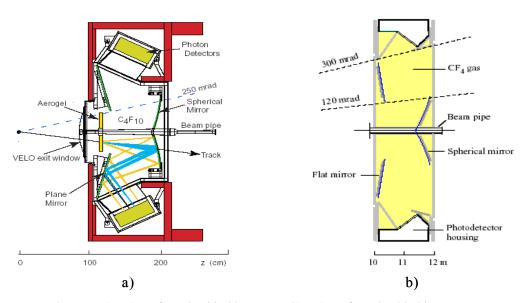

| Figure 1-7  | The RICH-1 and RICH-2 side views.                                                             | p11 |

| Figure 1-8  | A x-y projection of photons on the RICH-1 photo-detector plane.                               | p13 |

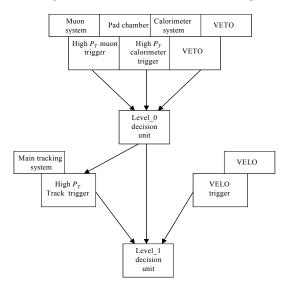

| Figure 1-9  | A block diagram of LHCb trigger contributions.                                                | p14 |

| Figure 1-10 | The General LHCb electronic readout scheme for Level_0 and Level_1.                           | p17 |

| Figure 1-11 | Bunch crossing synchronisation of the LHCb front end electronics.                             | p19 |

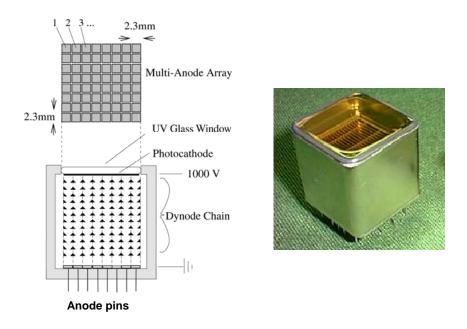

| Figure 2-1  | A schematic and photograph of a Hamamatsu M64 MAPMT.                                          | p25 |

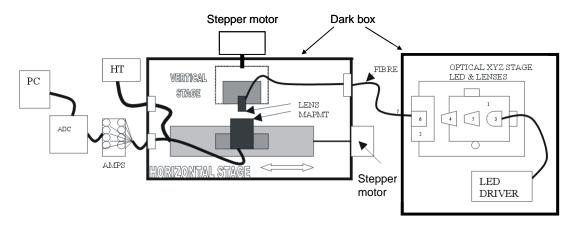

| Figure 2-2  | The MAPMT scanning facility.                                                                  | p28 |

| Figure 2-3  | A Basic FET circuit for generating a LED pulse.                                               | p29 |

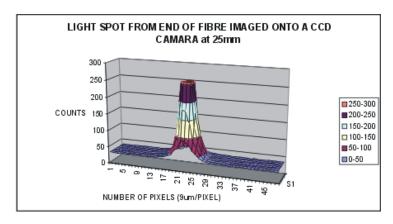

| Figure 2-4  | The Spot-size distribution of light from the end of the fibre.                                | p31 |

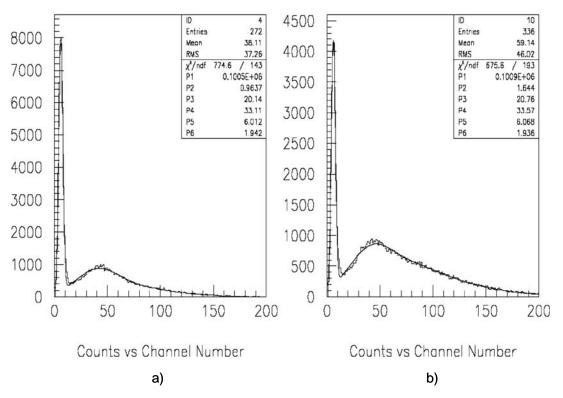

| Figure 2-5  | A Fitted spectra of MAPMT output for one, two and three photon input.                         | p32 |

| Figure 2-6  | Example of 1D and 2D scans across the face of the MAPMT Photocathode.                         | p33 |

| Figure 2-7  | Photograph of a single MAPMT pixel.                                                           | p34 |

| Figure 2-8  | Distribution of the mean of the single-photon peaks in ADC counts for 64 pixels of the MAPMT. | p35 |

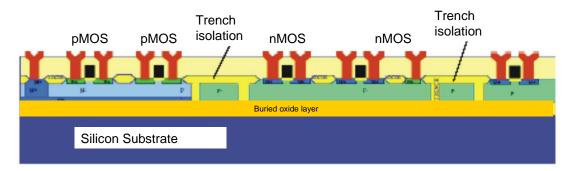

| Figure 3-1  | A cross sectional view of DMILL transistors.                                                  | p41 |

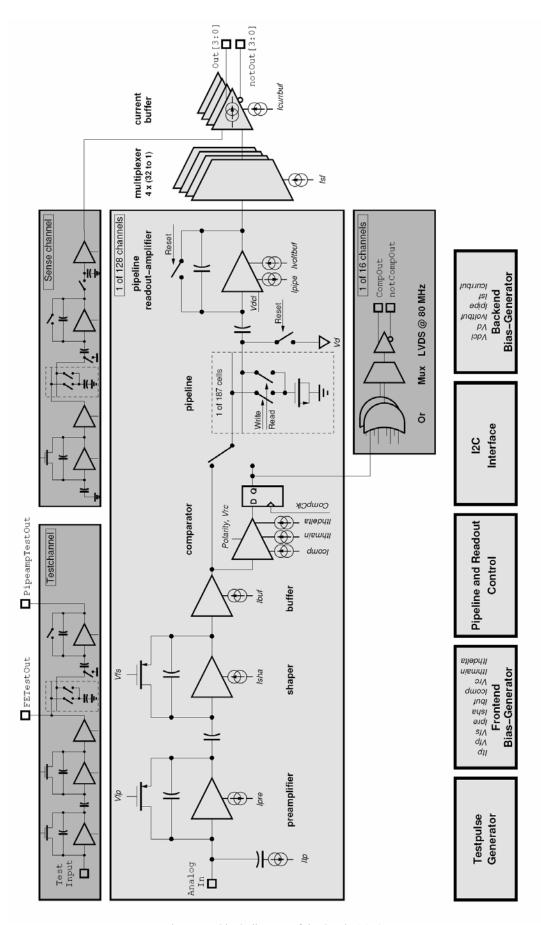

| Figure 3-2  | A Block diagram of the Beetle ASIC.                                                           | p47 |

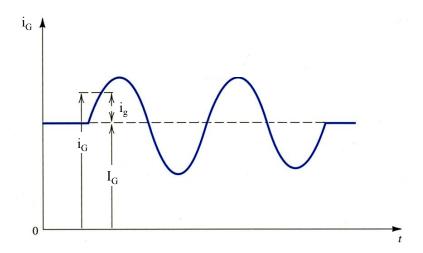

| Figure 3-3  | Wave-form showing symbol convention employed throughout this thesis.                                  | p48 |

|-------------|-------------------------------------------------------------------------------------------------------|-----|

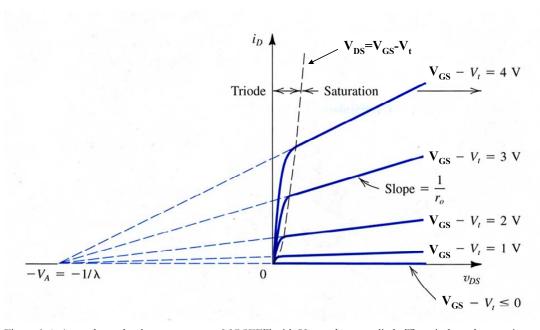

| Figure 3-4  | Operating characteristics of an n-channel enhancement-type MOSFET.                                    | p49 |

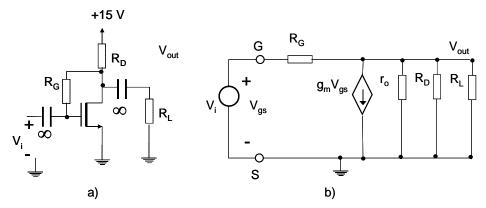

| Figure 3-5  | A common-source amplifier and the equivalent small-signal model.                                      | p52 |

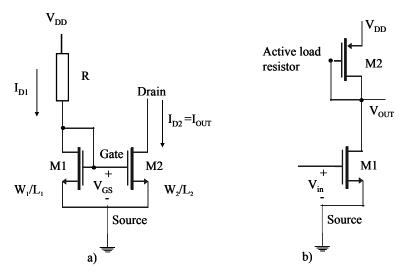

| Figure 3-6  | The Current mirror and common-source amplifier with active R load.                                    | p53 |

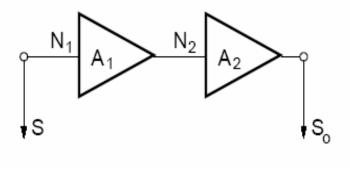

| Figure 3-7  | The Cascade of two amplifiers.                                                                        | p54 |

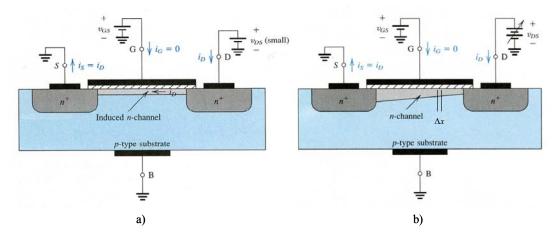

| Figure 3-8  | MOS FET in the triode region and saturation region.                                                   | p57 |

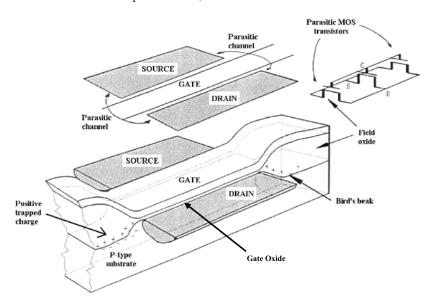

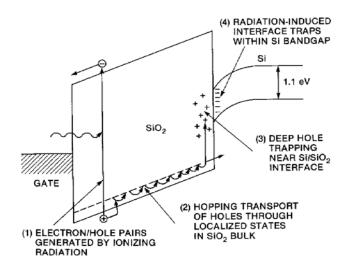

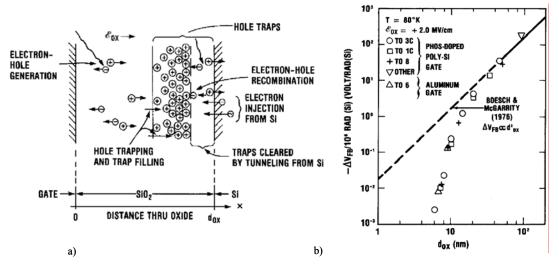

| Figure 3-9  | Gate and field oxides of a FET device.                                                                | p62 |

| Figure 3-10 | Energy band diagram of a MOS structure.                                                               | p64 |

| Figure 3-11 | Hole trapping in the MOS oxide with positive gate bias applied.                                       | p65 |

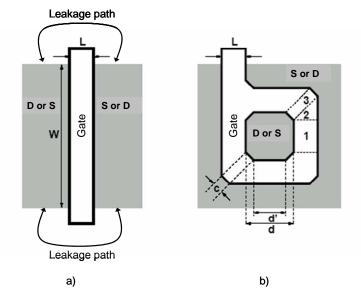

| Figure 3-12 | Schematic drawing of the linear and enclosed FET geometry.                                            | p67 |

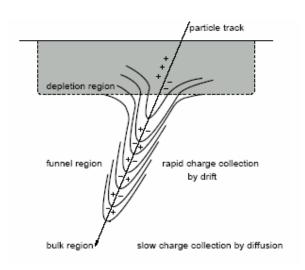

| Figure 3-13 | Enhanced charge collection by funnelling.                                                             | p69 |

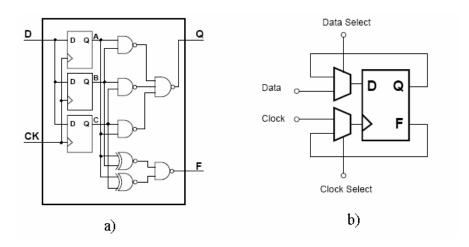

| Figure 3-14 | Triple redundant flip-flop and self correcting cell.                                                  | p71 |

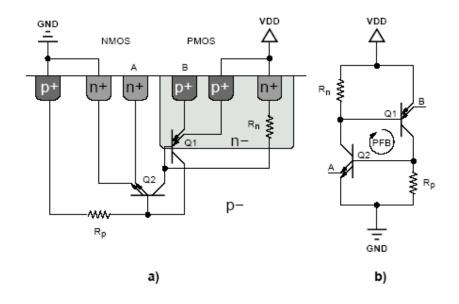

| Figure 3-15 | A CMOS device showing parasitic thyristors Q1 and Q2.                                                 | p72 |

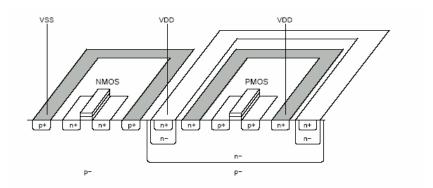

| Figure 3-16 | Layout principle of guard rings.                                                                      | p73 |

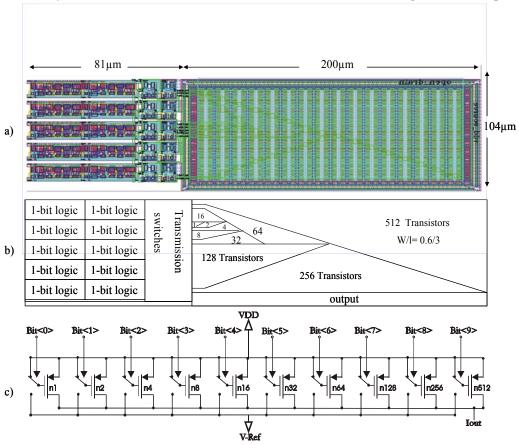

| Figure 4-1  | The BeetleBG1.0 bias generator test structure.                                                        | p74 |

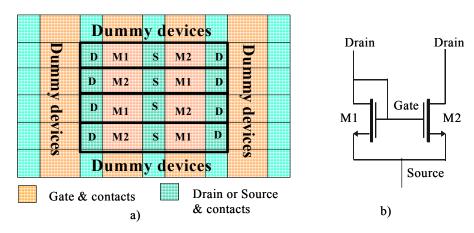

| Figure 4-2  | Applying layout rules to a current mirror component.                                                  | p76 |

| Figure 4-3  | The BeetleBG1.0 current reference scheme.                                                             | p78 |

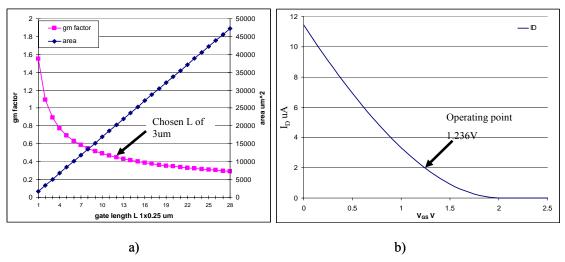

| Figure 4-4  | The optimisation for W/L of the BeetleBG1.0 LSB-FET.                                                  | p81 |

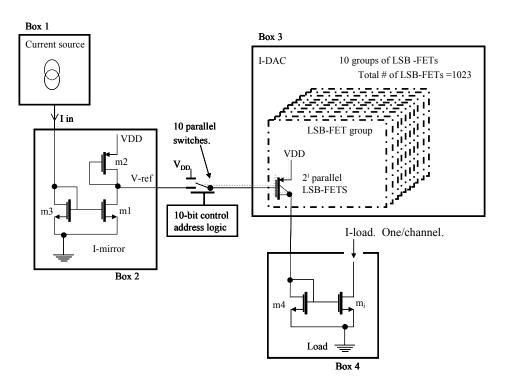

| Figure 4-5  | The BeetleBG1.0 10-bit binary-weighted current DAC.                                                   | p83 |

| Figure 4-6  | Linearity results for the BeetleBG1.0 current DAC.                                                    | p84 |

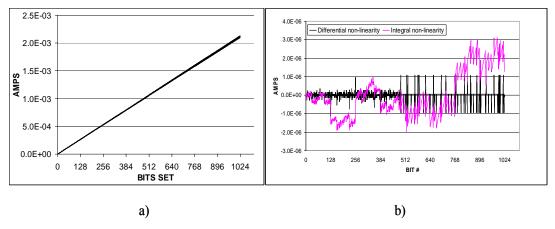

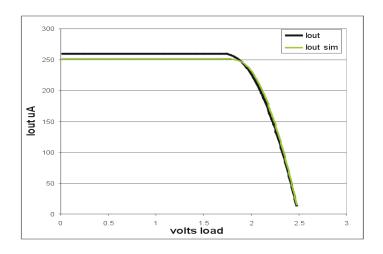

| Figure 4-7  | Measurement results for $I_D$ as a function of $V_{LOAD}$ for the LSB of the BeetleBG1.0 current DAC. | p86 |

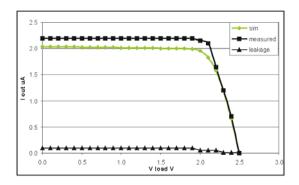

| Figure 4-8  | The BeetleBG1.0 V-ref current mirror used for the gate voltage of the current DAC.                 | p89  |

|-------------|----------------------------------------------------------------------------------------------------|------|

| Figure 4-9  | The BeetleBG1.0 regulated cascode current-source.                                                  | p90  |

| Figure 4-10 | $I_{\mbox{\scriptsize OUT}}$ from the BeetleBG1.0 regulated cascode current-source.                | P92  |

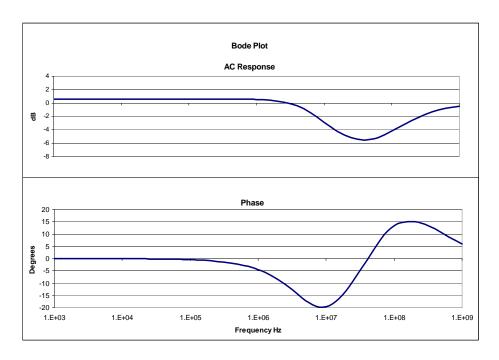

| Figure 4-11 | The Bode plot for the small-signal analysis of the BeetleBG1.0 I-DAC output.                       | p93  |

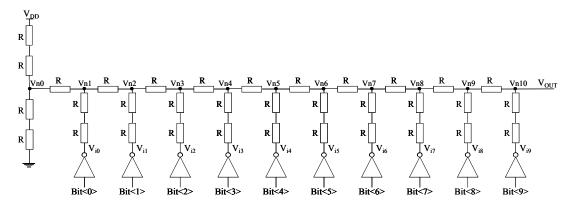

| Figure 4-12 | Schematic circuit diagram of the BeetleBG1.0 10-bit R-2R ladder.                                   | p95  |

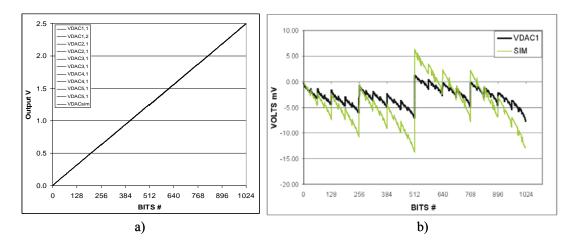

| Figure 4-13 | The BeetleBG1.0 R-2R 10-bit voltage DAC.                                                           | p97  |

| Figure 4-14 | Linearity results from the BeetleBG1.0 voltage DAC.                                                | p98  |

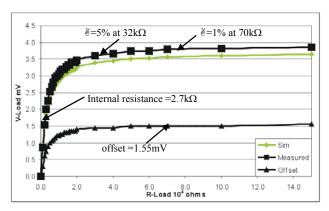

| Figure 4-15 | $V_{\text{out}}$ as a function of R load for the BeetleBG1.0 voltage DAC, with 1 LSB set.          | p99  |

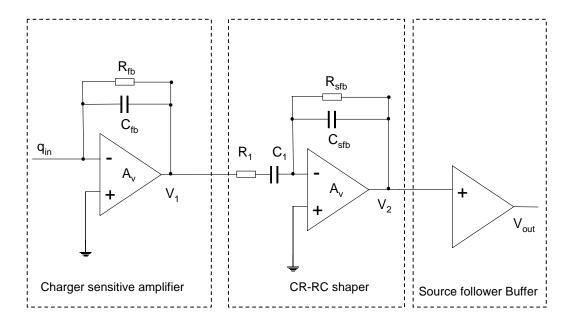

| Figure 5-1  | The Beetle front-end amplifier consisting of CSA, shaper amplifier and buffer.                     | p102 |

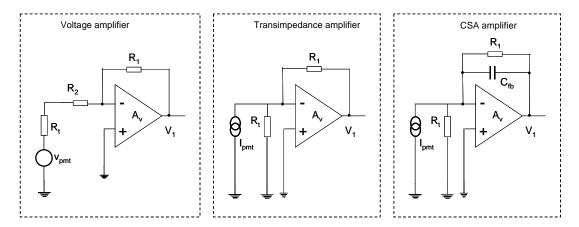

| Figure 5-2  | The three possible amplifier types considered for MAPMT use.                                       | p105 |

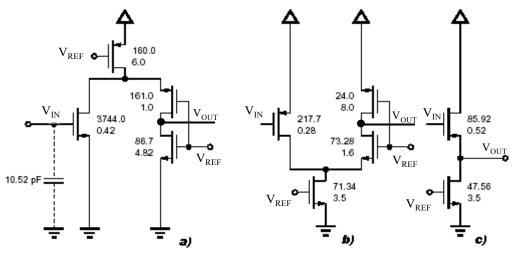

| Figure 5-3  | The core amplifiers of the Beetle1.3 chip.                                                         | p107 |

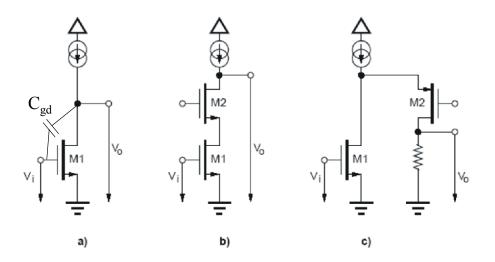

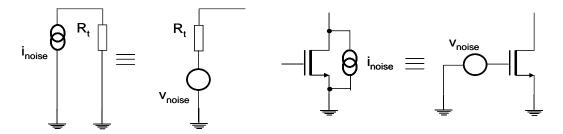

| Figure 5-4  | Design stages of the NMOS folded cascode amplifier.                                                | p108 |

| Figure 5-5  | The Norton and Thevenin-equivalents for a resistor and FET.                                        | p110 |

| Figure 5-6  | The noiseless CSA circuit connected to a MAPMT.                                                    | p112 |

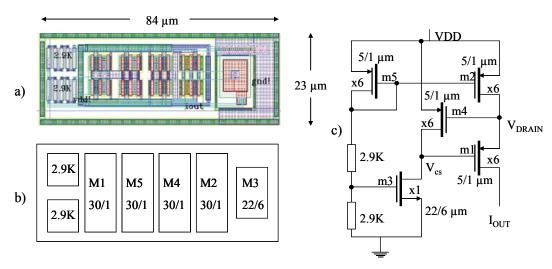

| Figure 5-7  | The schematic and physical layout of the Beetle1.2MA0 CSA pre-amplifier.                           | p114 |

| Figure 5-8  | Small-signal model of the BeetleMA CSA.                                                            | p115 |

| Figure 5-9  | The simulated BeetleMA CSA output response to a 300 ke <sup>-</sup> Input signal from a MAPMT.     | p117 |

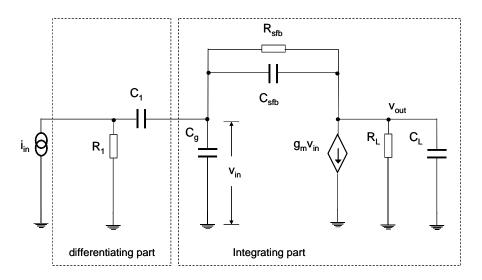

| Figure 5-10 | Small-signal model of the BeetleMA shaper.                                                         | p119 |

| Figure 5-11 | The schematic and physical layout of the BeetleMA shaper amplifier.                                | p121 |

| Figure 5-12 | The simulated BeetleMA shaper output response to a 300 ke <sup>-</sup> Input signal from an MAPMT. | p122 |

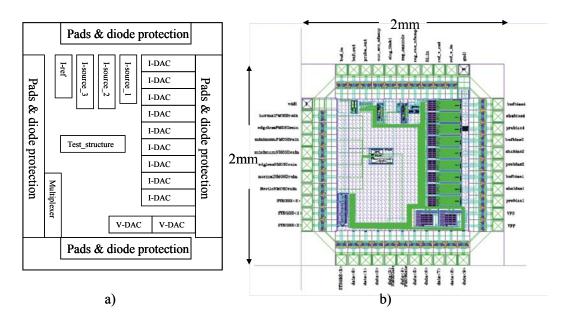

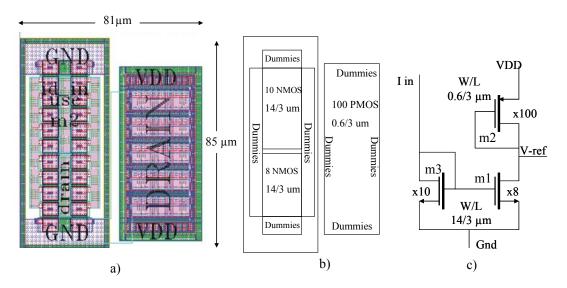

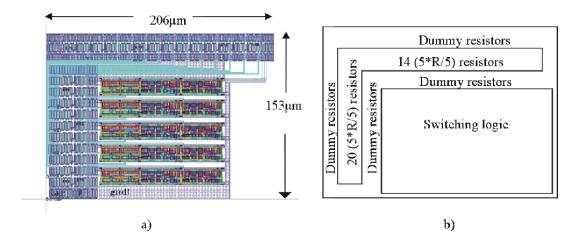

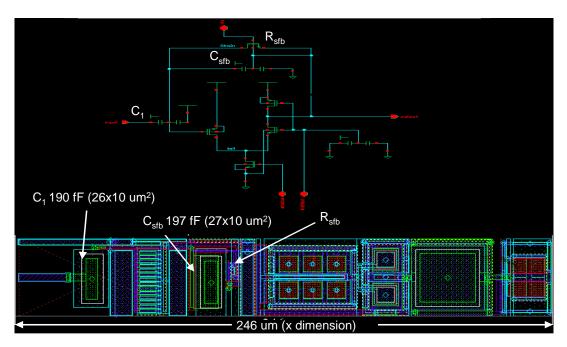

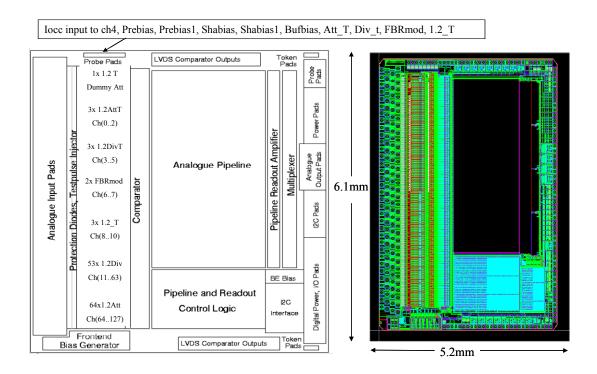

| Figure 5-13 | The Beetle1.2MA0 floor plan and layout.                                                                               | p123 |

|-------------|-----------------------------------------------------------------------------------------------------------------------|------|

| Figure 5-14 | The Beetle1.2MA0 test set-up.                                                                                         | p124 |

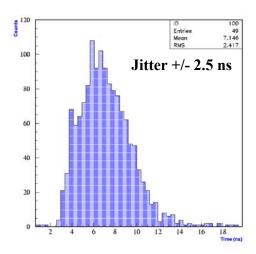

| Figure 5-15 | The measured time jitter from the MAPMT tube.                                                                         | p125 |

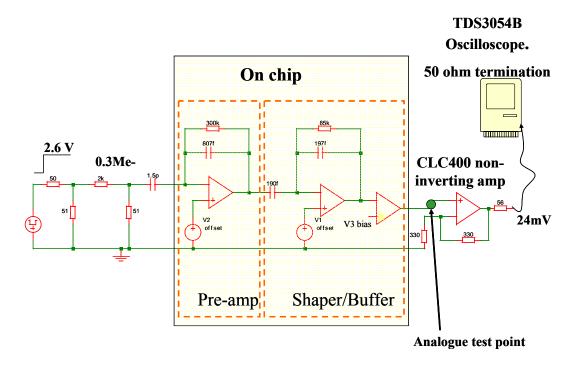

| Figure 5-16 | The test circuit for a single channel readout from the Beetle1.2MA0 probe points.                                     | p126 |

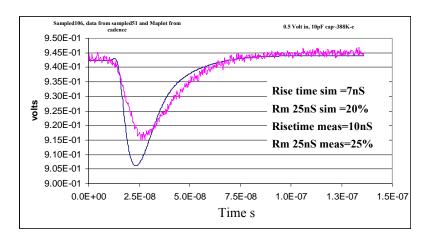

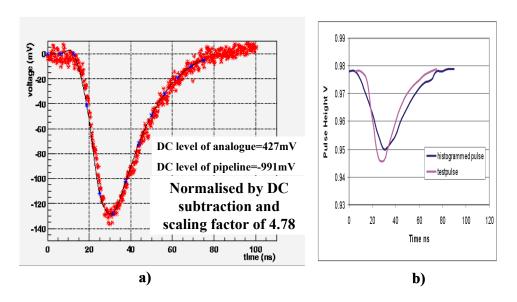

| Figure 5-17 | Comparison of simulated and measured analogue output response from an external test-pulse injection.                  | p127 |

| Figure 5-18 | A pulse height scan from the Beetle1.2MA0 pipeline.                                                                   | p128 |

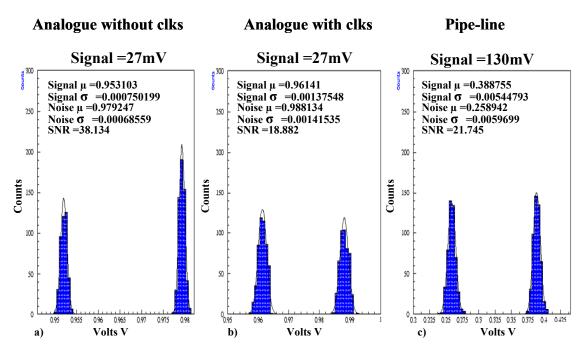

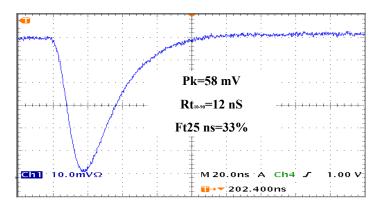

| Figure 5-19 | Signal and noise measured at the Beetle1.2MA0 probe point.                                                            | p129 |

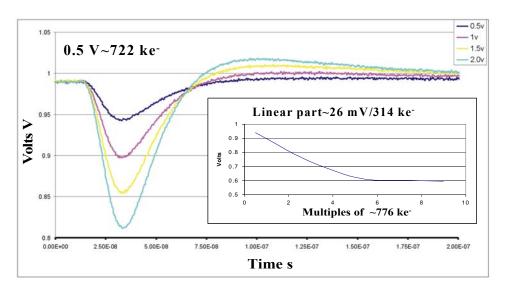

| Figure 5-20 | The pulse shape and linearity of the Beetle1.2MA0 front-end amplifier, measured at the probe point.                   | p130 |

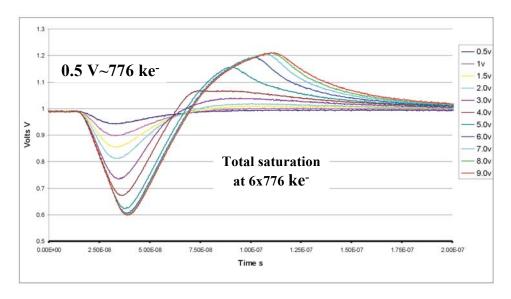

| Figure 5-21 | Beetle1.2MA0 front-end saturation effects measured at the probe point.                                                | p131 |

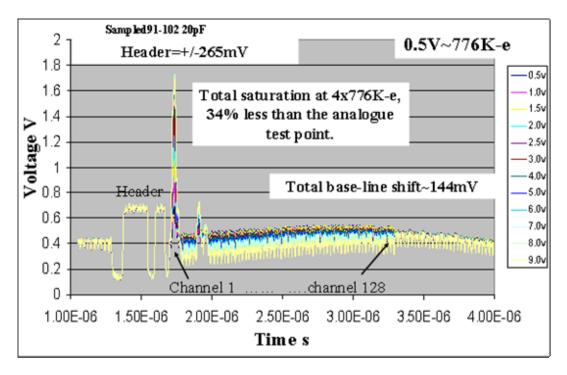

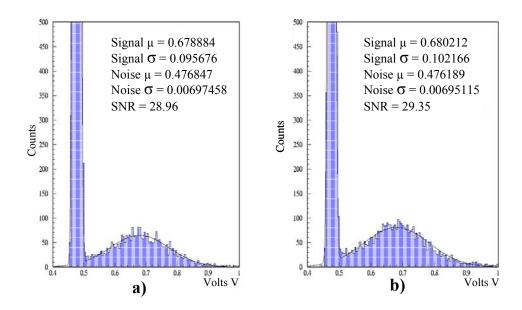

| Figure 5-22 | Full read out of 128 channels through the Beetle1.2MA0 pipeline.                                                      | p132 |

| Figure 5-23 | Zoom of data in channel 1 read out from the Beetle1.2MA0 pipeline.                                                    | p133 |

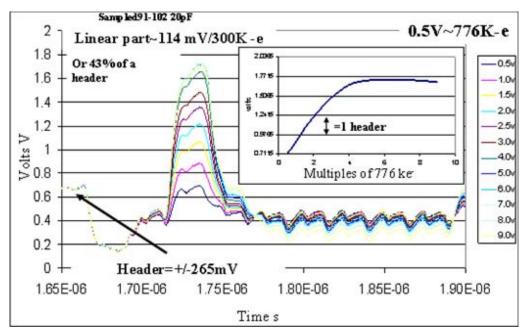

| Figure 5-24 | A typical Beetle1.2MA0 front-end response to a single-photon with the MAPMT.                                          | p134 |

| Figure 5-25 | Beetle1.2MA0 pipeline response to an intensity increasing                                                             | p135 |

|             | intensity light source on the MAPMT.                                                                                  |      |

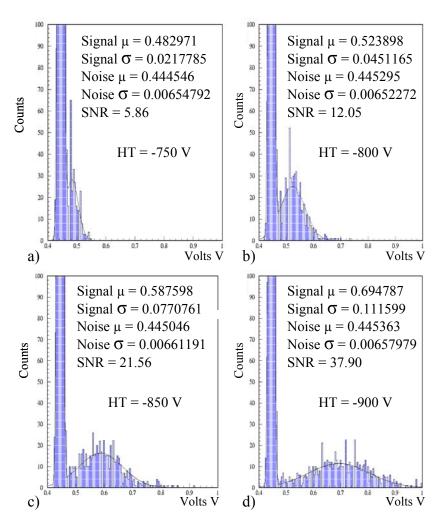

| Figure 5-26 | Photon response for $-750~\rm V$ to $-900~\rm V$ high voltage bias settings measured at the Beetle1.2MA0 probe point. | p136 |

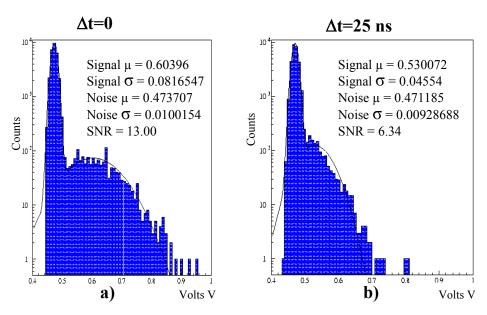

| Figure 5-27 | Measurement from the Beetle1.2MA0 pipeline at time t=0 and 25 ns later.                                               | p137 |

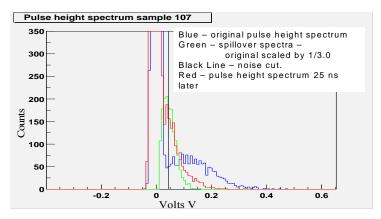

| Figure 5-28 | Pipeline spill-over scaling plot.                                                                                     | p138 |

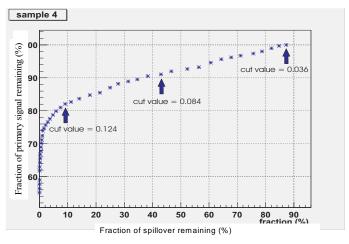

| Figure 5-29 | The fraction of signal remaining in the pipeline verses spill-over remaining.                                         | p138 |

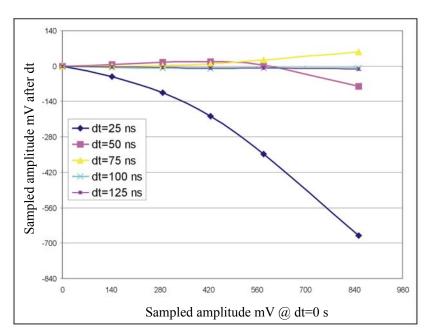

| Figure 5-30 | Pipeline pulse amplitude versus pulse remainder for $\Delta t = 25-125$ ns.                                           | p139 |

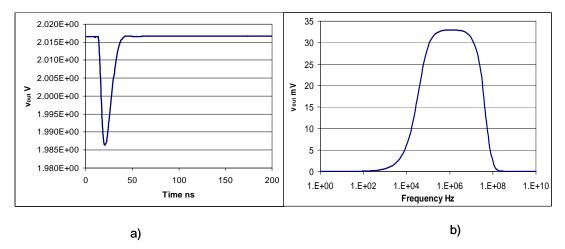

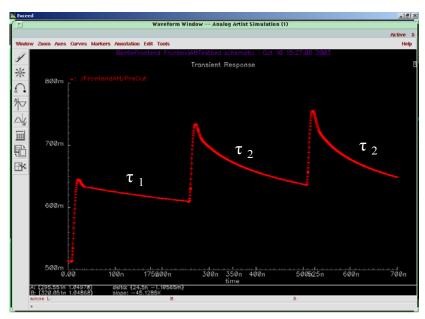

| Figure 5-31 | Simulated $v_{\text{out}}$ of the Beetle1.2MA0 CSA for a regularised 10 $\%$ Channel occupancy. | p140 |

|-------------|-------------------------------------------------------------------------------------------------|------|

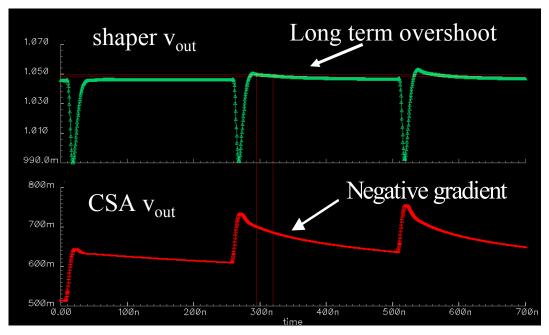

| Figure 5-32 | Simulation of the output voltage over-shoot from the Beetle1.2MA0 CSA and shaper.               | p141 |

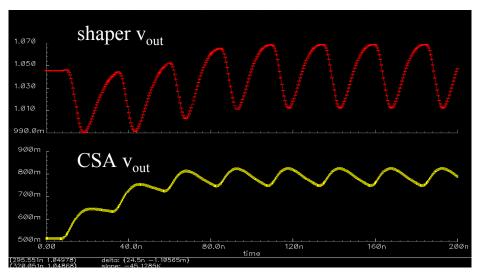

| Figure 5-33 | $v_{\text{out}}$ of the Beetle1.2MA0 CSA and shaper for the extreme case of 100 $\%$ occupancy. | p142 |

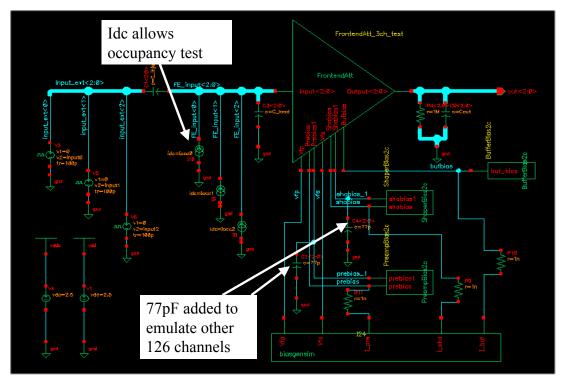

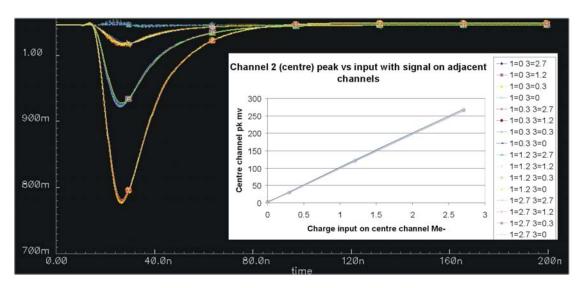

| Figure 5-34 | The 3 channel simulation test bed.                                                              | p143 |

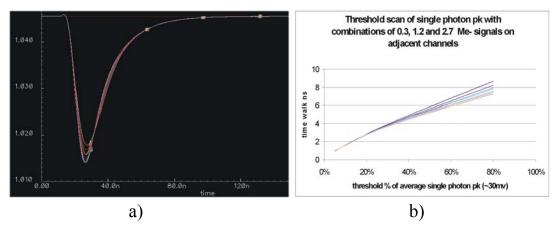

| Figure 5-35 | Cross talk evaluation on channel 2.                                                             | p144 |

| Figure 5-36 | Time walk of a single-photon response.                                                          | p145 |

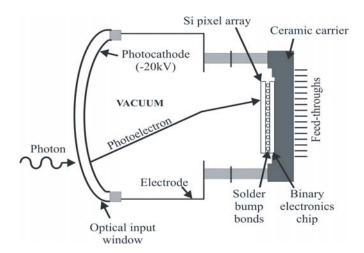

| Figure 6-1  | Schematic representation of the HPD.                                                            | p148 |

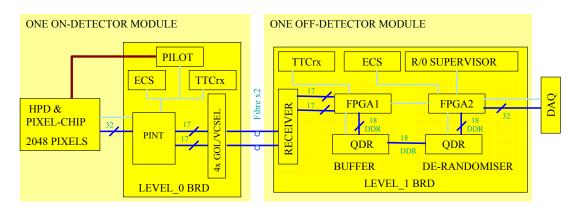

| Figure 6-2  | Block diagram of the demonstrator-system concept for HPD readout.                               | p149 |

| Figure 6-3  | Demonstrator readout scheme.                                                                    | p152 |

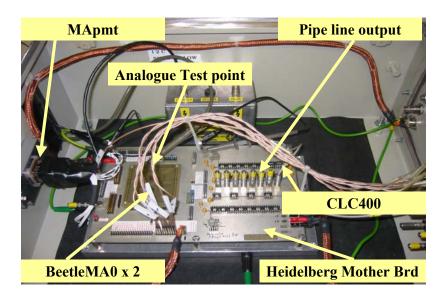

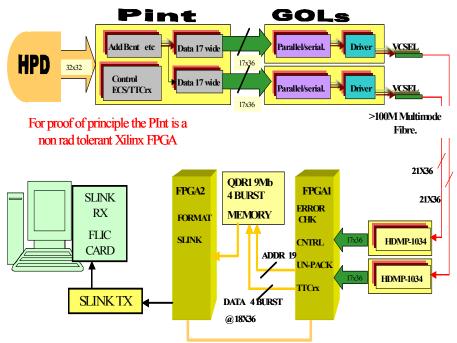

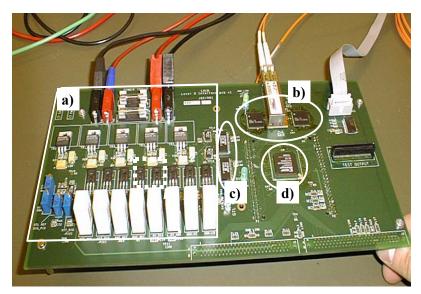

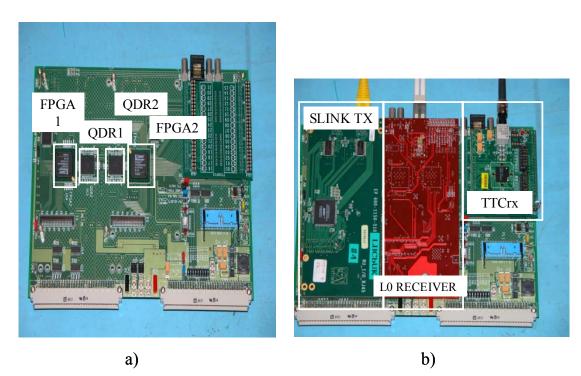

| Figure 6-4  | A photograph of the Level_0 demonstrator board.                                                 | p153 |

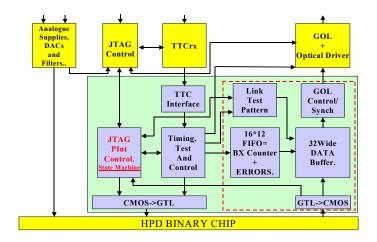

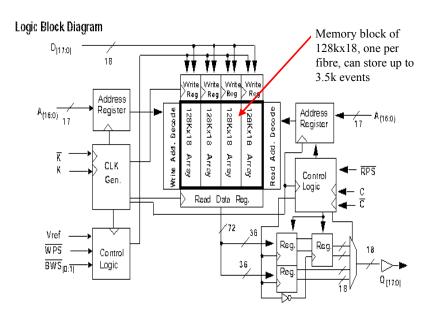

| Figure 6-5  | Functional block diagram of the PINT.                                                           | p154 |

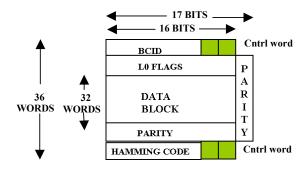

| Figure 6-6  | Event-block for one fibre and PINT formatting.                                                  | p155 |

| Figure 6-7  | A photograph of the Level_1 demonstrator board.                                                 | p159 |

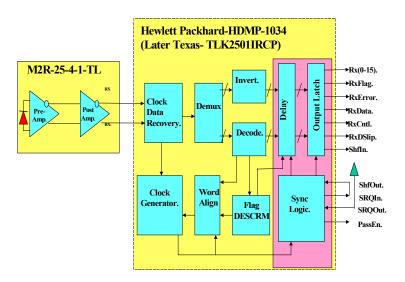

| Figure 6-8  | Block diagram of the L0 receiver board.                                                         | p160 |

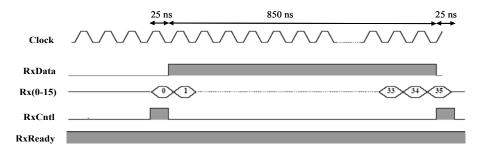

| Figure 6-9  | Timing relationship between RxData, RxCntl and RxReady.                                         | p161 |

| Figure 6-10 | Block diagram of the QDR SRAM.                                                                  | p162 |

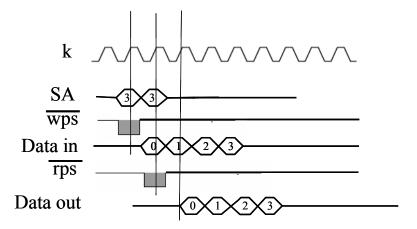

| Figure 6-11 | Timing diagram for writing and reading data to memory address 3 of the QDR.                     | p163 |

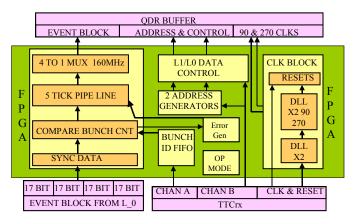

| Figure 6-12 | Block diagram for the FPGA algorithm and general interface scheme.                              | p164 |

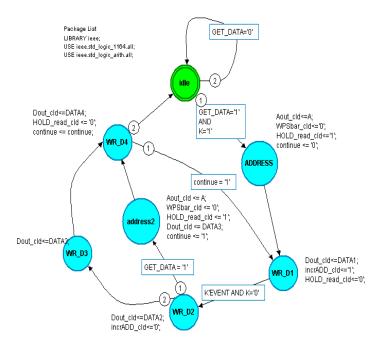

| Figure 6-13 | The write state machine.                                                                        | p167 |

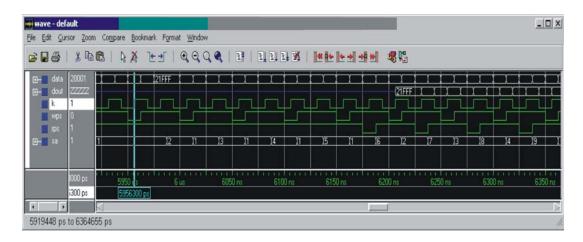

| Figure 6-14 | A simulation of data to and from the QDR chip.                                                  | p168 |

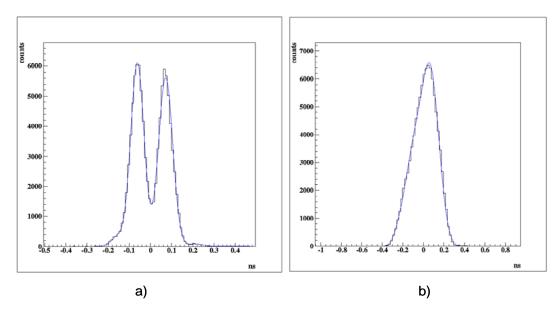

| Figure 6-15 | The TTCrx signal output jitter.                                                                 | p170 |

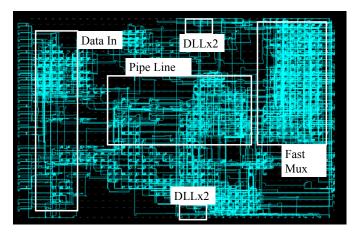

| Figure 6-16 | The internal layout of FGPA_1.                     | p171 |

|-------------|----------------------------------------------------|------|

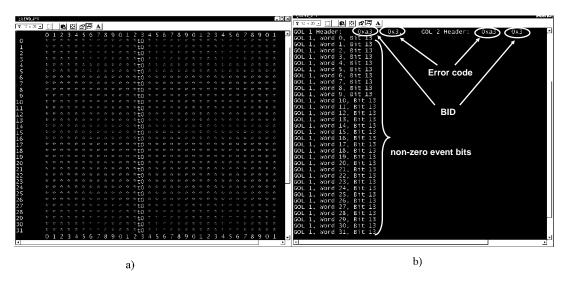

| Figure 6-17 | The readout from the S-link.                       | p173 |

| Figure 6-18 | Cherenkov rings observed from 10 GeV/c pions in an | p175 |

|             | $N_2$ gas radiator.                                |      |

#### **Preface**

The LHCb high-energy physics experiment is under development at CERN and will measure *CP*-violation in the B-meson system with very high precision. The experiment makes use of two Ring Imaging CHerenkov (RICH) detectors for particle identification. Two choices of RICH photon detectors have been proposed; the so-called Hybrid Photon Detector (HPD) being the baseline choice and the Multi-Anode Photo-Multiplier Tube (MAPMT) being the back-up. The HPD and MAPMT have effective pixel sizes of 2.5 mm<sup>2</sup> and 2 mm<sup>2</sup> respectively, corresponding to a total of ~325k and ~440k signal channels to be captured, temporarily stored, and read out. At the time of writing the HPD was adopted as the chosen photon detector.

To reduce the readout bandwidth and the amount of data that needs to be finally stored, LHCb uses three tiers of trigger and data storage: Level\_0, Level\_1 and the high level (HL). The trigger system processes the event data at each storage level and makes an accept or reject decision. The Level\_0 region is physically located on the LHCb detector, while Level\_1 and HL are some 100 m away but still within the experiment hall. When designing the RICH instrumentation system, special design considerations have to be made for electronic components on or near the detector to ensure radiation tolerance, as they will be subjected to high particle fluxes. Therefore the RICH electronics components used for Level\_0 have either been selected or designed to withstand the expected radiation level of 3 krad per year.

For the capture and storage of signals from the MAPMT, the 128-channel Beetle1.2MA0 front-end readout chip is used. The HPD readout utilizes the 1024 channel LHCBPIX1 chip, designed at CERN. Both devices are Application Specific Integrated Circuits (ASICs) with charge-sensitive input channels and 4 µs deep memories. Data capture rates are at 40 MHz in both cases.

This thesis describes the study of the MAPMT for its suitability of use as the RICH photon detector. The development of the Beetle1.2MA0 readout chip and its evaluation is fully detailed. In addition, the development of the RICH readout system that transmits, and stores, event data from the Level\_0 to Level\_1 regions is described. Particular detail is given to the Level\_1 memory region. Although the Level\_0 to Level\_1 readout chain has primarily been

designed for reading out the HPD, it is also compatible with the readout of the MAPMT with minor modifications.

In this thesis the author gives a general overview of the LHCb experiment and detector specifications in Chapter 1. Chapter 2 describes the MAPMT and its properties; a detailed account of the author's evaluation of a Hamamatsu R5900-00-M64 H7546B MAPMT is given. Chapter 3 discusses the electronic requirements for reading out an MAPMT and presents arguments why the Beetle ASIC chip was selected for this purpose. The principles underlying the design of a RICH readout chip to optimize for radiation tolerance and electronic noise are also given. Chapter 4 gives an account of a core module, the bias generator, which was designed and tested by the author. This module is internally used for biasing the Beetle chip. In order to make the Beetle chip compatible with RICH specifications, the author re-designed the Beetle front-end amplifiers. This necessitated a full study of candidate front-end amplifier types and resulted in the Beetle1.2MA0 chip submission. Chapter 5 describes the amplifier design flow in schematic and layout, and highlights the successful test results of the chip. Chapter 6 describes the upstream Level\_1 readout system, with particular attention given to data storage. The author's contribution was to select the Level\_1 hardware and develop algorithms to capture and buffer data received from the Level\_0 region. The author collaborated with the University of Cambridge in this work. Finally a summary is given in Chapter 7.

# Chapter 1.

# The LHCb experiment

Since 1993 physicists and engineers have been working on the circular proton-proton (pp) collider, named the Large Hadron Collider (LHC), which is situated at CERN Geneva. The LHC will make use of the existing 27 km circumference Large Electron Positron (LEP) collider tunnel. Each of the four interaction regions houses a major detector. The bunch crossings will occur at a nominal rate of 40 MHz, a centre-of-mass energy of  $\sqrt{s}$  =14 TeV and a design luminosity of the order of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. For precision measurements of *CP*-violation and rare decays of B-mesons, a high-energy particle detector named LHCb is being built. Particle identification is an essential requirement of LHCb and is achieved with two Ring Imaging CHerenkov (RICH) detectors. This chapter briefly describes the LHCb detector, the global readout electronics and synchronisation scheme that must be adhered to, and the trigger scheme that is used to either accept or reject stored data.

#### 1.1 The LHCb detector

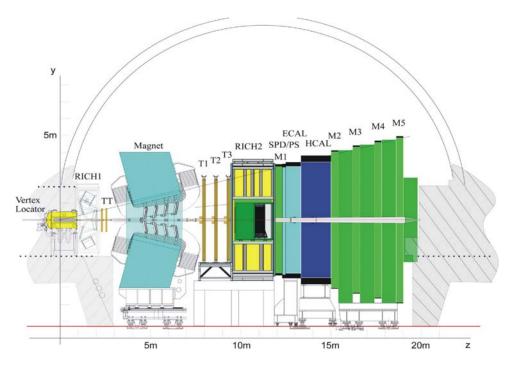

The LHCb detector [TDRp][TDR03opt], situated in the existing DELPHI pit at the Intersection-8 experimental area of the LHC, will be operational around summer 2007. A side view of the 19.7 m long detector is shown in Figure 1-1. At LHC energies, B-mesons generally emerge from collisions at angles close to the beam direction. This motivates a forward detector geometry with angular coverage between 10 and 300 mrad. Referring to Figure 1-1, LHCb has a Silicon VErtex LOcator (VELO), a Pile-up Veto detector (VETO), a Trigger Tracker (TT), a 4 Tm dipole magnet, two Ring Imaging Cherenkov detectors (RICH-1 & -2), three tracking stations (T1-T3), a Scintillating Pad Detector (SPD), a Pre-Shower (PS), an Electromagnetic CALorimeter (ECAL), a Hadronic CALorimeter (HCAL) and a five-station Muon system (M1-M5).

Figure 1-1 The side view layout of the LHCb spectrometer showing the VELO, the two RICH counters, the four tracking stations TT and T1-T3, the 4 Tm dipole magnet, the Scintillating Pad detector (SPD), Preshower (PS), Electro-magnetic (ECAL) and Hadronic (HCAL) Calorimeters, and the five muon stations M1-M5.

The LHCb coordinate system is such that z points along the detector axis, x points towards the centre of the LHC, and y is vertically upwards. The interaction point is at (0,0,0).

#### The interaction rate

For LHCb to make valid trigger decisions and reconstruct tracks with high efficiency, the detector occupancy must be kept low. A high occupancy will likely result when there is more than one pp interaction per bunch crossing. Multiple pp interactions would also cause ambiguity as to which primary vertex a specific B meson originated. Furthermore, the demands on the readout electronics would be increased and the tracking algorithms would have to deal with an increased particle density.

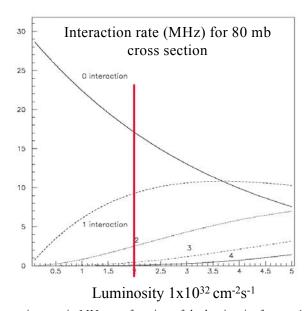

LHCb will operate with an average luminosity of  $2 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> in order to have only a single pp interaction within a bunch crossing. The number of n pp interactions in each bunch-crossing will follow a Poisson distribution

$$P_n = \frac{\mu^n}{n!} e^{-\mu}$$

with a mean  $\mu = L\sigma/f$ ,

where L is the luminosity, f is the bunch-crossing frequency and  $\sigma$  is the inelastic pp cross-section, which is ~80 mb at LHCb energies<sup>1</sup> [CHA03]. As only 2622 bunch crossings from the possible 3564 will have colliding beams, the effective bunch crossing frequency is ~30 MHz.

Figure 1-2 The interaction rate in MHz as a function of the luminosity for n = 1 to 4 using Equ 1-1.

At the nominal LHCb luminosity the mean  $\mu$  is 0.53 per crossing, compared to the LHC design of 20. Figure 1-2 shows the effective interaction rate as a function of the luminosity for zero to four pp interactions. The red line shows the nominal LHCb working value. As can be seen, the rate for single pp interaction is ~10 MHz.

#### The beam pipe

The performance requirements of LHCb demand that the position of the sensitive area of the VELO detectors is as close as possible to the beam and that there is a minimum amount of material in the detector acceptance. An increase in the amount of material leads to an increase in secondary particle interaction, which is problematic for the tracking stations and RICH detectors due to the increased occupancy that results. Secondary interactions are particularly critical for the VELO since material interactions in its vicinity make it difficult to reconstruct a

<sup>&</sup>lt;sup>1</sup> The barn is a unit of area. 1 mb=10<sup>-27</sup> cm<sup>2</sup>.

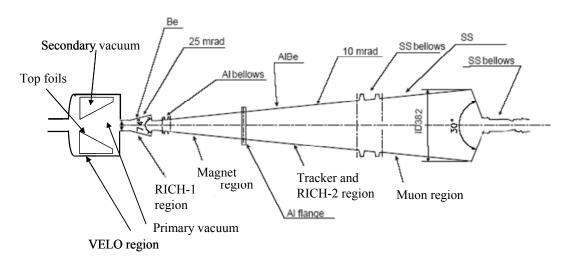

reliable vertex. For this reason the ~20 m LHCb beam pipe close to the VELO is made in sections of beryllium or aluminium/beryllium. The material thickness is a compromise between the mechanical strength required and an acceptable fraction of radiation-lengths. The cost and handling constraints makes it prohibitive to use any one low radiation-length material throughout the total beam length.

Figure 1-3 A representation of the beam pipe, including the VELO (not to scale).

Figure 1-3 is a representation of the LHCb beam pipe and shows the pipe sections and materials used. The VELO section (see also Figure 1-4) has a large primary vacuum vessel that maintains the  $\sim 10^{-9}$  mbar LHC vacuum. To protect the primary vacuum, the VELO detector modules are placed in a thin-walled aluminium alloy secondary container maintained at  $\sim 10^{-4}$  mbar. This structure also shields the detector modules within it from high frequency RF fields of the LHC beam. It also suppresses wake fields.

The RICH-1 section of the beam pipe is a 1840 mm length of 1 mm thick beryllium. The transition point from Be to AlBe, at the Al bellows, has been optimised to keep as low as possible the background induced by the beam pipe in the TT station. The final section is made from 2 to 4 mm thick stainless steel in the muon region, where secondary interactions are much less important.

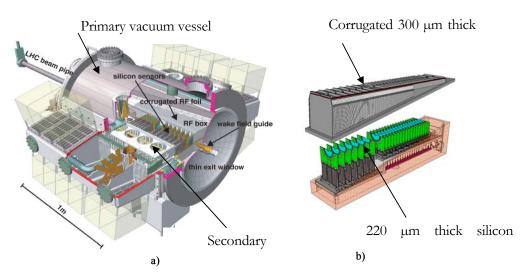

#### The VELO

The VELO must provide precise measurements of track coordinates close to the interaction region and is the main tracking system upstream of the magnet. The VELO features a series of silicon stations placed along the beam direction that are capable of measuring the primary vertex to a resolution of  $\sim 8~\mu m$  in the x and y direction, and  $\sim 40~\mu m$  in the z direction [MOR03].

Figure 1-4 a) 3D view of the VELO showing the large outer primary vacuum vessel and the internal (cut away area) of the internal secondary vacuum that houses the detector. b) The corrugated RF shield and silicon sensors.

Figure 1-4 a) shows a 3D view of the VELO with its primary and secondary vacuum vessels, as discussed previously. Figure 1-4 b) shows a more detailed view of the secondary vacuum vessel showing the silicon sensors within the RF shield. Each sensor is semi-circular in shape with an active area between radii of 8.17 mm and 42 mm. The 220 µm thick silicon sensors have either azimuthal (R measuring) or quasi-radial (phi measuring) strips, as shown in Figure 1-5 a). To maintain a high measurement resolution for tracks close to the beam axis whilst restricting the total number of readout strips, the pitch of the strips varies over the detector plane from 40 µm to 101.6 µm for the R measuring strips. Furthermore the strips are divided into four sections to insure a uniform strip capacitance. The magnitude and variation of strip capacitance has significant influence on the readout electronics as strip capacitance directly contributes to the electronic noise.

For the phi measuring detectors the strips are divided azimuthally into an inner and outer region. For the inner region the pitch varies from 35.5  $\mu$ m to 78.3  $\mu$ m, and the outer region from 39.3  $\mu$ m to 96.6  $\mu$ m.

There are 21 stations in total, shown in Figure 1-5c. As well as covering the full LHCb forward angular acceptance, the VELO also has a partial coverage of the backward hemisphere to improve the primary vertex measurement. The Level\_0 trigger, explained in section 1.2, aims to select beam crossings with only one pp interaction by reconstructing the z position of the primary interaction. For this purpose, two R measuring sensors placed upstream of the VELO stations are used, shown in blue in Figure 1-5 c). These stations are referred to as the VETO detector.

Figure 1-5 a) R and phi silicon detectors, b) R/phi arrangement per station, c) station set-up.

For reading out the VELO and VETO detectors, 16 front-end Beetle chips are used per silicon sensor. The Beetle chip development is a major work of the author and is described in chapters 3 to 5. For the VELO, the chips sample the data at a rate of 40 MHz and store them in a pipeline memory until the Level\_0 trigger decision has been made. On a Level\_0 trigger accept, the data are sent to a Level\_1 storage unit. In the case of the VETO the data channels are sampled at 40 MHz and have their signal response discriminated on-detector. A fast OR of groups of four data channels is performed and the result contributes to the Level\_0 trigger

decision-making process. Being so close to the interaction point, both the detector and readout chips are designed to be radiation hard<sup>2</sup> up to an expected exposed dose of the order of 10 Mrad per year.

#### Tracking system

The tracking system consists of the TT and T1-T3 tracking stations. The TT is the first station downstream of the VELO and is positioned in front of the magnet and just behind RICH-1. The three remaining stations are placed downstream of the magnet with equal spacing.

Together with the VELO, the TT is used in the Level\_1 trigger. Large impact parameter tracks found in the VELO are extrapolated to the TT. The magnetic field in the RICH-1 region allows their momenta to be coarsely measured. The TT consists of four planes of silicon strip detectors with strip pitch of 198 μm and thickness of 500 μm, split into two pairs of planes separated by 30 cm. The first and the fourth plane have vertical silicon strips while the second and third planes have their strips rotated by stereo angles of +5° and -5°, respectively. The total active area of the combined planes is approximately 8.3 m² giving ~140k readout channels. These are also read out using Beetle chips.

Each of the three tracking stations T1-T3 consists of an Inner Tracker (IT) close to the beam and an Outer Tracker (OT) surrounding the IT. The integration of the IT and OT are shown in Figure 1-6. The type of detector technology used and the physical size of the detectors are determined by the required resolution and the expected channel occupancy. For the high track density region close to the beam, silicon strip detectors are used. The strips are of the same type used in the TT discussed previously but are either 410  $\mu$ m or 320  $\mu$ m thick depending on their location. The readout electronics are also the same but the IT has fewer channels, approximately 130k. The Outer Tracker consists of straw tube drift cells, which are 5 mm in diameter. The emphasis is on tracking precision in the (x,z) magnet bending plane. The stations have two planes with wires in the vertical direction and two stereo planes which are tilted by either  $+5^{\circ}$  or  $-5^{\circ}$ .

<sup>2</sup> Circuits that can cope with doses up to a few 100 krad can be considered radiation tolerant whereas circuits that can cope with a few Mrad are classified as radiation hard.

9

Figure 1-6 The IT and OT integration for a single station.

The occupancy for each OT cell must be below 10% to ensure efficient track reconstruction. This gives constraints on the maximum wire length and cell size. The delay in signal arrival time at the preamplifier is the sum of the transit time of the track to the chamber, the drift time and the propagation delay along the wire. Besides additional constraints on the wire length and cell size, also the choice of 'fast' drift gas will be important. It is expected that all drift signals will be measured within 50 ns. The electronics used to read out the 54k channels is the so called 'ASDBLR' chip developed for ATLAS [TDRO].

#### The Calorimeter

The calorimeter, which consists of the ECAL, HCAL and PS/SPD, is used to identify electrons and hadrons for the trigger and off-line analyses. The PS, which is used to provide an accurate spatial detection of photons and electrons, is constructed from 14 mm thick lead plates followed by square scintillators that are read out by photo-detectors. The SPD is placed in front of the PS and is used for background rejection. The ECAL, built from 2 mm thick lead plates and scintillator plates, provides identification and an energy measurement of photons and electrons. The HCAL is constructed from scintillator tiles that are imbedded in an iron structure and read out with photo-detectors. Its purpose is to aid in the separation of high-energy hadrons and electrons, and to provide a transverse-energy measurement of hadrons.

#### The muon detector

The muon detector is used for muon identification and to provide trigger information. This detector makes use of Multi Wire Proportional Chambers (MWPCs). The station M1 is especially important for the transverse-momentum measurement of the muon track used in the Level\_0 muon trigger.

#### The magnet

The dipole magnet provides an integrated field of 4 Tm. The magnetic field is oriented vertically and has a maximum value of 1.1 T. The polarity of the field can be changed to compensate any small left-right asymmetries of the detector.

#### The Ring Imaging Cherenkov Detectors

Two RICH detectors, shown in Figure 1-7, are used in LHCb for the purpose of particle identification, primarily providing  $\pi/K$  separation in the momentum range from 1 to 100

Figure 1-7 a) RICH-1 from the side [TDR03opt], b) RICH-2 from the side [TDR00].

GeV/c. The first, RICH-1, a combined gas/aerogel device positioned upstream of the magnet, has an angular coverage of 25-300 mrad. The second, RICH-2, is a gas device downstream of

the magnet, which covers 10-120 mrad. These detectors are essential in reducing backgrounds and providing an efficient flavour tag of B<sup>0</sup> and anti-B<sup>0</sup> hadrons.

Cherenkov radiation is emitted whenever a charged particle with a velocity (v) exceeds the velocity of light c in a medium, i.e.  $v \ge c/n$ , where n= refractive index of the medium. Light is emitted in a coherent wave-front or cone with a characteristic Cherenkov angle given by  $\cos\theta = 1/(\beta n)$ , where  $\beta = v/c$  [YPS99]. In the LHCb RICH detectors, mirrors focus the Cherenkov photons onto photo-detection planes, which are outside the LHCb detector acceptance. Candidate photon detectors are Multi-Anode Photo-Multiplier Tubes (MAPMT) or pixel Hybrid Photon Detectors (HPD). The HPD was the baseline option and, during the time of writing, was chosen as the sole photon detector. MAPMTs were the backup solution and have been studied in depth for this thesis.

The RICH detectors are optimised to generate the maximum number of photons while maintaining the required spatial resolution. A source of imperfect resolution is the dispersion in the refractive index of the radiator. For  $C_4F_{10}$  gas the index varies from 1.0013 at long wavelength, to 1.0015 at about 200 nm, which is approximately the wavelength cutoff point of the photon detector with a UV glass entrance window. Therefore it is desirable to select wavelengths only within a small band that corresponds to the smallest change in the index. The RICH gas radiator chromatic dispersion is reduced by using small wavelengths into the UV range. However, the aerogel that is used to detect the lower momentum particles suffer mostly from Rayleigh scattering, which is dependent on  $\frac{1}{\lambda^4}$ , and therefore improves with larger wavelengths. Therefore the photo-detector is chosen to be sensitive to light in the visible and ultraviolet, and the Raleigh scattering is reduced with a filter, for example a glass window between the aerogel and gas interface.

The MAPMT can offer up to 200 times the gain of the HPD and is therefore less demanding on the front-end electronics due to a better signal-to-noise ratio (SNR). Conversely the HPD has far better single-photon resolution. A total photo-detector surface area of about  $2.9 \text{ m}^2$  is instrumented in the two RICH detectors, which requires approximately 480 HPDs or 5000 MAPMTs. The upstream RICH-1 has a 5 cm-thick aerogel radiator and an 85 cm-long  $C_4F_{10}$  radiator. The expected numbers of detected photons are 7 and 30 respectively for tracks

with particle velocity,  $\beta \cong 1$ . The downstream RICH-2 is filled with CF<sub>4</sub> radiator with an approximate length of 180 cm, giving 20 expected photons.

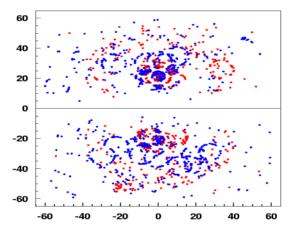

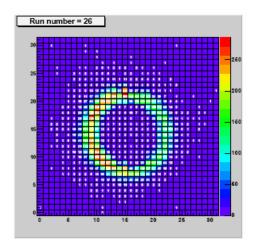

Several sources of background can place demands on the RICH readout electronics due to an increase in channel occupancy or by introducing saturation effects. For example, in RICH-1, low momentum charged particles bent backwards by the dipole magnet can strike the photo-detectors and produce showers of photo-electrons from Cherenkov radiation in their entrance windows. Further sources of background originate from secondary interactions in the upstream detector components, Rayleigh scattering of photons in the aerogel, particles remaining from previous bunch crossings and electronic noise. An example of a typical simulated event showing hit photo-detector pixels arising from gas and aerogel rings in RICH-1, including all background processes, is shown in Figure 1-8. The figure shows the x-y projection of photons on the photo-detector plane, in cm. In this event a typical number of about 50 charged particles were simulated traversing the detector.

Figure 1-8 x-y projection of photons on the photo-detector plane, in cm, for RICH-1. Background sources are included.

# 1.2 Triggers

With an LHC bunch crossing occurring every 25ns, approximately 10<sup>12</sup> B-hadron pairs will be produced per year at the LHCb luminosity. From these, approximately 10<sup>9</sup> will be of interest within the acceptance for storage and analysis. LHCb uses a 4-level trigger system to

make a decision on whether or not an event should be stored for off-line analysis. The trigger selects tracks originating a few millimetres away from where the pp collision took place; an average 7mm for an 80 GeV/c B-hadron. Tracks with a displaced vertex indicate that a B-hadron had been created, travelled a short way, and subsequently decayed. Each trigger level is more complex in its use of available information than the previous level. The first level, Level\_0, is implemented in custom electronic hardware. Level\_1 and the two High Level triggers (HLT) are computer algorithms executed on a farm of commodity processors.

To meet speed requirements, Level\_0 and Level\_1 triggers use coarse resolution information from selected detectors. The detectors and their trigger contributions are shown in Figure 1-9. The Level\_0 trigger uses information from the Muon, ECAL and HCAL to identify high-momentum leptons, hadrons and photons. The VETO is used to count the number of primary vertices and reject events that have multiple pp interactions. The Level\_0 trigger accepts events that have a single muon, electron or hadron high transverse momentum p<sub>T</sub>

Figure 1-9 Block diagram of trigger contributions [TDR00].

cluster. If the event is accepted, then the information on the high p<sub>T</sub> cluster which triggered the event is passed onto the Level\_1 trigger. Here the cluster is used as a seed to start the Level\_1 trigger analysis. All the event information from the VELO is used in the Level\_1 trigger decision. The event data from the VELO are first used to reconstruct the primary vertex. From this vertex a search of secondary vertices is performed. The trigger decision is then made on an

event probability based on the number of secondary vertices found. The algorithms used are sophisticated and require a longer time to make a decision than the Level\_0 trigger.

The next level of trigger, HLT-2, reconstructs the VELO information again but uses full momentum information to remove any false secondary vertices that may have been generated by low multiple-scattered momentum tracks. The final level of trigger, HLT-3, uses all the detectors, including both RICH detectors, to reconstruct specific B-hadron decay modes of interest.

To allow time for the trigger decisions to be made, event data are stored using a three-tier hardware storage system. The first tier, Level\_0, stores the detector signals in pipeline memory until the Level\_0 trigger accepts or rejects the data. The Level\_0 trigger latency, defined as the time elapsed between a pp interaction and the time when the trigger signal is received back at the front-end electronics, is chosen to be a constant 4 µs. The data reduction for the Level\_0 is about a factor of ~40. The second tier, Level\_1, stores the accepted data from Level\_0 in a pipeline for a maximum Level\_1 trigger latency<sup>3</sup> of 52.4 ms and gives a further data reduction by a factor of ~25. The Level\_1 trigger latency is defined as the time elapsed between the event data leaving the Level\_0 until the Level\_1 electronics receives back the Level\_1 trigger signal. The third tier stores data in memory on a farm of commodity processors. The total reduction in data is approximately a factor of 200k. The raw event size is approximately 31 kBytes which is stored on disk at a rate of 200 Hz. For more detailed information the reader is referred to [TDRtrig].

Accommodating the latency required for the triggers has a huge impact on the Level\_0 and Level\_1 hardware. For the Level\_0 a large memory requirement leads to a large die size for the custom-made front-end readout chips. This consequently leads to an increase in cost, an increase in complexity of the readout control logic, and introduces stringent timing issues with regards to storage, retrieval and synchronisation. The Level\_1 incurs much the same problems as the Level\_0 but has further demands on real estate as commercial components are employed.

<sup>&</sup>lt;sup>3</sup> This number has yet to be frozen.

These requirements, particularly readout time and synchronisation, require an LHCb global electronics scheme. This scheme is discussed further in the following section.

#### 1.3 LHCb Global Electronic Scheme

The LHCb experiment consists of several sub-detectors with ~one million electronic channels. Table 1-1 shows the sub-detector technology and the number of channels to be read out from each.

| Sub-detector    | Technology                             | # of Channels |

|-----------------|----------------------------------------|---------------|

| Trigger Tracker | silicon-strip detectors                | 140 k         |

| VELO            | r and phi silicon sensors              | 205 k         |

| Inner Tracker   | silicon-strip detectors                | 130 k         |

| Outer Tracker   | straw tubes                            | 54 k          |

| RICH 1          | HPD readout                            | ~172 k        |

| RICH 2          | HPD readout                            | ~268 k        |

| SPD/PS          | Lead/Scintillator with MAPMT           | 2 x 6 k       |

| ECAL            | Lead/Scintillator with phototube       | 6 k           |

| HCAL            | Iron/scintillating tile with phototube | 1.5 k         |

| Muon            | MWPC                                   | 26 k          |

Table 1-1 LHCb sub-detectors, technology and number of readout channels [SCH02].

For LHCb to work in a seamless and homogeneous way, all sub-detectors need to be completely synchronised to the beam crossing from data capture to data readout. This is of considerable importance for the Level\_0/Level\_1 triggers to ensure that the correct event data are extracted. In order to have event data alignment across the sub-detectors, global specifications have been determined. These include the maximum sample time for the analogue detector signals, maximum allowable trigger rates, derandomiser buffer lengths (described later) and event readout times. Not only do these global specifications ensure event data alignment, they also lead to common solutions such as common readout chips and interface modules. An example of a common module would be the Timing Trigger Control receiver (TTCrx) described in section 1.3.1. Common solutions make the experiment more predictable and minimize the resources and manpower needed during the development and testing phase.

This section briefly describes some of the global electronic specifications and components that are important to this thesis. The reader should refer to [CHR01\_L0], [CHR01\_L1] and [CHR\_E] for a comprehensive coverage of this subject matter.

#### 1.3.1 General scheme and specifications

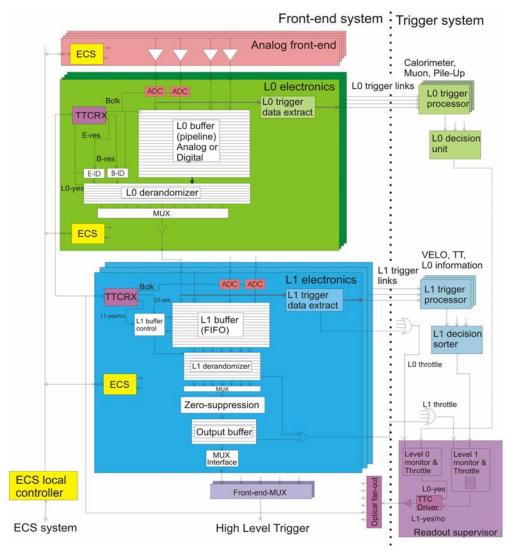

The general readout scheme for all LHCb sub-detectors is illustrated in Figure 1-10. The Level\_0 region, which includes the front-end amplifiers, is physically on the detector. This is a harsh environment in terms of radiation and electronic noise. The Level\_1 is in a radiation-free

Figure 1-10 The General LHCb electronic readout scheme for Level\_0 and Level\_1 [TDRtrig].

environment. The TTCrx and Experimental Control System (ECS) blocks in Figure 1-10 are common to both the Level\_0 and Level\_1 regions. The event data are stored in the pipeline memories for the latency periods while the derandomisers are temporary storage areas for event data being read out. The following sections describe the Readout Supervisor (RS), ECS, TTCrx, Level\_0 and Level\_1 electronics.

#### Readout Supervisor

The RS monitors and controls all data read out from the entire experiment. It receives decisions from the trigger system and drives the Timing Trigger Control (TTC) system. The TTC is the name given to the system that encompasses all the sub-modules needed to distribute the timing, trigger and control signals over the experiment. The TTCrx is one such sub-module. In the case of a possible Level\_0 or Level\_1 buffer overflow the RS will throttle back the data-flow by vetoing Level\_1 and Level\_0 trigger accepts. In normal operation one RS services all sub-detectors, however, each sub-detector has its own RS to allow for stand-alone calibration and debugging. To synchronize the TTC to the LHC machine, the RS uses the LHC machine synchronization signal, which has a fixed delay with respect to the bunch crossing. To be able to compensate for this delay and any delays contributed by the TTC system, the readout supervisor is capable of adding a coarse delay (in steps of ~100 ns) up to one complete LHC machine cycle period.

#### **Experimental Control System**

The ECS is responsible for the slow control parameters such as temperature monitoring, system configuration and power supply monitoring. Transmission errors detected by the Level\_0 and Level\_1 electronics are also sent to the ECS for notification. The ECS interfaces to the different parts of the experiment via JTAG or I<sup>2</sup>C. JTAG is the Joint Test Advisory Group, which in 1998 developed the JTAG testability bus specification. This can be used for communicating with or configuring logic and has the IEEE standard 1149.1 [JTAG]. I<sup>2</sup>C is also a standard for configuring and communicating but has a different protocol [PHI95].

#### **TTCrx**

The TTCrx is an Application Specific Integrated Circuit (ASIC) designed by the CERN EP Microelectronics group and fabricated in the DMILL process (see section 3.1.1). It regenerates the 40 MHz machine bunch clock, receives, decodes and executes any individual or broadcast commands that have originated from the RS, which include the triggers and resets.

The TTCrx has been designed to deliver only one level of triggering, whereas LHCb requires both a Level\_0 and a Level\_1 trigger. To circumvent this problem the Level\_0 trigger and the Bunch ID (BID), which is used for data tagging, are transmitted on a data channel designed for this purpose; known as 'channel-A'. However, the Level\_1 trigger is distributed on a second data channel, 'channel-B', which was intended for only broadcast commands; this limits the rate at which a Level\_1 trigger can be sent. The 8-bit broadcast command has a reduced bandwidth of one command every 16-clock cycles and can only deliver the two least significant bits of the BID. This requires that the 12-bit BID number is generated locally on the Level\_1 electronics and checked against the 2-bits from the TTCrx. Using the TTCrx in this way effects when and how often other broadcast commands can be sent. Both the Level\_0 and Level\_1 electronics need to be designed around this constraint.

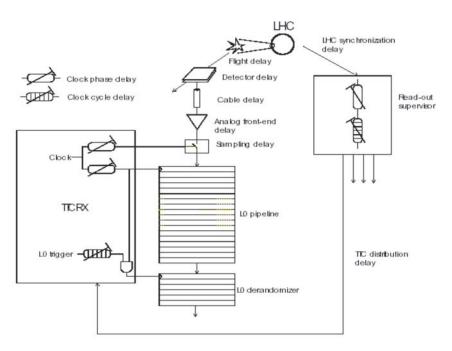

Figure 1-11 Bunch crossing synchronisation of the front end electronics [CHR01\_L0]

Three clocks are offered by the TTCrx: CLK40, CLK-des1 and CLK-des-2. CLK40 is phase-aligned with the machine clock. Clocks des1 and des2 are skewing clocks that can be independently phase-adjusted up to 25 ns in 100 ps steps. This is for either aligning the Level\_0 electronics to the detector, or aligning the Level\_1 to Level\_0 electronics. To extend the dynamic range of the fine clocks, the TTCrx offers an additional course delay of up to 15 bunch clocks on synchronous TTC signals such as the L0 trigger, resets and short broadcast commands. The total allowable local skewing is 400 ns. Figure 1-11 shows an example how the TTCrx can be utilised within the Level\_0. In the case of MAPMTs, described in the next chapter, each TTCrx in the instrumentation system would need to be independently adjusted to ensure correct sampling times.

#### Level\_0 region.

The analogue detector signals must be amplified and stored in either a digital or analogue pipeline memory at a bunch-crossing rate of 40 MHz. The raw signals from the detector element must be fully captured within the bunch-crossing period of 25 ns to ensure event synchronisation is maintained across the detector. The length of the pipeline must be large enough to allow 4 µs to elapse between the bunch crossing and the arrival of the Level\_0 trigger signal at the front-end electronics. This includes time-of-flight, cable delays, and 2 µs for the processing of the data in the Level\_0 trigger hardware. On the arrival of a Level\_0 accept/reject trigger signal every 25 ns, the event data should be overwritten on a reject, or moved into a derandomiser buffer for subsequent readout on an accept.

| Parameter                       | Value             |

|---------------------------------|-------------------|

| Bunch Crossing Frequency        | 40 MHz            |

| Max trigger rate                | 1.1 MHz           |

| Average trigger rate            | 1 MHz             |

| Latency                         | 4 μs (160 events) |

| Max consecutive trigger accepts | 16                |

| Derandomiser depth              | 16 events         |

| Derandomiser readout time       | 900 ns            |

Table 1-2 General requirements of the Level 0 electronics.

The necessary depth of the derandomiser buffer is calculated from the average Level\_0 trigger accept rate of 1 MHz and a readout speed that will maintain a maximum allowable event loss of less than 1 %. A derandomiser depth of 16 with an event-packet<sup>4</sup> readout speed from the derandomiser to Level\_1 electronics of 900 ns was chosen. This requirement was determined from simulations with parameters being varied [CHR\_s]. The 900 ns readout time allows 36 words<sup>5</sup> in an event-packet to be read out at 40 MHz (36x25 ns =900 ns). Four of these words are required for transmission overheads, to be utilised by the user, such as an event number. Therefore 32-words have been allocated for event data. With these derandomiser specifications, a 10 % faster readout compared to the write of the memory is achieved, which results in a simulated 0.5 % event loss. Consecutive Level\_0 accepts are allowed until the derandomiser buffer is full. To ensure against buffer overflow the RS emulates the Level\_0 derandomiser and throttles the Level\_0 accept rate when necessary. The TTCrx distributes the Level\_0 trigger decision to the front-end electronics, along with an associated BID, which is concatenated to the event data via the available user bits. The strict synchronicity between subdetectors for data transmitted from the Level\_0 region is made less critical by the BID identification. Table 1-2 summarises some of the Level\_0 specifications.

.

<sup>&</sup>lt;sup>4</sup> The term 'event-packet' in this context is used to describe a block of data that has the event data plus transmission information.

<sup>&</sup>lt;sup>5</sup> A word is a set of parallel bits that are treated, stored and transported as a unit. In most cases a word is 16 or 32 bits wide.

#### Level\_1 region.

The purpose of the Level\_1 electronics is to store event-packets accepted from Level\_0 and to either discard them on a Level\_1 trigger reject or to transport them to an event building network on an accept. The Level\_1 global specifications are based on using Quad Data Rate (QDR) or Double Data Rate (DDR) Random Access Memory (RAM) for the data storage regions [CHR01\_L1]. Table 1-3 gives the general specifications for the Level\_1 electronics.

Event-packets, which are 36 data words in length, are written to the Level\_1 buffer at an average rate of 1 MHz and a maximum rate of 1.1 MHz. The data rate is 25 ns per word. The event-packets are stored for a variable latency of up to ~52.4 ms while waiting for a Level\_1 accept or reject trigger signal. The average Level\_1 accept rate is 40 kHz. As the buffer size is still under consideration, provision must be made in hardware to increase this by up to a factor of 2 if necessary. The time between triggers is a compromise between slow Level\_1 readout speeds to reduce bandwidth requirements, and the need to keep the memory from filling. This is achieved by issuing the reject signal at the maximum rate possible, which is limited by the TTCrx speed to 400 ns, and the accept rate at a feasibly slow rate of 20 μs. The time between an accept and a following reject signal is 900 ns and whilst not optimal, is needed to keep compatibility to electronics already built on an earlier specification.

| Parameter                                 | Value                   |

|-------------------------------------------|-------------------------|

| Time between two consecutive rejects      | 400 ns                  |

| Time between accept and subsequent reject | 900 ns                  |

| Time between accept and subsequent accept | 20 μs                   |

| Buffer size <sup>6</sup>                  | 58254 events (~52.4 ms) |

| Max buffer input rate                     | 900 ns                  |

| Average trigger accept rate               | 40 kHz                  |

| Max buffer output rate (accept)           | 900 ns                  |

| Derandomiser buffer size                  | 448 events              |

Table 1-3 General requirements of the Level\_1 electronics.

<sup>&</sup>lt;sup>6</sup> The Level\_1 buffer described in chapter 6 has been designed for the predecessor buffer size of 1820 events. The decision to increase to 58254 event storage was made around August 2003.

At present the trigger signals being sent by the RS, via the TTCrx, arrive in the same order that the events are stored in the Level\_1 buffer. This makes the Level\_1 memory controller quite simple to implement as the address generation is always sequential. As this scheme makes use of QDR and DDR RAM that can have their memory location directly accessed, there is a proposal to send the BID with the Level\_1 trigger accept signal. This will alleviate the requirement of the RS only being allowed to send the trigger signals in a sequential manner, as the Level\_1 can make use of the BID to directly locate the correct event. This greatly simplifies the algorithms needed for the trigger and RS. Further to this, trigger rejects no longer need be sent, as the RS will ensure that any accepted event has been read out before the write pointer overwrites the memory contents.

Like the Level\_0, the Level\_1 has to interface to the TTC and ECS system. Unlike the Level\_0, it also interfaces directly to the RS. The Level\_1 checks the validity of the stored data and notifies the ECS system if there are data errors.

#### 1.4 Summary

In this chapter the LHCb detector, sub-detectors, global electronic scheme and triggering system have been introduced. It gives a description of the role in which the RICH plays within LHCb and sets out the electronics readout requirements. Two photo-detector technologies have been considered for the RICH detectors; both the MAPMT and HPD detectors are sampled at 40 MHz into a 4 µs memory and read out at an average Level\_0 trigger accept rate of 1 MHz into the Level\_1 region. The Level\_1 region stores these data while awaiting the Level\_1 accept trigger at an average rate of 40 kHz. The sampling clock, experiment synchronisation, triggers and fast control are utilised via the TTC. The slow control is implemented using the ECS. Both the MAPMT and HPD detectors require specialised radiation hard ASIC chips that can capture and store the signals, while being fully compatible to the global electronics of LHCb.

## Chapter 2

# The Multi-Anode Photo-Multiplier Tube

As described previously in Chapter 1, Cherenkov rings in the RICH detectors typically consist of between 5-30 photons, dependent on radiator, emitted from tracks with a particle velocity,  $\beta \cong 1$ . These photons are detected with wavelengths in the visible and near ultraviolet range. To reconstruct the ring for particle identification requires a photo-detector that has good quantum efficiency (~20-25 %), a wide spectral range and the required spatial detection resolution of ~2 mm<sup>2</sup>. The Multi-Anode Photo-Multiplier Tube (MAPMT) is a suitable candidate for this application.

This chapter describes the work undertaken by the author to characterise the R5900-00-M64 H7546B MAPMT from Hamamatsu. A brief description of the principle of operation and available tube types is followed by the test scheme. Finally, the tube is characterised with respect to gain, pixel-to-pixel gain uniformity, tube efficiency and pulse-height spectrum.

### 2.1 Principle of operation

Figure 2-1 shows a schematic and photograph of the Hamamatsu M64 8x8 MAPMT. The principle of operation of a PMT is that photons are detected through the following processes:

- a) The photon passes through the entrance window. The window material is chosen for its spectral response and its matching to the photo-cathode material. Borosilicate glass is the most common for responses above the 300 nm wavelength range, having a thermal coefficient very close to that of the Kovar alloy used for the leads of the photo-multiplier tube [MAP97].

- b) At the photo-cathode the photon excites a photo-electron that is emitted into the vacuum of the tube (photoelectric effect). Most photo-cathodes are made of a compound semiconductor consisting of alkali metals with a low work function, which is vaporised onto the inside of the entrance window. A common photo-cathode is the bialkali, which uses a combination of two alkali metals [MAP98].

c) Photo-electrons are accelerated and electrostatically focussed onto the first dynode (electrode), where they are multiplied by means of secondary electron emission. Beyond this is arranged a series of dynodes at progressively increasing voltages e.g. +100 V, +200 V. These are coated with a good secondary emitter (BeO) or (Mg-O-Cs), which yields 2-5 electrons when struck by an electron with energy over 100 eV. Hence an electron is accelerated to the first dynode where it liberates electrons, which are accelerated to the second dynode, and so on until reaching the anode. An amplification of 10<sup>6</sup> is readily obtainable, with a 5 ns pulse length. Ideally, the current amplification of a photo-multiplier tube having n dynode stages and an average secondary emission ratio of S per stage will be S<sup>n</sup>. There are a variety of dynode structures available, for example venetian-blind and circular cage. Each type exhibits different current amplification, time response, gain uniformity and secondary collection efficiency. The MAPMT has a square array of PMT structures, which allows pixallation of photon hits.

Figure 2-1 A schematic and photograph of a Hamamatsu M64 MAPMT.

# 2.2 The M64 MAPMT family

The photo-multiplier tubes considered for the LHCb RICH detectors are all from the Hamamatsu M64 family. Depending on the tube type, each stage has either 12 or 8 dynodes of bialkali on stainless steel [MAP97]. Photo-electrons are electrostatically focussed onto an array of 8 x 8 venetian-blind dynode stages. This gives 64 pixels each with a  $\sim$ 2 mm² detection area, where each pixel has its own anode pin. The study of the tubes first began in 1997 with an R5900-00-M64 H7546B, which is a standard Hamamatsu production tube<sup>7</sup>. In 1998 the tube was tested in the CERN SPS beam [ALB01]. The physical dimensions of the tube are  $\sim$  30 mm² x 20 mm, front area and depth respectively, which includes a 1 mm metal flange around the circumference. The entrance window is  $\sim$  800  $\mu$ m thick borosilicate glass with an 18.1 mm² bialkali photo-cathode that has a peak wavelength response of 420 nm. It is a 12 dynode device.

In 1998 Hamamatsu accepted a request from LHCb for the 1 mm metal flange to be removed to improve the active area of the tube by 14 % and the borosilicate window to be replaced with a UV-glass that is transparent up to wavelengths of 180 nm, hence improving the spectral range by 50 %. This tube is the 12 dynode R7600-03-M64, with serial numbers 9Cxxxx<sup>8</sup>; R7600 for no rim, 03 for the window type and M64 is the number of pixels. This tube was tested in the X7 beam at the CERN SPS, [ALB02]. Inefficiencies between pixels led to a further tube, R5900-03-M64<sup>9</sup>, with serial numbers 9Kxxxx. The modification was made to the physical layout of the 8 x 8 venetian-blind, improving on the homogeneity of the electrical field between cathode and blind. In 2002 the R7600-03-M64MOD, serial number GAxxxx, became available with an 8-dynode structure, R7600 body, UV-window (03) and with the 9K focussing. The 8-dynode chain gives a single-photon response of ~50,000 electrons at an HT of ~ -800 V. This relatively low gain makes the tube compatible with some of the silicon-sensor readout chips developed within LHCb, allowing the use of an existing readout chip rather than an in-house customised design.

<sup>&</sup>lt;sup>7</sup> Characteristics of this tube can be found on the Hamamatsu www site [HAM\_www].

<sup>&</sup>lt;sup>8</sup> The 9C is common to all these tubes, the xxxx is an incremental number per tube.

<sup>&</sup>lt;sup>9</sup> These were prototype tubes given by Hamamatsu and have the standard flange.

## 2.3 The MAPMT test set-up

The author designed and commissioned a test set-up and evaluated the Hamamatsu R5900-00-M64 MAPMT. With a bias voltage of -1000 V the gain of the tube is about  $1 \times 10^6$ . Output signals typically have rise-times of 1.5 ns with 5 ns duration. For a single photo-electron with charge  $1.6 \times 10^{-19}$  C, a 2 mV signal would be expected at the load (the base is designed to match  $50~\Omega$ ). The MAPMT has a quantum efficiency of ~20 %, and the gaps between pixels are  $300~\mu m$  ([HAM\_www] data sheet). The gain can vary between pixels by a factor of 5 [MAP97]. However this does not follow a normal distribution, and the large gain variation is dominated by a few 'bad' pixels, typically 5 % of the tube.

In order to make a reasonable assessment of the tube parameters and to ensure the suitability of the tube for the LHCb RICH application, photons from a light spot of 420 nm wavelength and 47  $\mu$ m in diameter were scanned across the surface of the tube in 100  $\mu$ m steps. The following subsections give details of the set-up required to deliver the light source to the tube, move the light source, and read out the 64 channels of the MAPMT.

## Mechanical housing and mounting

In order to protect the MAPMT from extraneous light, a dark box housing of 0.75x0.4x0.16 m (length, width, height) has been constructed, shown in Figure 2-2. The various components are labelled in the figure:

- 1) An optical x, y, z stage with 200 nm spatial resolution.

- 2) A large fixed platform for lens mounting.

- A blue LED.

- 4) A x10 objective lens.

- 5) A x20 objective lens.

- 6) An FC-type receptacle to accept the fibre.

- 7) A monomode fibre.

Figure 2-2 The MAPMT scanning facility.

The monomode fibre has a core diameter of 3.5  $\mu$ m, a cladding diameter of 125  $\mu$ m and a numerical aperture (NA) of 0.11. It has a 3 mm diameter graded index lens on its end with focal length of 25 mm. All feed-through connectors are electrically isolated from the box by nylon washers to reduce ground loops. Anodes 1 to 64 of the MAPMT are read out via individual coaxial cables with LEMO connectors, which have a common ground point on the tube. The MAPMT is supported and clamped using a silicon resin bonded fibre (SRBF) block. This is used for its insulation properties since the inner case of the MAPMT is held at bias potential. In this way the anode on the back of the entrance window is at the same potential as the case and therefore prevents leakage current between the two. Foam inserts between the MAPMT and SRBF are used to prevent damage to the tube.

Eight of the anode signals are simultaneously read out into a 16-channel NIMS amplifier, model 776, giving a gain of 100. The amplified signals are fed to a 12-channel CAMAC ADC, model 2249a, via AC coupling capacitors. The capacitors are necessary to remove the DC offsets of the amplifiers.

## Light source/coupling and stages for the scan

The peak wavelength response of the MAPMT is 420 nm (blue light). It would have been advantageous to use coherent light of the type produced by a laser, suitable for coupling to monomode fibres<sup>10</sup>. This could be focussed to a much smaller spot than incoherent light produced by an LED. Unfortunately blue lasers are not readily available and are expensive, so a blue 470 nm LED was used. This has a maximum luminosity of 1000 milli-candela and a view angle of 15 degrees, switched at 10 kHz with pulse duration of 15 ns. The short duration was required so that the ADC gate width could be minimised to reduce capture of MAPMT dark counts and system noise.

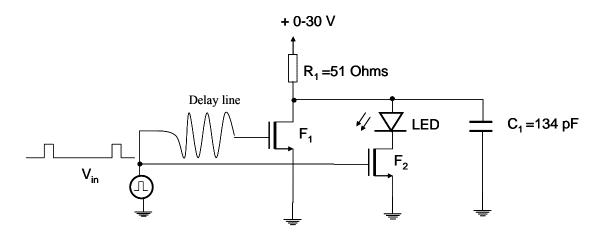

An electronic circuit was constructed so the LED could be pulsed rapidly and is shown in Figure 2-3. The principle of operation is as follows. First the 134 pF capacitor,  $C_1$ , charges with a slow RC time constant. Once fully charged, a short square input signal is pulsed at the input of the two FETs. The FET  $F_2$  connected to the LED anode switches 'on' and  $C_1$  quickly discharges through the LED, causing a burst of light. Due to the delay line  $F_1$  switches 'on' a small time after  $F_2$ , and abruptly turns the LED 'off' again. The resistor  $R_1$  is used to limit the current through  $F_1$  when it is switched 'on'.

Figure 2-3 Basic FET circuit for the LED pulse.

29

<sup>10</sup> A mono-mode fibre is a fibre that only has one acceptable ray-path for the frequency of the light. A multi-mode fibre has a number of possible rays that light of a particular frequency may take.

To deliver the LED light pulse to the MAPMT, a monomode fibre was used for two reasons. Firstly, to restrict the pulse to a narrow light spectrum with a spot-size conforming to a Gaussian distribution, and secondly, to minimise the spot-size from the end of the fibre. This is explained in the following section.

#### Monomode fibre and the light spot-size

Referring to Figure 2-2, the first step in coupling an LED to a monomode fibre is to use an objective lens to form a parallel beam. This proved difficult as the LED has its own encapsulated lens and is an incoherent light source. The parallel beam is therefore focussed through a second objective lens to a spot-size that matches the fibre. A local x, y, z stage is used to align the fibre with the focussed light spot. In practice the spot was ~1 mm in diameter.

A light wave entering the fibre is either refracted into the cladding and attenuated, or is totally internally reflected at the core/cladding boundary. In this manner it travels along the length of the fibre. There are actually only certain 'allowed' incident angles,  $\theta_{accept}$ , that will allow light to propagate through the fibre and these define the modes of the waveguide. The number of modes in a given waveguide depends on the optical frequency being transmitted and can be estimated from the normalised frequency or V-number, defined as  $V=[2\pi \, r_{core}/\lambda] \sin\theta_{accept}$ , where  $r_{core}$  is the fibre radius and  $\lambda$  is the wavelength of the light. For  $V \leq 2.405$  the fibre is termed a monomode [HAW89]. The larger the value of the sine of the acceptance angle, defined as the numerical aperture (NA), the larger the cone of light which can be coupled into the fibre and the more the light exiting the fibre will spread out. The fibre used for this project has NA=0.11.

It is possible to deliver the light to the face of the MAPMT by placing the end of the fibre as close to the borosilicate glass window as possible. However this involves having an air gap between the fibre and MAPMT face so that the fibre can be moved across the face during a scan. Due to this air gap and the  $800 \mu m$  thick window, the light spot will have spread to a diameter of  $\sim 200 \mu m$  before its incidence on the photo-cathode. Since the  $300 \mu m$  gap between MAPMT pixels has to be accurately mapped, a more acceptable light spot diameter must be

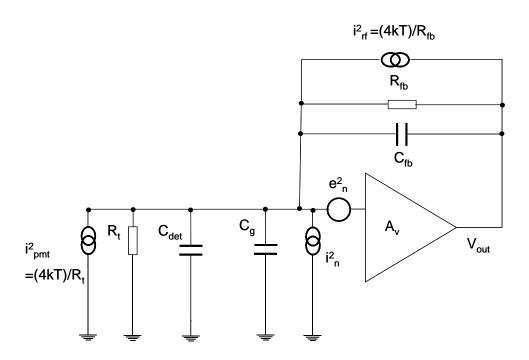

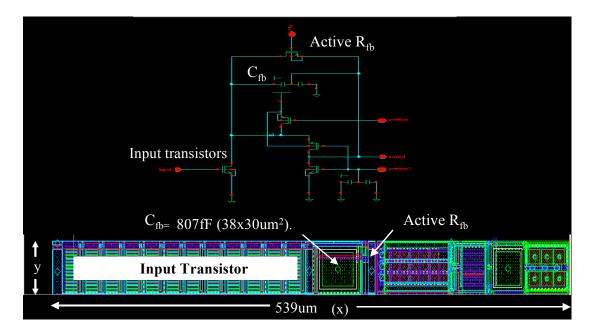

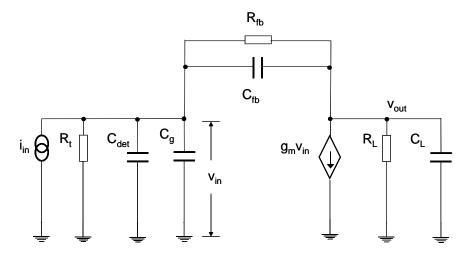

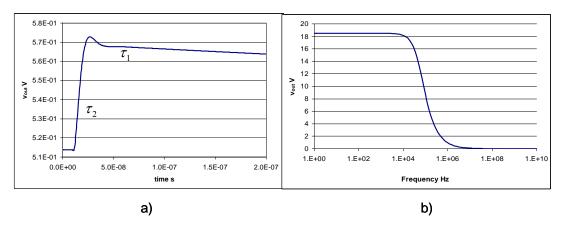

constructed. Therefore a graded index lens with a confocal parameter<sup>11</sup> of  $\sqrt{2}/0.8$  mm and a 25 mm focal length is mounted on the end of the monomode fibre.