# Informatikpraktikum: Vermessung des Transistor Missmatches eines 65 nm Stromspiegels und Testen von 65 nm SRAM-Speicherzellen

### Jakob Kunz

Abstract: In diesem Praktikum ging es darum, aufbauend auf einem früherern Praktikum, eine Messmethode auf ein neues Chipdesign anzupassen und so einen Digital-Analog-Wandler in 65 nm Technologie zu vermessen.

Anschließend wurde ein Messaufbau entwickelt, um SRAM-Speicherzellen, die in 65 nm Technologie gefertigt wurden, auf ihre Spannungsabhängigkeit und ihr Zeitverhalten hin zu untersuchen.

Betreuer: Dr. Johannes Schemmel, Matthias Hock

# Inhaltsverzeichnis

| 1  | Zweidimensionales Transistor-Array |                                                                                |    |  |

|----|------------------------------------|--------------------------------------------------------------------------------|----|--|

|    | 1.1                                | Bisherige Messungen und Ziel der neuen Messungen                               | 1  |  |

|    | 1.2                                | Untersuchung des Missmatches in zwei Dimensionen                               |    |  |

| 2  | $\mathbf{SR}$                      | $\mathbf{A}\mathbf{M}$                                                         | 7  |  |

|    | 2.1                                | Versuchsaufbau                                                                 | 7  |  |

|    | 2.2                                | Ansteuerung des AWGs mithilfe des Computers                                    | 8  |  |

|    | 2.3                                | Untersuchung des Spannungs- und Zeitverhaltens                                 |    |  |

|    |                                    | 2.3.1 Messung bei Raumtemperatur                                               | 8  |  |

|    |                                    | 2.3.2 Messung bei 50°C                                                         | 9  |  |

|    | 2.4                                | Test der SRAM-Speicherzellen bei kurzzeitig abgeschalteter Versorgungsspannung | 10 |  |

| Li | iterat                             | turverzeichnis                                                                 | 11 |  |

### 1 Zweidimensionales Transistor-Array

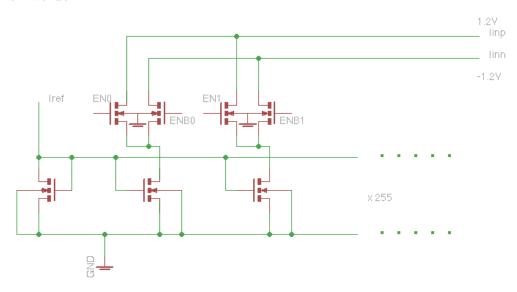

Um digitale Signale in analoge umzuwandeln, bedarf es eines sogenannten DACs (digital-to-analog converter). Eine Möglichkeit einen Strom-DAC zu bauen besteht in der Verwendung von Stromspiegeln, für deren korrekte Funktionalität es wichtig ist, dass das Missmatch, also der fertigungsbedingte Unterschied benachbarter Transistoren, möglichst gering ist. Im ersten Teil dieses Praktikum wurde genau dieses Missmatch an einer Transistor-Schaltung getestet, deren Aufbau an einen current-steering DAC angelehnt ist. Der prinzipielle Aufbau kann Abbildung 1 entnommen werden.

Abbildung 1: Aufbau der Stromspiegel-Schaltung auf dem Test-Chip ([1]).

### 1.1 Bisherige Messungen und Ziel der neuen Messungen

Diesem Praktikum voran ging ein Praktikum von C. Graf [1], in dem bereits Messungen an einem Digital-Analog-Wandler durchgeführt wurden. Dabei ging es darum, das Missmatch der Transistoren zu untersuchen, das möglichst gering sein sollte. In der Arbeit von C. Graf wurde eine periodische Korrelation der Transistoren mit einer Periodizität von 16 Nachbar-Nachbar-Abständen der Transistoren festgestellt.

In diesem Praktikum sollte es in einem ersten Schritt darum gehen, diese Periodizität näher zu untersuchen. Aufgrund des Aufbaus des Arrays (siehe [1]) liegt die einzig offensichtlich mögliche Ursache für eine periodische Abhängigkeit der Korrelation verschiedener Transistoren aus dem Stromspiegel in den Referenz-Transistoren, die alle acht Transistoren auftreten und den Strom spiegeln. Allerdings würde man eher eine Periodizität von 8 Nachbar-Nachbar-Abständen erwarten, als eine Periodizität von 16 Abständen.

Auf dem neuen Chip, der in diesem Praktikum untersucht wurde, wurden deshalb mehrere (auf 128 Transistoren verkürzte) 1-dimensionale Transistor-Arrays nebeneinandergesetzt und so zu einem 2-dimensionalen Array verschaltet.

So ist es möglich, die Periodizität genauer zu untersuchen, da man nun auch quer zu den ursprünglichen 1-dimensionalen Arrays messen kann und so direkt das Missmatch der Referenz-Transistoren untersuchen kann.

### 1.2 Untersuchung des Missmatches in zwei Dimensionen

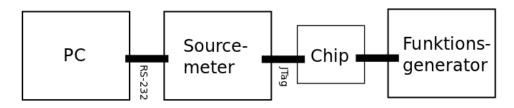

Zunächst wurde ein bestehendes C++-Programm dahingehend erweitert, dass mit dem bestehenden Messaufbau das neue DAC-Array zweidimensional untersucht werden kann. Jeder Transistor auf dem Array hat dabei die Breite 400 nm und die Länge 600 nm. Der Versuchsaufbau kann dabei Abbildung 2 entnommen werden.

Abbildung 2: Versuchsaufbau zur automatisierten Messung des Missmatches der Transistoren in dem Transistor-Array.

Die Messungen wurden aufgrund der deutlich gestiegenen Transistoranzahl im Vergleich zum alten Chip auf Messgeschwindigkeit hin optimiert. Wie sich zeigte, litt die Messgenauigkeit jedoch nicht darunter. Jeder Transistor wurde 20 Mal gemessen. Dabei wurde das Transistor-Array nicht einfach abgerastert, sondern es wurden stets zufällige Transistoren vermessen, wobei trotzdem sichergestellt wurde, dass alle Transistoren gleich oft gemessen wurden. So sollte vermieden werden, dass durch eine bestimmte Messrichtung eine Korrelation der Ergebniswerte zustande kommen könnte.

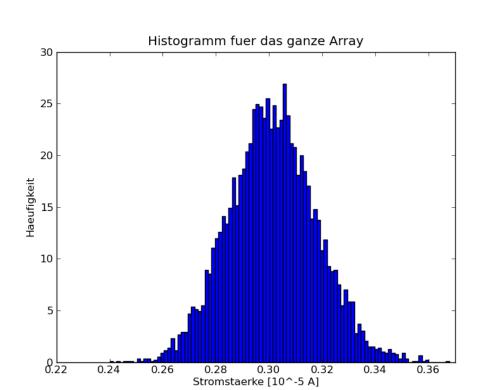

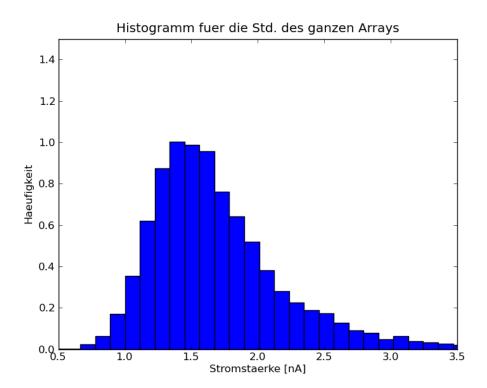

Abbildung 3 kann dabei ein Histogramm aller Messpunkte entnommen werden (exemplarisch wurde hier die Stromstärke von 3  $\mu$ A gewählt). Abbildung 4 beinhaltet die dazugehörige Standardabweichung für jeden Transistor, die sich durch die 20 Messungen ergibt. Aus diesen beiden Abbildungen erkennt man, dass die Messgenauigkeit nicht unter den schnelleren Messeinstellungen gelitten hat.

Abbildung 3: Histogramm für die gemittelte Stromstärke aus 20 Messungen an jeweils einem einzelnen Transistor des Arrays für eine eingestellte Referenzstromstärke von 3  $\mu$ A.

Abbildung 4: Histogramm für die Standardabweichung der gemittelten Stromstärke aus 20 Messungen an jeweils einem einzelnen Transistor des Arrays für eine eingestellte Referenzstromstärke von 3  $\mu$ A.

Über alle Transistoren gemittelt ergaben sich folgende Stomstärkewerte für unterschiedliche eingestellte Stromstärken:

| Eingestellte Stromstärke [A] | Gemittelte Stromstärke [A] | Std. [A]             | Std. der Simulation [A] |

|------------------------------|----------------------------|----------------------|-------------------------|

| $1.00 \cdot 10^{-6}$         | $9.20 \cdot 10^{-7}$       | $7.18\cdot10^{-8}$   | $1.17\cdot 10^{-7}$     |

| $3.00 \cdot 10^{-6}$         | $3.01 \cdot 10^{-6}$       | $1.65 \cdot 10^{-7}$ | $2.42 \cdot 10^{-7}$    |

| $1.20 \cdot 10^{-5}$         | $1.21 \cdot 10^{-5}$       | $3.96 \cdot 10^{-7}$ | $5.18 \cdot 10^{-7}$    |

Tabelle 1: Mittelwerte und deren Standardabweichungen für die Mittelung der Mittelwerte aller Transistoren aus der 20-malige Messungen des Transistor-Arrays bei verschiedenen angelegten Stromstärken. In der rechten Spalte ist zum Vergleich noch die Standardabweichung der Simulation angegeben.

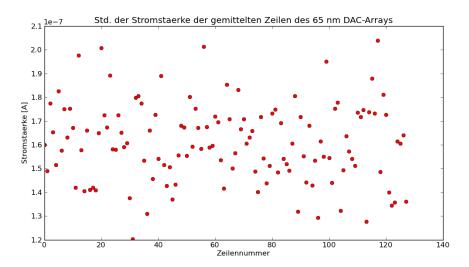

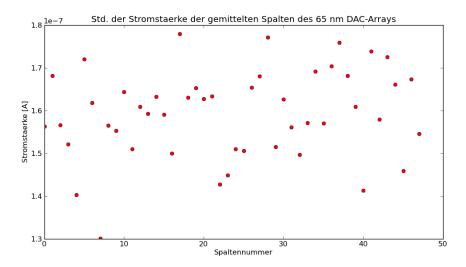

Anschließend wurden einmal über alle Zeilen und einmal über alle Spalten des DAC-Arrays gemittelt, um zu untersuchen, ob es zu auffällig größeren Fehlern an den Randbereichen des DAC-Arrays kommt. Abbildungen 5 und 6 zeigen diese Mittelungen exemplarisch für eine eingestellte Referenzstromstärke von 3  $\mu$ A.

Abbildung 5: Standardabweichung der Mittelung über alle Zeilen des Transistor-Arrays für eine eingestellte Referenzstromstärke von 3  $\mu$ A.

Abbildung 6: Standardabweichung der Mittelung über alle Spalten des Transistor-Arrays für eine eingestellte Referenzstromstärke von 3  $\mu$ A.

Wie aus den Schaubildern hervorgeht, nimmt die Standardabweichung zum Rande des DAC-Arrays nicht signifikant zu.

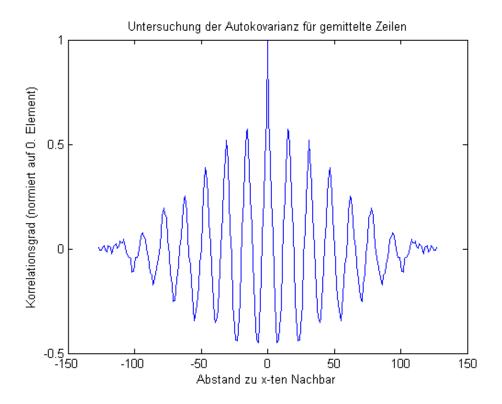

Anschließend wurde die Autokovarianz benachbarter Transistoren sowohl in Zeilen- als auch in Spaltenrichtung untersucht, um herauszufinden, ob eine Korrelation zwischen benachbarten Transistoren besteht. In Spaltenrichtung konnte dabei die von C. Graf gemessene Periodizität von 16 Nachbar-Nachbar-Abständen bestätigt werden (siehe Abbildung 7). Außerdem konnte bestätigt werden, dass die Ausprägung der sinusförmigen Periodizität für höhere Referenzstromstärken stärker ausgeprägt ist.

Abbildung 7: Untersuchung der gemittelten Zeilen des DAC-Arrays auf Autokovarianz für eine eingestellte Referenzstromstärke von 12  $\mu$ A.

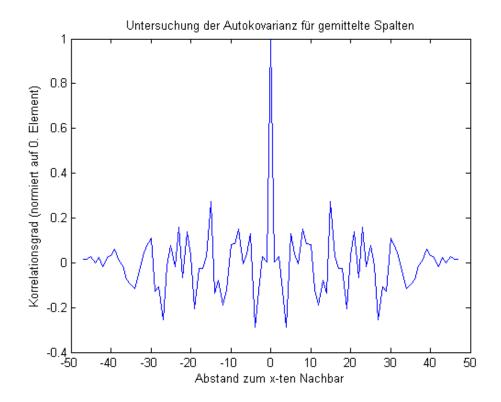

Warum die Periodizität nicht 8 Abstände beträgt, konnte nicht geklärt werden. In Zeilenrichtung hingegen konnte keinerlei Korrelation der einzelnen Transistoren zueinander festgestellt werden (siehe Abbildung 8).

Abbildung 8: Untersuchung der gemittelten Spalten des DAC-Arrays auf Autokovarianz für eine eingestellte Referenzstromstärke von 12  $\mu$ A.

Damit ist klar, dass die Ursache für die Periodizität in Spaltenrichtung auf die Referenz-Transistoren zurückzuführen sein muss, da sonst auch eine Periodizität in Zeilenrichtung hätte beobachtet werden müssen.

### 2 SRAM

### 2.1 Versuchsaufbau

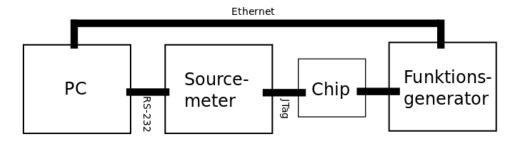

Für die Messungen an den SRAM-Speicherzellen musste der Aufbau so erweitert werden, dass man mithilfe des Messcomputers Frequenzen während der Messung verändern kann. Der genaue Aufbau kann Abbildung 9 entnommen werden.

Abbildung 9: Versuchsaufbau für die Messung des Spannungs- und Zeitverhaltens der SRAM-Speicherzellen

### 2.2 Ansteuerung des AWGs mithilfe des Computers

Um automatisiert und mit ausreichend kurzen Lese- und Schreibzyklen messen zu können, musste der Funktionsgenerator Tektronix AWG 7102 mit dem PC angesteuert werden. Dazu wurde ein C++ Programm geschrieben. Es ist nun einfach möglich, den AWG anzusprechen, indem man die in diesem Praktikum geschriebene Datei "awg.h" in seinen Code einbindet. Ein kleiner exemplarischer Beispielcode zur Verwendung des AWG sieht so aus:

```

#include <iostream>

#include <boost / asio . hpp>

#include "awg.h"

3

4

int main(int argc, char* argv[])

5

6

{

7

using namespace std;

8

AWG FuncGen:

9

FuncGen. RequestSetting ("SOURce1: FREQuency?");

10

FuncGen. SendCommand ("SOURce1: FREQuency_5000MHz");

11

12

13

return 0;

14

}

```

Das Programm erfragt zunächst die eingestellte Sampling-Rate des AWG und setzt sie danach auf 5000 MHz.

### 2.3 Untersuchung des Spannungs- und Zeitverhaltens

### 2.3.1 Messung bei Raumtemperatur

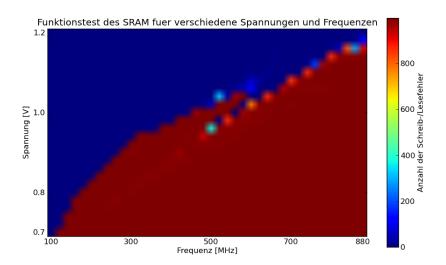

Die SRAM-Speicherzellen wurden bei verschiedenen Versorgungsspannungen und Frequenzen bei Raumtemperatur getestet. Für die Einstellungen des SRAM-Controllers auf dem Chip wurde dabei TR=1, TSU=0, TWR=0 (siehe HICANN-Dokumentation) gewählt, da sich diese Einstellungen aus Vortests als geeignete untere Begrenzung für sinnvolle Messungen am Versuchschip erwiesen hatten.

Die Ergebnisse der Messung können Abbildung 10 entnommen werden.

Abbildung 10: Ergebnis der Messung der SRAM-Zellen bei Raumtemperatur für verschiedene Spannungen und Frequenzen.

Man kann Abbildung 10 entnehmen, dass die Speicherzellen für große Versorgungsspannungen und kleine Frequenzen am besten funktionieren. Für den Betrieb der Speicherzellen sollte man also einen Punkt im blauen Bereich des Schaubildes wählen. Man kann dem Schaubild auch eine gewisse Überstruktur entnehmen, die im Rahmen dieses Praktikums jedoch nicht erklärt werden konnte.

### 2.3.2 Messung bei 50°C

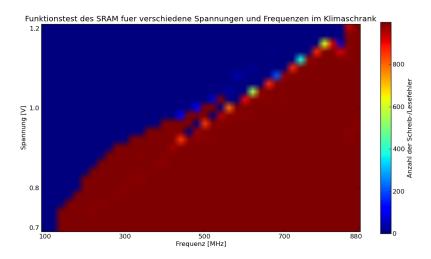

Für eine Messung bei realistischeren Betriebstemperaturen, wurde der Versuchschip in eine Klimakammer eingebracht und es wurde erneut das Spannungs- und Frequenzverhalten der SRAM-Speicherzellen untersucht. Das Ergebnis kann Abbildung 11 entnommen werden.

Abbildung 11: Ergebnis der Messung der SRAM-Zellen bei einer Umgebungstemperatur von 50°C für verschiedene Spannungen und Frequenzen.

Bei 50°C ist der Spannungs-Frequenz-Bereich, in dem die SRAM-Zellen noch funktionieren nicht signifikant von dem Bereich bei Raumtemperatur verschieden.

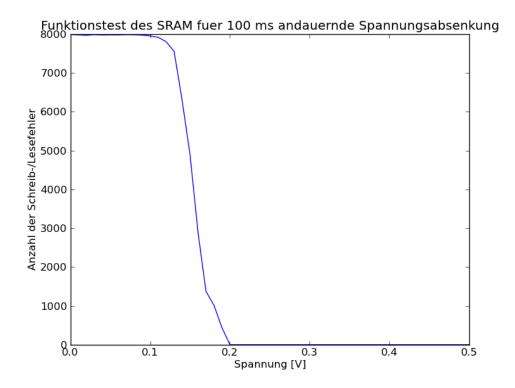

# 2.4 Test der SRAM-Speicherzellen bei kurzzeitig abgeschalteter Versorgungsspannung

Die SRAM-Speicherzellen wurden für diese Tests bei einer Versorgungsspannung von 1.2 V und einer eingestellten Frequenz von 200 MHz voll geschrieben, anschließend wurde die Versorgungsspannung für 100 ms auf verschiedene niedrige Spannungswerte eingestellt. Danach wurde die Versorgungsspannung wieder auf 1.2 V gestellt und die Daten wurden ausgelesen. Dies wurde 1000 Mal pro niedrigem Versorgungsspannungswert wiederholt und es wurden die dabei auftretenden Schreib-/Lesefehler gezählt. Das Ergebnis kann Abbildung 12 entnommen werden.

Abbildung 12: Ergebnis der Messung der SRAM-Zellen mit kurzzeitig abgesenkter Versorgungsspannung.

## Literatur

[1] Christian Graf, Transistor-Mismatch bei einem Strom-DAC in 65nm-Technologie, Projektpraktikum, September 2011