KIRCHHOFF-INSTITUT FÜR PHYSIK

## RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

## Development of Fast Sampling Transient Recorders with Custom ASICs

Inaugural-Dissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

> vorgelegt von Dipl.-Ing. Cristian Ovidiu Chiţu aus Ploieşti Rumänien

> > Mannheim, 2000

Dekan: Referent: Korreferent: Professor Dr. Reinhard Männer, Universität Mannheim Professor Dr. Reinhard Männer, Universität Mannheim Professor Dr. Werner Hofmann, Max-Planck-Institut für Kernphysik Heidelberg

Tag der mündlichen Prüfung: 06. November 2000

## Development of Fast Sampling Transient Recorders with Custom ASICs

A Dissertation Submitted to the Faculty of Mathematics and Computer Science of the University of Mannheim for the Degree of Doktor der Naturwissenschaften (Dr. rer. nat.)

> By Dipl.-Ing. Cristian Ovidiu Chiţu from Ploieşti Romania

> > Mannheim, 2000

# Zusammenfassung

Analoge Speicher aus geschalteten Kapazitäten sind für eine Vielzahl von Anwendungen geeignet, sofern keine fortlaufende Digitalisierung der analogen Signale notwendig ist. In Datennahmesystemen, die auf einem analogen Speicher basieren, werden die Eingangssignale mit hoher Rate abgetastet und für begrenzte Zeit zwischengespeichert. Die analogen Abtastwerte werden dann mit einer geringeren Rate ausgelesen und mit einem langsamen ADC digitalisiert, bevor neue Signale aufgenommen werden. Die Vorteile eines analogen Speichers sind ein geringerer Leistungsverbrauch, geringere Kosten, eine große Dichte und ein höherer dynamischer Bereich bei hohen Abtastraten. Ein analoger Speicher führt die Abtastung und Zwischenspeicherung von Werten mit höheren Raten und grösserer Genauigkeit durch, als dies durch eine direkte digitale Umwandlung bewerkstelligt werden könnte.

Diese Dissertation untersucht detailliert die wichtigen Komponenten zweier analoger Speicher. Die Forschungsarbeit hat zum Entwurf von zwei analogen Speichern geführt, die Analogsignale mit einer Abtastrate von einigen hundert MHz aufnehmen können. Dies wird durch eine Speicherarchitektur bewerkstelligt, in der die Sockelwerte der Speicherzellen und die Abtastzeiten unabhängig vom Signalpegel sind. Die Ansteuerung der Schreibadresse für diese Speicher wurde durch Inverter-Verzögerungsketten realisiert, die eine hohe Güte bezüglich der Abtastrate und der Zeitgenauigkeit gewährleisten.

Auf Grundlage der in dieser Arbeit entwickelten Konzepte wurden zwei analoge Speicher entworfen und in der AMS 0.8  $\mu$ m CMOS Technologie mit Poly-zu-Poly Kapazitäten integriert. Ausgedehnte Messungen dieser Prototypen bei einer Abtastrate von 500 MHz werden dargestellt. Nachdem ein einfaches Multiplikations - und Additionskorrekturverfahren durchgeführt wurde, entspricht der dynamische Bereich, die Linearität, der Offset und die Verstärkung einer Genauigkeit von 8 Bit.

## Abstract

Switched capacitor analog memories are well suited to a number of applications where a continuous digitisation of analog signals is not needed. In data acquisition systems based on the use of an analog memory, the input waveforms are sampled and stored at a high rate for a limited period of time, and the analog samples are then retrieved at a lower rate and digitised with a slow ADC before new waveforms are acquired. The advantages of using an analog memory are lower overall power dissipation and cost, high density, and potentially superior dynamic range at high sampling rates. The analog memory shows the fact that the sampling and storage of samples in analog memory cells can be accomplished at a higher rate and with a greater precision than direct digital conversion.

This dissertation examines the important components of two analog memories in detail. The research has led to the design of two analog memories that can acquire analog waveforms at sampling rates of several hundred MHz. This is accomplished by a memory architecture in which the memory cell pedestals and sampling times are independent of the signal level. The write address control for these memories has been realised with inverter delay chains that provide high performance with respect to sampling rate and timing accuracy.

Based upon the concepts developed in this work, two analog memories were designed and integrated in a AMS 0.8  $\mu$ m CMOS technology with poly-to-poly capacitors. Extensive measurements of these prototypes at a sampling rate of 500 MHz are presented and demonstrate a dynamic range, linearity, offset, and gain accuracy corresponding to a precision of 8 bits after a simple multiplication and addition correction procedure.

## Acknowledgements

This work was supported by the Max-Planck-Institut für Kernphysik in Heidelberg and has been done at ASIC Labor in Heidelberg.

I extend my sincere appreciation to my work supervisor, Prof. Dr. W. Hofmann, which enabled the completion of this research. I am particularly grateful to him for extending to me the freedom in defining and directing my research, and I also appreciate his insightful and constructive help to write with clarity and precision.

I am also indebted to my Ph.D. supervisor, Prof. Dr. R. Männer. I would like to point out his positive attitude to all attractive and perspective ideas born during my work.

Many thanks go to Prof. Dr. N. Fliege for serving on my oral examination committee.

I like to thank my colleagues from ASIC Labor and Cherenkov group of the Max-Planck-Institut für Kernphysik for many valuable discussions and for help during the research.

Also many thanks to my professors from the Faculty of Electronics and Telecommunications of Bucharest, Romania, who offered me a solid basis in electronics, from where I could develop and build further.

Very important for me was the support and love of my parents who were so far away from me.

Finally, I want to give special thanks to my wife, Cristina. Without her support and understanding, this dissertation would not have been possible.

# Contents

| Li       | st of | Tables                             | $\mathbf{v}$ |

|----------|-------|------------------------------------|--------------|

| Li       | st of | Figures                            | <b>ii</b>    |

| 1        | Intr  | oduction                           | 1            |

|          | 1.1   | Motivation                         | 1            |

|          | 1.2   | Outline                            | 2            |

| <b>2</b> | Swi   | tched Capacitor Analog Memory Cell | <b>5</b>     |

|          | 2.1   | Overview                           | 5            |

|          | 2.2   | Analog Memory Architectures        | 5            |

|          | 2.3   | Analog Memory Concept              | 6            |

|          | 2.4   | CMOS Technology                    | 7            |

|          | 2.5   | NMOS Transistor Switch             | 8            |

|          |       | 2.5.1 NMOS Switch Resistance       | 8            |

|          |       | 2.5.2 Error Voltage                | 9            |

|          |       | 2.5.3 Distortion and Timing Errors | 11           |

|          | 2.6   | CMOS Transmission Gate Switch      | 13           |

|          |       | 2.6.1 CMOS Switch Resistance       | 13           |

|          |       | 2.6.2 Error Voltage                | 14           |

|          | 2.7   | Capacitors                         | 18           |

|          | 2.8   | Matching Properties of Memory Cell | 19           |

|          | 2.9   |                                    | 20           |

| 3        | Ana   | log Memory Circuit                 | 23           |

| U        | 3.1   |                                    | 23           |

|          | 3.2   |                                    | 23           |

|          | 3.3   | 1                                  | 24           |

|          |       |                                    | 24           |

|          |       |                                    | 26           |

|          |       | 1                                  | 29           |

|          |       |                                    | 31           |

|          |       | 0 0                                | 32           |

|          |       |                                    | 34           |

|   |               | 3.3.7 Leakage Current                                 | 35         |

|---|---------------|-------------------------------------------------------|------------|

|   | 3.4           | Summary                                               | 35         |

| 4 | Rea           | dout Operational Amplifier                            | 37         |

| _ | 4.1           | Overview                                              | 37         |

|   | 4.2           | Amplifier Circuit                                     | 37         |

|   | 4.3           | Simulation Results                                    | 39         |

|   | 4.4           | Amplifier Noise                                       | 42         |

|   | 4.5           | Summary                                               | 43         |

| 5 | Cor           | ntrol Circuits                                        | 45         |

| Э | 5.1           | Overview                                              | <b>45</b>  |

|   | $5.1 \\ 5.2$  | High Speed Addressing Circuit                         | $45 \\ 45$ |

|   | 0.2           |                                                       | $45 \\ 45$ |

|   |               | 5.2.1 Circuit Description                             | 45<br>48   |

|   | につ            |                                                       | 48<br>48   |

|   | 5.3           | Read Addressing Circuits                              |            |

|   |               | 5.3.1 Read Control Circuit for FASTSAMP-EV chip       | 48         |

|   | F 4           | 5.3.2 Read Control Circuit for FASTSAMP-V1 chip       | 50         |

|   | 5.4           | Summary                                               | 53         |

| 6 | $\mathbf{Me}$ | mory Calibration and Correction Procedures            | 55         |

|   | 6.1           | Introduction                                          | 55         |

|   | 6.2           | DC Calibration                                        | 56         |

|   |               | 6.2.1 Subtraction Method                              | 56         |

|   |               | 6.2.2 Multiplication and Addition Method              | 57         |

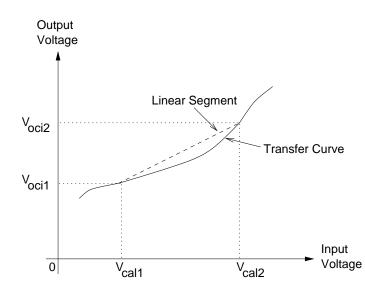

|   |               | 6.2.3 Piece-Wise Linear Approximation Method          | 58         |

|   | 6.3           | AC Calibration                                        | 59         |

|   | 6.4           | Method to Calibrate Signals from Cherenkov Telescopes | 61         |

|   | 6.5           | Summary                                               | 61         |

| 7 | Sim           | ulation and Experimental Results                      | 63         |

|   | 7.1           | Overview                                              | 63         |

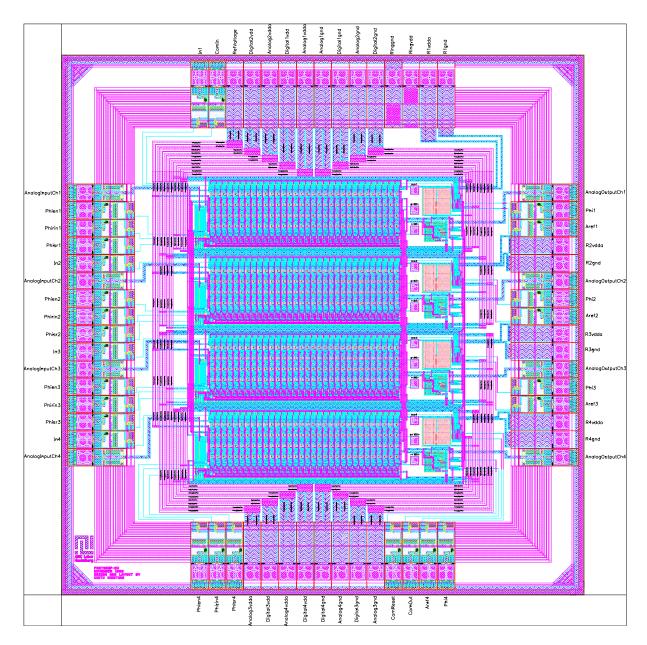

|   | 7.2           | Chips Layout                                          | 63         |

|   | 7.3           | Simulation Results                                    | 68         |

|   | 7.4           | Analog Memory Noise                                   | 69         |

|   | 7.5           | Experimental Results                                  | 71         |

|   |               | 7.5.1 DC Transfer Characteristic                      | 71         |

|   |               | 7.5.2         Dynamic Range                           | 76         |

|   |               | 7.5.3 AC Response                                     | 76         |

|   | 7.6           | Summary                                               | 80         |

| 6 | C             |                                                       | <b>0</b> 1 |

| 8 |               | Conclusions and Suggestions                           | 81<br>01   |

|   | 8.1           | Conclusions                                           | 81         |

|   | 8.2           | Suggestions for Future Work                           | 82         |

#### Contents

| $\mathbf{A}$ | Parameters                                          | 85  |

|--------------|-----------------------------------------------------|-----|

| в            | Analysis of Charge Injection in MOS Analog Switches | 87  |

| $\mathbf{C}$ | FASTSAMP-EV Chip Test Setup                         | 91  |

| D            | FASTSAMP-V1 Chip Test Setup                         | 97  |

| Bi           | bliography                                          | 103 |

# List of Tables

| 3.1                 | Architectures for both chips                         | 24 |

|---------------------|------------------------------------------------------|----|

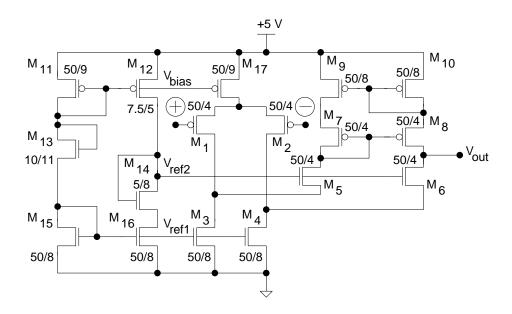

| $4.1 \\ 4.2 \\ 4.3$ | Dc operating points of MOS transistors               | 38 |

| 6.1                 | Calibration and correction parameters                | 59 |

| $7.1 \\ 7.2$        | Calculation and measurement results for both devices |    |

|                     | AMS 0.8 $\mu$ m CMOS Process Parameters [40]         |    |

| C.1                 | Test setup equipment list for FASTSAMP-EV chip       | 92 |

| D.1                 | Test setup equipment list for FASTSAMP-V1 chip.      | 98 |

# List of Figures

| 1.1          | Signal acquisition in an analog memory                                                                                                              | 2  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $2.1 \\ 2.2$ | Simplified representation of an analog memory                                                                                                       | 7  |

|              | technology.                                                                                                                                         | 8  |

| 2.3          | NMOS switch placed in (a) signal and (b) signal return path                                                                                         | 9  |

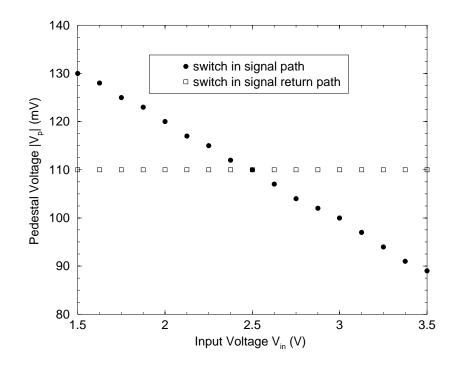

| 2.4          | Pedestal voltage as a function of input voltage for NMOS switch                                                                                     | 10 |

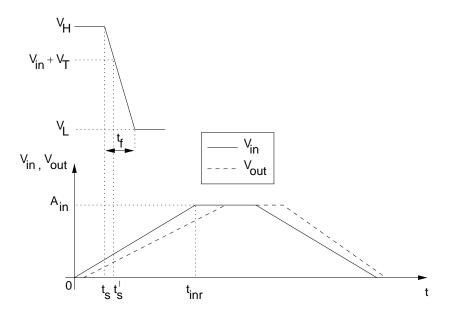

| 2.5          | Timing errors when the sampling switch is placed in signal path                                                                                     | 11 |

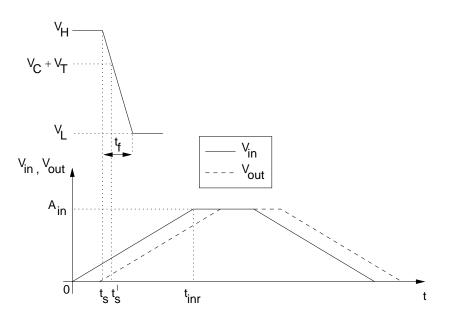

| 2.6          | Timing errors when the sampling switch is placed in signal return path                                                                              | 12 |

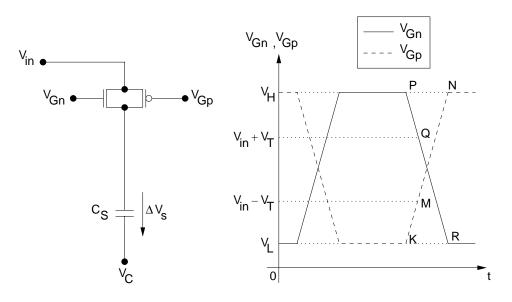

| 2.7          | Schematic of the CMOS switch placed in signal path.                                                                                                 | 14 |

| 2.8          | Schematic of the CMOS switch placed in signal return path                                                                                           | 16 |

| 2.9          | Pedestal voltage as a function of input voltage for CMOS switch                                                                                     | 17 |

| 2.10         | Physical structure of poly-to-poly capacitor.                                                                                                       | 18 |

| 3.1          | Block diagram for (a) FASTSAMP-EV and (b) FASTSAMP-V1 chips                                                                                         | 25 |

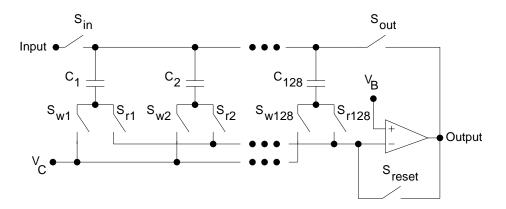

| 3.2          | Memory architecture with one amplifier per channel. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                             | 26 |

| 3.3          | Simplified schematic of one analog memory channel                                                                                                   | 26 |

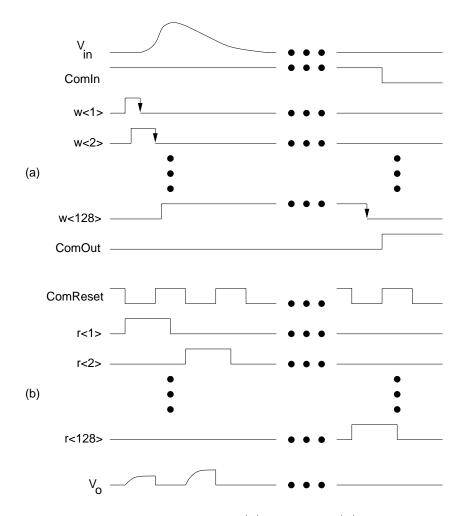

| 3.4          | Timing diagram for (a) write and (b) read phases                                                                                                    | 27 |

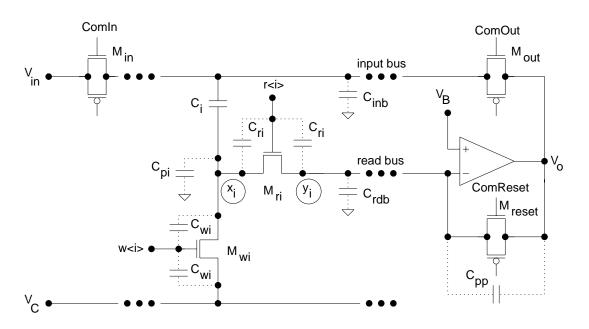

| 3.5          | Analog memory channel with parasitic capacitances                                                                                                   | 28 |

| 3.6          | Circuit configuration before the memory cell is addressed for readout                                                                               | 30 |

| 3.7          | Circuit configuration when the memory cell is addressed for readout. $\ldots$                                                                       | 31 |

| 3.8          | (a) Triangle input waveform. (b) Waveforms at node $x_i$ in Figure 3.5 with                                                                         |    |

|              | the write switch turned off at time $t_1$ (solid line) and $t_2$ (dashed line)                                                                      | 32 |

| 3.9          | Equivalent circuit of a memory cell during signal acquisition                                                                                       | 33 |

| 3.10         | Time response of the analog memory cell to a step input                                                                                             | 34 |

| 4.1          | Schematic of the folded cascode amplifier.                                                                                                          | 38 |

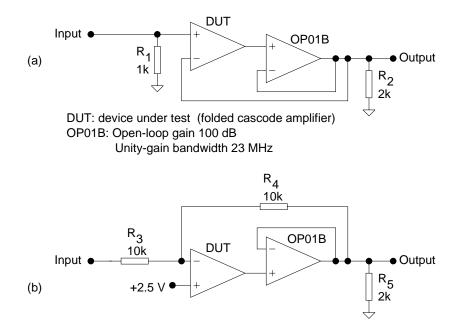

| 4.2          | Amplifier in the (a) voltage follower and (b) inverter configuration. $\ldots$                                                                      | 39 |

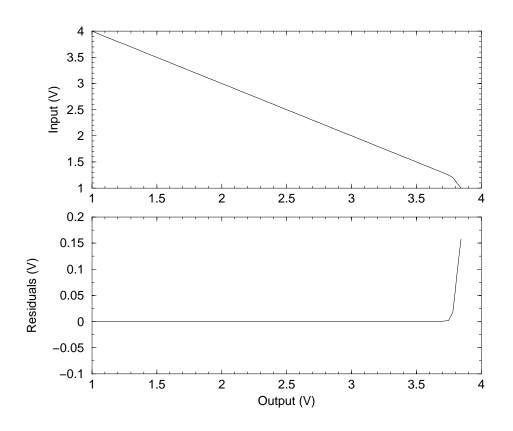

| 4.3          | Upper: Input voltage as a function of output voltage. Lower: Residuals from a fit to a 2.5 V output voltage range. The amplifier is in the inverter |    |

|              | $configuration. \dots \dots$                  | 40 |

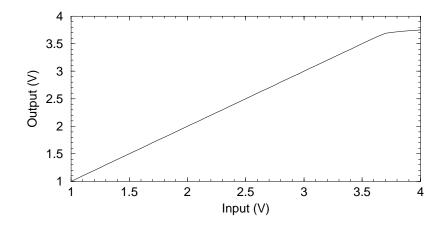

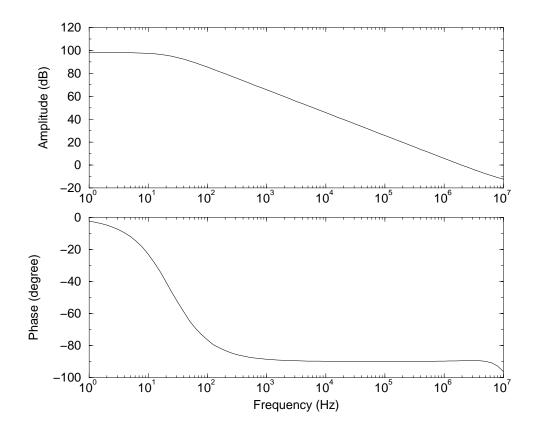

| 4.4          | Output voltage plotted as a function of input voltage. The amplifier is in the follower configuration.                                              | 40 |

| 4.5          | Amplitude (upper) and phase (lower) plotted as a function of frequency.                                                                             | 41 |

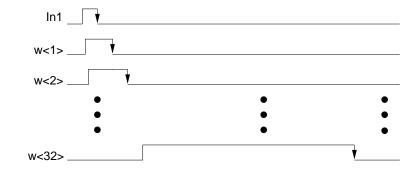

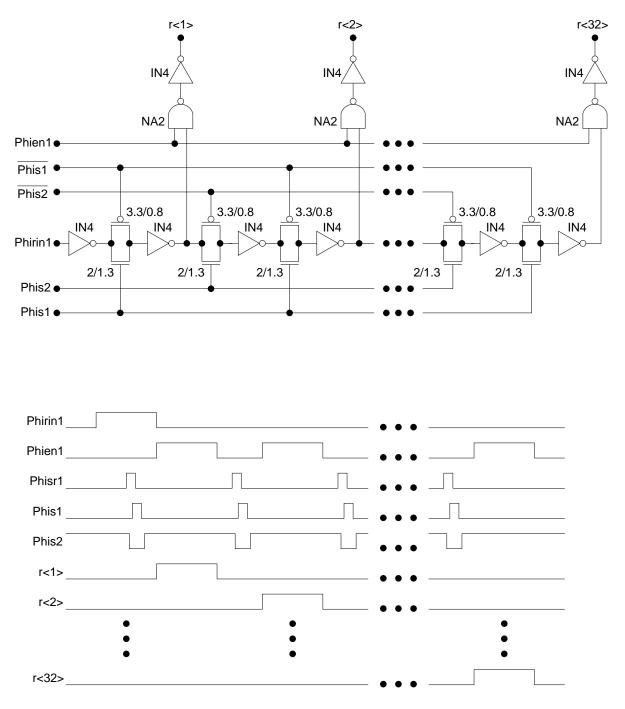

| 5.1                                       | Inverter delay chain of 32 cells and servo feedback circuit                                                                                                                                                                                | 46 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

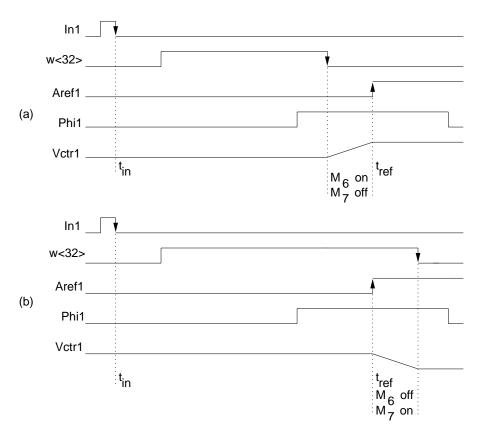

| $5.2 \\ 5.3$                              | Timing diagram of the write signals in one delay chain. $\ldots$ $\ldots$ $\ldots$ Timing diagram of the inverter chain showing the falling edge of the last write signal $w < 32$ > which can be (a) before or (b) after the raising edge | 47 |

|                                           | of the reference pulse $Aref1$                                                                                                                                                                                                             | 47 |

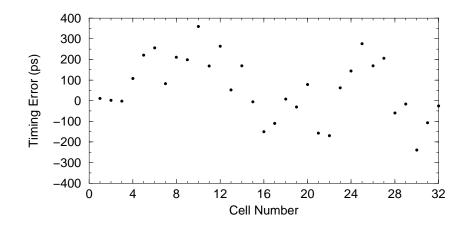

| 5.4                                       | Timing errors after simulations in one delay chain                                                                                                                                                                                         | 48 |

| 5.5                                       | A 32 stage dynamic two-phase shift register with timing diagram                                                                                                                                                                            | 49 |

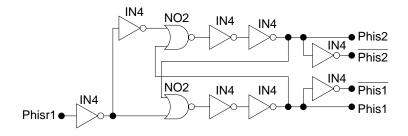

| 5.6                                       | Two-phase clock generator.                                                                                                                                                                                                                 | 50 |

| 5.7                                       | Read control circuitry with timing diagram.                                                                                                                                                                                                | 51 |

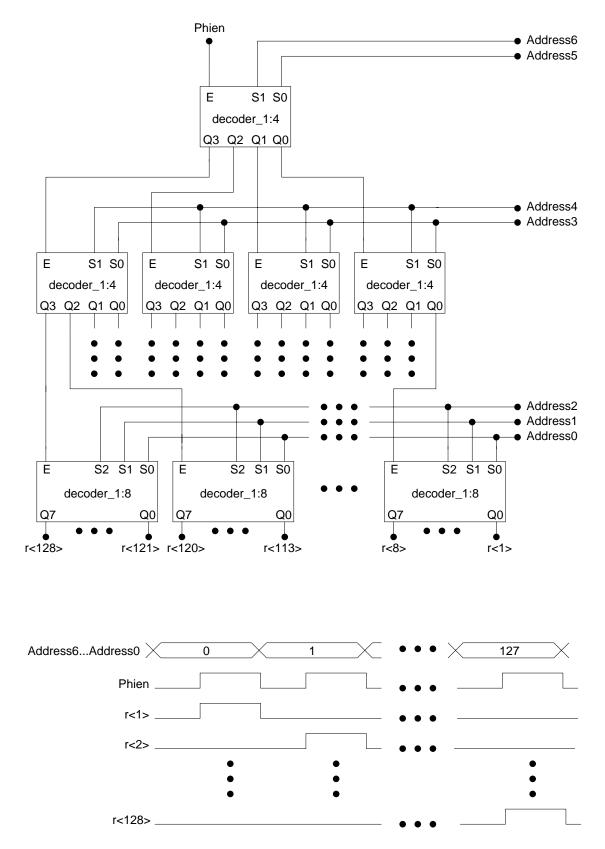

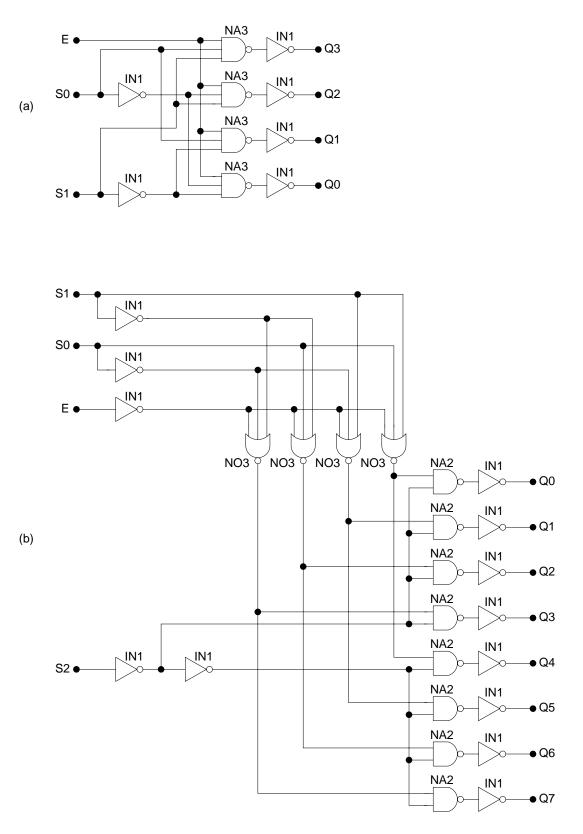

| 5.8                                       | Schematics of the (a) 1 of 4 decoder and (b) 1 of 8 decoder.                                                                                                                                                                               | 52 |

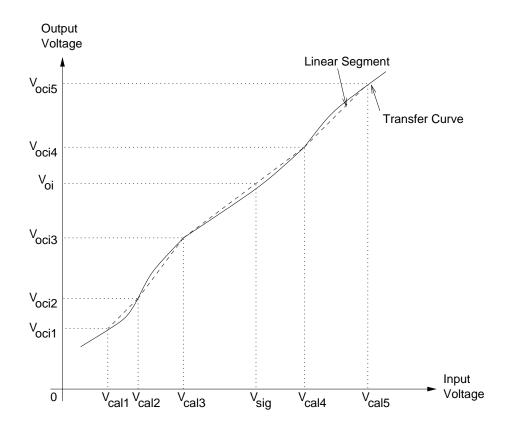

| 6.1                                       | Dc correction procedure using a subtraction method.                                                                                                                                                                                        | 56 |

| 6.2                                       | Dc correction procedure using a multiplication and addition method. $\ldots$                                                                                                                                                               |    |

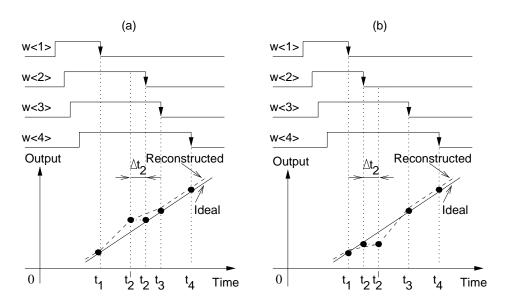

| $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ | Dc correction procedure using a piece-wise linear approximation method Effect of sample time error on the reconstructed output of four write signals showing the actual sample time of the write signal $w < 2 >$ which can be             | 58 |

|                                           | (a) after or (b) before the nominal sample time                                                                                                                                                                                            | 60 |

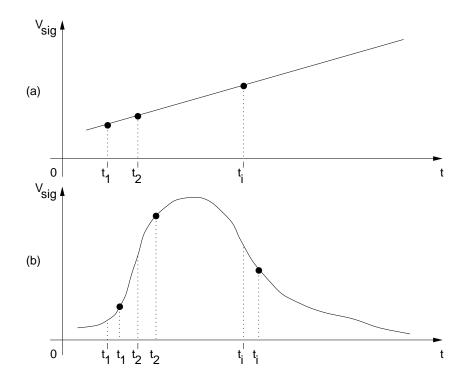

| 6.5                                       | Input signal as (a) ramp wave or (b) signal from Cherenkov telescope                                                                                                                                                                       | 60 |

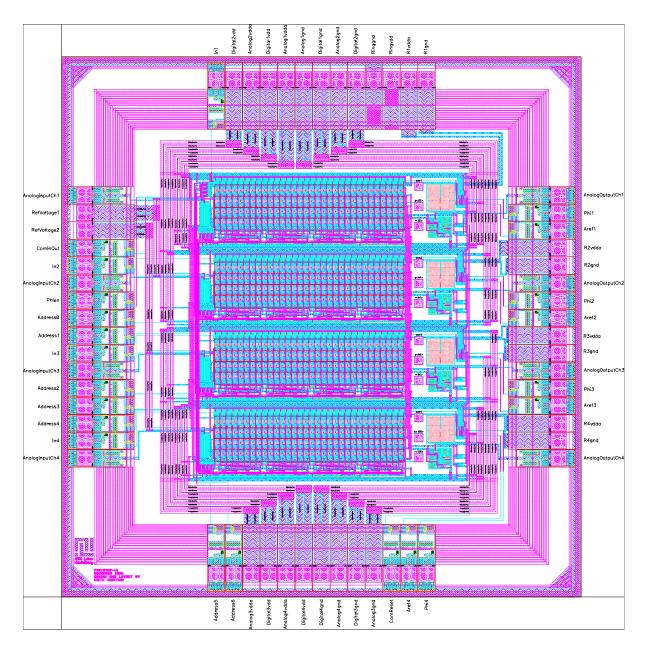

| 7.1                                       | Layout view (3.26 mm $\times$ 3.37 mm) of the FASTSAMP-EV chip                                                                                                                                                                             | 64 |

| 7.2                                       | Layout view (3.26 mm $\times$ 3.39 mm) of the FASTSAMP-V1 chip                                                                                                                                                                             | 65 |

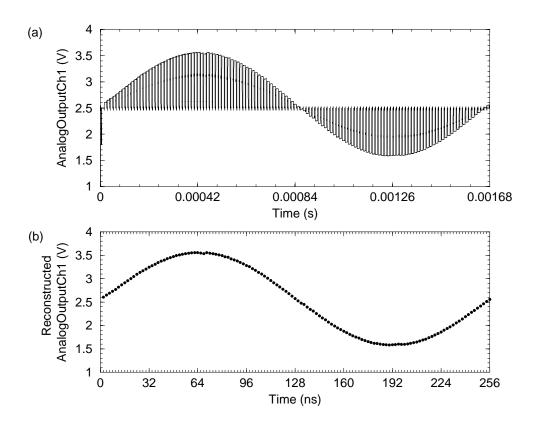

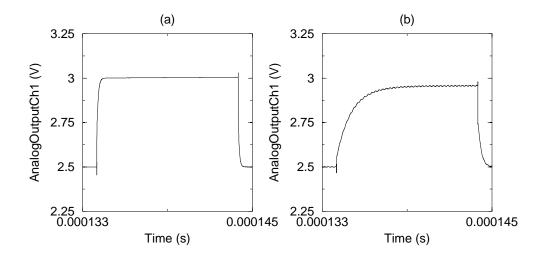

| $7.3 \\ 7.4$                              | Schematic (upper) and layout (lower) of an analog memory cell Response after simulations of one channel to a 2 V peak-to-peak, 3.906250 MHz sine wave sampled at 500 MHz. The pulse is plotted on                                          | 66 |

| 7.5                                       | the (a) read and the (b) write time scale                                                                                                                                                                                                  |    |

| 7.6                                       | parasitic simulations. The pulse is plotted on the read time scale Circuit for analysis of analog memory noise during the (a) write and (b)                                                                                                | 68 |

|                                           | read phase.                                                                                                                                                                                                                                | 69 |

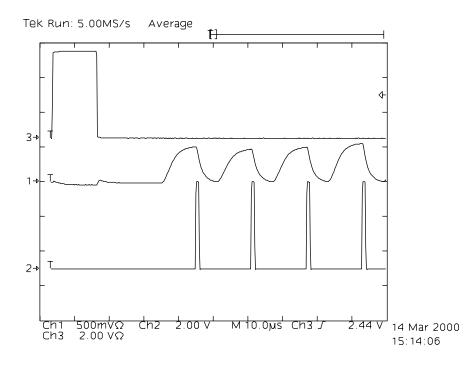

| 7.7                                       | Picture taken from the oscilloscope representing three channels Ch1:<br>AnalogOutputCh1, Ch2: TriggerScope and Ch3: ComIn or ComInOut                                                                                                      | 70 |

| 7.0                                       | depending of the chip version                                                                                                                                                                                                              | 70 |

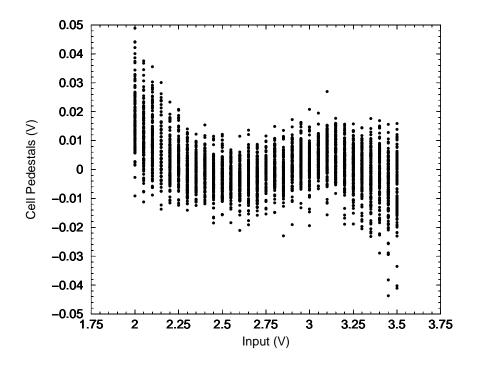

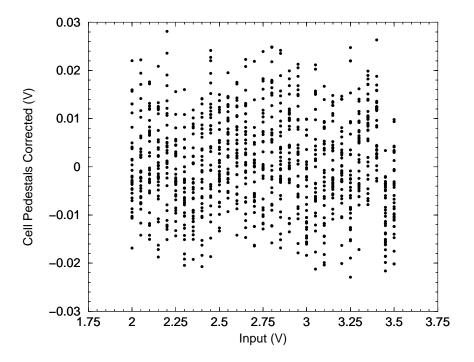

| 7.8                                       | Cell pedestals after calibration as a function of input voltage for the 128                                                                                                                                                                | 72 |

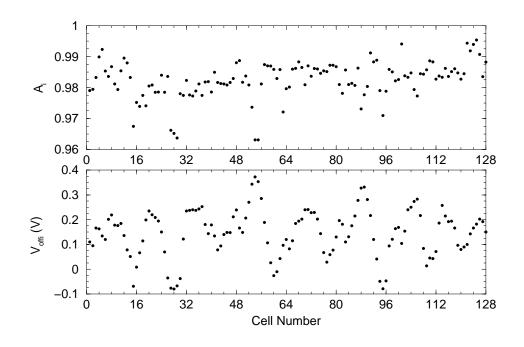

| 7.9                                       | memory cells. Dc measurements for FASTSAMP-EV device                                                                                                                                                                                       | 12 |

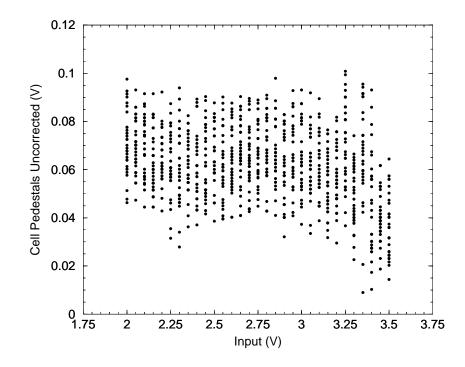

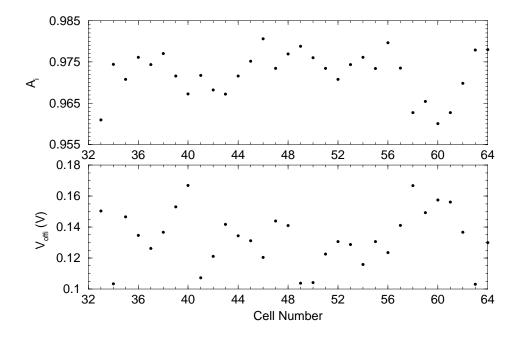

| 1.9                                       | memory cells. Dc measurements for FASTSAMP-V1 device                                                                                                                                                                                       | 73 |

| 7 10                                      | Cell pedestals after calibration as a function of input voltage for the 32                                                                                                                                                                 | 10 |

| 1.10                                      | memory cells. Dc measurements for FASTSAMP-V1 device                                                                                                                                                                                       | 73 |

| 7.11                                      | Cell gain (upper) and cell offset voltage (lower) as a function of cell number                                                                                                                                                             | 10 |

| 1.77                                      | for FASTSAMP-EV device.                                                                                                                                                                                                                    | 74 |

| 7.12                                      | Cell gain (upper) and cell offset voltage (lower) as a function of cell number                                                                                                                                                             |    |

|                                           | for FASTSAMP-V1 device                                                                                                                                                                                                                     | 74 |

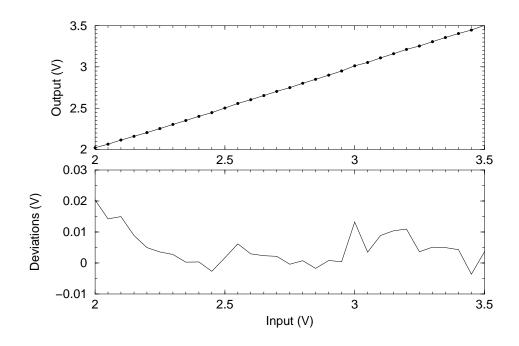

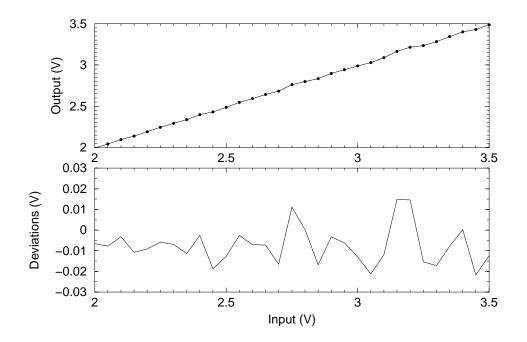

| 7.13       | Upper: Output plotted as a function of input voltage. Lower: Devi-<br>ations for the selected 1.5 V input signal range. Dc measurements for<br>FASTSAMP-EV device                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.14       | FASTSAMP-EV device.75Upper: Output plotted as a function of input voltage.Tower: Devi-ations for the selected 1.5 V input signal range.Dc measurements forFASTSAMP-V1 device.75                                             |

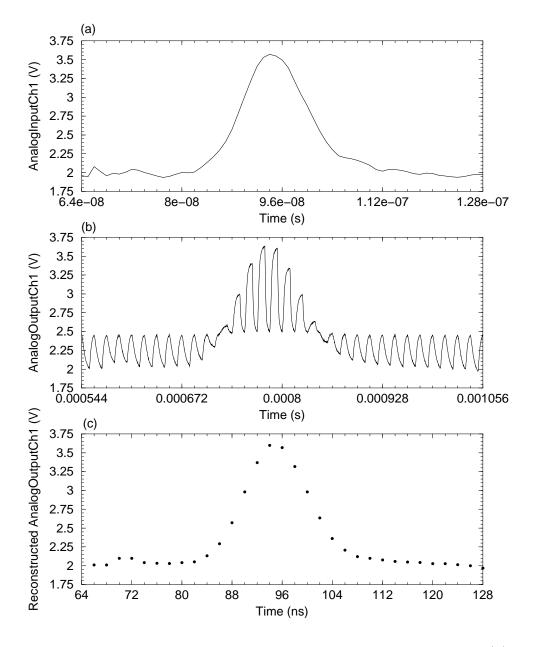

| 7.15       | Response after measurements of 32 cells to a 1.5 V peak-to-peak (a) gaus-<br>sian pulse sampled at 500 MHz. The pulse is plotted on the (b) read and<br>the (c) write time scale. Ac measurements for FASTSAMP-V1 device 77 |

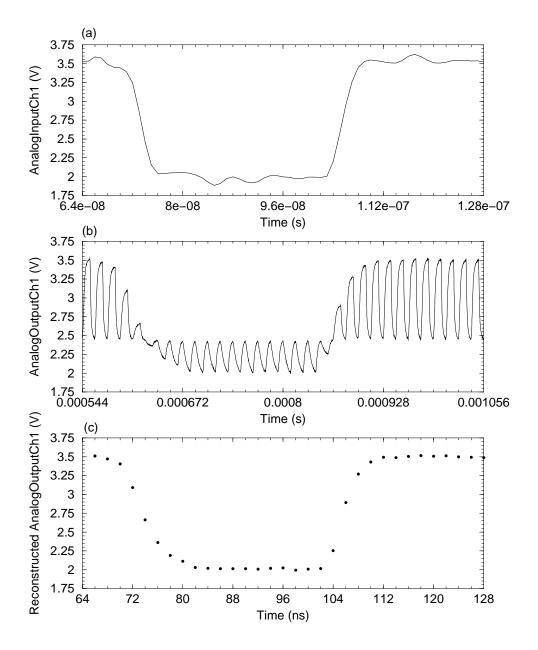

| 7.16       | Response after measurements of 32 cells to a 1.5 V peak-to-peak (a) rectangle pulse sampled at 500 MHz. The pulse is plotted on the (b) read and                                                                            |

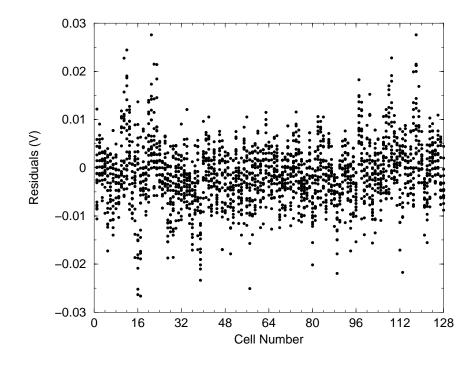

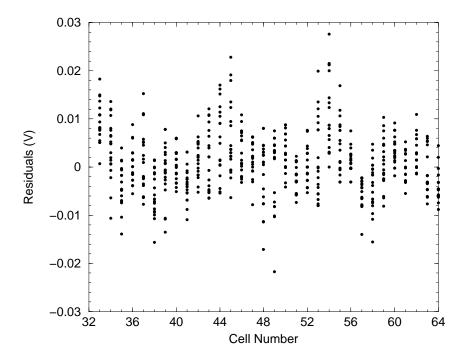

| 7.17       | the (c) write time scale. Ac measurements for FASTSAMP-V1 device 78<br>Results of 20 measurement sets from a 1.5 V peak-to-peak, 3.906250 MHz<br>sine wave sampled at 500 MHz. Residuals are plotted as a function of cell  |

| 7.18       | number for FASTSAMP-EV device                                                                                                                                                                                               |

|            | number for FASTSAMP-V1 device                                                                                                                                                                                               |

| B.1<br>B.2 | Schematic of the NMOS switch placed in signal return path                                                                                                                                                                   |

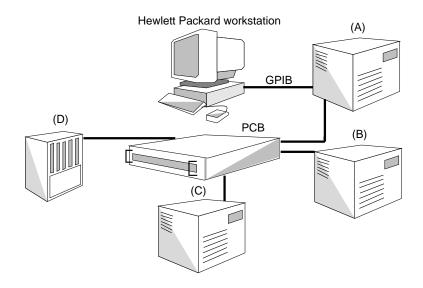

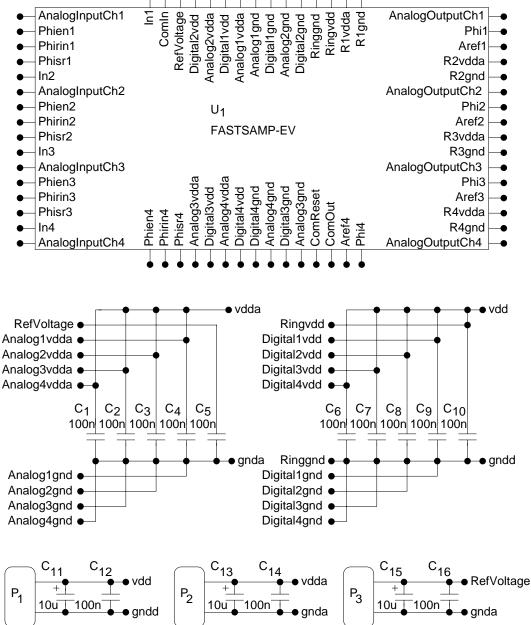

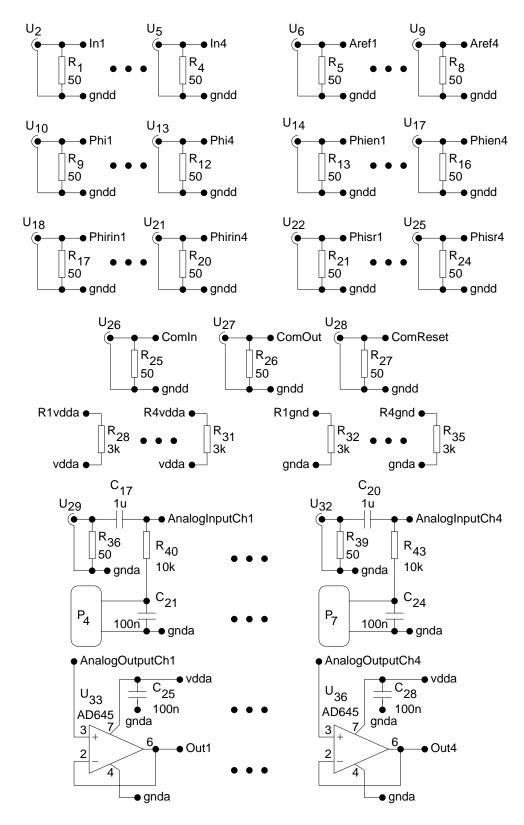

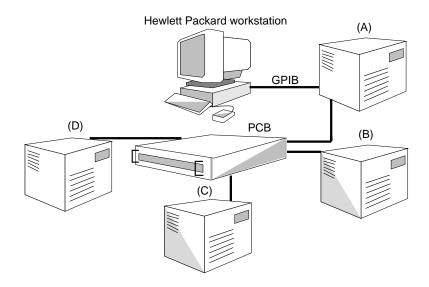

| C.1<br>C.2 | Experimental setup for FASTSAMP-EV chip                                                                                                                                                                                     |

| C.3        | supply connections                                                                                                                                                                                                          |

| C 4        | tions between the chip and other components                                                                                                                                                                                 |

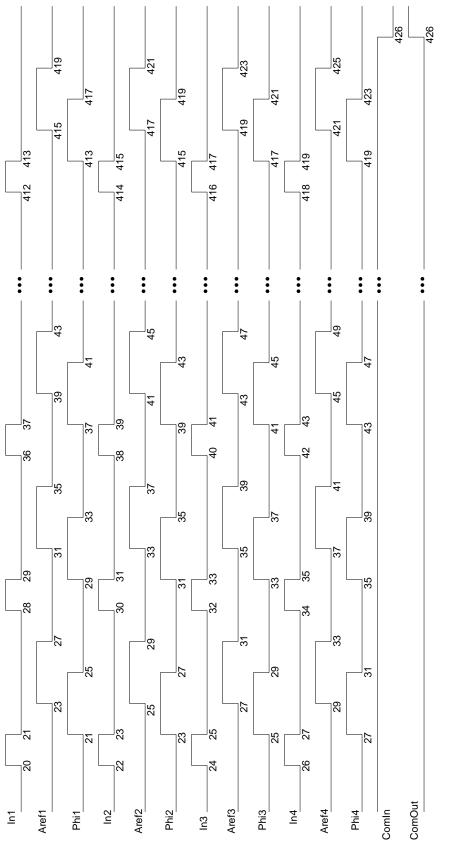

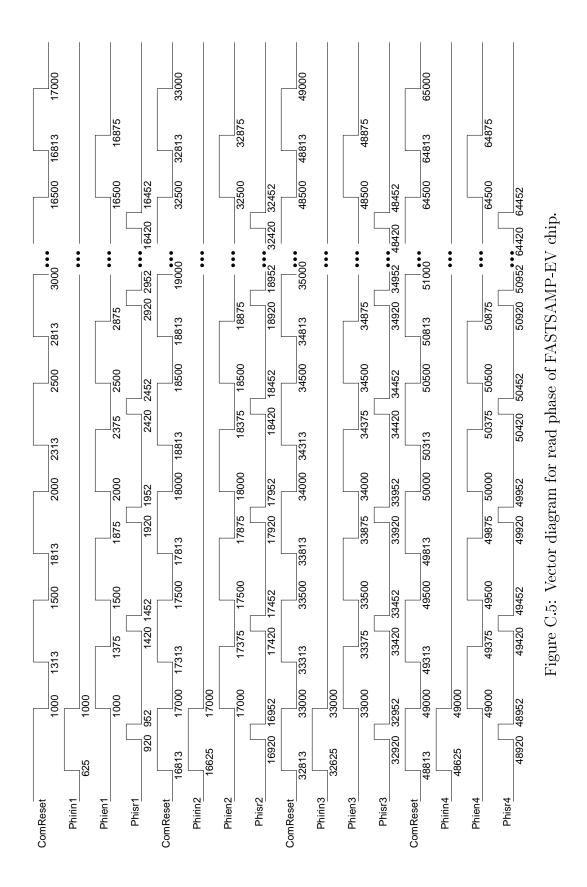

|            | Vector diagram for write phase of FASTSAMP-EV chip                                                                                                                                                                          |

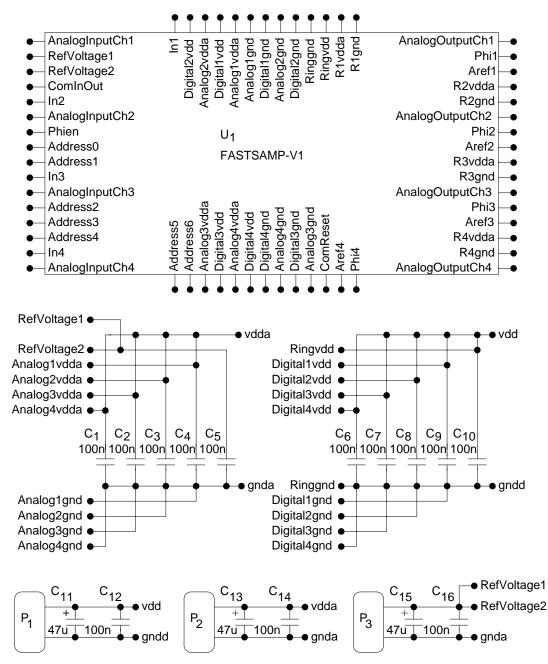

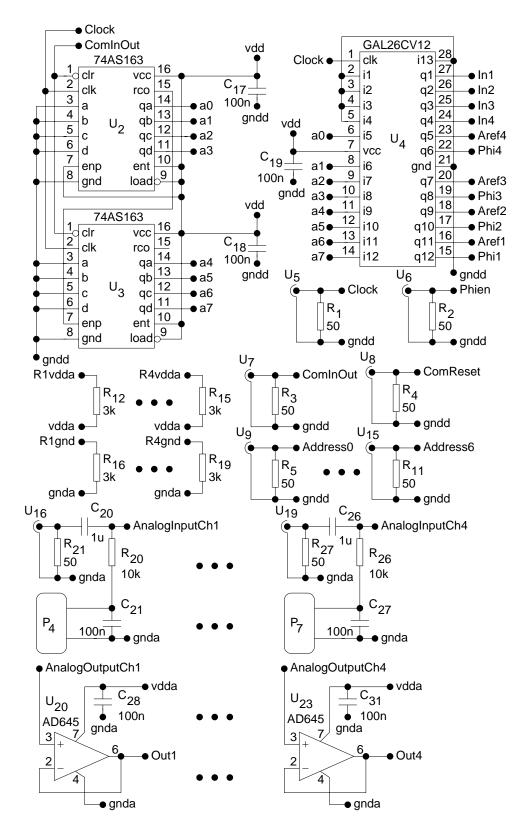

| D.1<br>D.2 | Experimental setup for FASTSAMP-V1 chip                                                                                                                                                                                     |

| D.3        | supply connections                                                                                                                                                                                                          |

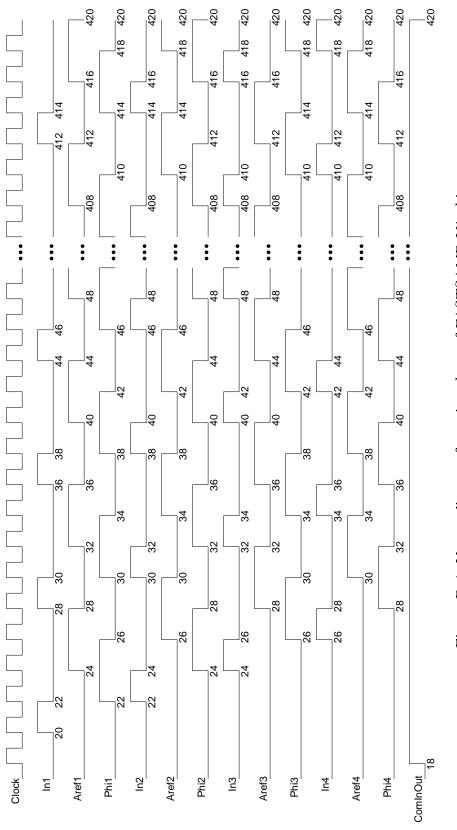

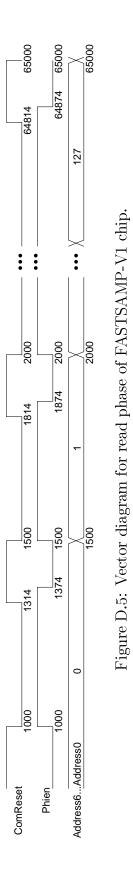

| D.4<br>D.5 | tions between the chip and other components                                                                                                                                                                                 |

# Chapter 1

# Introduction

### 1.1 Motivation

In many modern data acquisition systems the analog waveforms need only to be captured as snap shots and continuous digitisation is not necessary. Such applications include pulse echo phenomena (radar, ultrasonics), pulse shape recording (high energy physics experiments), and laboratory instrumentation (oscilloscopes, transient digitisers). In these applications an input waveform can be sampled at a high sampling frequency for a limited period of time, and the samples are stored in an analog memory. The analog samples are then retrieved at a lower rate and digitised with a slow analog-to-digital (ADC) converter before a new waveform is acquired. Advantages of using an analog memory include low overall power dissipation and cost, high density, and potentially superior dynamic range at high sampling rates.

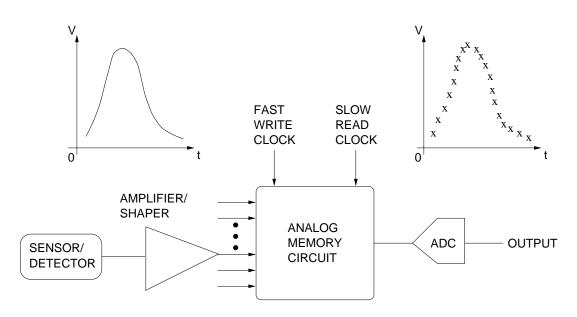

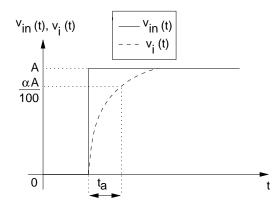

A block diagram of a typical waveform acquisition system is shown in Figure 1.1. The electrical signal generated in the detector or sensor is amplified and shaped. The analog waveform is then sampled at high speed rate by using a fast write clock and stored in the analog memory. The stored information is read out at slow rate and is converted into digital form. Because the readout speed and latency are not crucial, a commercial ADC can be used to convert data from analog into digital form. In addition, many signal channels can be multiplexed onto one ADC. The use of an analog memory eases the speed required of the ADC considerably and therefore significantly reduces the cost and the power dissipation.

Specific application for the memories proposed in this work appears for the camera electronics of the Cherenkov telescopes [1] in the High Energy Stereoscopic System (HESS) project [2]. Cameras for these telescopes and their readout systems were developed at Max-Planck-Institut für Kernphysik in Heidelberg. A large part of the trigger electronics, analog signal storage, and monitoring electronics are integrated in the camera electronics of the Cherenkov telescope. Fast photomultipliers (PMTs) are used to convert the Cherenkov light from the sky into electrical signals. The proposed analog memories are an alternative for the camera electronics of the Cherenkov telescopes where continuous data acquisition is not required.

Figure 1.1: Signal acquisition in an analog memory.

A number of concepts and circuits considered in this thesis have been taken from [26] and adapted for the Cherenkov application. This is the case of the analog memory architecture, of the readout operational amplifier and of the control circuits. Changes in the design from [26] can be found in the high speed addressing circuit and read control circuit.

In this thesis the basic characteristics of integrated transistor switches and capacitors are reviewed and two circuits for waveform sampling at rate of 500 MHz are introduced. Each circuit consists of four channels with 128 cells in each channel for acquiring analog waveforms. The architectures of these circuits are investigated in detail with respect to their theoretical dc and ac performances. Both switched capacitor analog memories for capturing fast signals from Cherenkov telescopes have been integrated in the Austria Microsystems (AMS) 0.8  $\mu$ m complementary metal oxide semiconductor (CMOS) process with poly-to-poly capacitors. The chips have been tested at ASIC laboratory in Heidelberg and the experimental results are presented in this thesis.

### 1.2 Outline

The implementation of analog memory cells using switched capacitor circuits is described in Chapter 2. Several analog memory architectures that have been implemented are examined briefly. The chapter then describes the MOS transistor explored with respect to its use as a voltage switch. The error voltages are evaluated for several memory cell configurations wherein the switch is inserted in the signal or signal return paths. The limiting factors governing the matching of the signal responses among individual memory cells are identified.

Chapter 3 introduces an analog memory core architecture. The operation of this

memory and its expected performance are discussed. Performance parameters such signal range, small signal acquisition bandwidth, and acquisition time are presented. The memory circuit's transfer function is derived, illustrating the effect of component mismatch within a memory channel on the memory response.

The folded cascode amplifier architecture is described in Chapter 4. The amplifier is examined and its gain, bandwidth, and noise are investigated. The simulation results are compared to the calculated parameters.

The control circuits which provide the write and read addresses for analog memory core are described in Chapter 5. A write control circuit comprising delay chains with feedback control circuits is proposed. Depending of the chip version, the read control circuit is implemented with shift registers or decoders.

Calibration and correction procedures that can be used for high precision data acquisition are reviewed in Chapter 6.

The simulation and experimental results of two circuits are presented in Chapter 7. These circuits were integrated in a AMS 0.8  $\mu$ m CMOS technology with poly-to-poly capacitors. The test setups used for the characterisation of the memories are explained and experimental results are presented. A dynamic range of 8 bits has been achieved for sampling rate of 500 MHz.

Chapter 8 summarises the contributions of this research and identifies areas of future study.

# Chapter 2

# Switched Capacitor Analog Memory Cell

### 2.1 Overview

In this chapter the operation of the MOS transistor is investigated with emphasis on its use in sample and hold configuration. The chapter starts with a short description of some architectures that have been realised in switched capacitor technologies. In the following section the analog memory concept is explained. In Section 2.5 and Section 2.6 are expressed the error voltages for MOS transistors and CMOS transmission gates as a function of the circuit parameters. Implementation of poly-to-poly capacitors for the storage of the sampled signal is reviewed in Section 2.7. For many analog memory applications the uniformity of the memory cell transfer characteristic in a channel is more important than the absolute channel offset and gain. The parameters limiting this uniformity are discussed in Section 2.8.

### 2.2 Analog Memory Architectures

Strong cost and performance incentives especially encourage the use of analog switched capacitor memories in high energy physics experiments [3]. Fast analog waveform capture for thousands of channels must be provided with a minimum of power dissipation. The design challenge is to produce an uniform and linear response in large number of memory cells at a level of performance comparable to the accuracy inherent in the technology. Principal performance issues are cell-to-cell offset and gain variations within a memory channel, which are governed by the circuit architecture and its sensitivity to the matching properties of its constituent transistors and capacitors [4]–[6]. In high precision applications, the lowest achievable cell non-uniformities may not be acceptable and must therefore eliminated by correcting the data. In large systems, it is essential that the number of correction constants and the computational effort to be minimised.

Early analog memory circuits based on a sample and hold topology contain a sampling switch, a storage capacitor, and a readout buffer in each memory cell [7]-[10]. In order to

meet the need for lower power and higher density, architectures based on switched capacitor circuits were introduced [11]–[17]. In these circuits, each channel comprises a bank of capacitors that are switched to a single operational amplifier for readout. Architectures in which the sampling transistors are placed in the signal path [7]–[13] exhibit signal dependent charge injection in each cell. Cell pedestals are then a function of the input signal and may require individual offset, gain, and linearity corrections. In addition, a serious disadvantage of these implementations in high speed applications is the dependence of the sampling transistor turn off time on the signal level [8].

In circuits based on traditional charge redistribution switched capacitor techniques [17], sampling switch charge injection can be made independent of the signal level, but the cell gain is a linear function of the size of the storage capacitor. Cell-to-cell gain matching of better than 0.5 % across an entire channel is therefore difficult to achieve, and both offset and gain corrections are commonly needed for each cell.

An analog memory architecture published in [26] was used in this thesis and described in Chapter 3. It will be shown that for this architecture the memory cell pedestal voltages are independent of the input signal voltage.

### 2.3 Analog Memory Concept

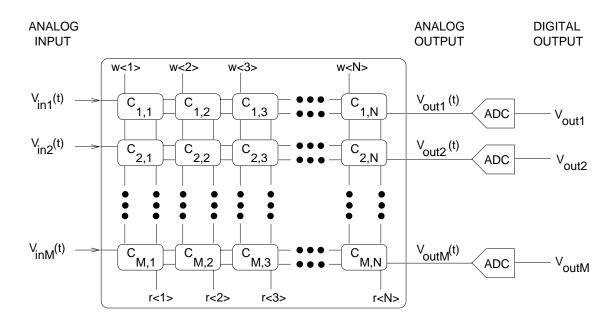

The concept of an analog memory circuit comprising M signal channels with N cells in each channel is shown in Figure 2.1. Each cell of the memory  $C_{j,i}$  is located on the column address i  $(1 \le i \le N)$  and the row address j  $(1 \le j \le M)$ . An analog input signal  $V_{inj}(t)$  is applied to all N memory cells in the channel j. The write control signals w < 1 > through w < N > as well as the read control signals r < 1 > through r < N >are common to all channels. The analog waveforms are stored in the analog memory by sequentially addressing the memory cells within a channel via the write control signals w < 1 > through w < N >. After the write phase is finished, the readout phase is initiated by applying sequentially the read addresses r < 1 > through r < N >. The analog output  $V_{outj}(t)$  can be digitised by an on or off-chip ADC converter which provides the digital information  $V_{outj}$ .

The maximum number of the analog values which can be stored in the array represented in Figure 2.1 is the number of rows M times the number of columns N. Usually in analog memory applications [8, 9] the number of channels is large compared with the number of cells in one channel  $(M \gg N)$ . In such applications, the minimum time between the acquisition of two consecutive input waveforms must be long enough to permit a sequential read out of the data.

This thesis focuses on analog waveform sampling applications in which the number of cells in a channel is large compared to the number of channels on one chip  $(N \gg M)$ .

For both types of applications where  $(M \gg N)$  and  $(N \gg M)$  the time between the readout of two adjacent memory cells can be much larger than the time between the acquisition two consecutive input samples. This facilities the use of a low speed high resolution ADC converter. Generally, a single converter is sufficient for digitisation of the analog waveforms from many memory cells.

Figure 2.1: Simplified representation of an analog memory.

### 2.4 CMOS Technology

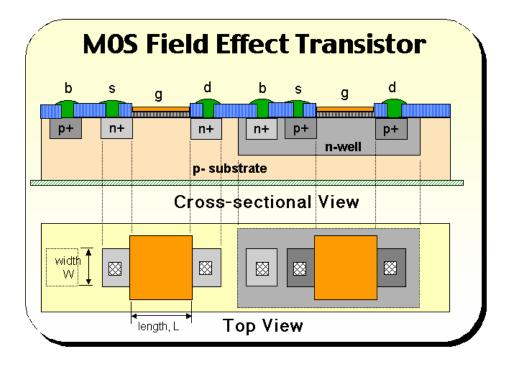

The AMS 0.8  $\mu$ m CMOS process is a *twin*-well technology on *p*-substrate with double metal and double poly [40]. In a twin-well technology, there are created individual wells for NMOS and PMOS transistors and the substrate may be either *n*-type or *p*-type. The structure of an *n*-channel and *p*-channel MOS transistor using a *n*-well technology is shown in Figure 2.2. The *n*-channel device is formed with two heavily doped  $n^+$  regions diffused into a lighter doped p-substrate. The two  $n^+$  regions are called d (drain) and s (source). and are separated by a distance, L (referred to as the device length). At the surface between the drain and source lies a gate electrode q that is separated from the silicon by a thin dielectric material (silicon dioxide). The b terminal is the bulk, or substrate, which contains the drain and source diffusions. Similarly, the *p*-channel transistor is formed by two heavily doped  $p^+$  regions within a lightly doped n for n-well processes. It, too, has a gate on the surface between the drain and source separated from the silicon by a thin dielectrical material (silicon dioxide). For a *n*-well process, the *p*-substrate connection is common throughout the integrated circuit and is connected to the lowest potential. Multiple n-wells can be fabricated on a single circuit, and they can be connected to different potentials in various ways depending upon the application. Essentially both NMOS and PMOS transistors have four terminals as identified in Figure 2.2 by q (gate), d (drain), s (source) and b (bulk).

An interesting observation can be made from the layout of the MOS transistor in Figure 2.2. The MOS devices are totally geometrically symmetric with respect to drain and source and so must also be electrically symmetric. The designation of drain and source is thus arbitrary. In many applications a convention has evolved for convenience and consistency in device modelling in regard to drain and source designation.

Figure 2.2: Physical structure of an NMOS and PMOS transistor in a *n*-well CMOS technology.

### 2.5 NMOS Transistor Switch

#### 2.5.1 NMOS Switch Resistance

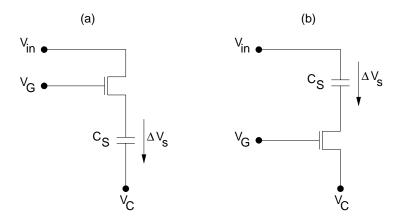

In an analog memory cell the MOS transistor can be used as a voltage switch. Two sample and hold configurations were proposed in Figure 2.3 using an NMOS transistor as switch and a storage capacitor  $C_s$ .

An expression of the on channel resistance can be found as follows. In the on state of the switch, the voltage across the switch should be small, and the gate-to-source voltage  $V_{GS}$  should be large. Therefore, the NMOS transistor is assumed to be in the ohmic region [18]–[21] ( $V_{DS} < V_{GS} - V_T$ ) and the current through the device is given by

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left( V_{GS} - V_T - \frac{V_{DS}}{2} \right) V_{DS},$$

(2.1)

where  $V_{DS}$  is the drain-to-source voltage,  $\mu_n$  is the electron mobility in the channel, Wand L are the width and length of the channel,  $V_T$  is the threshold voltage and  $C_{ox}$  is the oxide capacitance per unit area. The on resistance of the channel can be approximated by

$$R_{DS} = \frac{1}{\frac{\partial I_{DS}}{\partial V_{DS}}} \approx \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T)}.$$

(2.2)

The on resistance is inversely proportional to the W over L ratio and is nonlinear since it depends on the gate-to-source voltage.

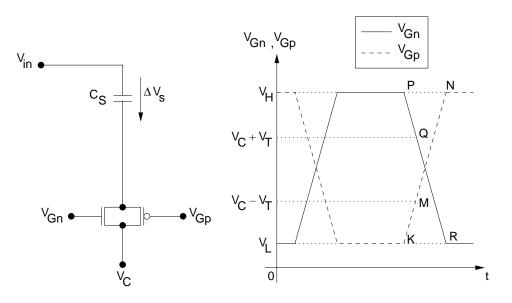

Figure 2.3: NMOS switch placed in (a) signal and (b) signal return path.

#### 2.5.2 Error Voltage

As long as the the NMOS switches are conducting, the voltage across the storage capacitor in Figure 2.3 is given by

$$\Delta V_s = V_{in} - V_C, \qquad (2.3)$$

where  $V_{in}$  is the input voltage and  $V_C$  is the reference voltage. The NMOS transistor turns off when the gate-to-source voltage is less than the threshold voltage. The voltage across the capacitor after turn off of the sampling switch is

$$\Delta V_s = V_{in} - V_C - V_p, \qquad (2.4)$$

where  $V_p$  is the pedestal voltage due to charge injection and clock feedthrough effect [22]– [25]. In Appendix B these effects are explained in detail and the expression of the pedestal voltage for an NMOS switch placed in signal return path is derived. The magnitude of the pedestal voltage differs for the two cell arrangements represented in Figure 2.3.

In the configuration shown in Figure 2.3(a) the pedestal voltage can be derived in similar way than in Appendix B and written as follows

$$V_p = \frac{\alpha C_{ox} WL}{2C_S} (V_H - V_{in} - V_T) + \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_{in} - V_L + V_T).$$

(2.5)

$C_p$  is the parasitic capacitance to ground,  $C_{ov}$  is the gate overlap capacitance,  $\alpha$  is a coefficient (0 <  $\alpha$  < 1),  $V_L$  and  $V_H$  are the low and high levels of the transistor gate voltage. The pedestal voltage can be split into a gain error and an offset,

$$V_p = \varepsilon V_{in} + V_{of}. \tag{2.6}$$

The gain error in the circuit is

$$\varepsilon = \frac{C_{ov}}{C_{ov} + C_S + C_p} - \frac{\alpha C_{ox} WL}{2C_S},\tag{2.7}$$

Figure 2.4: Pedestal voltage as a function of input voltage for NMOS switch.

while the offset voltage is

$$V_{of} = \frac{\alpha C_{ox} WL}{2C_S} (V_H - V_T) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_L - V_T).$$

(2.8)

Following (2.5) through (2.8) for the circuit configuration shown in Figure 2.3(a), the error voltage  $V_p$  during turn off depends on the input signal level.

The circuit shown in Figure 2.3(b) can be analysed in the same manner as the circuit in Figure 2.3(a), with the result that the pedestal voltage (see Appendix B) is for this configuration

$$V_p = -\frac{\alpha C_{ox} WL}{2C_S} (V_H - V_C - V_T) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_C - V_L + V_T).$$

(2.9)

The gain error and offset voltage can be written as

$$\varepsilon = 0 \tag{2.10}$$

$$V_{of} = -\frac{\alpha C_{ox} WL}{2C_S} (V_H - V_C - V_T) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_C - V_L + V_T).$$

(2.11)

It is evident from (2.9) through (2.11) that the error voltage is independent on the input signal voltage.

The results of SPICE [43]–[46] simulations for the two circuits in Figure 2.3 when they are implemented in the AMS 0.8  $\mu$ m CMOS technology are illustrated in Figure 2.4. The

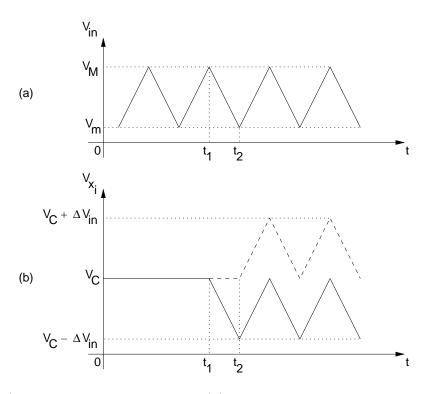

Figure 2.5: Timing errors when the sampling switch is placed in signal path.

absolute values of the simulated pedestal voltages are plotted as a function of the input voltage. The W/L ratio of the NMOS transistor was set to 25  $\mu$ m/0.8  $\mu$ m and the size of the sampling capacitance was 500 fF. The gate voltage was a ramp which fell from the high value 5 V toward the low value 0 V in 300 ps. The pedestal voltage varies by 40 mV across an input voltage range of 2 V when the switch is inserted in signal path (Figure 2.3(a)) or is constant (Figure 2.3(b)).

#### 2.5.3 Distortion and Timing Errors

In the preceding subsection the responses of two sample and hold cells to dc input signals were evaluated. This subsection proposes an analysis of distortion and timing errors for ac input signals.

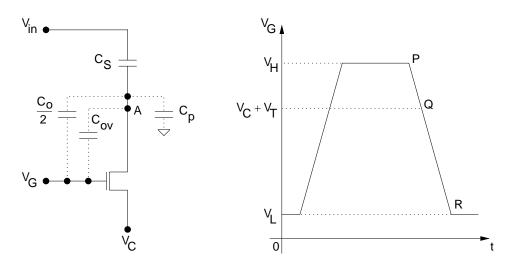

For the configuration shown in Figure 2.3(a) an ac input pulse with an amplitude of  $A_{in}$  and rise and fall times of  $t_{inr}$  was considered. The process is illustrated in Figure 2.5. The gate control voltage of the NMOS transistor fell from the high value  $V_H$  to the low value  $V_L$  with the fall time of  $t_f$ . At the ideal sampling time  $t_s$  the switch is supposed turned off at high level  $V_H$  of the gate control voltage. In reality, the switch turns off when the gate control voltage reaches  $(V_{in} + V_T)$  and the actual sampling time  $t'_s$  is given by

$$t'_{s} = t_{s} + \frac{t_{f}}{V_{H} - V_{L}} (V_{H} - V_{in} - V_{T}).$$

(2.12)

For the rising input signal when

$$V_{in} = \frac{A_{in}}{t_{inr}}t\tag{2.13}$$

Figure 2.6: Timing errors when the sampling switch is placed in signal return path.

the output signal after changing the time scale can be written as follows

$$V_{out} = \frac{A_{in}}{t_{inr}} \left[ t + \frac{t_f}{V_H - V_L} (V_H - V_{in} - V_T) \right].$$

(2.14)

Inserting (2.13) into (2.14), the dependence  $dV_{out}/dt$  on  $dV_{in}/dt$  can be expressed as

$$\frac{dV_{out}}{dt} = \left(1 - \frac{A_{in}}{t_{inr}} \frac{t_f}{V_H - V_L}\right) \frac{dV_{in}}{dt}.$$

(2.15)

The ratio  $A_{in}/t_{inr}$  is positive for a rising input signal and negative for a falling input signal. The resulting signal slope  $dV_{out}/dt$  is smaller for rising input signals and larger for falling signals, as indicated with dashed lines in Figure 2.5. The sample and hold configuration wherein the switch is inserted in the signal path introduces timing errors and signal distortion.

For sinusoidal input signals,  $V_{in} = A_{in} \sin(2\pi f t)$ , the output waveform  $V_{out}$  is given by

$$V_{out} = A_{in} \sin\left\{2\pi f\left[t + \frac{t_f}{V_H - V_L}(V_H - V_T) - \frac{A_{in}t_f}{V_H - V_L}\sin(2\pi ft)\right]\right\}.$$

(2.16)

The output result is an analog waveform which is harmonic distortioned in comparison with the input signal.

For the circuit of Figure 2.3(b), where the sampling switch is placed in the signal return path, the actual sampling time is given by

$$t'_{s} = t_{s} + \frac{t_{f}}{V_{H} - V_{L}} (V_{H} - V_{C} - V_{T}), \qquad (2.17)$$

as illustrated in Figure 2.6. In the same manner can be determined

$$\frac{dV_{out}}{dt} = \frac{dV_{in}}{dt} \tag{2.18}$$

and for sinusoidal input signals,  $V_{in} = A_{in} sin(2\pi f t)$ ,

$$V_{out} = A_{in} \sin\left\{2\pi f\left[t + \frac{t_f}{V_H - V_L}(V_H - V_C - V_T)\right]\right\}.$$

(2.19)

Thus, there is a constant time delay for pulse inputs and a constant phase shift for input sine waves. As a conclusion, the circuit in Figure 2.3(b) exhibits superior performance in respect to amplitude and timing errors.

#### 2.6 CMOS Transmission Gate Switch

The CMOS transmission gate simply consists of a complementary pair of MOS transistors connected in parallel. In comparison with MOS transistors, the CMOS transmission gates require the generation of complementary control signals, which could be difficult to implement in high speed sampling circuits. In the following subsection the error voltage terms for the complementary switch are described.

#### 2.6.1 CMOS Switch Resistance

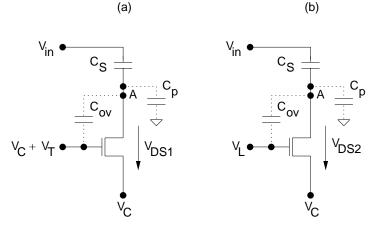

In Figure 2.7 is represented a basic sample and hold configuration of a CMOS transmission gate switch placed in signal path. The on resistances of the NMOS and PMOS transistors are

$$R_{DSn} = \frac{1}{\frac{\partial I_{DSn}}{\partial V_{DSn}}} \approx \frac{1}{\mu_n C_{ox} \frac{W_n}{L_n} \left( V_{GSn} - V_{Tn} \right)}$$

(2.20)

$$R_{DSp} = \frac{1}{\frac{\partial I_{DSp}}{\partial V_{DSp}}} \approx \frac{1}{\mu_p C_{ox} \frac{W_p}{L_p} \left(-V_{GSp} + V_{Tp}\right)}$$

(2.21)

where  $\mu_p$  is the hole mobility. The conductance of the complementary CMOS switch is simply the sum of the individual NMOS and PMOS conductances

$$\frac{1}{R_{DS}} = \frac{1}{R_{DSn}} + \frac{1}{R_{DSp}}.$$

(2.22)

With  $V_{GSn} = V_{Gn} - V_{in}$ ,  $V_{GSp} = V_{Gp} - V_{in}$ , and  $V_{Tn} = -V_{Tp} = V_T$ , this equation can be rewritten as

$$\frac{1}{R_{DS}} \approx \left(\mu_p \frac{W_p}{L_p} - \mu_n \frac{W_n}{L_n}\right) C_{ox} V_{in} + \mu_n C_{ox} \frac{W_n}{L_n} (V_{Gn} - V_T) + \mu_p C_{ox} \frac{W_p}{L_p} (-V_{Gp} - V_T).$$

$$(2.23)$$

Figure 2.7: Schematic of the CMOS switch placed in signal path.

The conductance of the transmission gate depends on the input signal level as expressed in (2.23). However, the first term in this equation can be eliminated by choosing the width over length ratios of the transistors according to their mobility ratio

$$\frac{W_n}{L_n} = \left(\frac{\mu_p}{\mu_n}\right) \frac{W_p}{L_p}.$$

(2.24)

In practice, a fraction of the input level dependence will remain since the ratio of the mobilities can not be accurately controlled in the fabrication process.

#### 2.6.2 Error Voltage

It is assumed that both transistors NMOS and PMOS turn off simultaneously and therefore the error voltages can be summed. For the circuit configuration in Figure 2.7 the voltage  $\Delta V_s$  across the storage capacitor becomes

$$\Delta V_s = V_{in} - V_C - V_p \tag{2.25}$$

with

$$V_p = V_{pn} + V_{pp} \tag{2.26}$$

where  $V_{pn}$  and  $V_{pp}$  are pedestal voltages for NMOS and PMOS transistors due to charge injection and clock feedthrough effect. The error voltage  $V_{pn}$  can be written as in (2.5)

$$V_{pn} = \frac{\alpha C_{ox} W_n L_n}{2C_S} (V_H - V_{in} - V_T) + \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_{in} - V_L + V_T)$$

(2.27)

and the error voltage  $V_{pp}$  can be derived in a similar fashion to that for the NMOS transistor with the following result:

$$V_{pp} = -\frac{\alpha C_{ox} W_p L_p}{2C_S} (V_{in} - V_L - V_T) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H - V_{in} + V_T).$$

(2.28)

The total pedestal error voltage  $\mathcal{V}_p$  is

$$V_{p} = \left[\frac{2C_{ov}}{C_{ov} + C_{S} + C_{p}} - \frac{\alpha C_{ox}}{2C_{S}}(W_{n}L_{n} + W_{p}L_{p})\right]V_{in} + \frac{\alpha C_{ox}}{2C_{S}}[W_{n}L_{n}(V_{H} + V_{L}) + (W_{p}L_{p} - W_{n}L_{n})V_{T}] - \frac{C_{ov}}{C_{ov} + C_{S} + C_{p}}(V_{H} + V_{L}). \quad (2.29)$$

The total pedestal voltage can be split into the gain error  $\varepsilon$  and offset voltage  $V_{of},$

$$V_p = \varepsilon V_{in} + V_{of}. \tag{2.30}$$

Minimum error voltage in (2.29) is achieved for equivalent areas of both transistors

$$W_n L_n = W_p L_p. (2.31)$$

Under this condition the pedestal voltage becomes

$$V_p = \left(\frac{2C_{ov}}{C_{ov} + C_S + C_p} - \frac{\alpha C_{ox} W_n L_n}{C_S}\right) V_{in} + \frac{\alpha C_{ox} W_n L_n}{2C_S} (V_H + V_L) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H + V_L)$$

(2.32)

and the gain error and offset voltage are

$$\varepsilon = \frac{2C_{ov}}{C_{ov} + C_S + C_p} - \frac{\alpha C_{ox} W_n L_n}{C_S}$$

(2.33)

$$V_{of} = \frac{\alpha C_{ox} W_n L_n}{2C_S} (V_H + V_L) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H + V_L).$$

(2.34)

The pedestal voltages introduced in the circuit shown in Figure 2.8 can be written for NMOS transistor as in (2.9)

$$V_{pn} = -\frac{\alpha C_{ox} W_n L_n}{2C_S} (V_H - V_C - V_T) - \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_C - V_L + V_T)$$

(2.35)

and for PMOS transistor as

$$V_{pp} = \frac{\alpha C_{ox} W_p L_p}{2C_S} (V_C - V_L - V_T) + \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H - V_C + V_T).$$

(2.36)

Figure 2.8: Schematic of the CMOS switch placed in signal return path.

The total pedestal voltage  $V_p$  is the sum of the individual contributions as in (2.26)

$$V_{p} = \frac{\alpha C_{ox}}{2C_{S}} \left[ W_{p} L_{p} (V_{C} - V_{L}) - W_{n} L_{n} (V_{H} - V_{C}) + (W_{n} L_{n} - W_{p} L_{p}) V_{T} \right] + \frac{C_{ov}}{C_{ov} + C_{S} + C_{p}} (V_{H} + V_{L} - 2V_{C})$$

(2.37)

and is independent of the input signal level. Under the condition that  $W_n L_n = W_p L_p$  for the circuit simplifies to

$$V_p = \frac{\alpha C_{ox} W_n L_n}{2C_S} (2V_C - V_L - V_H) + \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H + V_L - 2V_C).$$

(2.38)

Thus the gain error and offset voltage become

$$\varepsilon = 0 \tag{2.39}$$

$$V_{of} = \frac{\alpha C_{ox} W_n L_n}{2C_S} (2V_C - V_L - V_H) + \frac{C_{ov}}{C_{ov} + C_S + C_p} (V_H + V_L - 2V_C).$$

(2.40)

As is the case for a single transistor switch, the circuit configuration with the switch in the signal path has a pedestal voltage that is dependent on the input signal voltage (2.32), whereas  $V_p$  is constant when the switch is inserted in the signal return path (2.38).

In this subsection it was assumed that the two complementary switches turn off simultaneously and part of the injected channel charge thus cancels. In practice, this is hard to accomplish, and the error voltages may be larger than suggested by (2.32) and (2.38). An important remark is that the gain error of the CMOS transmission gate is larger than the gain error of the MOS transistor when the switches are placed in signal path.

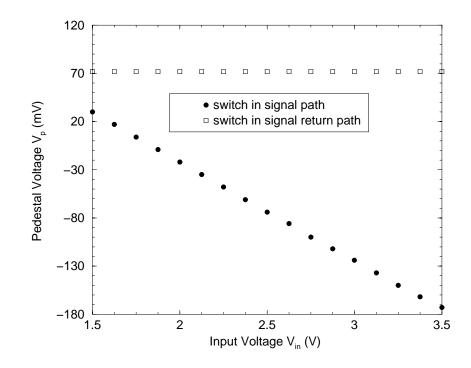

Figure 2.9: Pedestal voltage as a function of input voltage for CMOS switch.

The optimum performance for a CMOS transmission gate can be achieved using (2.24) and (2.31) to determine the geometry of the transistors. These relations give

$$L_n = L_p \sqrt{\frac{\mu_n}{\mu_p}} \tag{2.41}$$

and

$$W_p = W_n \sqrt{\frac{\mu_n}{\mu_p}}.$$

(2.42)

For AMS 0.8  $\mu$ m CMOS technology the mobilities are listed in Table A.1 of Appendix A and therefore (2.41) and (2.42) can be rewritten as

$$L_n \approx 1.665 L_p \tag{2.43}$$

and

$$W_p \approx 1.665 W_n. \tag{2.44}$$

The two circuits in Figure 2.7 and Figure 2.8 have been implemented in AMS 0.8  $\mu$ m CMOS technology and simulated with SPICE. The values of the pedestal voltages are plotted as a function of the input voltage and the results are shown in Figure 2.9. The storage capacitor was 500 fF.  $W_n$  and  $L_p$  were set to 25  $\mu$ m and 0.8  $\mu$ m, respectively.  $L_n$  and  $W_p$  were calculated from (2.43) and (2.44) with the values 1.33  $\mu$ m and 41.6  $\mu$ m. The gate voltages were two ramps of 300 ps each one. For an input voltage range of 2 V, the pedestal voltage varies by 140 mV when the switch is inserted in signal path (Figure 2.7), or is constant for the alternative configuration (Figure 2.8).

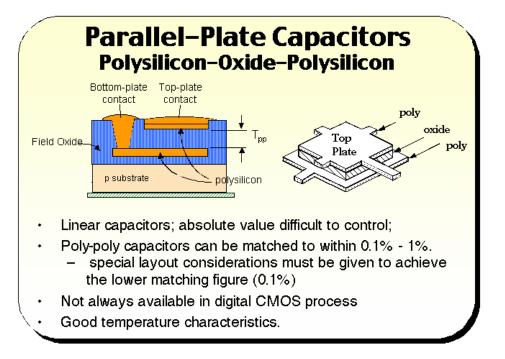

Figure 2.10: Physical structure of poly-to-poly capacitor.

# 2.7 Capacitors

The quality of capacitors determines the performance of an analog memory. Important issues are the matching of nominally identical capacitors and the absolute sizes and matching of associated parasitic capacitances. There are basically three types of capacitors suitable for analog circuit design available in CMOS processes: poly-over-diffusion capacitors, metal-to-metal capacitors and poly-to-poly capacitors. The first type of capacitor is formed using a polysilicon layer on top of crystalline silicon separated by a dielectric (silicon dioxide layer). In order to achieve a low voltage coefficient capacitor, the bottom plate must be heavily doped diffusion, which generally requires an extra implantation step in the fabrication process. The second type of capacitor is that formed by two metal layers separated by a dielectric. The advantages of this capacitor are its low voltage dependence and a good temperature characteristic. Finally, the third type of capacitor consists of two polysilicon layers separated by silicon dioxide, as illustrated in Figure 2.10. It can be seen that a double polysilicon process is needed to implement this capacitor since both the upper and lower plates are formed with polysilicon. The dielectric is formed by a thin silicon dioxide layer which can only be produced by using several steps beyond the usual single polysilicon process. The advantages of this capacitor are nearly voltage independent parasitic capacitance, good matching (up to 1%) and a good temperature characteristic. A typical value for the capacitance in AMS 0.8  $\mu m$  CMOS technology with poly-to-poly capacitors is 1.77 fF/ $\mu$ m<sup>2</sup>, while the associated bottom plate parasitic capacitance is 0.066 fF/ $\mu$ m<sup>2</sup> [40].

# 2.8 Matching Properties of Memory Cell

In analog memory applications the uniformity of the memory cell response in one channel is more important than the absolute channel gain and offset. The uniformity is affected by two principal sources of error: inaccuracies in the fabrication process [4]–[6] and control signal feedthrough.

The analog memory cells are designed with the geometry identically but the imperfections in the fabrication process determine a mismatching degree from cell to cell. In addition, there are variations in the area of the storage capacitor plates and the thickness of the dielectric. The characterisation of mismatch in MOS transistors is more complex than that in the case of capacitors. The matching of transistor characteristics on a chip is determined by the matching of threshold voltages, mobilities, oxide and gate overlap capacitances, and the widths and lengths of the transistor gates. The main contribution to cell response variations within a memory channel is the mismatch in the charge injection during turn off of the switch.

Assuming that the variations in width  $\delta W$  and length  $\delta L$  of two mismatched transistors in a channel are equal  $\delta W = \delta L = \delta P$  then

$$\delta(WL) = (W + \delta P)(L + \delta P) - WL \approx (W + L)\delta P, \qquad (2.45)$$

where  $\delta(WL)$  is the variation in area. For the circuit configuration in Figure 2.3(b) the pedestal voltage due to the charge injection from (2.9) is

$$V_{p1} = -\frac{\alpha C_{ox} WL}{2C_S} (V_H - V_C - V_T).$$

(2.46)

The variation in pedestal voltage  $\delta V_{p1}$  can be written as

$$\delta V_{p1} = -\frac{\alpha C_{ox} \delta(WL)}{2C_S} (V_H - V_C - V_T). \qquad (2.47)$$

Inserting (2.45) in (2.47) yields

$$\delta V_{p1} \approx -\frac{\alpha C_{ox} (W+L) \delta P}{2C_S} (V_H - V_C - V_T).$$

(2.48)

The variation in error voltage due to the nonuniform charge injection  $\delta V_{p1}$  is thus proportional to the channel width and length of the sampling transistor.

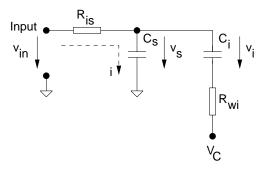

The time constant  $\tau$  with which the voltage across  $C_S$  follows a change in the input voltage depends on the on resistance  $R_{DS}$  of the sampling switch and the size of the capacitor,

$$\tau = R_{DS}C_S. \tag{2.49}$$

If it is assumed that  $W \gg L$ , (2.2) and (2.48) are inserted into (2.49), the time constant  $\tau$  can be approximated as

$$\tau \approx -\frac{\alpha L \delta P}{2\mu_n \delta V_{p1}}.$$

(2.50)

Thus, switches with smaller W/L ratio yield smaller pedestal mismatches but limit the signal bandwidth of the sampling cell.

In some analog memory applications CMOS transmission gates are used as switches because their absolute pedestal voltages reduced, as discussed in Section 2.6. However, the use of CMOS switches does not improve the matching of the sampling cell performance, since the pedestal error voltages  $\delta V_{p1}$  of the PMOS and NMOS transistors are independent and the resulting pedestal error is therefore not cancelled. If the mismatch of the PMOS and NMOS transistors is uncorrelated, the total error voltage is then given by the square root of the sum of the squares of the individual error voltages.

Another potential source of charge injection mismatch is the variation in sampling capacitance. If  $\delta C_S$  is the variation in the sampling capacitance, the voltage error  $\delta V_{p1}$  from charge injection onto mismatched capacitors can be written as

$$\delta V_{p1} \approx -\frac{\alpha C_{ox} WL}{2C_S} \left(\frac{\delta C_S}{C_S}\right) (V_H - V_C - V_T).$$

(2.51)

Typically, this error is small compared to the error from the mismatch of the sampling switches and can therefore be neglected.

The second principal source of error is the feedthrough of control signals via the substrate and parasitic inter-layer capacitances. In analog memories, the input waveform is sampled sequentially onto a bank of memory cells. The capacitive coupling from control signal lines to individual memory cell nodes may not be uniform across the chip and therefore the layout of the circuit must be carefully designed to minimise coupling through parasitic inter-layer capacitances and through the substrate. In addition, perturbations in the power supply, ground, signal, buses can be the cause of memory cell performance mismatch, since the signal is captured at different times in the memory cells of the channel.

### 2.9 Summary

The MOS transistors make one of the best switch realisations available in integrated circuit form. They require small area, dissipate very little power, and provide zero offset, low on resistance and high off resistance. Together with storage capacitors, the NMOS transistors create basic sample and hold circuits necessary for acquiring analog waveforms. A voltage switch can be realised by a single NMOS or PMOS transistor, or with a CMOS transmission gate. One of the most serious limitations of the MOS switches is that error voltages are introduced due to the charge injection and clock feedthrough effect. The CMOS transistor. The clock circuitry for CMOS switches is more complex because of the requirement for a complementary clock which may be difficult to implement in high speed analog circuits. In addition, it is more important to have an uniformity of the individual memory cell responses in one channel than the absolute error voltage. Therefore the use of a MOS transistor as voltage switch in place of a CMOS transmission gate is suitable to assure an uniformity in the channel.

#### 2.9. Summary

In a sample and hold circuit the voltage switch can be inserted in signal path or in signal return path. The error voltage is independent of the input signal level when the switch is placed in signal return path and can therefore be cancelled by a simple subtraction procedure. Furthermore, the sample and hold configuration wherein the switch is placed in signal return path introduces a constant time delay for ac input signals.

The analysis of sample and hold configurations presented in this chapter provides basic ideas for the design of analog memory circuits, as proposed in the following chapter.

# Chapter 3

# **Analog Memory Circuit**

# 3.1 Overview

In this chapter an analog memory circuit for use in high speed data acquisition systems has been introduced. A circuit implementation of the architecture and its theoretical performance are investigated in detail. A short description of the architectures of two chips implemented is presented in Section 3.2. The architecture of the analog memory core is identical for both chips implemented and is described in detail in the following section. The performances of the analog memory are evaluated through a theoretical analysis of dc transfer function, signal range, small signal acquisition bandwidth, acquisition time and leakage current.

# **3.2** Chips Architecture

Two chips for camera electronics of the Cherenkov telescope have been integrated in the Austria Microsystems (AMS) 0.8  $\mu$ m complementary metal oxide semiconductor (CMOS) process with poly-to-poly capacitors. In Table 3.1 are presented the architectures for both chips. The write control circuit as well as the analog memory core are identically for both chips while the read control circuit is different. The analog memory core is described in detail in the following section and the write and read control circuits are discussed in Chapter 5. FASTSAMP-EV was the first experimental chip implemented followed by FASTSAMP-V1 which is more approached to the camera electronics requirements of the Cherenkov telescope.

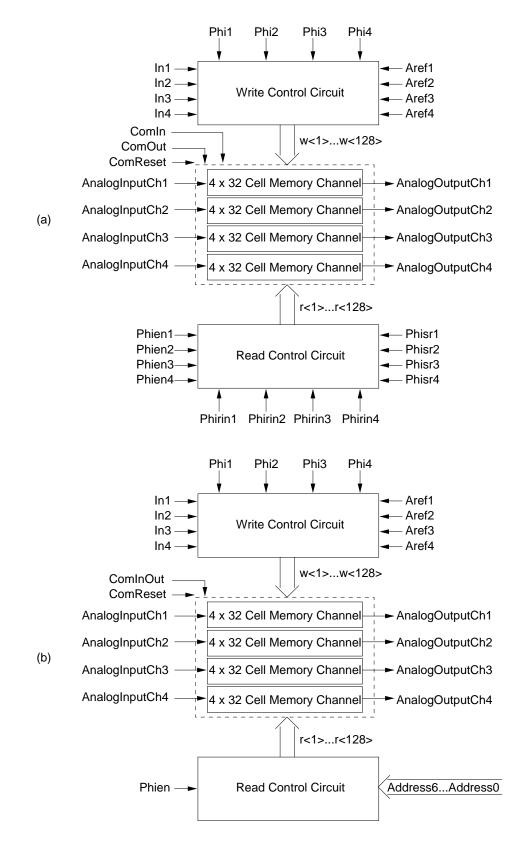

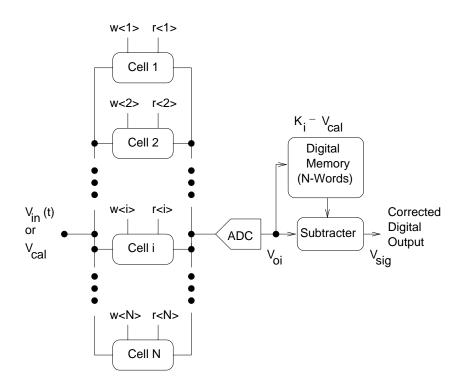

The block diagrams of the chips are shown in Figure 3.1. The analog input signals are AnalogInputCh1 through AnalogInputCh4 while the analog outputs are AnalogOutputCh1 through AnalogOutputCh4. The analog waveforms applied at the four inputs are sampled and stored in the analog memory core which consists of four channels with 128 cells in each channel. The write address signals w < 1 > through w < 128 > are generated in the high speed write control circuit implemented to achieve 500 MHz sampling frequency. The read address signals r < 1 > through r < 128 > are generated in the read control circuit which operates at 100 kHz readout frequency. The

| Chip Name     |         | FASTSAMP-EV                                        | FASTSAMP-V1           |  |

|---------------|---------|----------------------------------------------------|-----------------------|--|

|               |         | $(Fast \ Sampling$                                 | (Fast Sampling        |  |

|               |         | Transmission Recorder                              | Transmission Recorder |  |

|               |         | - $m{E}$ xperimental $m{V}$ ersion)                | - First $V$ ersion)   |  |

|               | Analog  | - 4 channels with 128 memory cells in each channel |                       |  |

|               | Memory  | was proposed for acquiring analog waveforms        |                       |  |

|               | Core    |                                                    |                       |  |

|               | Write   | - sampling rate of 500 MHz                         |                       |  |

| Architectures | Control | - consists of four 32 cell delay chains            |                       |  |

|               | Circuit |                                                    |                       |  |

|               | Read    | - implemented with                                 | - implemented with    |  |

|               | Control | 4 two-phase shift registers                        | a 1 of 128 decoder    |  |

|               | Circuit | - readout frequency of 100 kHz                     |                       |  |

Table 3.1: Architectures for both chips.

other signals which appear in the block diagrams are provided externally.

The two control signals ComIn and ComOut which appear in the block diagram of FASTSAMP-EV chip in Figure 3.1(a) have been replaced by a single external signal ComInOut necessary for FASTSAMP-V1 chip, as illustrated in Figure 3.1(b). Internally, this replacement has been done by using an inverter.

# **3.3** Analog Memory Core

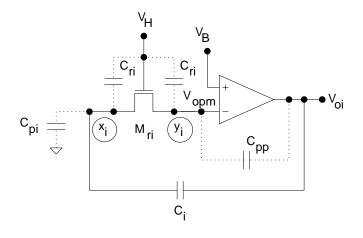

### 3.3.1 Architecture

The proposed architecture of one channel of the analog memory core [26] is shown in Figure 3.2.  $V_B$  and  $V_C$  are dc reference voltages. The operation of the analog memory channel can be described into write and read phases. During the write phase, the switches  $S_{in}$  and  $S_{reset}$  are closed while  $S_{out}$  and read switches  $S_{r1}$  through  $S_{r128}$  are open. The input waveform is then sampled and stored on the storage capacitors  $C_1$  through  $C_{128}$  by sequentially closing and opening the write switches  $S_{w1}$  through  $S_{w128}$ . After the analog input waveform has been stored, the switch  $S_{in}$  is opened and  $S_{out}$  is closed. The analog waveform recorded can be read out by consecutively closing and opening the read switches  $S_{r1}$  through  $S_{r128}$ .

The architecture presented in Figure 3.2 with a single readout amplifier offers a low power dissipation, small area, and minimum cell-to-cell variations. The use of independent write and read address switches for each cell simplifies the write and read control circuits considerably. As suggested in Chapter 2, the write switches are inserted in the signal return path. The capacitors are switched across the amplifier during readout in order to obtain a cell gain that is insensitive to the size of the sampling capacitor. The description and operation of the architecture shown in Figure 3.2 are analysed in the following subsections.

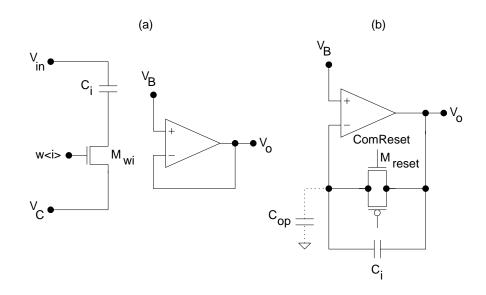

Figure 3.1: Block diagram for (a) FASTSAMP-EV and (b) FASTSAMP-V1 chips.

Figure 3.2: Memory architecture with one amplifier per channel.

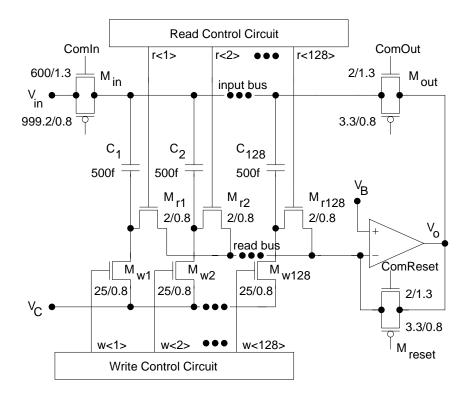

Figure 3.3: Simplified schematic of one analog memory channel.

### 3.3.2 Description

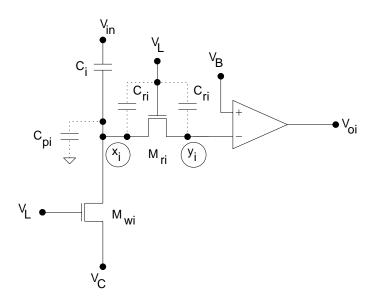

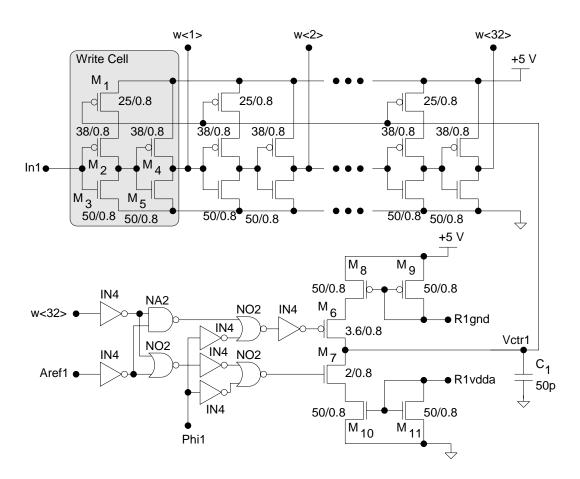

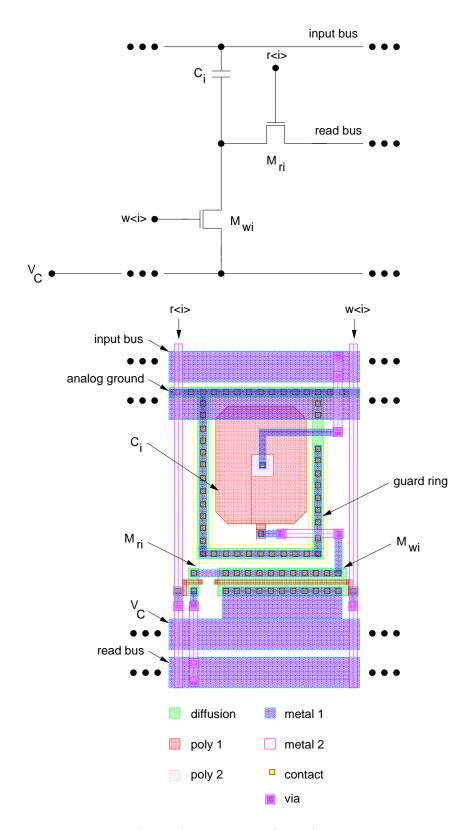

A simplified schematic of one channel of the proposed analog memory [27, 28], comprising 4 blocks of 32 cells, is shown in Figure 3.3. Each memory cell consists of a large write transistor  $M_{wi}$ , a minimum size read transistor  $M_{ri}$ , and a sampling capacitor  $C_i$ . The cells are addressed via write lines w < 1 > through w < 128 > and read lines r < 1 >through r < 128 >. The voltage  $V_C$  is a dc reference common to the sources of all write transistors,  $M_{wi}$ . The switch  $M_{reset}$  serves to configure the operational amplifier as

Figure 3.4: Timing diagram for (a) write and (b) read phases.

a voltage follower in order to force the nodes of the amplifier input and output to the dc bias level  $V_B$  during reset.

The channel dimensions of the NMOS and PMOS transistors comprising the input switch  $M_{in}$  are  $W/L = 600 \ \mu m/1.3 \ \mu m$  and  $W/L = 999.2 \ \mu m/0.8 \ \mu m$ , respectively. As suggested by (2.41) through (2.44), the relative sizes of these devices were chosen so as to minimise the signal dependence of the switch on resistance and the total error voltage. The drawn dimensions of the write and read transistors are  $W/L = 25 \ \mu m/0.8 \ \mu m$  and  $W/L = 2 \ \mu m/0.8 \ \mu m$  (minimum size), respectively. The storage capacitor was chosen of 500 fF and the output amplifier is a folded cascode design of the type described in Chapter 4.

The operation of the circuit can be described into write and read cycles. In the write phase, analog signals applied at the channel input,  $V_{in}$ , are sampled and stored in the memory cells at a high rate. The stored analog information is subsequently read out serially at the channel output,  $V_o$ , at a lower speed.

During the write phase, the switch  $M_{in}$  is turned on, connecting the signal  $V_{in}$  to the input bus, while the switch  $M_{out}$  and the read switches  $M_{r1}$  through  $M_{r128}$  are all off,

Figure 3.5: Analog memory channel with parasitic capacitances.

isolating the input bus from the read bus. The switch  $M_{reset}$  is on to keep the read bus at a defined potential  $V_B = V_C = 2.5$  V during the entire write phase. An analog signal applied at the circuit's input is sampled onto the cell capacitors  $C_i$  by sequentially turning transistors  $M_{w1}$  through  $M_{w128}$  on and off, as illustrated in Figure 3.4(a). Samples of the input waveform at 128 discrete times are thereby stored in the memory channel.

The voltage  $\Delta V_{si}$  stored across the capacitor  $C_i$  in the memory cell  $i, 1 \leq i \leq 128$ , is after the sampling

$$\Delta V_{si} = V_{in} - V_C - V_{pwi}, \qquad (3.1)$$

where  $V_{pwi}$  is the voltage error due to the charge injection and clock feedthrough effect in the switch  $M_{wi}$  during turn off. As derived in Appendix B, with the source and drain terminals of the write transistor at reference voltage  $V_C$  at turn off, the pedestal voltage  $V_{pwi}$  can be written as

$$V_{pwi} = -\frac{C_{wi} + \frac{C_{ox}W_{wi}L_{wi}}{2}}{C_{tot}} \sqrt{\frac{\pi U C_{tot}}{2\beta}} erf\left[\sqrt{\frac{\beta}{2U C_{tot}}} (V_H - V_C - V_T)\right] - \frac{C_{wi}}{C_{wi} + C_{pi} + C_i} (V_C - V_L + V_T)$$

(3.2)

where  $C_{wi}$  is the write transistor gate overlap capacitance,  $C_i$  is the sampling capacitance,  $V_T$  is the threshold voltage,  $V_L$  and  $V_H$  are the low and high levels of the write transistor gate voltage,  $C_{ox}$  is the oxide capacitance per unit area,  $W_{wi}$  and  $L_{wi}$  are the width and length of the write transistor, U is the slew rate of the gate voltage,  $C_{pi}$  is the capacitance associated with the cell sampling capacitor terminal connected to the write switch  $M_{wi}$ ,

$\beta = \mu_n C_{ox} W_{wi} / L_{wi}$ , and  $\mu_n$  is the electron mobility in the channel. The capacitance  $C_{tot}$  is

$$C_{tot} = C_i + C_{pi} + C_{wi} + \frac{C_{ox} W_{wi} L_{wi}}{2}.$$

(3.3)

The important fact of this investigation is that  $V_{pwi}$  remains independent of the input voltage,  $V_{in}$ .

The parasitic capacitances for one analog memory channel are illustrated in Figure 3.5 and listed in Table A.2 of Appendix A. The values have been extracted from the layout of the analog memory core which is identically for both chips. The slew rate of the gate voltage U with a typical value of 5 V/300 ps corresponds to the falling edges (300 ps) of the write address signals. The pedestal voltage  $V_{pwi}$  has been calculated from (3.2),  $V_{pwi} = -130$  mV, in which (-80 mV) represents the charge injection contribution and (-50 mV) due to the clock feedthrough effect.