# RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

KIRCHHOFF-INSTITUT FÜR PHYSIK

## INAUGURAL-DISSERTATION

zur

Erlangung der Doktorwürde

der

Naturwissenschaftlich-Mathematischen

Naturwissenschaftlich-Mathematischen Gesamtfakultät

$\operatorname{der}$

Ruprecht-Karls-Universität Heidelberg

vorgelegt von

Dipl.-Phys. Ulrich Trunk

aus

Heidelberg

Tag der mündlichen Prüfung: 19. Dezember 2000

# Development and Characterisation of the Radiation tolerant HELIX128-2 Readout Chip for the HERA-B Microstrip Detectors

Gutachter:

Prof. Dr. Karl-Tasso Knöpfle Prof. Dr. Volker Lindenstruth

## DISSERTATION

submitted to the

Combined Faculties for the Natural Sciences and for Mathematics

of the Rupertus Carola University of

Heidelberg, Germany

for the degree of

Doctor of Natural Sciences

# Development and Characterisation of the Radiation tolerant HELIX128-2 Readout Chip for the HERA-B Microstrip Detectors

presented by

Diplom-Physicist Ulrich Trunk

born in Heidelberg

Heidelberg, 19. December 2000

Referees:

Prof. Dr. Karl-Tasso Knöpfle Prof. Dr. Volker Lindenstruth

#### Abstract

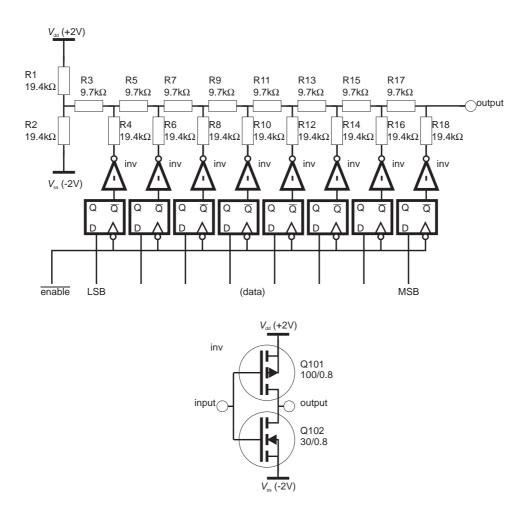

Within this doctoral thesis work, major parts of the preamplifier and readout chip HELIX128-2 have been developed. Among others these circuits included the "Bias Generator" part, which uses digital-to-analogue converters to provide bias currents and control voltages for the amplifier stages of the chip, and a serial interface for programming all the chips operational parameters.

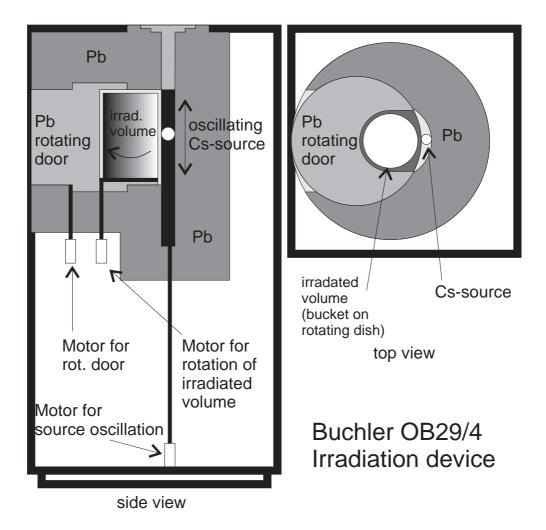

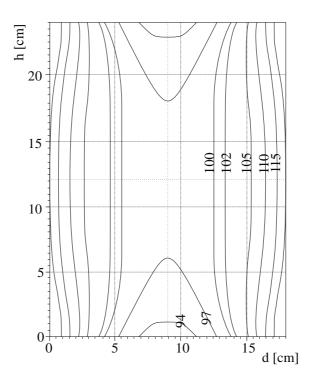

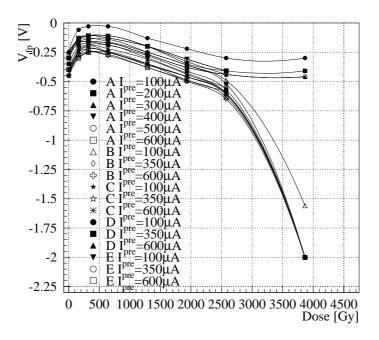

Furthermore, a complete characterisation of the chip, also under irradiation with a  $^{137}$ Cs-source was performed.

Deficiencies found during the necessary tests and measurements resulted in an improvement of the chip within several revision steps: 2.2, 2.3, 3.0, 3.1 and 3.1a.

The modifications required therefore, included all parts of the circuit, except for the frontend and multiplexer. Especially the pipeline r/w logic control has been improved within this work.

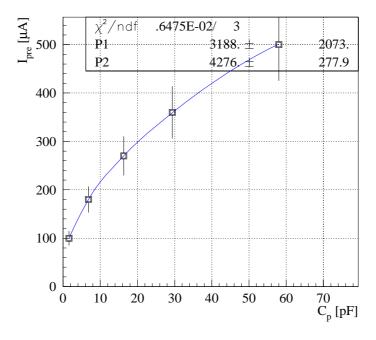

**HELIX128-2** is a low noise VLSI readout chip for 128 channels of silicon strip detectors or Microstrip Gaseous Chambers ( $\overline{ENC} = 462\mathrm{e}^- + 35.4\mathrm{e}^-/\mathrm{pF}$  for a new chip and  $571\mathrm{e}^- + 52.0\mathrm{e}^-/\mathrm{pF}$  at  $3.9\mathrm{kGy}^1$ ). Its architecture implements besides an analogue readout path similar to the CERN RD20/FElix chip (Charge sensitive preamplifier, shaper, analogue memory and serial readout of a triggered samples' channel data) also an undelayed binary readout path. The latter is intended for trigger applications and uses individual comparators following each channel's frontend, and a combination of their data in groups of four channels.

The two parts of this thesis are: A description of the HELIX128-2 with a special emphasis on the circuits' implementation. The second part presents the characterisation results of the chip including the chip performance after irradiation doses up to 3.9kGy.

<sup>&</sup>lt;sup>1</sup>Under the conditions at HERA-B (i.e.  $t_{\rm fall} \approx 100 \, \rm ns$  at  $C_{\rm p} = 16.3 \, \rm pF$  and  $I_{\rm pre} = 350 \, \mu \rm A$ )

### Zusammenfassung

## Entwicklung und Charakterisierung des strahlungstoleranten HELIX128-2 Auslesechips für die HERA-B Mikrostreifenzähler

In der vorliegenden Doktorarbeit wurden große Teile der Schaltung des Verstärker- und Auslesechips HELIX128-2 entwickelt. Dazu gehörten unter anderem der "Bias Generator", eine Schaltung zur Einstellung der Ruheströme und Kontrollspannungen der Verstärkerstufen mit Digital-zu-Analog Wandlern, sowie eine serielle Schnittstelle zum Programmieren der Betriebsparameter des Chips.

Des weiteren wurde eine vollständige Charakterisierung des Chips, einschließlich der Bestrahlung mit einer <sup>137</sup>Cs-Quelle durchgeführt.

Die bei den dazu notwendigen Tests und Messungen gefundenen Unzulänglichkeiten führten zu einer Weiterentwicklung des Chips in verschiedenen Revisionsstufen: 2.2, 2.3, 3.0, 3.1 und 3.1a.

Die dabei eingeflossenen Modifikationen betrafen mit Ausnahme von Eingangsstufe und Multiplexer alle Schaltungsteile. Insbesondere an der Pipeline Schreib-/Lesesteuerung wurden im Rahmen dieser Arbeit Verbesserungen vorgenommen.

**HELIX128-2** ist eine rauscharme ( $\overline{ENC} = 462e^- + 35.4e^-/pF$  für einen neuen Chip,  $\overline{ENC} = 571e^{-} + 52.0e^{-}/pF$  nach  $3.9kGy^{2}$ ) VLSI-Schaltung zur Auslese von 128 Kanälen eines Silizium-Streifenzählers oder einer MSGC<sup>3</sup>. Die Architektur implementiert neben einem analogen Auslesepfad, der dem Konzept des CERN RD20/FElix Chip folgt (Ladungsverstärker, Pulsformer, analoger Zwischenspeicher und serielle Auslese der Kanäle getriggerter Daten) auch über einen unverzögerten binären Datenpfad. Er ist für Triggeranwendungen gedacht und über der Eingangsstufe folgende Komparatoren realisiert, deren Signale in Gruppen von vier Kanälen zusammengefaßt werden.

Die vorliegende Arbeit gliedert sich daher in zwei Teile: Der erste Teil ist die Beschreibung des HELIX128-2 mit besonderem Schwerpunkt auf der Schaltungsimplementation. Der zweite Teil gibt die Ergebnisse der Charakterisierung des Chips wieder und beinhaltet die Chipeigenschaften unter Bestrahlung bis  $3.9 \mathrm{kGy}$ .

<sup>&</sup>lt;sup>2</sup>Unter den Bedingungen des HERA-B Experiments ( $t_{\rm fall} \approx 100 \, \rm ns$  bei  $C_{\rm p} = 16.3 \, \rm pF$  und  $I_{\rm pre} = 350 \mu {\rm A})$   $^3{\rm Mikrostreifen-Proportionalz\"{a}hler}$

# Contents

| In | Introduction 4                          |                                                                        |      |  |  |

|----|-----------------------------------------|------------------------------------------------------------------------|------|--|--|

| 1  | $\mathcal{CP}	ext{-}\mathbf{Violation}$ |                                                                        |      |  |  |

| 2  | The                                     | e HERA-B Experiment                                                    | 9    |  |  |

|    | 2.1                                     | The Silicon Vertex Detector System of HERA- $B$                        | . 14 |  |  |

|    |                                         | 2.1.1 Design Considerations                                            |      |  |  |

|    |                                         | 2.1.2 Geometry and Layout                                              |      |  |  |

|    |                                         | 2.1.3 Mechanics and Construction                                       |      |  |  |

|    | 2.2                                     | Silicon Strip Detectors                                                | . 19 |  |  |

|    |                                         | 2.2.1 Charge Generation                                                | . 19 |  |  |

|    |                                         | 2.2.2 Charge Detection                                                 | . 21 |  |  |

|    |                                         | 2.2.3 Spatial Resolution                                               |      |  |  |

|    | 2.3                                     | The Inner Tracking System of HERA-B                                    |      |  |  |

|    | 2.4                                     | Microstrip Gaseous Chamber Detectors                                   |      |  |  |

|    | 2.5                                     | Microstrip Gaseous Chamber Detectors with Gas Electron Mul-            |      |  |  |

|    |                                         | tiplier                                                                | . 27 |  |  |

| 3  | $\mathbf{The}$                          | e HELIX128-2.2 Readout Chip                                            | 30   |  |  |

|    | 3.1                                     | Requirements                                                           | . 30 |  |  |

|    | 3.2                                     | Overview                                                               | . 32 |  |  |

|    | 3.3                                     | Frontend                                                               | . 35 |  |  |

|    |                                         | 3.3.1 Noise in Amplifiers                                              | . 37 |  |  |

|    |                                         | 3.3.2 The Charge Sensitive Preamplifier                                | . 44 |  |  |

|    |                                         | 3.3.3 The Pulse Shaper Circuit                                         | . 48 |  |  |

|    |                                         | 3.3.4 The Frontend Buffer                                              | . 51 |  |  |

|    | 3.4                                     | The Comparator Circuit                                                 | . 54 |  |  |

|    | 3.5                                     | Pipeline – The Analogue Memory                                         | . 57 |  |  |

|    | 3.6                                     | The Pipeline Readout Amplifier $(Pipeamp)$                             | . 59 |  |  |

|    | 3.7                                     | The Readout Multiplexer                                                | . 63 |  |  |

|    |                                         | 3.7.1 Daisy-Chained Readout of two or more HELIX128                    | . 65 |  |  |

|    | 3.8                                     | The Output Transconductance Amplifier                                  |      |  |  |

|    | 3.9                                     | Pipeline Control Circuit                                               |      |  |  |

|    |                                         | 3.9.1 Incrementer – Calculator and Buffer for valid Pipeline Addresses |      |  |  |

|    |                                         | 3.9.2 Multi-Event Buffer – Derandomiser for Triggered Events           |      |  |  |

|              | 3.10  | The Interface-, Control- and Bias Generator Circuit $(SUFIX)$ . | . 74  |

|--------------|-------|-----------------------------------------------------------------|-------|

|              |       | 3.10.1 The Bias Generator Circuit                               | . 75  |

|              |       | 3.10.2 The Digital Control Circuits                             | . 87  |

|              | 3.11  | Other Circuits                                                  | . 91  |

|              |       | 3.11.1 The Test Pulse Circuit                                   |       |

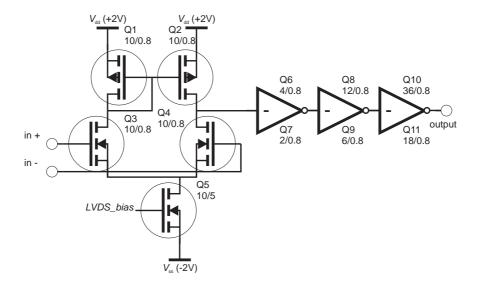

|              |       | 3.11.2 The LVDS Receiver Circuit                                |       |

|              |       |                                                                 |       |

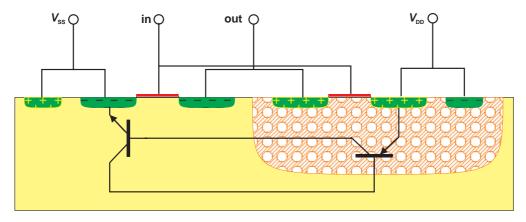

| 4            |       | iation Damage in CMOS Structures                                | 97    |

|              | 4.1   | CMOS Manufacturing Process                                      |       |

|              |       | 4.1.1 Process Steps                                             |       |

|              | 4.2   | MOS transistor characteristics                                  | . 100 |

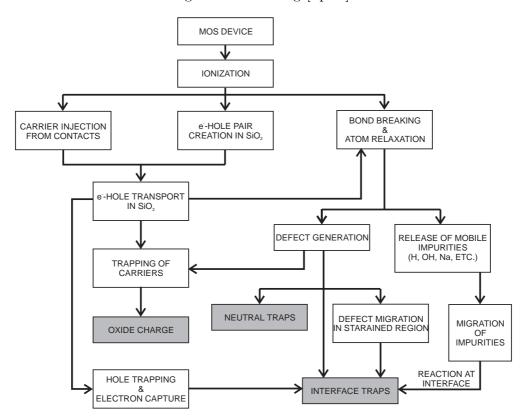

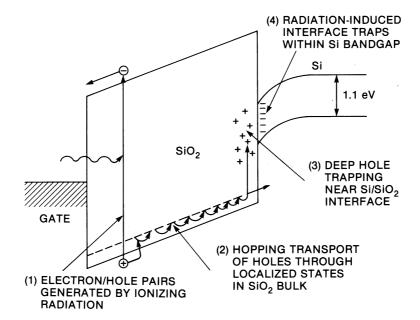

|              | 4.3   | Ionising Damage                                                 | . 102 |

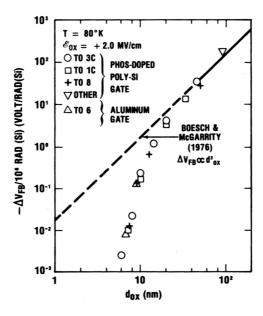

|              |       | 4.3.1 Trapped Charges in Silicon Oxide                          | . 103 |

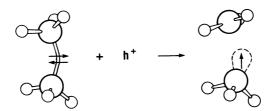

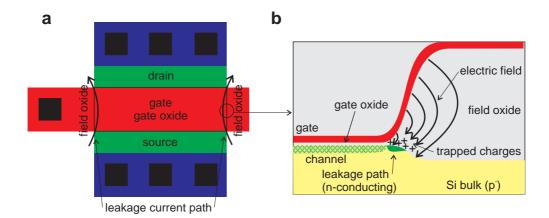

|              |       | 4.3.2 Interface States                                          | . 106 |

|              | 4.4   | Non-Ionising Damage                                             | . 110 |

|              | 4.5   | Total Dose Effect and Annealing                                 | . 111 |

|              | 4.6   | Single-Event effects caused by Radiation                        | . 111 |

|              |       | 4.6.1 Single-Event Upset $(SEU)$                                | . 112 |

|              |       | 4.6.2 Single-Event Latchup $(SEL)$                              |       |

|              |       | - · · · · · · · · · · · · · · · · · · ·                         |       |

| 5            |       | racterisation and Irradiation Results                           | 115   |

|              | 5.1   | CMOS-Process Parameters                                         |       |

|              | 5.2   | Characteristics of the unirradiated Chip                        |       |

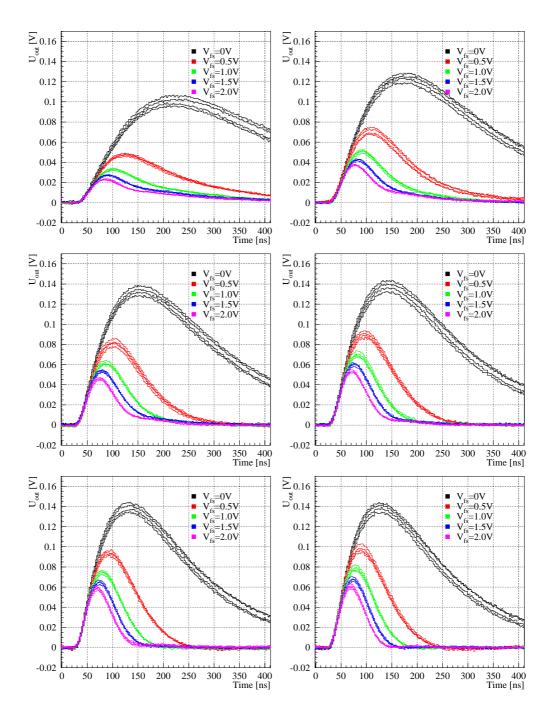

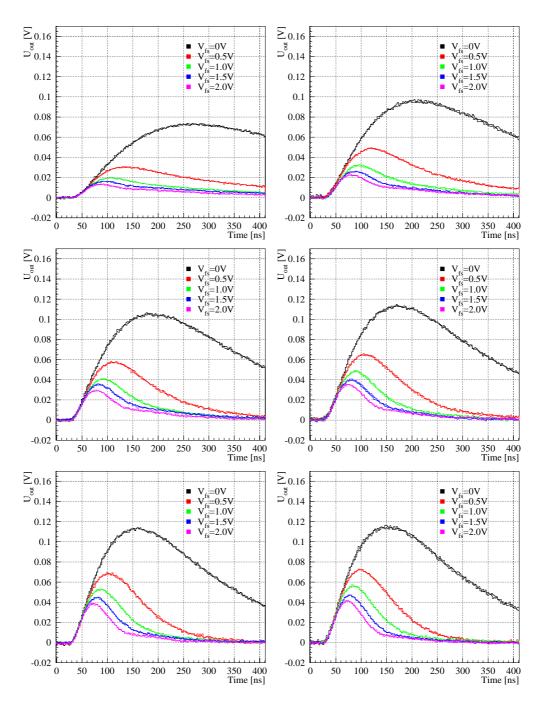

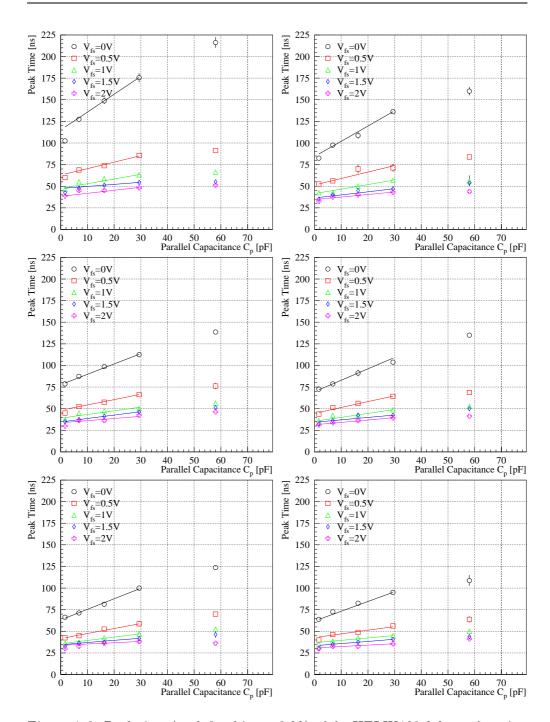

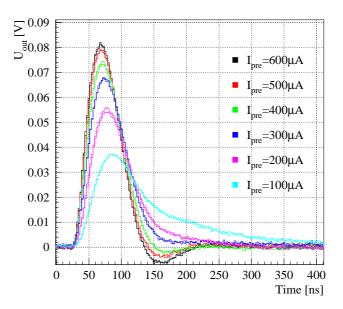

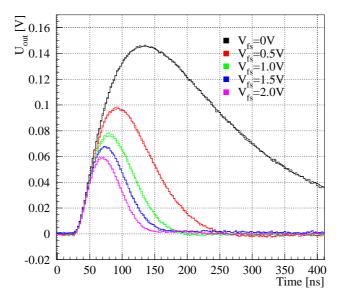

|              |       | 5.2.1 Pulse Shapes and Sensitivity                              | . 125 |

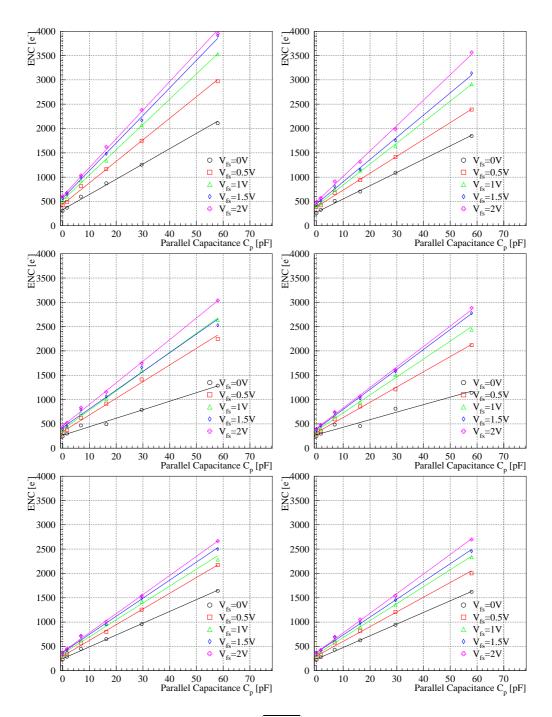

|              |       | 5.2.2 Noise                                                     | . 126 |

|              | 5.3   | Characteristics of the irradiated Chip                          | . 127 |

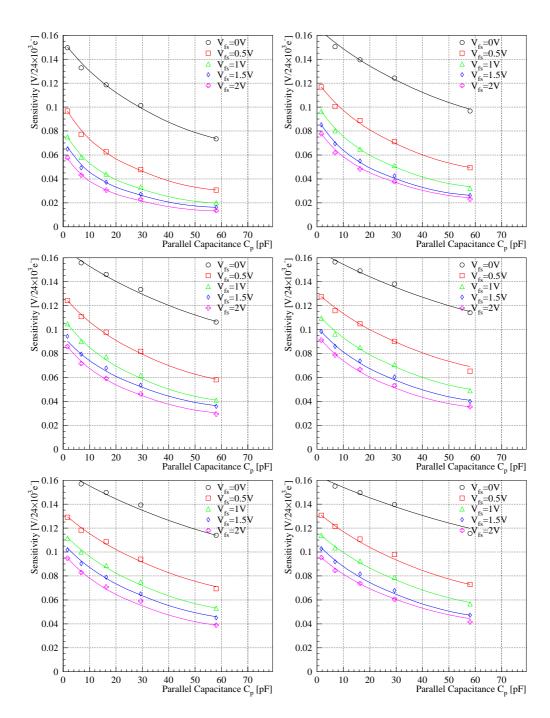

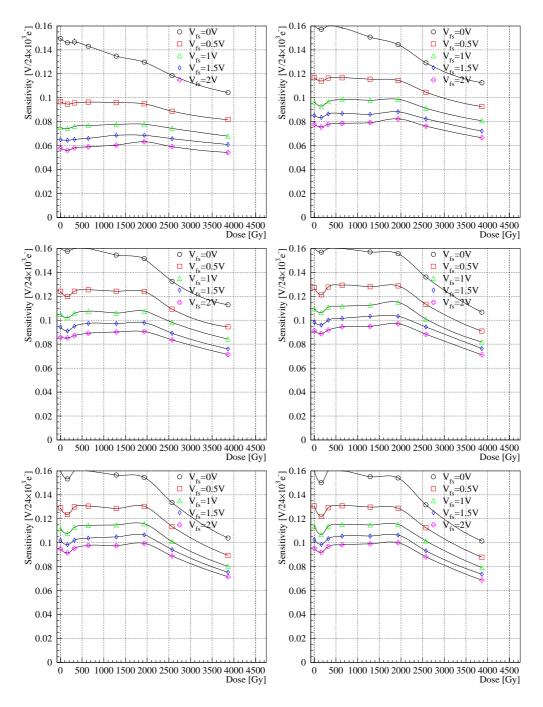

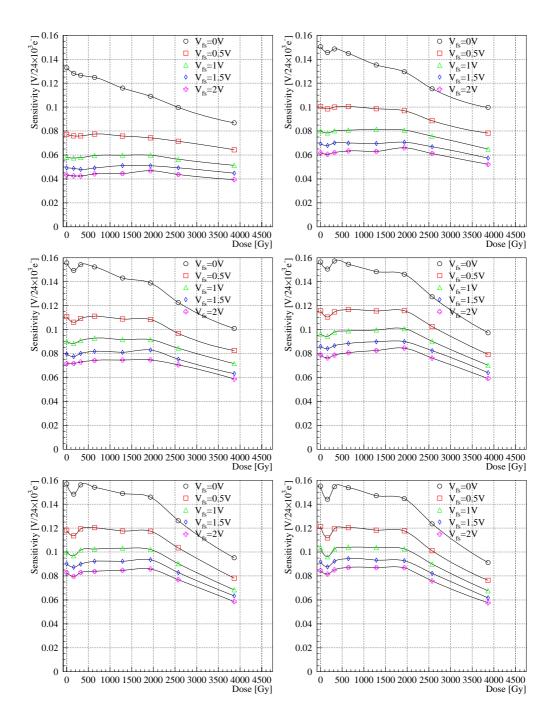

|              |       | 5.3.1 Sensitivity                                               | . 127 |

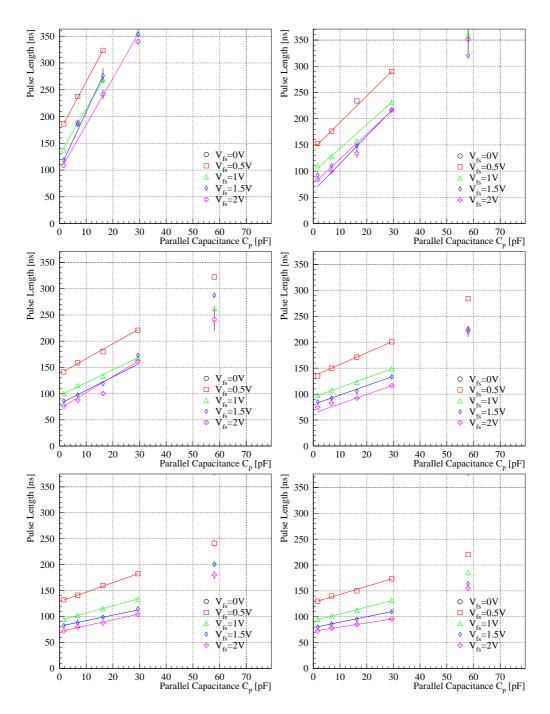

|              |       | 5.3.2 Pulse Shapes                                              | . 128 |

|              |       | 5.3.3 Noise                                                     | . 129 |

|              |       | 5.3.4 Power Consumption                                         | . 129 |

|              |       | 5.3.5 Node Voltages                                             |       |

|              | 5.4   | Conclusions                                                     |       |

| _            | _     |                                                                 |       |

| 6            |       | nmary                                                           | 137   |

|              | Outl  | ook                                                             | . 138 |

| Da           | anksa | agung                                                           | 147   |

| ٨            | Mos   | surement Data                                                   | 148   |

| <b>17.</b>   | TATES | Data Data                                                       | 140   |

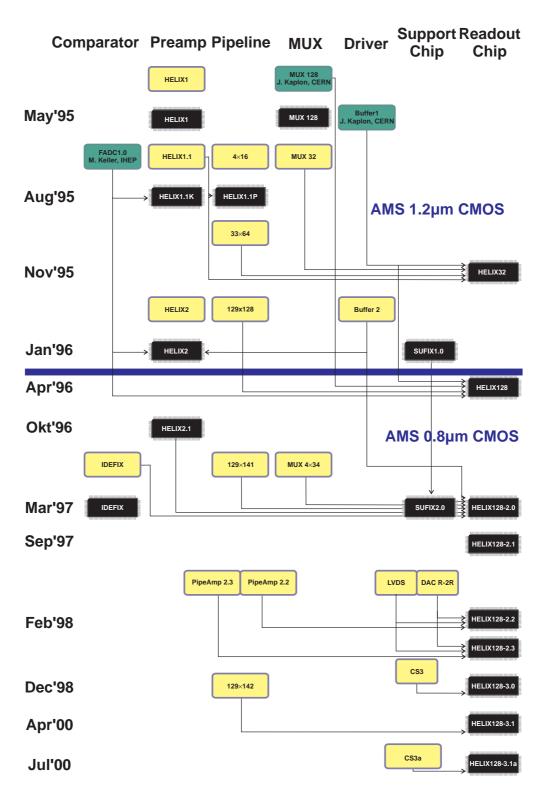

| В            | Hist  | ory: The Family Tree of the HELIX Chip                          | 176   |

| $\mathbf{C}$ | HEI   | LIX128-x Users Manual                                           | 179   |

| D            | Bias  | and Control Voltage Recommendations                             | 236   |

| ${f E}$      | HEI   | LIX128-2 known Bugs and Limitations                             | 243   |

${\bf F} \quad {\bf Verilog\ Source\ of\ HELIX128-2's\ Interface\ and\ Control\ Circuit\,247}$

## Introduction

Todays physics provides us with a broad knowledge about the formation of the universe and the structure of matter. Concerning the latter, the standard model of electroweak interaction has proven incredibly successful by predicting the existence not only of the  $Z^0$ -boson but also of the b- and t-quark. One also knows how to create matter from energy by applying  $E = m \cdot c^2$ , the famous equation found by Albert Einstein in 1905 [Ein05], but due to the conservation of momentum, charge etc. one can only create pairs of particles – one will always be the anti-particle of the other. If an elementary particle meets its anti-particle, they annihilate and revert to energy again.... Thus the fact that the whole universe known to us only consists of matter and lacks any sizable amount of antimatter is still a – admittedly very fortunate – mystery, not yet solved by physics.

There is a glimpse of understanding this paradox: A small asymmetry in mixing and decay of the  $K^0/\overline{K^0}$ -mesons, known as  $\mathcal{CP}$ -Violation [Chr64]. In certain decay channels of their heavier relatives, the  $B^0/\overline{B^0}$ -mesons, this effect is expected to be much larger. Thus it is feasible to study the  $\mathcal{CP}$ -Violation in the system of the B-mesons to extend our knowledge.

The HERA-B experiment [HB93] [HB95] will accomplish this task but has to face some obstacles: Due to their higher mass the cross section for the production of  $B^0$ - $\overline{B^0}$ -pairs with a hadron accelerator is much lower than for K-mesons, higher centre of mass energy allows more concurrent processes producing a higher background of unwanted particles, finally their lifetime is shorter, which makes them travel less before decaying into other particles.

HERA-B therefore has to run at a rather high interaction rate to collect enough statistics in a finite time, it needs a very high spatial resolution to find the (secondary) vertices of the decaying B-mesons, and a very sophisticated trigger algorithm to suppress the high background of concurrent processes. In turn the required high-rate, high-resolution detector components, especially silicon microstrip detectors and microstrip gaseous chambers, need highly integrated high-speed readout electronics. Furthermore, the detector system will collect irradiation doses that put further demands and restrictions on the materials and technologies used. Commercial CMOS  $ASIC^4$  technology and a sophisticated design allowed the realisation of the HELIX128 readout chip especially tailored to meet all these demands, at moderate cost.

The construction and performance of HELIX128 are presented in this work.

<sup>&</sup>lt;sup>4</sup>Application Specific Integrated Circuit

# Chapter 1

# $\mathcal{CP}$ -Violation

For a long time it was assumed that all weak interaction processes are invariant under the following operations:

- Charge conjugation  $\mathcal{C}$

- Parity transformation<sup>2</sup>  $\mathcal{P}$

- Time-reversal<sup>3</sup>  $\mathcal{T}$

Studies of weak decays of nuclei [Wu57] and of pions and muons [Gar57][Fri57] showed that C as well as P-symmetry was not conserved. This can be visualised by applying  $\mathcal{C}$  or  $\mathcal{P}$  transformation on a left-handed<sup>4</sup> neutrino  $\nu_L$ :

$$\begin{array}{c}

\nu_L \xrightarrow{\mathcal{P}} \nu_R \\

\nu_L \xrightarrow{\mathcal{C}} \overline{\nu}_L

\end{array}$$

Neither the right-handed<sup>5</sup> neutrino nor the left-handed antineutrino have been observed. In turn it was believed that symmetry under the product  $\mathcal{CP}$  of both transformations was still conserved, since its result is a right-handed antineutrino – an existing particle:

$$\nu_L \xrightarrow{\mathcal{CP}} \overline{\nu}_R$$

For the  $K^0$ -mesons it made up this simplified scenario: While produced as strangeness eigenstates  $K^0(s=+1)$  and  $\overline{K^0}(s=-1)$  with  $\mathcal{CP}|K^0\rangle = |\overline{K^0}\rangle =$  $-1\cdot |K^0\rangle$ , one of the preferred hadronic decay modes is  $K_S^0\to \pi^+\pi^-$  (lifetime  $\approx 10^{-10}$  s). For the latter,  $\mathcal{CP}|K_S^0\rangle = |K_S^0\rangle$  had to be valid, since  $\mathcal{CP}|\pi^+\pi^-\rangle =$  $|\pi^+\pi^-\rangle$ . The  $K_S^0$  had to be a mixture of  $K^0$  and  $\overline{K^0}$ , and Gell-Mann and Pais

$<sup>^1\</sup>mathrm{particle}$  is replaced by its antiparticle  $^2\mathrm{space}$  reflection, this is needed to reverse all radial-vector like properties

<sup>&</sup>lt;sup>3</sup>inversion of the direction of time (in the 4-dimensional time-space continuum)

<sup>&</sup>lt;sup>4</sup>antiparallel orientation of spin and momentum vectors

<sup>&</sup>lt;sup>5</sup>parallel orientation of spin and momentum vectors

[Gell55] postulated a long-lived  $K_L^0$  which had to be the other linear combination of  $K^0$  and  $\overline{K^0}$ , orthogonal w.r.t.  $K_S^0$ :

$$\mathcal{CP}\left|K_S^0\right\rangle = \mathcal{CP}\left|(K^0 + \overline{K^0})/\sqrt{2}\right\rangle = \left|(\overline{K^0} + K^0)/\sqrt{2}\right\rangle = \left|K_S^0\right\rangle$$

(1.1)

$$\mathcal{CP}\left|K_L^0\right\rangle = \mathcal{CP}\left|(K^0 - \overline{K^0})/\sqrt{2}\right\rangle = \left|(\overline{K^0} - K^0)/\sqrt{2}\right\rangle = -\left|K_L^0\right\rangle \quad (1.2)$$

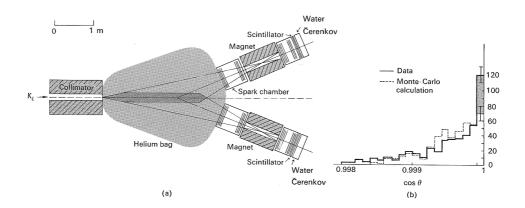

In 1964 Christenson et al. [Chr64] discovered an anomaly in the decay of  $K_L^0$ -mesons: With the apparatus depicted in fig. 1.1 they found besides the preferred decay mode of the  $K_L^0$ -mesons

$$K_L^0 \longrightarrow \pi^0 \pi^+ \pi^-$$

which conserves  $\mathcal{CP}$  symmetry, approximately 50  $\mathcal{CP}$ -violating events with

$$K_L^0 \longrightarrow \pi^+\pi^-.$$

Figure 1.1: (a) Experimental setup of Christenson et al. (1964) demonstrating the decay  $K_L \to \pi^+\pi^-$ . Rare two-pion decays are distinguished from three-pion and leptonic decays by the invariant mass of the pair and the direction  $\theta$  of their resultant momentum vector wrt. the  $K_L$  beam axis. (b)  $\cos(\theta)$  distribution of events with 490 MeV  $< M_{\pi\pi} < 510$  MeV. The shaded deviation from the distribution expected for three-body decays of about 50 events collinear with the beam is due to the  $\mathcal{CP}$ -violating  $\pi^+\pi^-$  decay mode [Per82].

The model of weak interaction – a unitary  $2 \times 2$  matrix parametrised by the Cabbibo Angle  $\Theta_C$  – could not describe this phenomenon since the matrix elements had to be real numbers. A unitary  $3 \times 3$  matrix (now parametrised by 3 angles  $\Theta_1, \Theta_2, \Theta_3$  and a complex phase  $\delta$ , which describes the  $\mathcal{CP}$ -violation) was proposed by Kobayashi and Maskawa in 1973 [Kob73]. It also postulated the existence of a  $3^{\rm rd}$  family of quarks (consisting of top and bottom), which was

found later. This Cabbibo-Kobayashi-Maskawa (CKM) matrix is an important part of today's Standard Model of Electroweak Interaction:

$$\begin{pmatrix} |dl\rangle \\ |sl\rangle \\ |b'\rangle \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \cdot \begin{pmatrix} |u\rangle \\ |c\rangle \\ |t\rangle \end{pmatrix}$$

(1.3)

The transition of a quark  $|q\rangle$  into another quark  $|q'\rangle$  is proportional to  $|V_{qq'}|^2$ , the squared element of the CKM matrix<sup>6</sup>. For  $\mathcal{CP}$ -violating transitions  $|V_{qq'}|^2 \neq 1$  $\left|V_{\overline{q}\,\overline{q'}}^2\right| = \left|V_{qq'}^{*\,2}\right|$  has to be valid, i.e.  $\Im(V_{qq'}) \neq 0$ . A widely used parametrisation of the CKM matrix was suggested by Wolfen-

stein [Wol83] which uses real parameters  $\lambda$ , A,  $\rho$  and  $\eta$ , where  $\lambda = \sin \Theta_C$ :

$$\mathbf{V} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & \lambda^3 A(\rho - \imath \eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & \lambda^2 A \\ \lambda^3 A(1 - \rho - \imath \eta) & -\lambda^2 A & 1 \end{pmatrix} (1.4)$$

Any of the six unitarity conditions, esp.

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0$$

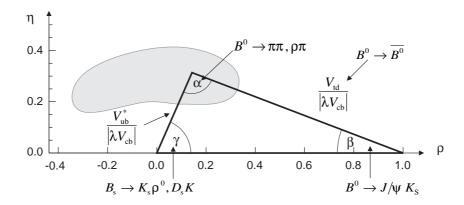

is represented by the so called *Unitarity Triangle* [Cha84] [Jar88] in the  $(\rho, \eta)$ plane of the Wolfenstein parametrisation (fig. 1.2). While two corners of this triangle are fixed at (0,0) and (1,0), the tip is given by  $(\rho,\eta)$  and the sides are  $\propto V_{ub}$  and  $\propto V_{td}$ .  $\mathcal{CP}$ -violation is possible if the area of the triangle is different from zero, i.e.  $\eta \neq 0$ .

Figure 1.2: Unitarity Triangle in the  $\rho - \eta$  plane of the Wolfenstein parametrisation of the CKM matrix. The  $(1-\sigma)$  contour shown constrains the position of the triangle's tip by data given in [Ali93].

Decays of  $B^0/\overline{B^0}$  mesons into a  $\mathcal{CP}$  eigenstate X via a single transition amplitude are predicted to exhibit strong  $\mathcal{CP}$  asymmetries directly related to the

<sup>&</sup>lt;sup>6</sup>Another interpretation of this matrix is a base transformation from the eigenstates of the electroweak interaction to the mass eigenstates of the quarks [Per82].

shape of the *Unitarity Triangle*, independent from poorly known hadronic amplitudes [HB93] [Big89]. Therefore the measurement of these decay modes is very suitable to broaden the understanding of  $\mathcal{CP}$ -violation. The particle-antiparticle asymmetry in these decay modes arises from the interference of the direct decay  $B^0 \to X$  and the decay through mixing  $B^0 \to \overline{B^0} \to X$ . Examples for these decay modes are  $B^0 \to \pi^+\pi^-$  (providing  $\alpha$  in fig. 1.2),  $B^0 \to J/\Psi K_S^0$  (providing  $\beta$ ) and  $B_S \to \rho^0 K_S^0$  (providing  $\gamma$ ). E.g. for the decay  $B^0 \to J/\Psi K_S^0$  (also called "gold plated" decay mode) the relation to  $\beta$  is given by the decay rates

$$n_{B^0 \to J/\Psi + K_S^0}(t) \propto e^{-t} (1 + \sin 2\beta \sin xt)$$

(1.5)

$$\overline{n}_{\overline{B^0} \to J/\Psi + K_S^0}(t) \propto e^{-t} (1 - \sin 2\beta \sin xt). \tag{1.6}$$

The measurement of this  $\mathcal{CP}$  asymmetry in the *gold plated* decay of the neutral B-mesons is the primary objective of the HERA-B experiment.

## Chapter 2

# The HERA-B Experiment

"HERA-B is an experiment designed primarily to search for  $\mathcal{CP}$ -violation in decays of B mesons into the "gold plated" decay mode  $B \to J/\psi + K_S^0$ . The B mesons are produced in interactions of 820 GeV protons in the HERA proton beam with an internal wire target in the beam halo. The use of a halo target results in a minimal disturbance of the ep luminosity operation of HERA and allows the parallel operation of both the ep collider experiments and of HERA-B. Despite the small B meson production cross section, the experiment can accumulate sufficient statistics to detect the rare  $\mathcal{CP}$ -violating B decays, by running at high interaction rates - between 30 and 50MHz - for several years of HERA operation. Among the strong background of "ordinary" proton-nucleus interactions, B-decay candidates are selected by requiring a dilepton in the  $J/\psi$  mass range already at the first trigger level, and refining the signature at higher trigger levels. The detector covers almost  $4\pi$  in the rest frame of the reaction and allows the efficient detection and identification of reaction products. While optimised for the study of the  $B \to J/\psi K_S^0$  mode, the detector and its trigger system are flexible enough to access a wide range of additional physics topics, ranging from B<sub>s</sub> mixing and B hadron spectroscopy to the very detailed investigation of heavy-quark,  $J/\psi$  and  $\Upsilon$  production mechanisms, and to high-statistics investigations of rare charm decay modes."[HB95]

For a long time hadron accelerators have been known to be heavy quark factories, and not only the  $J/\Psi$  but also the  $\Upsilon$  resonances have been discovered in hadron experiments. Even in the range of modest energies available for fixed target experiments the production rates of charm and beauty quarks exceed the rates available at  $e^+e^-$  storage rings. Unfortunately this advantage is bought by the large background of other (undesired) hadronic interactions.

For the HERA-B experiment [HB93] [HB95] an internal target has been chosen. It consists of eight individually adjustable target wires, interacting with the halo (the less populated outer regions) of the 920GeV HERA proton beam. By only using the halo of the proton beam, the luminosity operation of the two ep collider experiments H1 and ZEUS is not restricted. The usage of eight separate target wires enables the experiment to run at event rates of up to 40MHz by allowing on average 4 interactions per bunch crossing (every 96ns). This is necessary since only one  $B^0/\overline{B^0}$  pair is produced in  $1.3 \cdot 10^6$  collisions. And only one out of  $2.3 \cdot 10^3$   $B^0$ -mesons decays into the gold plated

decay channel. Taking inefficiencies of the detector system into account, this yields about  $3 \cdot 10^{11}$  collisions to be observed in order to find one  $B^0$  decaying into that channel. For a measurement of  $sin2\beta$  with an error  $\Delta sin2\beta \approx 0.1$ about 2500 decays of  $B^0$  into the gold plated channel

$$B^0 \longrightarrow J/\Psi + K_S^0 \longrightarrow l^- + l^+ + \pi^+ + \pi^-$$

(2.1)

$$B^{0} \longrightarrow J/\Psi + K_{S}^{0} \longrightarrow l^{-} + l^{+} + \pi^{+} + \pi^{-}

\overline{B^{0}} \longrightarrow J/\Psi + K_{S}^{0} \longrightarrow l^{-} + l^{+} + \pi^{+} + \pi^{-}

(2.1)$$

$l^- + l^+ = {

m lepton}$  pair (i.e.  $e^- + e^+$  or  $\mu^- + \mu^+$ )

have to be observed. Running at an event rate of ≈40MHz this corresponds to almost one year (i.e.  $10^7$ s) of data taking.

Since the final states in eq. 2.1 and 2.2 are the same, B-tagging has to be used to identify the initial particle. b-quarks are always produced as  $b/\overline{b}$ -pairs, thus the flavour of the first quark can be determined from the flavour of the second one.

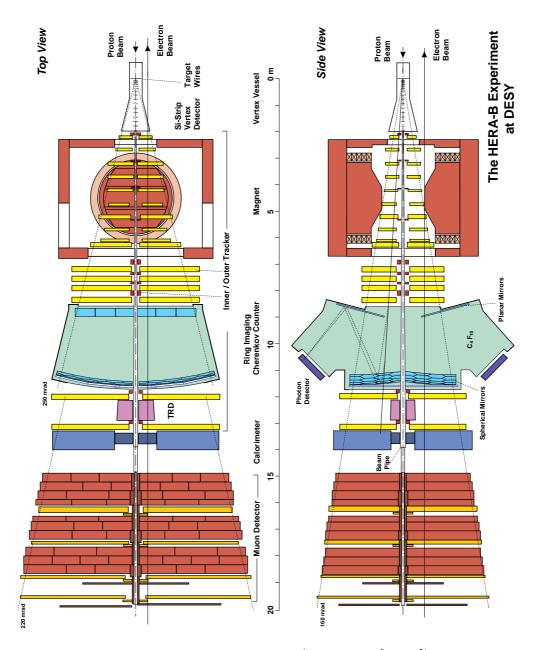

The setup of the HERA-B experiment as a forward spectrometer is depicted in fig. 2.1. To cover about 90% of the  $4\pi$  solid angle in the rest frame of the Bmesons, a geometric acceptance of 220mrad horizontal and 160mrad vertical is required. The detector components downstream of the target are the following:

- The silicon vertex detector (VDS<sup>1</sup>). It uses 16 planes of double-sided silicon detectors with a strip pitch of 51.7μm and 54.6μm (cf. section 2.2). Its main purpose is the reconstruction of the B-mesons decay vertices to separate them from the background of other events. On average the Bmesons travel about 9mm downstream from the target before decaying. The resolution required to reconstruct B mesons is about 10% of that value. The detailed description of the vertex detector is given in section 2.1. 147,456 channels have to be read out.

- The dipole magnet of the HERA-B spectrometer is located 4.5m downstream of the target. Due to the Lorentz-force, charged particles traversing the 2.2Tm field of the spectrometer magnet experience a momentum dependent deflection in the horizontal plane. The direction of the deflection depends on the sign of the particle's charge.

- The inner tracking system (ITR) is described in section 2.3 and reconstructs the tracks of charged particles between the end of the vertex detector (about 2.5m from target) and the electromagnetic calorimeter (about 13.25m downstream wrt. the target). Besides its primary objective of particle tracking, the ITR in conjunction with the magnet also provides a momentum measurement, since charged tracks experience a momentum-dependent deflection in the magnetic field. It covers the area from 10mrad up to 25cm from the beam. In addition to the 18,400 trigger outputs about 135,000 channels of MSGC-GEM<sup>2</sup> detectors (described in section 2.5) have to be read out.

<sup>&</sup>lt;sup>1</sup>Vertex Detector System

$<sup>{}^{2}\</sup>overline{\underline{\underline{M}}}$ icrostrip  $\underline{\underline{G}}$ aseous  $\underline{\underline{C}}$ hamber with  $\underline{\underline{G}}$ as  $\underline{\underline{E}}$ lectron  $\underline{\underline{M}}$ ultiplier

- The outer tracking system (OTR) [Ber99] accomplishes the track reconstruction in the area outside the inner tracking system, i.e. distances from 25cm of the beam to the 220mrad horizontal and 160mrad vertical acceptance of the detector. Like the inner tracking systemthe detector planes are grouped in 11 superlayers. About 96,000 channels of proportional drift tubes with hexagonal cross section have to be read out. The minimum diameter of the drift tubes is restricted to 5mm, a compromise between moderate occupancies and the safety margin for high-voltage arcovers. The intrinsic resolution of the drift tubes is limited to ≈200µm by the inhomogeneous field near the anodes and the position of the wires. The fill gas is a mixture of Ar, CF<sub>4</sub> and CO<sub>2</sub>.

- The high  $p_{\rm T}$  trigger chambers [HB95] are located in and behind the magnet. Three layers of gas-pixel chambers (inner region) and straw chambers with pad readout are used to detect pion pairs with a transverse momentum  $p_{\rm T} \geq 1.5 {\rm GeV/c}$ . This allows HERA-B to trigger  $B^0 \to \pi^+\pi^-$  decays, enabling the measurement of  $\alpha$  in fig. 1.2. About 27,000 channels have to be read out.

- The ring image Čerenkov detector (RICH) [Ham95] serves the purpose of particle identification: Particles traversing a medium at a velocity higher than the speed of light in that particular medium emit photons in the UV or visible region, the so called Cerenkov light. The opening angle of the light cone depends on the particle velocity and the refractive index of the medium. The light cone of a particle is projected as a ring onto a photon detection plane by mirrors. From the diameter of the ring, which is proportional to the opening of the light cone, the particle's velocity can be calculated. Together with the measurement of its energy or momentum, the mass and in turn the particle type can be determined. The distinction of K-mesons from pions by the RICH is of prime importance to tag B decays in the gold plated channel. The HERA-B RICH is located between 8.5m and 12m from the target and uses C<sub>4</sub>F<sub>10</sub> as radiator gas. The photon detection plane is equipped with Hamamatsu H6568 16-anode photomultiplier tubes. Approximately 28,000 channels have to be read out.

- The transition radiation detector (TRD) [Sav98], 12.0m downstream of the target provides an additional instrument for particle identification. Its particular task is hadron rejection in the central area of the electromagnetic calorimeter. Elementary particles emit transition radiation in the soft x-ray region, when crossing the interface between materials of different refractive indices. The X-ray photons are detected by straw tubes filled with a gas mixture based on krypton. The HERA-B TRD has an active area of  $(134 \times 89)$ cm<sup>2</sup> and 36 radiator and straw tube layers. About 7,300 channels have to be read out.

- The electromagnetic calorimeter (ECAL) [Zoc00] is located 13.25m from the target. It is a Shashlik-calorimeter made of alternating layers of

lead resp. tungsten absorber and scintillator material. Incident photons produce a shower of electron-positron pairs and photons. The energy deposited in the scintillators by these secondary particles is converted into UV light which in turn is converted into visible light by shashlik-type wave length shifting fibers and read out with photomultipliers. The main purpose of the ECAL is the detection of electron/positron pairs as "track seeds", i.e. initial points for the track reconstruction. Furthermore it has to provide a hadron/ $e^{\pm}$  discrimination at the level of  $\approx 100$ . The spatial resolution of the calorimeter, which covers an energy range of 2...500GeV, decreases from 2.5mm in the inner region to 17mm for the outer region. The number of readout channels is 6,500.

• The muon system (MUON) [Buc99] consists of 3 hadron absorber layers made of iron and armoured concrete. The detector layers behind each absorber are composed of a central gas-pixel detector and outer proportional tubes with and without pad readout. A fourth detector layer without absorber provides tracking information not deteriorated by muon deflection in the absorber material. The gas mixture used is based on argon. In total 29,500 channels have to be read out.

The trigger system consists of four stages. The first level trigger (FLT) [Ful98] looks for track seeds in the MUON  $(J/\Psi \to \mu^+\mu^-)$ , ECAL  $(J/\Psi \to e^+e^-)$  and High pT  $(B \to \pi^+\pi^-)$  systems. These track candidates are extrapolated and fitted though the ITR and OTR detectors with a Kalman Filter algorithm. The kinematic parameters of the fitted tracks in the vertex are extracted. The decision of the FLT is finally based on the invariant mass of possible track pair combinations. The decision of the FLT has to be taken within 12µs since the detector components can only keep their data pipelined for 128 bunch crossings. Due to the 50kHz input rate of the  $2^{\rm nd}$  level trigger and the input frequency of 10MHz (i.e. the HERA bunch crossing frequency) a suppression of background events by a factor of  $\gtrsim 200$  has to be achieved. The hardware implementation uses LUTs<sup>3</sup> and PLDs<sup>4</sup>.

At the **second level trigger** (SLT) [Ger00] stage the data of the Vertex detector as well as the analogue data of the tracking detectors is available. From this data the exact decay vertices and momentum vectors of  $J/\Psi$ -candidates are calculated. The decision of the SLT is based on the parallelity of the momentum vector and the displacement of the B-vertex wrt. the target. Furthermore the quality of the track fit is taken into account. A rate reduction of  $\approx 100$  within an average latency of 7ms has to be accomplished. It's implementation does no longer use the ADSP21060 (SHARC<sup>TM</sup>) DSPs<sup>5</sup> of the DAQ<sup>6</sup> system as proposed in [HB95], but a farm of 240 commercial personal computers running Linux, which it shares with the third level trigger.

<sup>&</sup>lt;sup>3</sup>Look Up Tables

<sup>&</sup>lt;sup>4</sup>Programmable Logic Devices

<sup>&</sup>lt;sup>5</sup>Digital Signal Processor

<sup>&</sup>lt;sup>6</sup>Data Aquisition

Figure 2.1: HERA-B detector (taken from [HB95])

The **third level trigger** (TLT) runs on the same farm of commercial personal computers as the SLT. Large parts of the TLTs decision are based on information not directly associated with the tracking data, thus enabling triggers for physics outside  $\mathcal{CP}$ -Violation (e.g  $B_s$  mixing). A reduction by a factor of 10 within a latency of 100ms is required to meet the 50Hz input rate of the 4LT.

The **fourth level trigger** (4LT) is also a software implementation. It runs on a dedicated PC farm consisting of 200 CPUs and performs a full event reconstruction, also including the derivation of calibration data. The actual 4<sup>th</sup> level trigger decision is based on the event classification performed during event reconstruction. The 4LTs decision takes 4s on average, yielding a reduction by 2.5. Finally the data is written to disk or tape at a rate of about 20Hz.

## 2.1 The Silicon Vertex Detector System of HERA-B

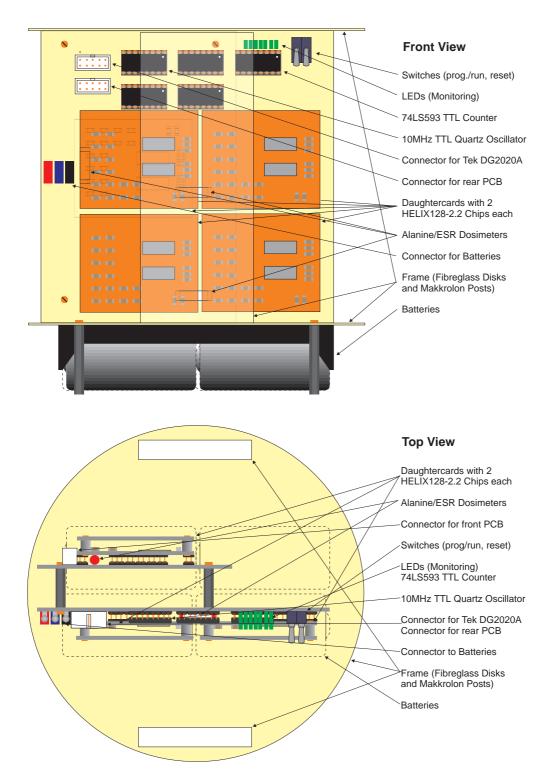

The task of the silicon vertex detector (VDS) is to measure the displacement of the B-meson decay vertices with resolutions of  $\leq 500 \mu m$  in z (beam) direction and  $\leq 25 \mu m$  in the x-y (transverse) plane. A detailed description is given in [Knö98], [Bau98] and [Bau00]. The HERA-B VDS subsystem is read out by HELIX128-2.27 chips.

## 2.1.1 Design Considerations

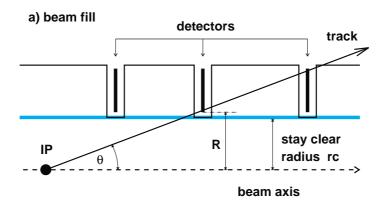

The final limit for the resolution of tracking detectors is not only restricted by their intrinsic resolution, but also by multiple scattering, i.e. a particle does not have to cross all tracking layers on a straight line. In particular a deflection of the particle before or when hitting the first plane of the detector has a deteriorating effect on the vertex resolution. Therefore the thickness of the material traversed by a particle has to be minimised. A straightforward approach to eliminate this problem is to mount target and vertex detector in a common vacuum vessel, which in case of HERA-B would be a part of the HERA proton ring. However, the necessity to shield the detectors from the fields of the beam mirror current and the wake fields in such a vertex vessel (resonant cavity!) prevents the realisation of this solution. Folding a thin shielding around the detector modules as depicted in fig. 2.2 while still placing the detectors in a secondary vacuum leads to the Roman Pot [Bat85] configuration. The shielding can be aligned perpendicular to the detector planes and it can be as thin as 100µm, since there is no pressure drop across the shielding. This way the amount of radiation length the particle has to pass through is kept minimal. The rather high impedance of the vertex vessel has to be short-circuited for the high beam mirror current ( $\geq 2A_{\text{peak}}$  [Sch]) by some additional shielding, to suppress wake fields and their detrimental effects on the beam.

A retractable Roman Pot system, as implemented in the P238 detector at CERN  $Sp\overline{p}S$  [Bra88] provides further improvements, since the detector can be

$<sup>^7{</sup>m First~HELIX128-3.1}$  and HELIX128-3.1a equipped detector modules are expected be installed by the end of 2000 (cf. appendix B and E).

Figure 2.2: Schematic view of a forward vertex detector in a Roman Pot system. The beam pipe is "folded" around the detectors. A retractable Roman Pot system, can be moved closer to the beam during data taking than the *stay clear radius* required for beam fills. Operation close to the beam is required to reach the necessary acceptance for *B*-meson decays. [Knö98].

retracted to a "save" position while filling the accelerator ring. It can be moved very close to the beam during data taking, thus increasing the resolution of the detector system.

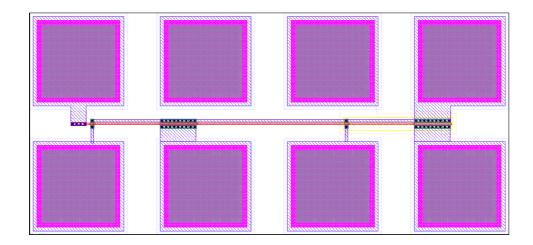

### 2.1.2 Geometry and Layout

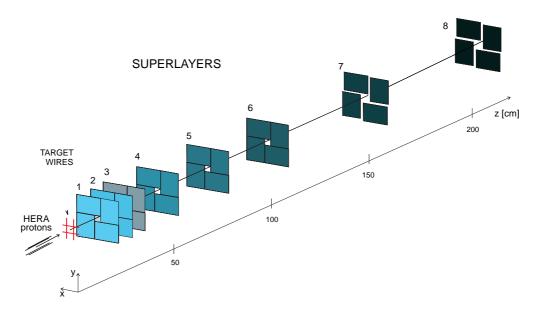

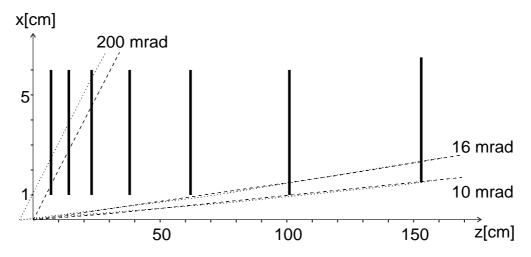

The HERA-B VDS depicted in fig 2.3 provides an angular coverage from 10mrad to 250mrad – consistent with the overall acceptance of the HERA-B detector. It covers 90% of the  $4\pi$  solid angle in the rest frame of the B mesons. Consisting of eight superlayers, made of two double-sided silicon strip detectors per quadrant, the HERA-B VDS typically provides 4 views per superlayer (cf. fig. 2.4). The detectors are  $7\times5\mathrm{cm}^2$ , so they can be cut from 4" wafers. To suppress ambiguities in the track reconstruction, views with a small stereo angle are required. Therefore the strips of the silicon detectors are tilted by  $2.5^{\circ}$  wrt. the detector edges and the two detectors of a superlayer are mounted with the p-sides facing each other. This results in views of  $\pm2.5^{\circ}$ ,  $87.5^{\circ}$  and  $92.5^{\circ}$ .

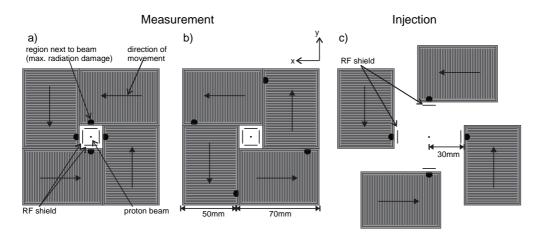

The detectors of the HERA-B VDS can be retracted from the beam axis during fills as shown in fig 2.5. This is necessary to avoid disturbances during

the filling of the ring and to prevent undue radiation damage during that phase. To increase detector lifetime by distributing radiation damage and accumulated dose more evenly, the detectors can be also moved perpendicular to beam and retraction axes into two working positions, which is also depicted in fig. 2.5.

Figure 2.3: Isometric view of the VDS's eight superlayers (taken from [Abt00]).

Figure 2.4: Acceptance of the HERA-B silicon vertex detector (taken from [Rie98]). Only the 7 superlayers inside the vessel are shown.

Cooling of the detectors is required to suppress leakage currents (producing noise) and the "reverse annealing" process in the detectors. Furthermore the heat of the readout electronics, dissipating about 10W per quadrant and superlayer, has to be removed .

Figure 2.5: Arrangement and retraction schema for the 4 detector elements of a sublayer: a) Detector positions for data taking. b) Alternative detector layout. It is obtained from a) by a 5cm clockwise shift of the detectors. It is intended to increase the lifetime of the detectors by evenly distributing radiation damage. c) Retracted detector positions during beam fills.

#### 2.1.3 Mechanics and Construction

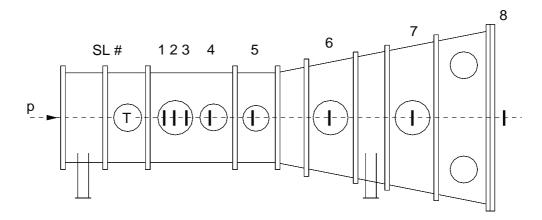

The mechanical backbone of the HERA-B VDS is the conically shaped vertex vessel made of stainless steel. A Schematic is shown in fig. 2.6. The length of the vessel, which also contains the eight wire targets is about 2.5m. Its maximum diameter is 1.16m at the rear end, governed by the 250mrad acceptance of the detector. The upstream end of the vertex vessel flanges to the HERA proton beam line system. The rear end is closed with a spherically shaped exit window made of aluminium. The exit window is only 3mm thick and welded to the 0.5mm thick beam pipe running through all other parts of the HERA-B experiment to minimise radiation length. Four flanges per quadrant allow the Roman Pots containing the silicon detectors to protrude into the beam region. Retraction and tangential movement of the detectors is accomplished by bellows and spindle gear driven linear bearings attached to the vessel. Detector positions are controlled by commercial electromechanic linear gauges [Brä]. The vacuum inside the vessel is  $< 10^{-8}$  mbar, while the secondary vacuum inside the Roman Pots is 10<sup>-6</sup>mbar. Four bands made of aluminum coated stainless steel foil running along the beam from the target to the exit window carry the beam mirror current. They provide suppression of wake fields inside the vertex vessel and are retracted together with the detectors during beam fills. The bands are only 5µm thick, but amount to a radiation length of  $X/X_0 \approx 3\%$  at 10mrad, i.e. in the worst case.

The detector modules of the 8th superlayer are mounted on the rear end of the *vertex vessel*, outside the exit window. Since they are mounted outside the beam pipe, a retraction mechanism is not required.

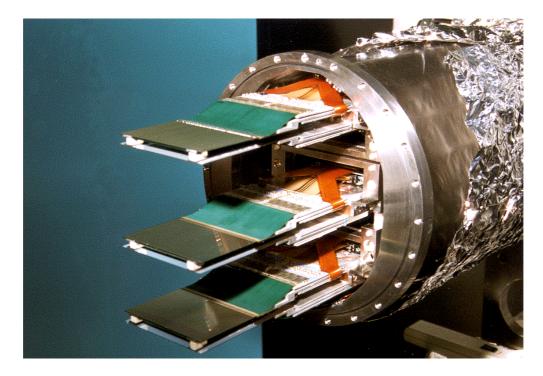

Detectors of one quadrant of the first three superlayers are depicted in fig. 2.7.

Figure 2.6: Drawing of the *vertex vessel*. The target (T) and the detectors' (I) Roman Pots protrude into the vessel through flanges, which are also located on the top and bottom sides of the vessel.

Figure 2.7: Detector modules (one quadrant of the first three superlayers) with two double-sided strip detectors per superlayer. The length of the carbon fibre carriers varies from 150mm for the detectors next to the target (shown) to 430mm for the most downstream ones, which also have separated Roman Pots.

## 2.2 Silicon Strip Detectors

Besides silicon, there are only a few other materials which might be used for a high resolution tracking detector like the HERA-B VDS. The alternatives are gallium-arsenide (GaAs) (or other III-V semiconductors) and diamond. Besides their higher cost, their primary ionisation per radiation length is smaller than  $7800 \frac{e^-/\text{hole pairs}}{0.1\% X_0 \ MIP}$  [PDG96] generated in silicon.

## 2.2.1 Charge Generation

Charged elementary particles traversing matter interact with the electrons and nuclei contained therein. This fact on the one hand enables us to build detectors for these particles, on the other hand, it sets a limit for the spatial resolution of these detectors, as already pointed out in sect. 2.1.1. There are two categories of energy loss a charged elementary particle experiences when interacting with matter:

- Non-ionising energy loss like Čerenkov radiation, Bremsstrahlung and Pair Production in the relativistic energy range and Phonon Excitation at lower energies.

- Ionising energy loss.

For all electromagnetically interacting particles, ionisation is the main contribution to their energy loss.

The mean ionising energy loss per unit path length, also called *stopping power* is given by the Bethe-Bloch formula [Bet33][PDG00]:

$$\left\langle \frac{\partial E}{\partial x}(E) \right\rangle = 4\pi r_e^2 m_e c^2 N_{\rm A} \frac{Z}{A} \rho \frac{z^2}{\beta^2} \left( \ln \left( \frac{2m_e c^2 \beta^2}{I(1-\beta^2)} \right) - \beta^2 \right)$$

(2.3)

E = projectile energy (in keV)

$\beta = v/c$  projectile velocity

z = projectile charge (in e)

x = path length (in cm)

$r_e = 2.82 \cdot 10^{-13} \mathrm{cm} = \mathrm{classical}$  electron radius

$m_e = 511 \text{keV/c}^2 = \text{electron rest mass}$

$N_{\rm A} = 6.02 \cdot 10^{23} \, \rm mol^{-1} = Avogadro's number$

Z = atomic number of the medium (Si: Z = 14)

A = atomic weight of the medium (Si: A = 28.1u = 28.1g/mol)

$\rho=$  mass density of the medium (Si:  $\rho=2.7 g/cm^3)$

I = average ionisation potential (Si: <math>I = 172eV)

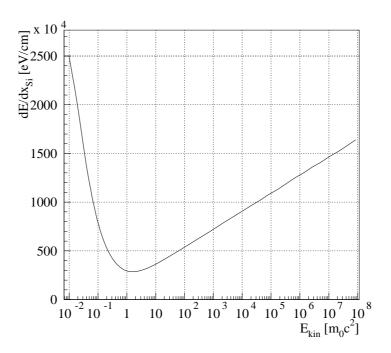

Fig. 2.8 shows the specific energy loss of silicon. As expected from eq. 2.3, the energy loss shows a  $1/\beta^2$  increase at low energies. This behaviour causes the so-called Braqq-peak: A particle stopped in the material has lost most of

its energy at the very end of the track. At relativistic energies the  $\ln\left(\frac{\beta^2}{1-\beta^2}\right)$  term in eq. 2.3 causes the specific energy loss to increase again. A particle with an energy corresponding to the minimum of the curve is called a *minimum ionising particle* (MIP). Most particles encountered in HERA-B are in that energy region.

Figure 2.8: Stopping Power (energy loss per unit length) of Silicon (eq. 2.3).

The distribution of the energy loss per unit path length  $\frac{\partial E}{\partial x}$  is described by the Landau distribution [Lan44], which is highly asymmetric and shows a long tail at high energies. The shape of the distribution arises from so-called  $\delta$ -electrons, which occasionally receive a high momentum transfer from the incident particle. These  $\delta$ -electrons can travel some 10µm in silicon, causing secondary ionisation along their path and thus deteriorating the spatial resolution of a detector. The variance (i.e. width) of the Landau distribution is much smaller than the  $\sqrt{n_e}$  variance of the Poisson distribution ( $n_e$  = number of electron/hole pairs produced), which describes counting processes. The variance of the Landau distribution can be related to the variance of the Poisson distribution by the  $Fano-factor\ F\ [Kno97]$ :

$$var(Q) = \sigma^{2}(Q) = F\langle Q \rangle = F\frac{\langle E \rangle}{\epsilon} \cdot (2q_{e})^{2}$$

$$\sigma(Q) = \sqrt{F \cdot \langle Q \rangle} = \sqrt{F \cdot \overline{n_{e}}} \cdot 2q_{e}$$

(2.4)

$$\iff \qquad \sigma(Q) = \sqrt{F \cdot \langle Q \rangle} = \sqrt{F \cdot \overline{n_e}} \cdot 2q_e \qquad (2.5)$$

$\langle E \rangle$  = mean energy loss of the projectile

$\langle Q \rangle$  = mean charge induced by the projectile

F = Fano-factor (Si: F = 0.084...0.143)

$\epsilon = \text{energy to create one electron-hole pair (Si: } \epsilon = 3.6 \text{eV})$

$q_e = 1.602 \cdot 10^{-19} \,\mathrm{C} = \mathrm{elementary\ charge}$

$\overline{n_e}$  = mean number of electron-hole pairs produced

The mean energy loss per unit path of a minimum ionising particle of elementary charge  $q_e$  (e.g. a 1...2MeV electron) in silicon is  $\langle \frac{\partial E}{\partial x} \rangle \approx 390 \text{eV}/\mu\text{m}$ [PDG84] or 110  $e^-$ -hole pairs per µm on average. Due to the large asymmetry of the Landau distribution, the most probable energy loss per unit path length is  $290 \text{eV/}\mu\text{m}$  or  $82 e^-$ -hole pairs per  $\mu\text{m}$ . In  $300 \mu\text{m}$  of silicon, which is the usual thickness of commercial wafers, this amounts to 88keV or 24600  $e^-$ -hole pairs. It should be mentioned that the average energy  $\epsilon$  to create an electron-hole pair is 3.6eV, which is larger than the bandgap of 1.12eV.

#### 2.2.2Charge Detection

To separate electrons and holes an electric field has to be present. Otherwise electrons and holes will recombine again, creating photons and phonons. Unfortunately applying a voltage to intrinsic silicon causes a significant current superimposed to the signal of the detected particle. It is mainly due to charge carrier injection at the contacts, but there is also a thermally generated population of electrons in the conduction band (cf. tab. 2.1) and the same number of holes in the valence band, contributing to conductivity.

| Atomic Weight                                      | 28.09u                                       |

|----------------------------------------------------|----------------------------------------------|

| Crystal Lattice                                    | diamond                                      |

| Lattice Constant                                   | 5.43Å                                        |

| Relative Dielectric Constant $\epsilon_{\rm r}$    | 11.9                                         |

| Breakdown Field Strength                           | $\approx 3 \cdot 10^7 \mathrm{V/m}$          |

| Bandgap $(T = 300 \text{K})$                       | 1.12eV                                       |

| Intrinsic Charge Carrier Density $(T = 300K)$      | $1.45 \cdot 10^{10} \mathrm{cm}^{-3}$        |

| n-Substrate Doping Concentration                   | $1.5 \dots 2 \cdot 10^{12} \mathrm{cm}^{-3}$ |

| Electron Mobility $\mu_e \ (T = 300 \text{K})$     | $1380 \mathrm{cm}^2/\mathrm{Vs}$             |

| Electron Diffusion Constant $D_n$ $(T = 300K)$     | $\approx 35 \mathrm{cm}^2/\mathrm{s}$        |

| Hole Mobility $\mu_{\rm p}~(T=300{\rm K})$         | $450 \mathrm{cm}^2/\mathrm{Vs}$              |

| Hole Diffusion Constant $D_{\rm p}~(T=300{\rm K})$ | $\approx 11 \text{cm}^2/\text{s}$            |

Table 2.1: Properties of silicon used for Detectors [Sze81]

To suppress this current, contacts to the intrinsic silicon have to be doped, i.e. some silicon atoms are replaced with elements having a different number of electrons in their outermost shell. Doping with elements of the III<sup>rd</sup> main group in the periodic table of elements ("acceptors" like boron) will cause holes in the valence band (p-type silicon) and those of the V<sup>th</sup> main group ("donors" like arsenic and phosphorus) will create electrons in the conduction band (n-type silicon). The charge carriers created by doping the silicon (majority carriers) will outnumber the carriers of opposite charge intrinsic to the silicon (minority carriers) by several orders of magnitude. As a result the minority carriers will (almost) completely recombine, leaving only the majority carriers for conduction.

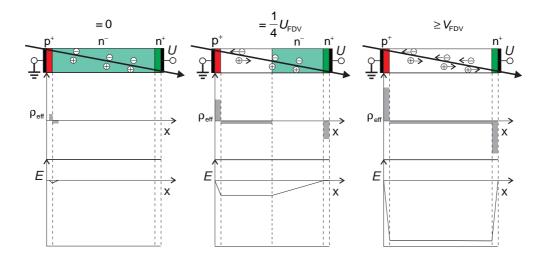

Applying a positive voltage to the n-doped part of the diode depicted in fig. 2.9 causes a region of the depth d, the so-called pn-junction, to be depleted from all charge carriers [Ash81]:

$$d_{\rm p,n} = \sqrt{\frac{2\epsilon_0 \epsilon_{\rm r} (V_0 - V_{\rm D})}{q_e (n_{\rm D} + n_{\rm A})}} \frac{n_{\rm A}}{n_{\rm D}}$$

(2.6)

$d_{\mathrm{p,n}}=\mathrm{depth}$  of the depletion layer (in n and p doped regions)

$\epsilon_0 \epsilon_{

m r} = {

m dielectric\ constant}$

$n_{\rm A}={

m acceptor}$  concentration

$n_{\rm D}={

m donor\ concentration}$

$V_{\mathrm{D}} = \mathrm{diffusion} \ \mathrm{voltage}$

$V_0 = {\it external voltage}$

Figure 2.9: Principle, effective space charge density  $\rho_{\rm eff}$  and electric field E of a silicon detector (pin-diode) for different bias voltages. Only the electron-hole pairs generated in the depleted region ( $E \neq 0$ ) are separated and cause a signal.  $V_{\rm FDV}$  is the full depletion voltage.

E.g. for p-type silicon  $(n_A \gg n_D, V_0 \gg V_D)$  using the specific resistivity

$$\rho_{\rm n} = \frac{1}{q_e \overline{\mu}_{\rm n} n_{\rm D}} \tag{2.7}$$

$\overline{\mu}_n$  = electron mobility

eq. 2.6 can be simplified:

$$d_{\rm n} = \sqrt{\frac{2\epsilon_0 \epsilon_{\rm r} V_0}{q_e n_{\rm D}}} = \sqrt{2\epsilon_0 \epsilon_{\rm r} \overline{\mu}_{\rm n} \rho_{\rm n} V_0}$$

(2.8)

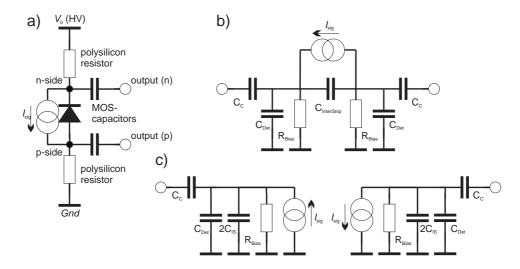

The depletion grows proportional to the square root of the reverse voltage  $V_0$  and the capacitance of the pn-junction decreases  $C_{\rm pn} \propto 1/\sqrt{V_0}^{-8}$ . To fully deplete a silicon wafer of 300µm thickness about 40...140V are required. Assuming a homogeneous charge distribution along the particles track, the signal of a silicon detector can be approximated by the superposition of two rectangular current pulses: A short one ( $\approx 175 \, \mathrm{nA} \times 10 \, \mathrm{ns}$ ) caused by the electrons and a long one ( $\approx 70 \, \mathrm{nA} \times 25 \, \mathrm{ns}$ ) due to the holes [PDG00]. Since the signal is a current the depletion voltage has to be supplied via bias resistors, which leads to the equivalent circuit depicted in fig. 2.10.

Figure 2.10: a) Equivalent circuit of a silicon detector with bias resistors and AC coupling. The change in the voltage drop over  $R_{\text{bias}}$  due to radiation damage requires AC coupling of the readout electronics. b), c) small signal models of a)

Due to radiation damage (cf. chapter 4) the  $n^-$  substrate of detectors used in HERA-B turns into  $p^-$  silicon when subjected to a fluence  $\Phi \gtrsim 3.5 \cdot 10^{12} {\rm cm}^{-2}$  [Rie98]. Furthermore radiation damage also increases the leakage current ( $I_{\rm leak} \propto \Phi$  [Lut99]), which is removed by AC-coupling of the readout electronics. The leakage current is the only *intrinsic* noise source of a silicon

<sup>&</sup>lt;sup>8</sup>This dependency is used e.g. for voltage controlled oscillators or filters (VCO, VCF).

detector, but the detector capacitance together with the principle of a charge sensitive amplifier accounts for an additional noise contribution (cf. eq. 3.16).

## 2.2.3 Spatial Resolution

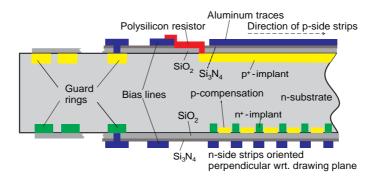

To obtain a spatial resolution from a silicon detector, the heavily doped contacts have to be segmented. E.g. dividing the n<sup>+</sup> and p<sup>+</sup>-implants into orthogonal strips results in a double-sided silicon strip detector as the ones used in the HERA-B VDS depicted in fig. 2.11. It should be denoted that the e.g. for detectors made from an n-type wafer, the region between the n<sup>+</sup> implants can not be depleted. Thus the strips have to be isolated by an additional p-implant.

Figure 2.11: Cross section of a silicon strip detector (not to scale) taken from [Rie98].

The spatial resolution of such a detector for single strip hits is given by [Lut87]:

$$\sigma_x = \frac{\Delta x}{\sqrt{12}} \tag{2.9}$$

$\Delta x = \mathrm{strip} \ \mathrm{pitch}$

Fortunately the charge is usually distributed among two or more strips, enabling interpolation by calculating the charges' centre of gravity. Assuming a rectangular charge distribution having a width equal to the strip pitch  $\Delta x$  and a finite signal to noise ratio, interpolation over n strips yields a resolution of [Lut87]:

$$\sigma_x^2 = \left(\frac{\Delta x}{S/N}\right)^2 \sum_{i=1}^n \left(\frac{x_1 - \overline{x}}{\Delta x} \left(i - 1\right)\right)^2 \tag{2.10}$$

$\Delta x = \mathrm{strip} \ \mathrm{pitch}$

S/N = signal to noise ratio

$x_1 = \text{position of the } 1^{\text{st}} \text{ strip used for calculation}$

$\overline{x}$  = calculated centre of gravity

The best resolution is obtained when the particle hits exactly between two adjacent strips with only their signals evaluated. Eq. 2.10 then yields

$$\sigma_x = \frac{\Delta x}{\sqrt{2} \cdot S/N}.\tag{2.11}$$

For a strip pitch of 50µm and a S/N = 20 the calculated resolution is  $\sigma_x = \frac{50\mu\text{m}}{\sqrt{2}\cdot20} = 1.8\mu\text{m}$ . However, inclined tracks, the Landau-distributed charge generation and quantisation errors of ADCs employed in subsequent DAQ stages have not been taken into account for this calculation. In practical detector operation resolutions of  $\lesssim 10\mu\text{m}$  are reached.

## 2.3 The Inner Tracking System of HERA-B

The track information of the inner tracking system is used to connect hits in the calorimeter to the vertex detector, and thus has to provide binary information for the L1 trigger as well as (higher resolution) analogue data required for tracking and momentum measurement.

The inner tracking detector is divided into 48 layers, 36 between the silicon vertex detector and the RICH, the remaining 12 between RICH and the calorimeter (cf. fig. 2.1). Each of these layers consists of four MSGC-GEM detectors, each covering one quadrant around the beam pipe [HB95].

The mechanical structure of the ITR consists of carbon fibre composite plates attached to the support structure of the OTR, with an MSGC-GEM detector on either side. Since these detectors cover the same quadrant, four of these plates form two layers of the ITR. Besides the detectors, the carrier plates also hold HV supply circuitry and gas supply tubing. For detector readout three readout boards, each equipped with two HELIX128 chips, connect to one MSGC. These six readout boards together with the subsequent "trigger driver board" are also mounted to the support plates.

## 2.4 Microstrip Gaseous Chamber Detectors

Microstrip Gaseous Chambers (MSGC) [Oed88] are derived from MWPCs<sup>9</sup> [Cha70] [Cha68] and share the same principle of operation. The difference is that the anode wires of the proportional chamber are replaced by a planar anode structure on top of an insulating substrate. Created with photolithographic techniques, structures having an anode strip pitch of  $\leq 300 \mu$ m can be produced.

Eq. 2.3 describes the ionisation caused by a particle traversing matter. In case of gaseous media, electrons and ions are created. Despite the relatively low ionisation energies of typical fill gases ( $I_{\rm Ar/CH_4} \approx 30 {\rm eV}$ ), the low density of the media reduces the primary ionisation to about  $8.5e^-$ -ion pairs per mm. Applying a constant electric field  $\vec{E}$ , electrons and ions will drift towards anode

<sup>9</sup>Multi Wire Proportional Chamber

or drift electrode with a constant velocity given by [Sau91]:

$$\vec{v}_{\rm d} = \frac{q_e \vec{E}}{\sqrt{2m}\rho\sigma(\bar{\epsilon})\sqrt{\bar{\epsilon}}} \tag{2.12}$$

$\vec{E} = \text{electric field}$

m =mass of the ion or electron

$\rho$  = molecular density of the gas

$\sigma(\overline{\epsilon}) = \text{cross section for scattering}$

$\overline{\epsilon}$  = mean energy of the ion or electron

In the vicinity of the anodes the electric field is strong enough for secondary ionsation, causing an avalanche of electrons and ions. The electric field in this region can be approximated by a cylindrical capacitor  $(E(r) = \frac{1}{\ln(r_a/r_b)} \frac{V_a}{r})$  with radii  $r_a$  (inner) and  $r_b$  (outer). The multiplication of the small initial charges by secondary ionisation in the region of the very high electric field near the anodes is given by the the Diethorn-formula [Die56]:

$$a = \exp\left[\frac{V_{\rm a}}{\ln\left(r_{\rm b}/r_{\rm a}\right)} \frac{\ln 2}{\Delta V} \ln\left(\frac{V_{\rm a}}{pr_{\rm a}K \ln\left(r_{\rm a}/r_{\rm b}\right)}\right)\right]$$

(2.13)

$V_{\rm a}={

m applied}$  high Voltage

$r_{\rm a}=$  anode radius ( $r_{\rm a}\approx 10\mu {\rm m}$  for MSGCs)

$r_{\rm b}={

m cathode\ radius\ }(r_{\rm b}\leq 120\mu{

m m\ for\ MSGCs})$

p = gas pressure

$\Delta V, K = {

m gas\ parameters}$

Usual values for a are in the order of several thousands.

The secondary ionisation process also causes UV-light due to the de-excitation of freshly ionised atoms. To avoid ionisation by these UV photons, which would cause an avalanche of ionisation filling (and probably destroying) the whole detector, the photons have to be absorbed by a "quencher" gas (e.g. CH<sub>4</sub>) added to the gas mixture.

In case of a proportional detector, the signal to noise ratio does not only depend on the Landau-distributed primary charge, but also on the Polya-distribution describing fluctuations in the gas multiplication (i.e. the avalanche size). According to [Kno97] the Polya-distribution can also be related to Poisson statistics:

$$S/N = \frac{Q}{\sigma(Q)} = \frac{\sqrt{n}}{\sqrt{F+b}} \tag{2.14}$$

$n = \text{number of primary electron-ion pairs } (\approx 25 \text{ for an MSGC})$

$F = \text{Fano-factor} (F \approx 0.17)$

$b = \text{factor for Polya-distribution } (b \approx 0.5)$

Applying eq. 2.10 to the values given above yields S/N of about 6, and a spatial resolution of about 35μm for an MSGC with 300μm anode pitch.

## 2.5 Microstrip Gaseous Chamber Detectors with Gas Electron Multiplier

Not only for HERA-B[HB93] [HB95] but also for many other experiments (e.g. [CMS94]) MSGCs were considered the optimum replacement for MWPCs in high-rate hadronic environments or when fast readout was required. But the first tests with "larger" detectors ( $(12.5 \times 12.5) \text{cm}^2$ ) showed that the concept failed in a hadronic environment [Vis96] [Hot97] [Bre97]: To achieve electron multiplication by  $a \approx 4000$  a rather high electric field in the vicinity of the anode strips was required. The primary ionisation of heavy or slow particles (e.g. nuclear fragments) together with this high field caused sparks and arcovers, which in turn produced open circuits on the anode strips due to spark erosion. For that reason other experiments (e.g. CMS) abandoned their plans to use MSGCs.

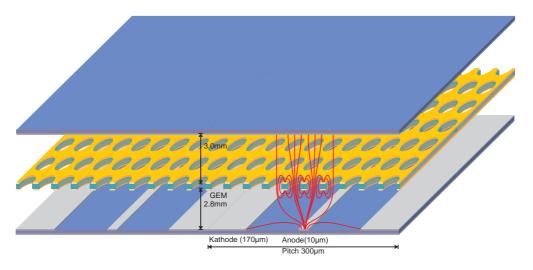

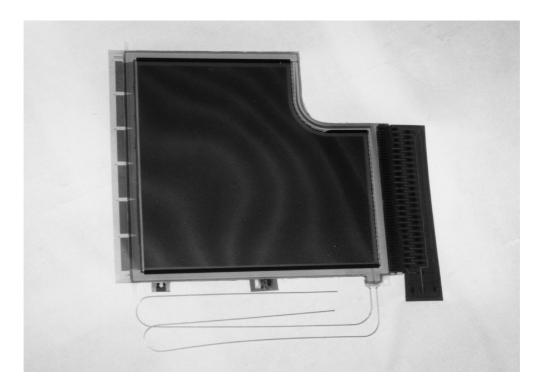

In theory one can overcome this sparking problem by reducing the anode voltage and hence the electron multiplication in the anode region. For a practical realisation, one would have to employ some kind of "electron premultiplier" to achieve the required gain and S/N figures. The Gas Electron Multiplier (GEM) proposed by F. Sauli [Sau96] [Sau97] is such a device: It consists of a Kapton foil with copper coating on both sides, through which holes of 55µm diameter are etched. The pitch of the hexagonally arranged holes is 140µm. When a high voltage is applied between top and bottom side of the GEM foil, all field lines have to pass through the holes. The field can be chosen high enough to cause electron multiplication inside the holes. Fig. 2.12 shows a schematic drawing of a MSGC-GEM including a few field lines, while fig. 2.13 shows a  $25 \times 25 \,\mathrm{cm}^2$  MSGC-GEM used in the HERA-B inner tracking system.

Figure 2.12: Schematic drawing of a MSGC-GEM. The electron multiplication process is split between the GEM foil (centre plane with holes) and the anode strips (on bottom plane). This greatly reduces the risk of discharges and arcovers. The dector is only sensitive to primary ionisation in the volume between the drift electrode (top plane) and the GEM-foil, since only charges generated there are multiplied by the GEM.

Figure 2.13: Photography of a MSGC-GEM detector used in the HERA-B inner tracking system. The anode strips are horizontally aligned and the readout electronics are connected to the left-hand side of the detector (6 HELIX128 chips, i.e one per connector group). The PCB on the right-hand side contains the cathode biasing circuits. The HERA proton beam pipe passes through the cut out top left edge of the detector.

## Chapter 3

# The HELIX128-2.2 Readout Chip

#### 3.1 Requirements

To comply with the requirements of the HERA-B experiment, a readout chip for the silicon vertex detector and inner tracking system had to be built to the following specifications, which are mainly taken from [HB93] and [HB95]:

- Number of channels: 128 (plus an additional frontend-only test channel for detector studies, which is not required but would be a nice add on.)

- Noise: For new chips a noise figure better than  $400e^-+40e^-/pF$  is required to achieve a signal-to-noise ratio of ≥20 with detector capacitances of 20pF and signals of  $24 \cdot 10^3 e^-$ . After 2kGy accumulated dose, a S/N ratio ≥13 under the same conditions was required. The wear limit for irradiated detector modules given in [Rie98] is S/N ≤ 7 to remain operational with a reasonable safety margin.

- **Signal shape:** For a chip using peak sampling mode, rise and fall times ≤96ns (the HERA bunch crossing frequency) are needed. A remainder or undershoot in the following sample would seriously deteriorate the trigger performance of the chip and therefore has to be ≤5%.

- Leakage current compatible charge sensitive amplifier: For DC-coupling to an MSGC detector, the charge sensitive amplifier must be able to sink the leakage current of an anode strip ( $I_{leak} \leq 50$ nA [Zie]).

- Input protection: The gates of the input transistor have to be protected from voltages ≥ 15V when MSGCs are read out. The protection must not deteriorate the noise performance of silicon strip detectors. Internal protection diodes and external series resistors only present in MSGC systems are the most feasible solution.

- Sampling frequency: The sampling frequency is given by the 10.4MHz bunch crossing frequency of the HERA accelerator ring.

- Latency: The decision of the first level trigger in HERA-B is available after 12µs. This requires a storage depth of about 128 samples.

- Analogue readout: The 128 channels of one chip can't be read out in parallel. Therefore they have to be multiplexed to a single line.

- Readout architecture is governed by the 50kHz L1 trigger rate and the requirement of dead-time free operation (i.e. simultaneous sampling and readout) in HERA-B. To minimise common mode noise, the readout frequency should be an (preferably even) integer multiple of the sampling frequency. Including a 100% safety margin for the trigger rate, this leads to 20.8MHz for single chip readout and 31.2MHz (41.6MHz) for the daisy chained readout of two chips. The latter reduces the number of channels in the subsequent DAQ stage by a factor of two. Therefore daisy chained readout was considered a requirement. To avoid dead time introduced by fluctuations of the trigger rate, a derandomiser buffer for 8 triggers was demanded.

- Trigger signals: HERA-B's L1 trigger relies on track data from the inner tracking systemand OTR. To obtain this information from the ITR, all channels have to be equipped with discriminators sharing a common threshold level and feeding their outputs to a second, undelayed readout path. The required resolution is 96ns in the time domain and better than 2400e<sup>-</sup> in amplitude. The required spatial resolution is in the order of 1.5mm, which allows to combine (i.e. logical OR) the signals of four channels (cf. section 2.3). Open drain outputs of the trigger signals are feasible, since in HERA-B the data of two MSGCs are ored together. Though not required for HERA-B, the polarity of the discriminator outputs was made switchable to allow use of the trigger outputs also with double-sided silicon detectors.

- Geometry: To comply with the 50µm readout pitch of silicon strip detectors, the width of the chip is restricted to 6.4mm. The requirement was set to 6.2mm to cover inaccuracies in the dice cutting and chip placement processes.

- Radiation tolerance: The detector modules of the HERA-B silicon vertex detector have to be replaced after about one year of operation. This is due to the deterioration of the silicon strip detectors by radiation damage. Since the readout chips can not be disconnected from detectors and reused, they will be replaced within the same intervals. The required radiation tolerance for the readout chips given in [HB93] and [HB95] is 2kGy/a. In the final design of the vertex detector the chips are mounted at r<sub>⊥</sub> =10cm instead of r<sub>⊥</sub> =7cm as claimed in [HB93], which reduces the annual dose by a factor of two. It is however advisable to provide a safety margin of at least 100% (cf. chapter 5).

- Power dissipation: The cooling system for the readout chips of the silicon vertex detector, which are mounted in the vacuum vessel, has been

built to handle up to about 14W per quadrant and superlayer [Sey97] ( $(1280ch + 1024ch) \cdot 2 = 4608ch$ ) [Sey97]. Therefore the power dissipation has to be less than 3.0mW per channel.

• Remote control: The chips are inaccessibly mounted inside the detector or inside a vacuum vessel. Therefore the remote adjustment of all parameters that might need to be changed (e.g. bias currents or control voltages) is mandatory. On the other hand the number of control lines for the chip has to be kept at as small as possible.

These specifications are very close to those of the CERN RD20 [Gad92] [Bin93] [Bre94/1] [Bre94/2] FElix chip and its derivatives [Fre95] [APV6] [Fre96] developed for experiments at the future CERN LHC accelerator. Unfortunately did these chips neither fulfill all the requirements of the HERA-B experiment (esp. concerning sampling frequency, subsequent triggers, trigger outputs and the ability to read out MSGCs) nor were these chips available in quantities in 1995, when the development of the HELIX128 started. Except for the deconvolution filter, which is not required at 10MHz sampling frequency, the HELIX' analogue signal path very closely resembles the RD20 concept, while the HELIX' Pointer/FIFO based implementation of the storage/readout control circuit is completely different from the shift register based solution implemented on the RD20 FElix chip.

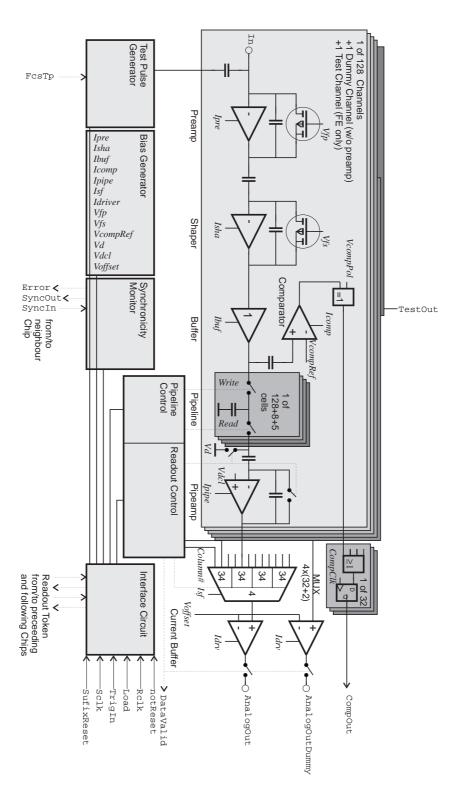

#### 3.2 Overview

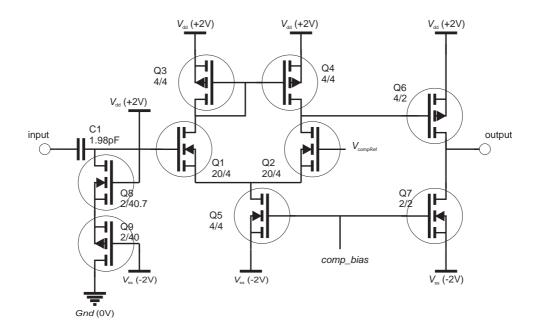

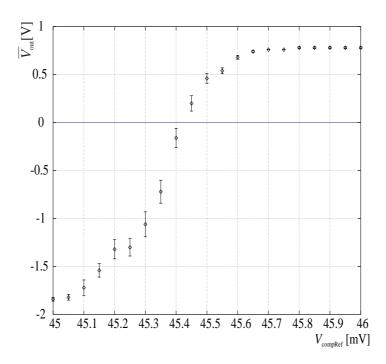

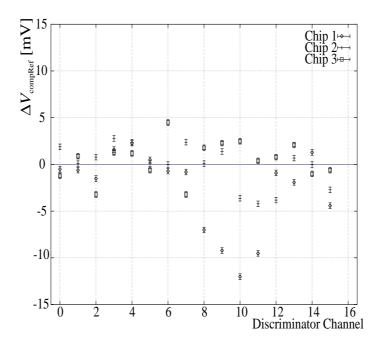

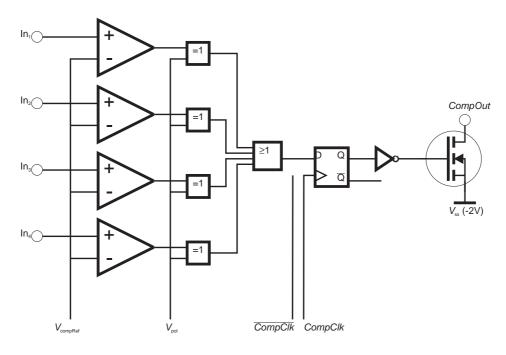

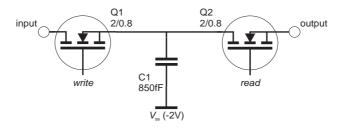

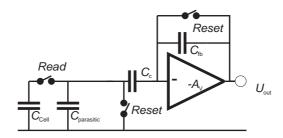

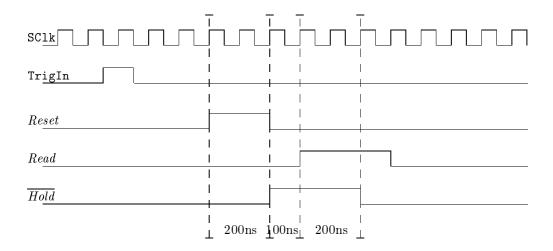

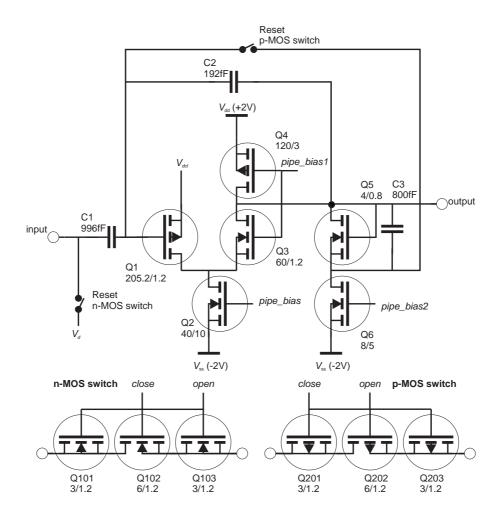

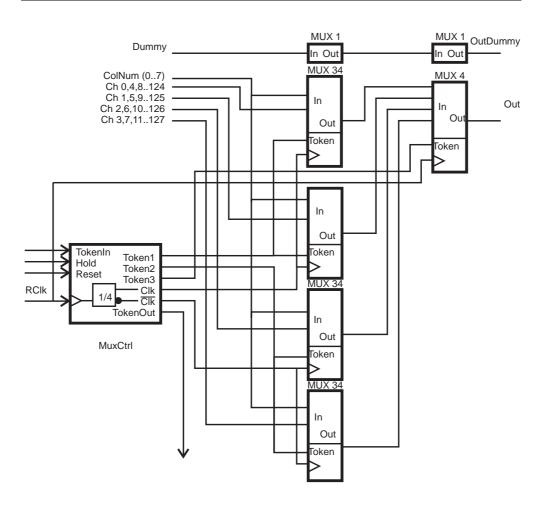

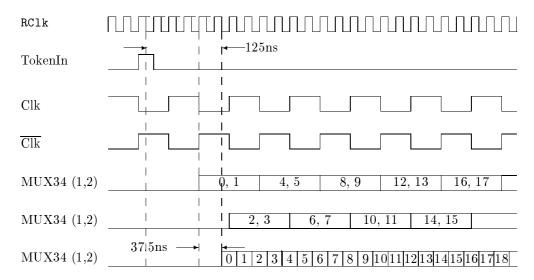

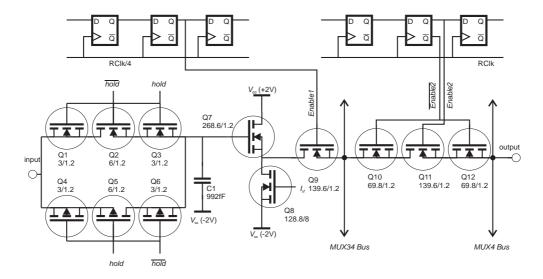

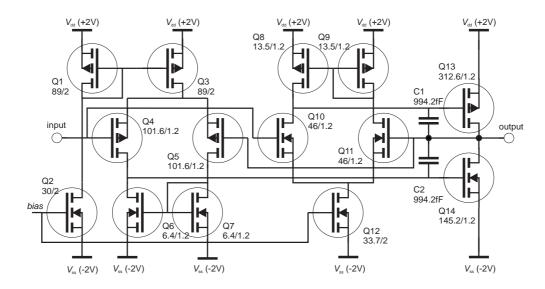

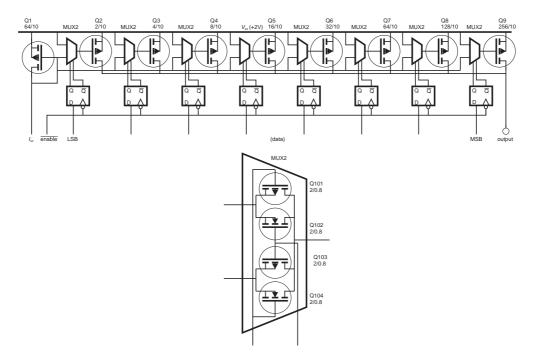

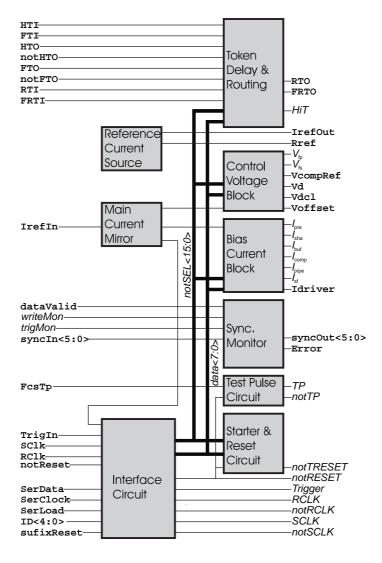

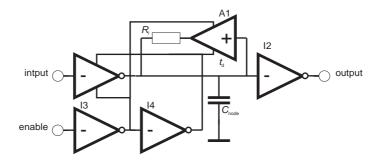

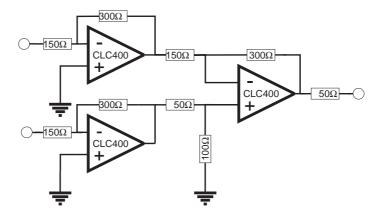

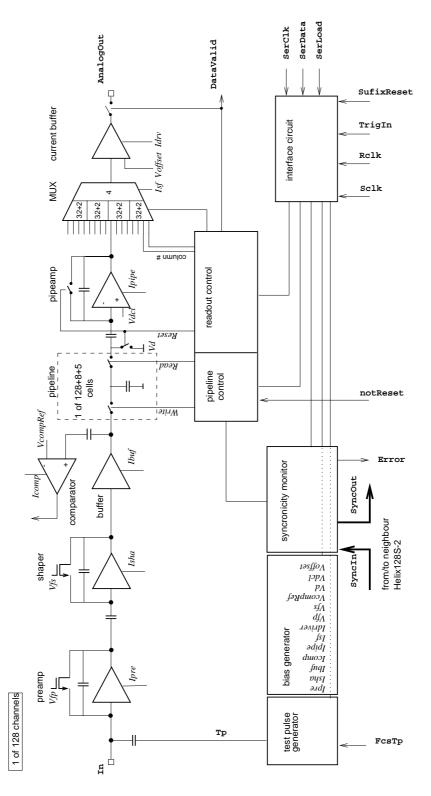

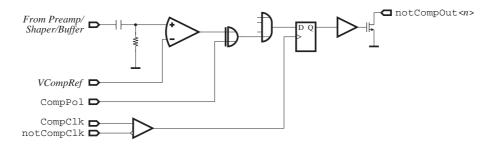

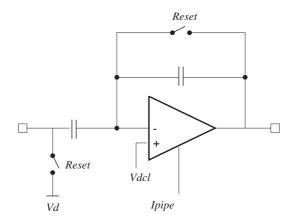

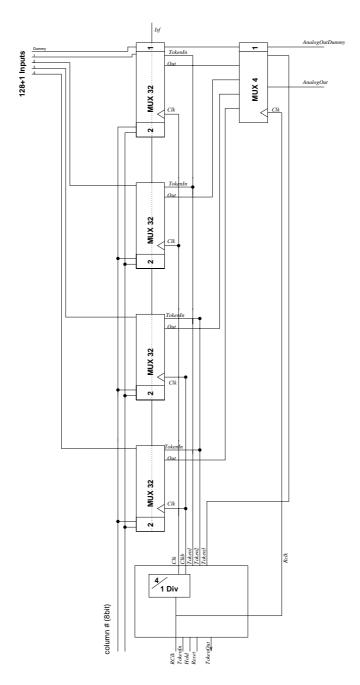

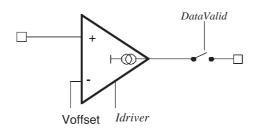

The block schematic of the HELIX128-2.2<sup>1</sup> is depicted in fig. 3.1. Its deduction from the requirements is rather straight-forward: Each channel's readout path splits after the front end. The output of each front end channel is sampled onto a pipeline storage capacitor and in parallel it is AC-coupled to a comparator. This AC-coupling removes the individual offset voltage of each frontend channel and permits a common threshold voltage for all 128 channels. The comparator outputs run through an XOR gate enabling a polarity reversal before being ORed together in groups of four adjacent channels. These 32 signals are then latched with a clock signal independent from the analogue sampling process. The outputs of these latches connect to open drain output pads.

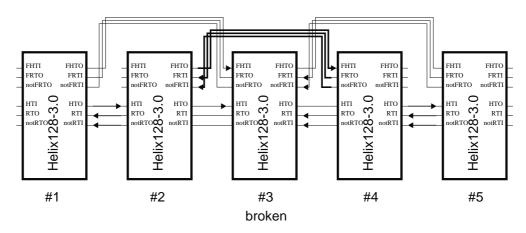

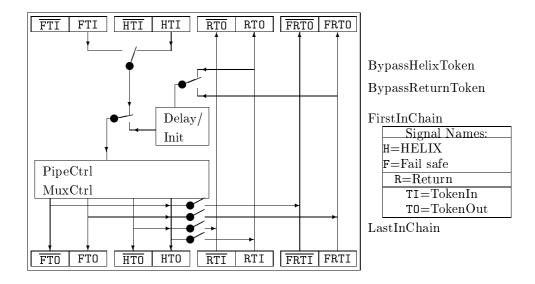

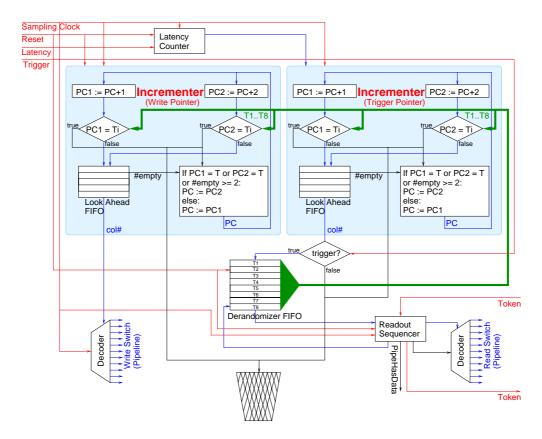

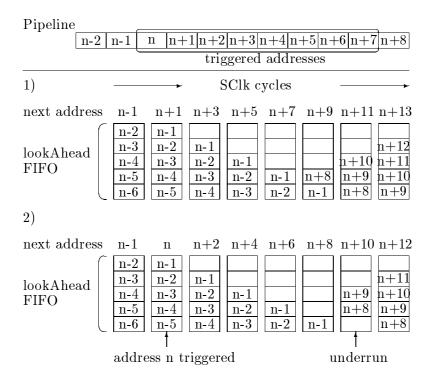

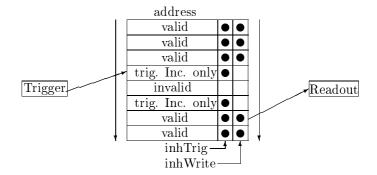

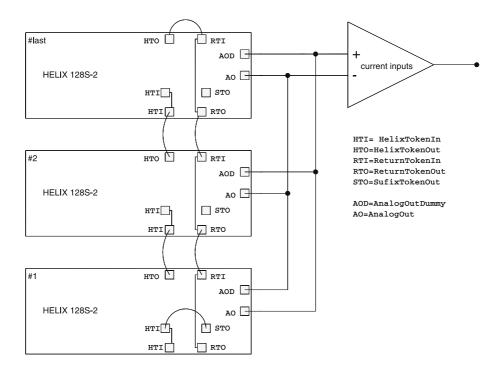

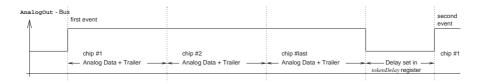

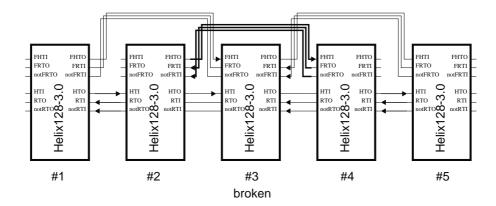

The sampled analogue signal has to be kept for up to 128 clock cycles before it is either overwritten or marked for readout by a trigger signal. The oldest triggered samples are read out with a resetable charge sensitive amplifier and multiplexed together with some digital information to a single line. The signal of this line is driven off-chip by a current buffer. This storage/readout sequence is controlled by a digital circuit, which can also handle up to 8 subsequent triggered samples and the daisy chained readout of two or more chips (i.e. they subsequently multiplex their analogue data to the same readout line).

<sup>1</sup>This description also covers all subsequent versions (i.e. HELIX128-2.2 also covers the HELIX128-3.0, HELIX128-3.1 and HELIX128-3.1a chips) unless otherwise denoted (cf. appendix B and E).

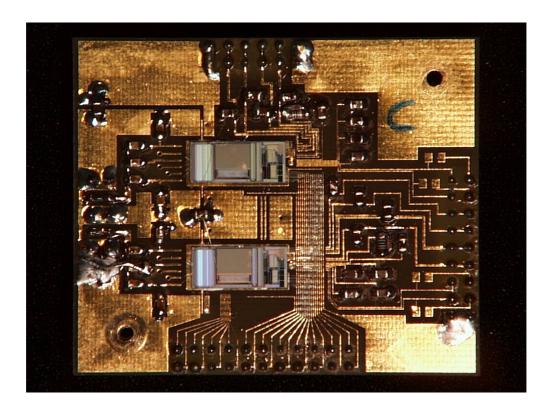

Figure 3.1: Block schematic of the HELIX128-2.2 and later chips.

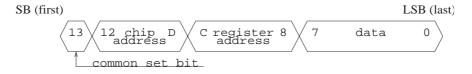

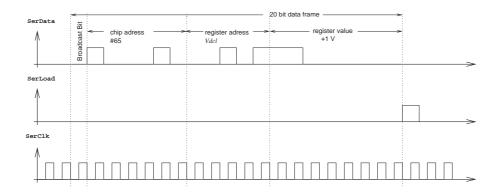

Remote control is accomplished via the trigger input and a dedicated load signal<sup>2</sup>, allowing the adjustment of bias currents, control voltages, trigger latency and other parameters.

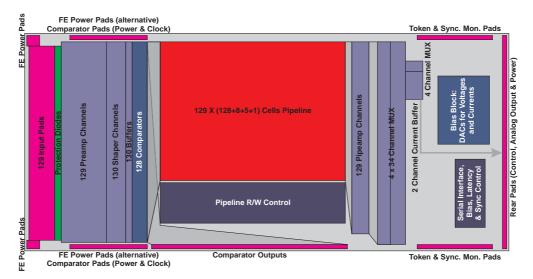

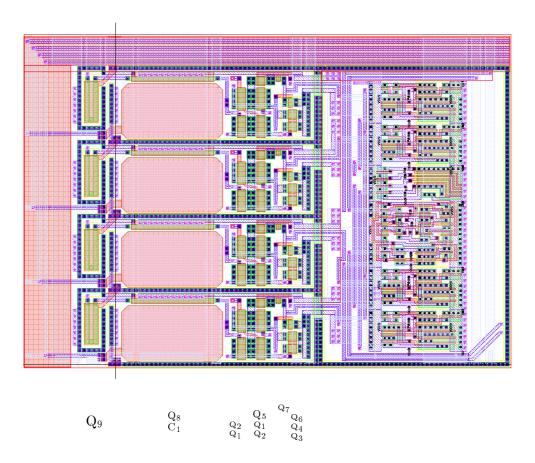

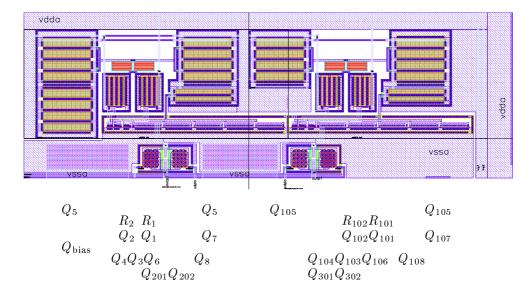

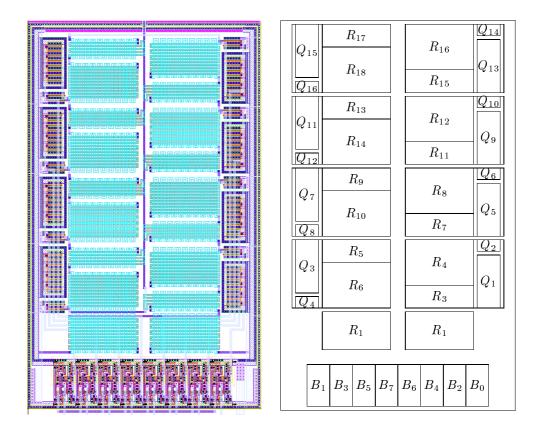

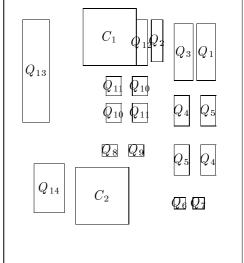

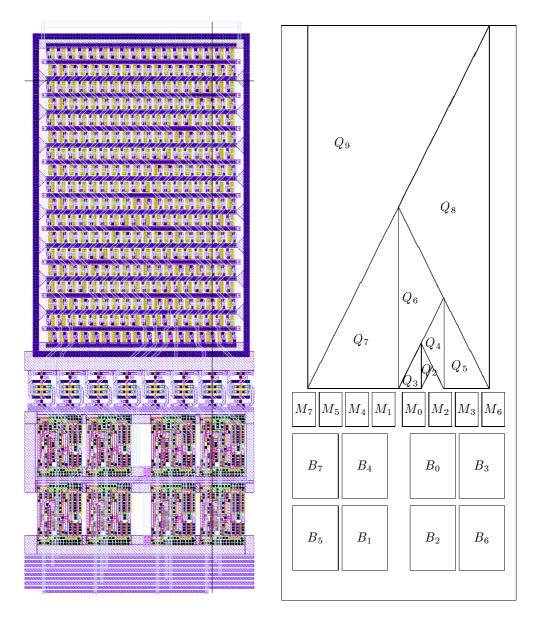

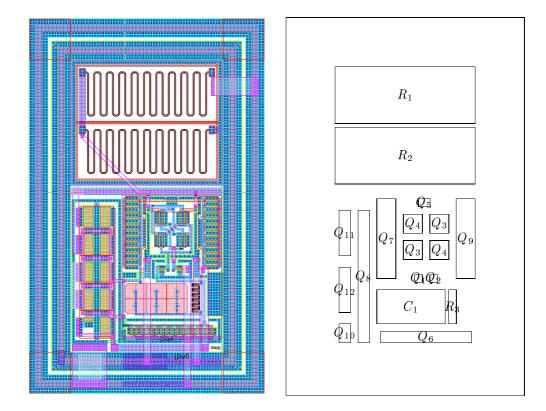

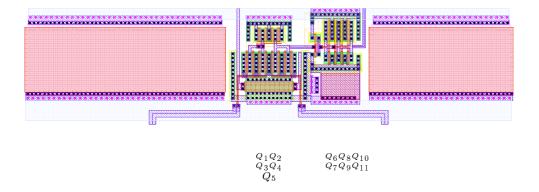

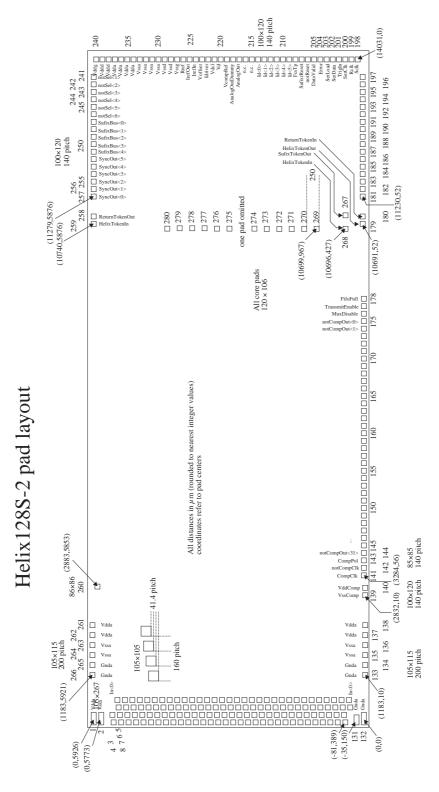

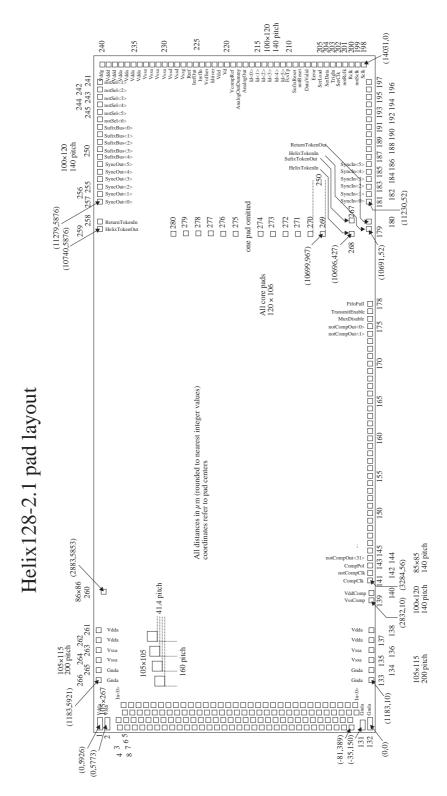

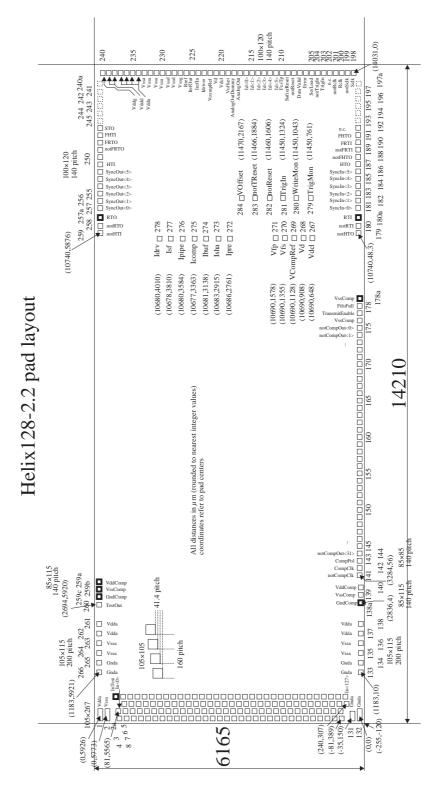

Figure 3.2: Layout floorplan of the HELIX128-2.2 and later chips. The relaxed spacing of the building blocks on the right-hand side of the chip is due to the space required by the token and synchronicity monitoring pads.

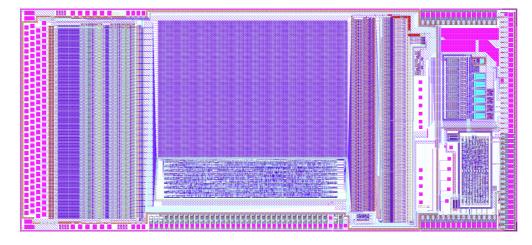

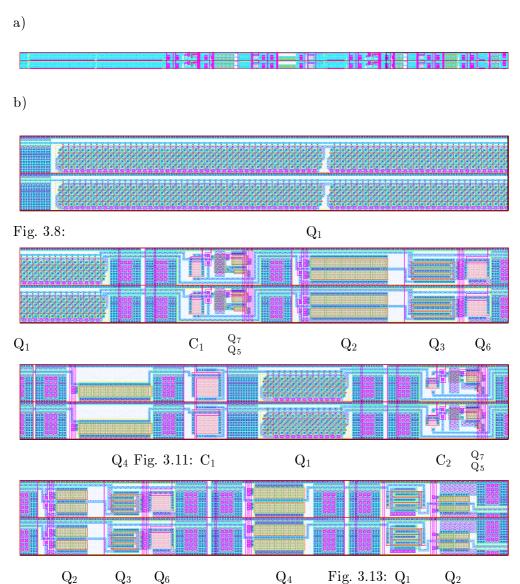

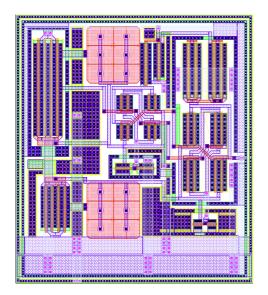

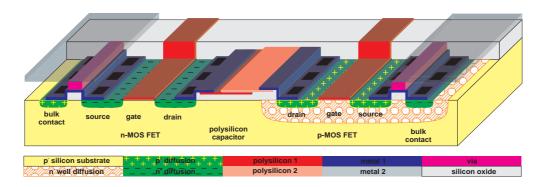

Figure 3.3: Layout of the HELIX128-3.0 chip. It differs from HELIX128-2.2 only in only very few details. The colour scheme of the layers is explained in fig. 4.1.

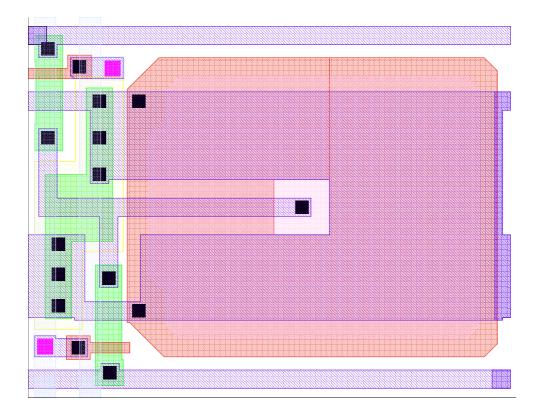

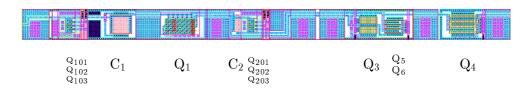

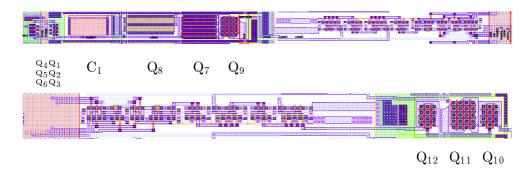

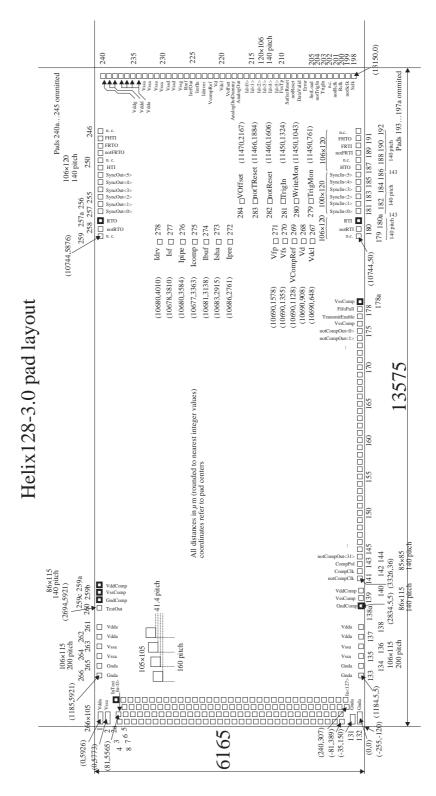

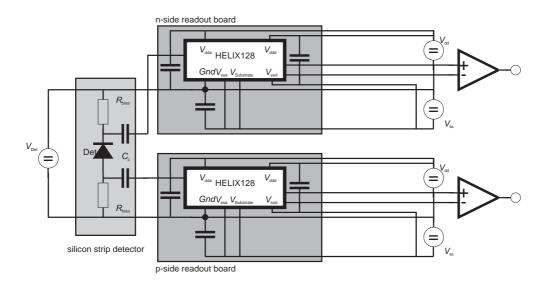

The layout floorplan of the  $(6.2 \times 14.2)$ mm<sup>2</sup> chip is shown in fig. 3.2. It is governed by the attempt to separate the noisy (i.e. digital) components from the sensitive ones (esp. the frontend) while keeping related or interacting parts as close together as possible. Fig. 3.3 shows the layout of the chip.

<sup>&</sup>lt;sup>2</sup>HELIX128-2.0 and 2.1 use a dedicated 3-line interface instead.

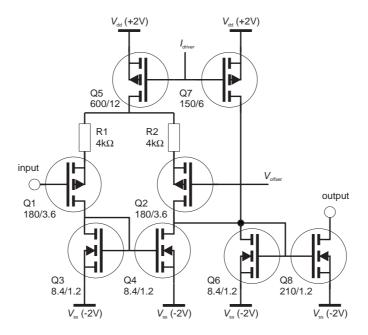

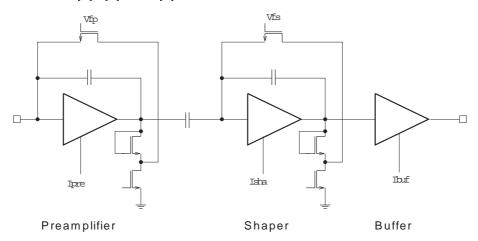

#### 3.3 Frontend

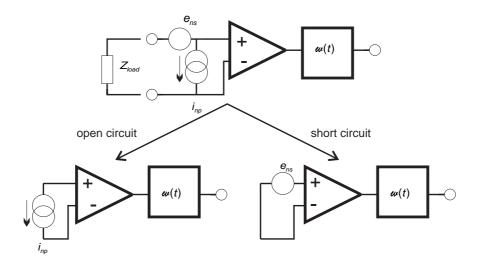

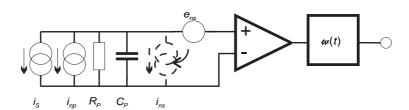

The frontend of a readout chip for silicon strip detectors or Microstrip Gaseous Chambers has to consist of a charge sensitive or current sensitive preamplifier and a filter circuit. The decision upon the principle of the preamplifier can be either based on the expected noise performance for a given detector capacitance and bandwidth or the chip technology used. In case of microstrip detectors and 10MHz signal rate the decision has to be in favour of a charge sensitive amplifier [Fal98] from the noise performance point of view:

$$q_{\text{ineq}}^2 = 4kT \frac{1}{(R_{\text{p}} \parallel R_{\text{fb}})|\imath\omega|^2} + \frac{i_{\text{p}}^2}{|\imath\omega|^2} + e_{\text{s}}^2 \cdot (C_{\text{p}}^2 + C_{\text{fb}}^2) [C^2/\text{Hz}]$$

(3.1)

$q_{\rm ineq}={

m equivalent}$  spectral input noise charge density (cf. sect. 3.3.1)  ${

m [C/\sqrt{Hz}]}$

$i_{\rm p}=$  (parallel) current noise density  ${\rm [A/\sqrt{Hz}]}$

$e_{\rm s}={

m (series)}$  voltage noise density  ${

m [V/\sqrt{Hz}]}$

$k = \text{Boltzmann's constant } (1.38 \cdot 10^{-23} \text{J/K})$

T = absolute temperature [K]

$\omega$  = angular velocity equivalent to the system bandwidth [s<sup>-1</sup>]

$R_{\rm p}=$  resistance on amplifier input node (i.e resistance of the detector,  $\geq 10{\rm M}\Omega$  for MSGs or silicon strip detectors)  $[\Omega]$

$R_{\rm fb}=$  feedback resistance of the amplifier ( $\leq 1{

m M}\Omega$  for a current sensitive amplifier,  $\geq 10{

m M}\Omega$  for a charge sensitive amplifier)  $[\Omega]$

$C_{\rm p}=$  capacitance on amplifier input node (i.e capacitance of the detector,  $\approx$  20pF for MSGCs or silicon strip detectors) [F]

$C_{\rm fb}={

m feedback}$  capacitance (pprox 0 for a current sensitive amplifier, pprox 300fF for a charge sensitive amplifier) [F]

While the first term in eq. 3.1 is increased for a current sensitive amplifier due to the lower values of  $R_{\rm fb}$  required, the finite contribution of  $C_{\rm fb}$  to the last term for the charge sensitive amplifier can be still neglected. For microstrip detectors  $C_{\rm fb}$  is smaller than  $C_{\rm p}$  by about two orders of magnitude. Therefore a charge sensitive amplifier is feasible. For  $C_{\rm p}$  comparable to  $C_{\rm fb}$  (e.g. for pixel detectors) and increased system bandwidth (supressing the first two terms in eq. 3.1) the current sensitive amplifier takes over.

Concerning the chip technology a charge sensitive amplifier is feasible when implemented in CMOS technology:

The polysilicon feedback capacitor governing the behaviour of a charge sensitive amplifier is a nearly ideal, extremely accurate and well matching device, while linear resistors required for current sensitive amplifiers are suffer from by bad accuracy, poor matching and large parasitics in CMOS processes. In a bipolar process a current sensitive amplifier can make use of a common base circuit, which eliminates the feedback resistor and takes advantage of the higher transconductance of bipolar transistors.

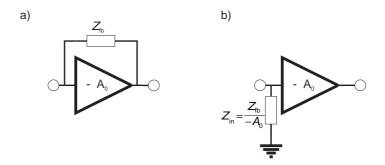

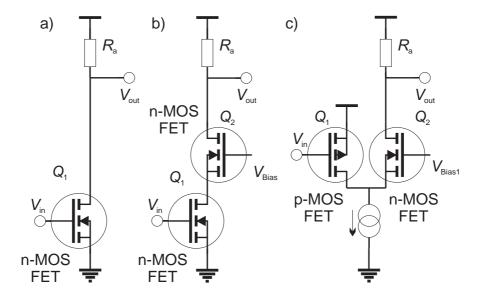

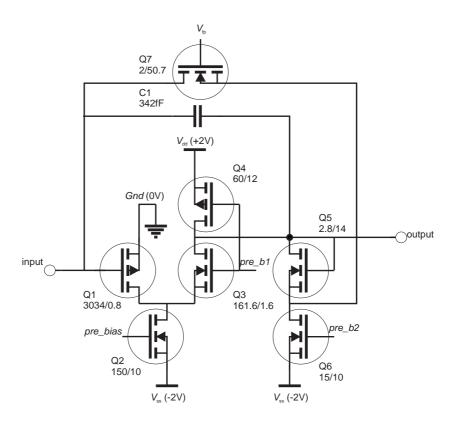

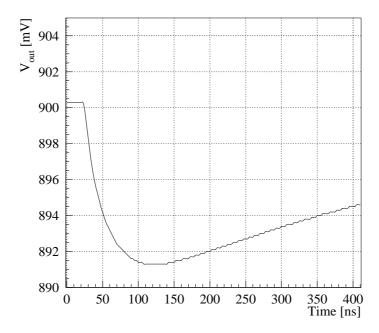

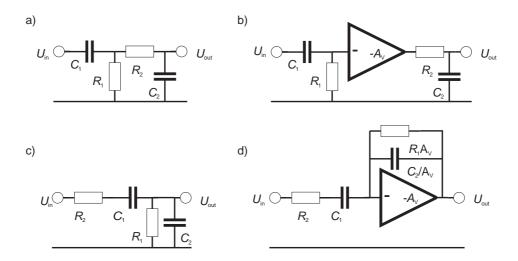

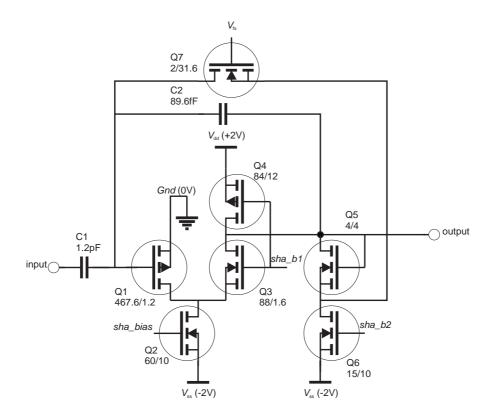

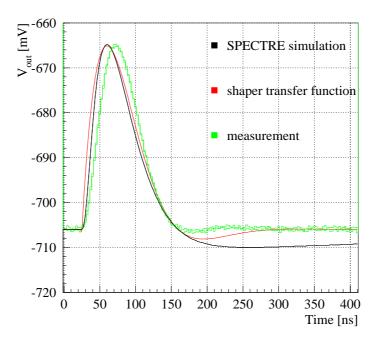

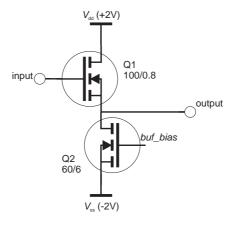

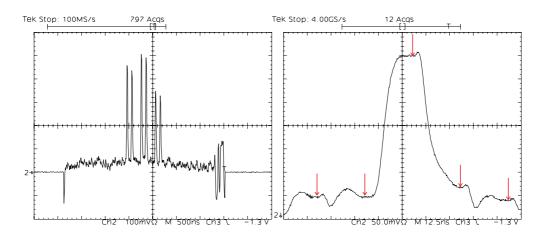

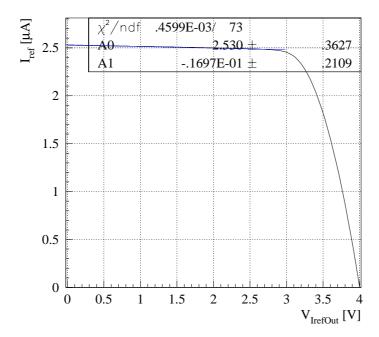

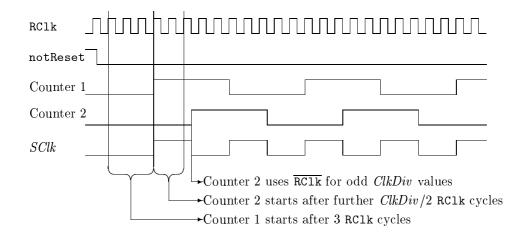

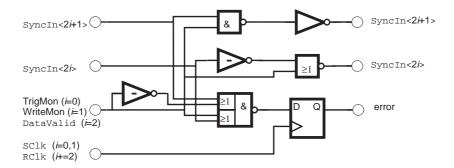

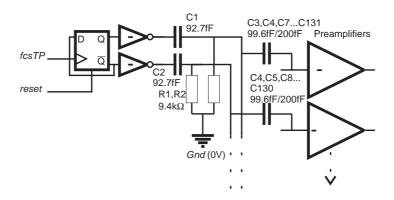

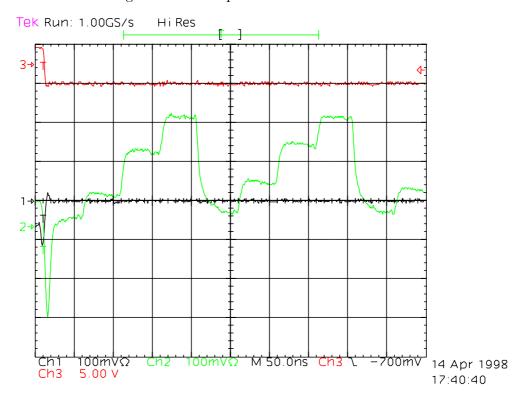

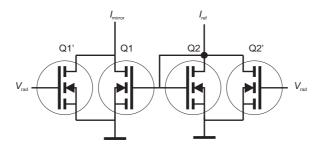

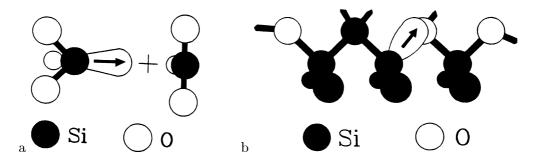

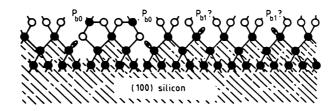

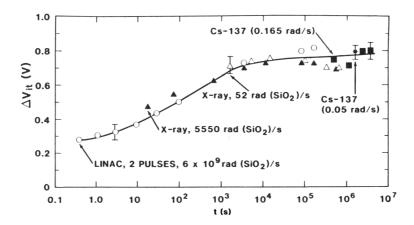

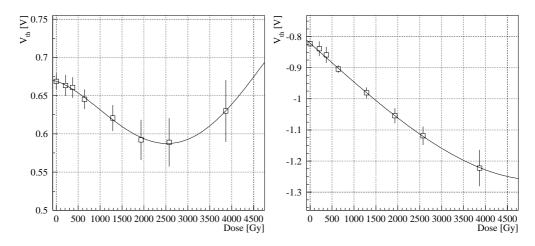

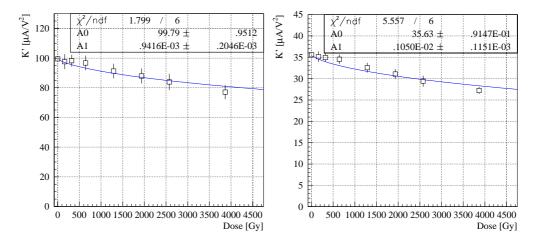

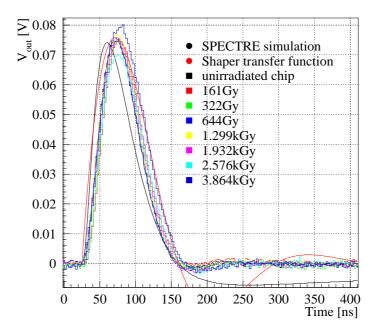

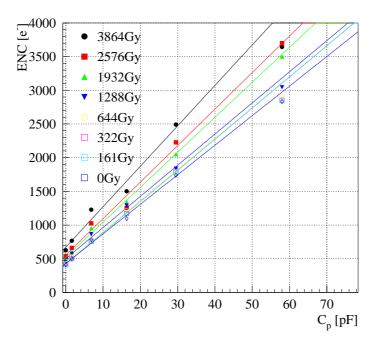

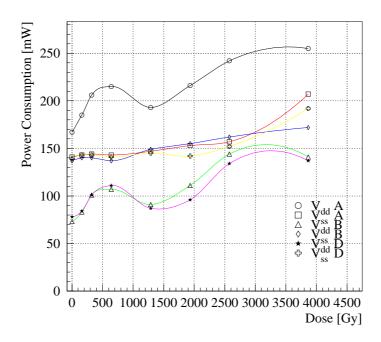

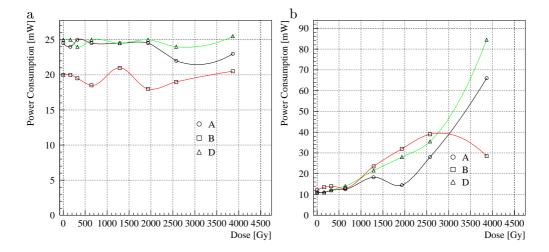

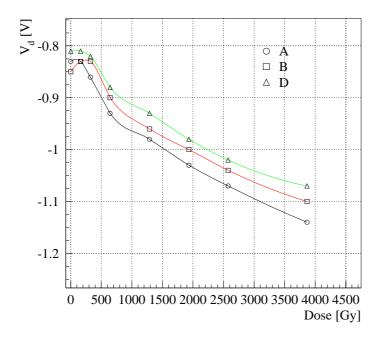

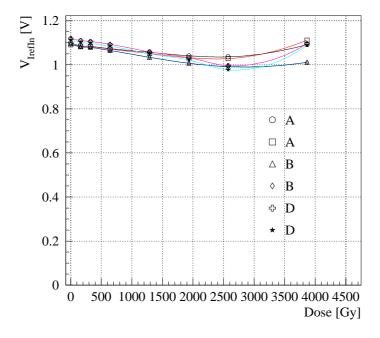

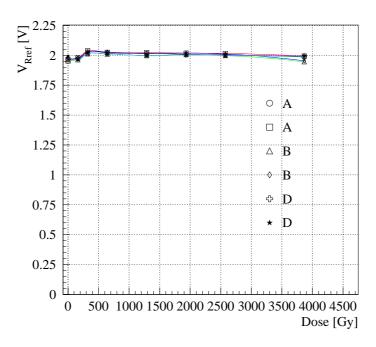

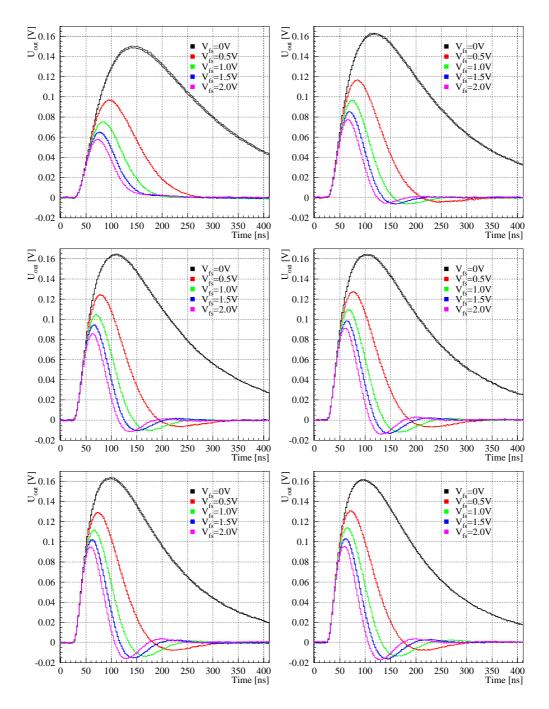

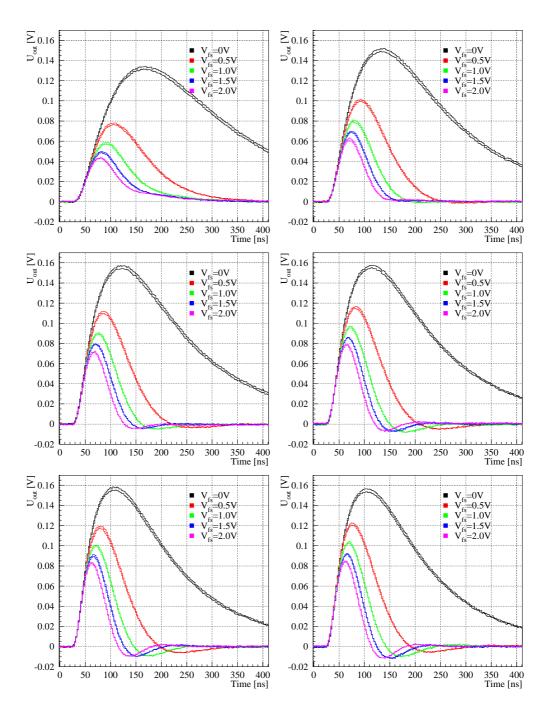

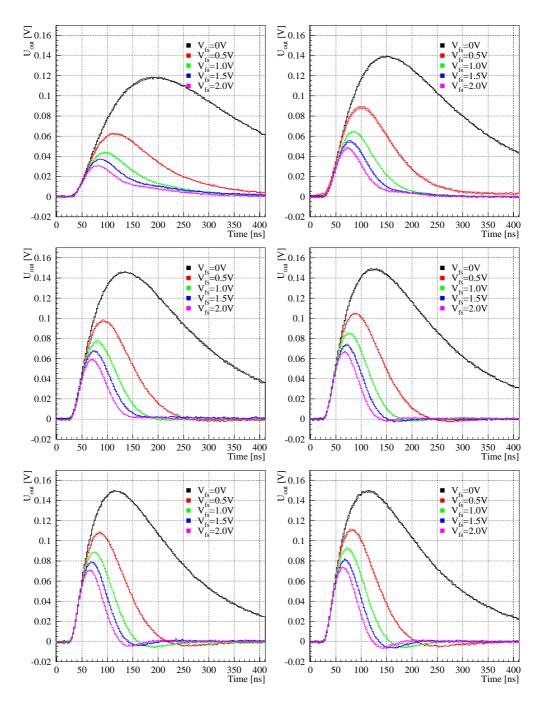

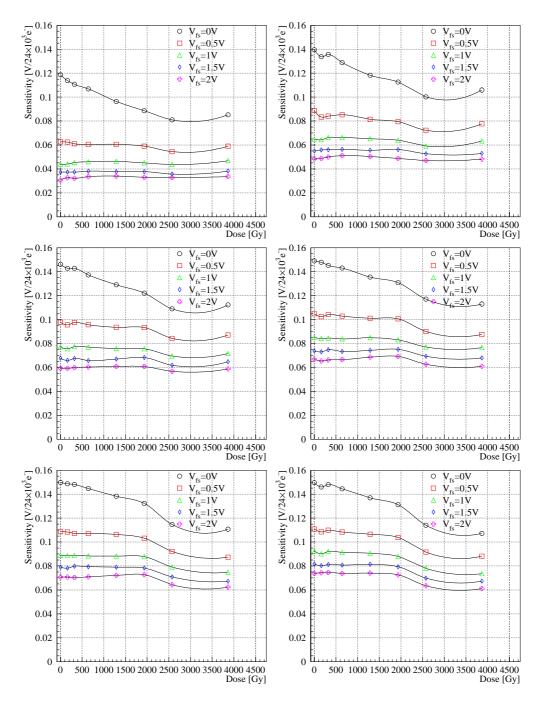

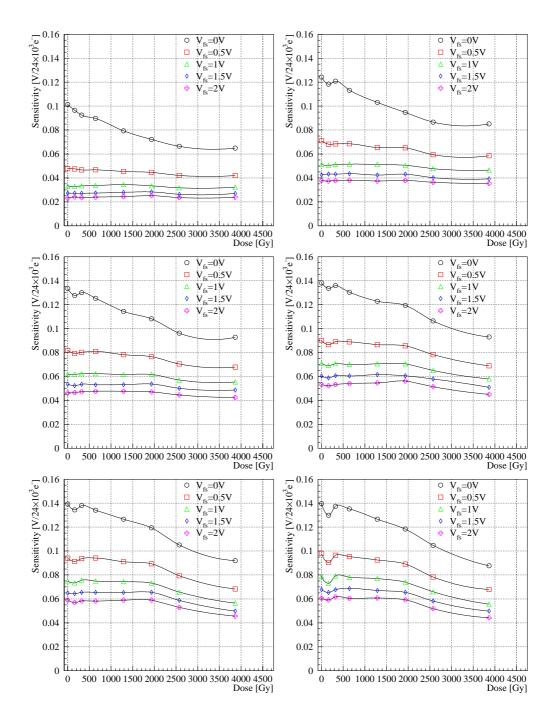

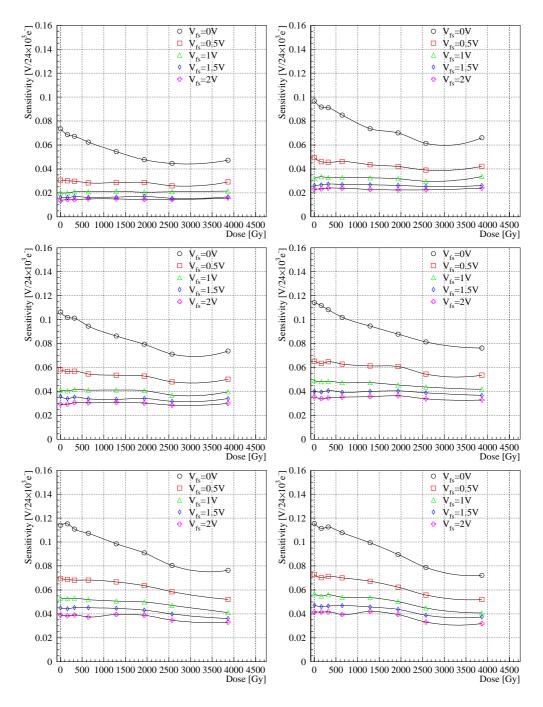

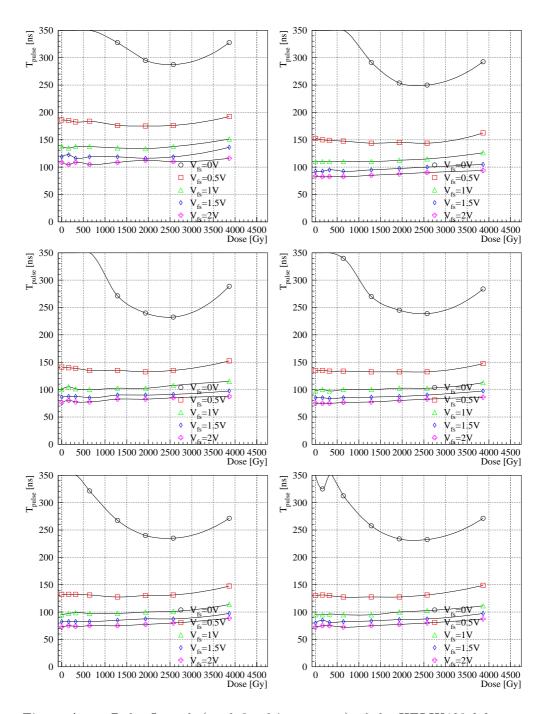

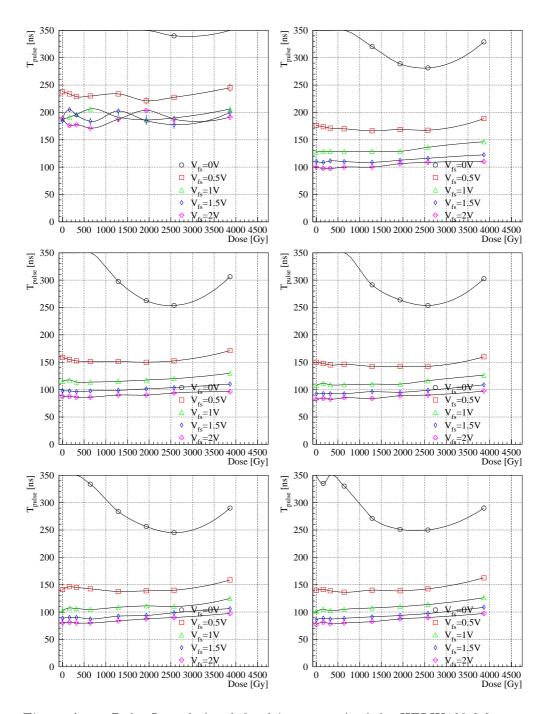

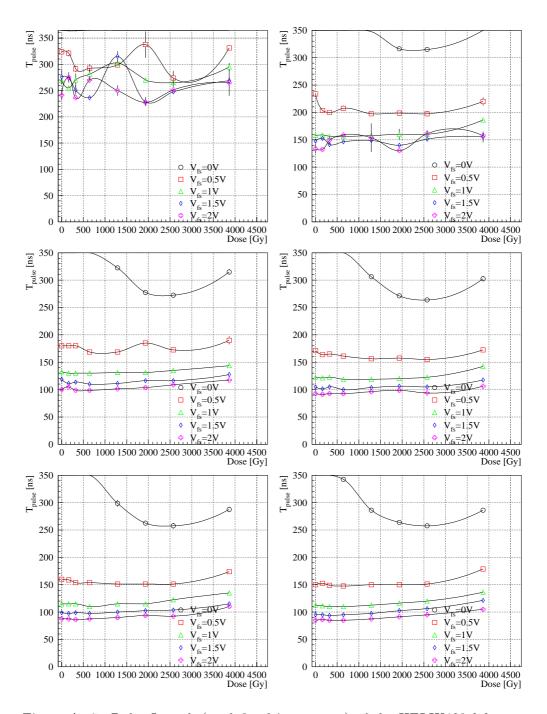

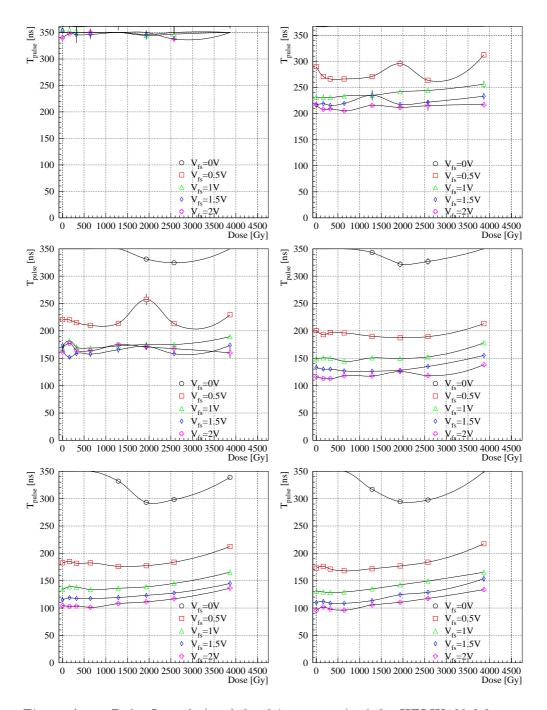

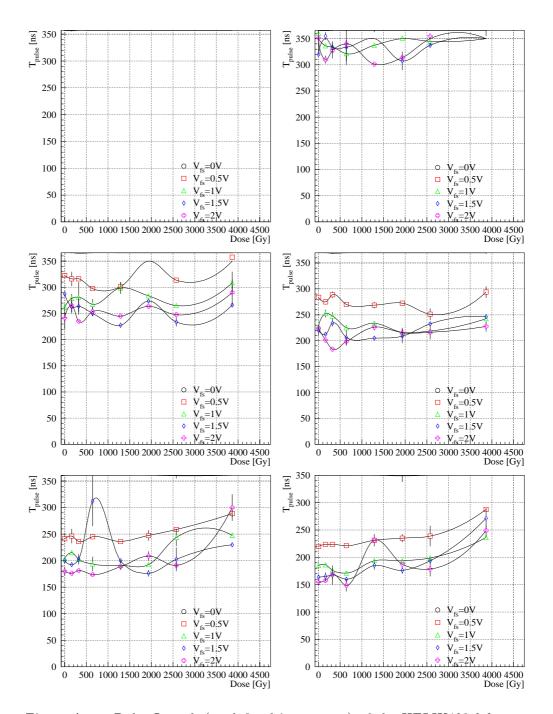

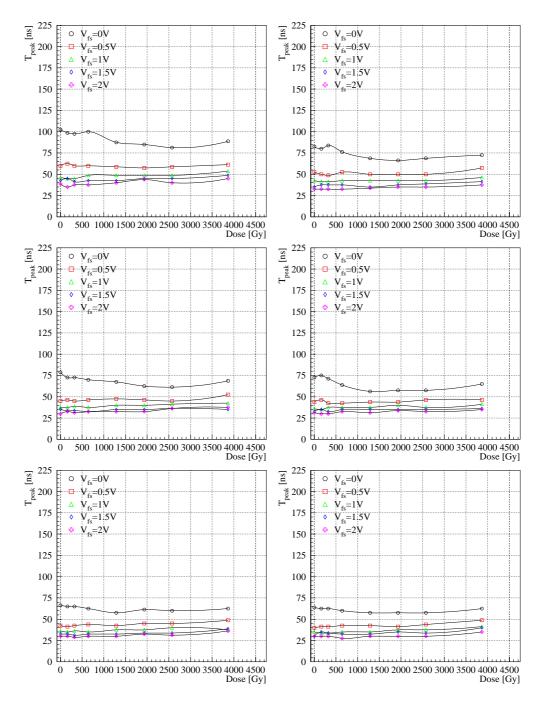

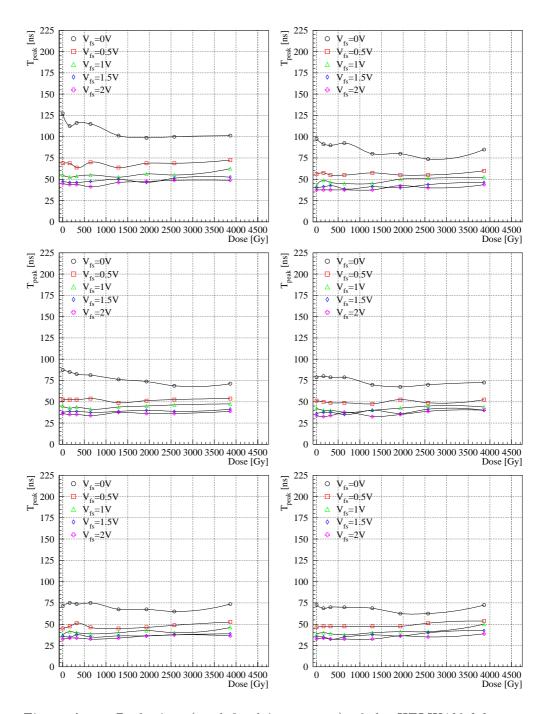

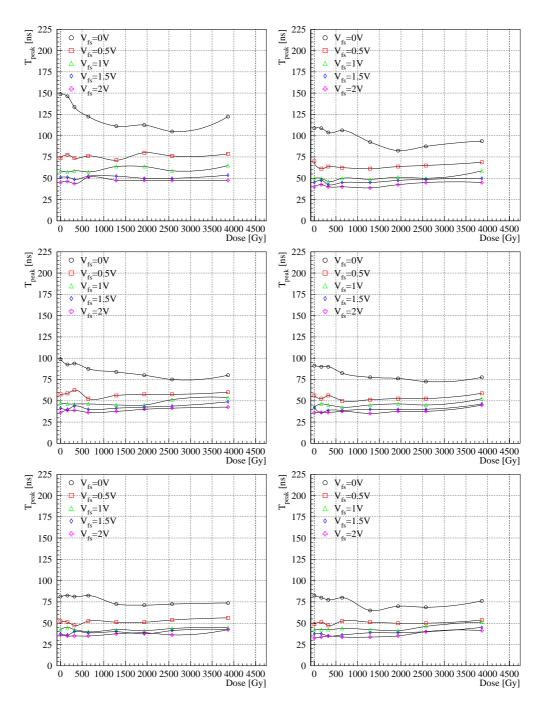

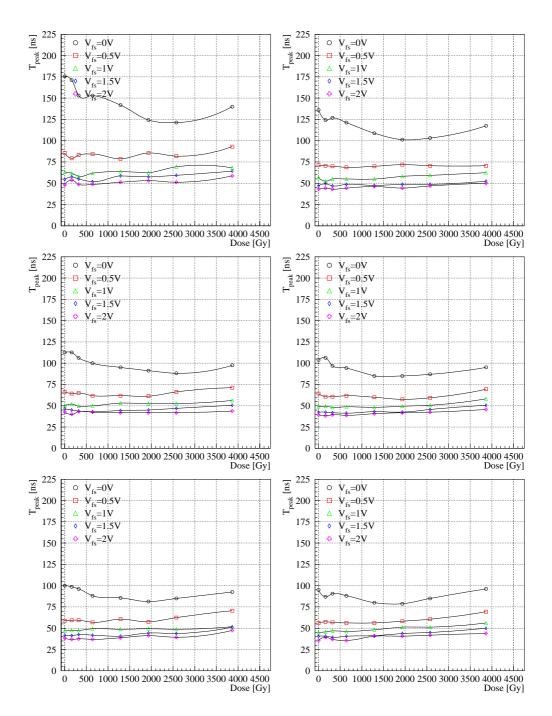

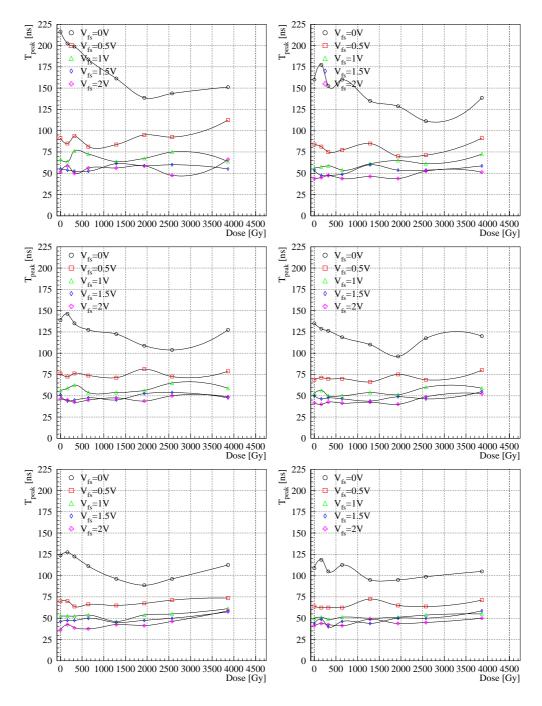

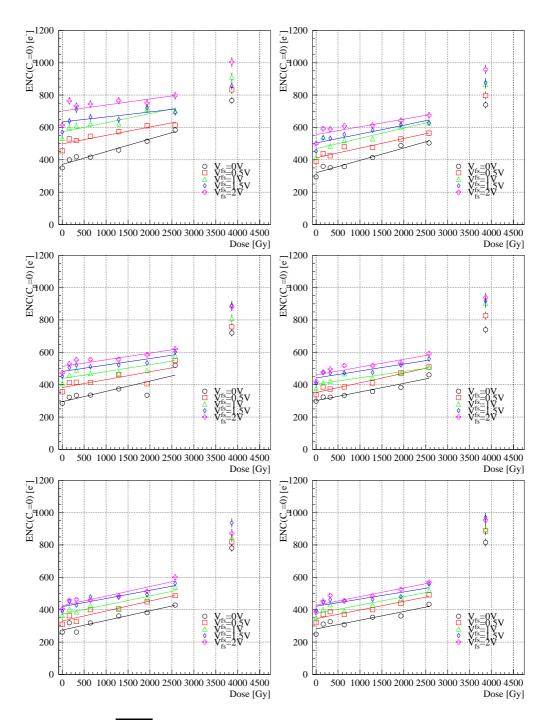

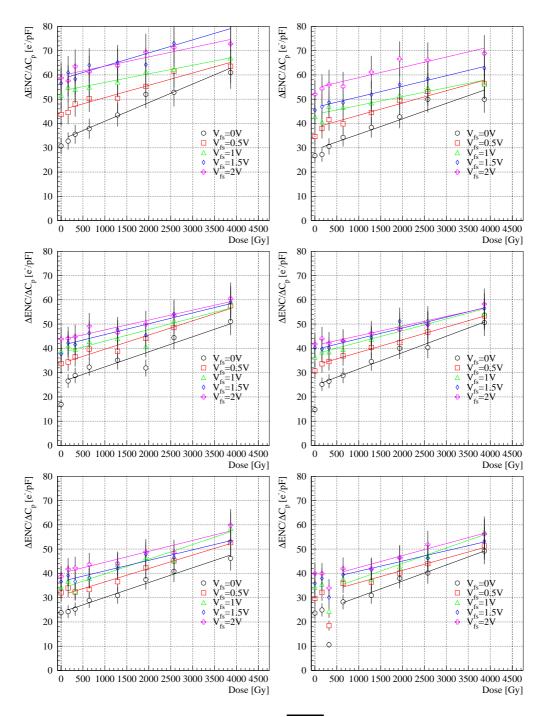

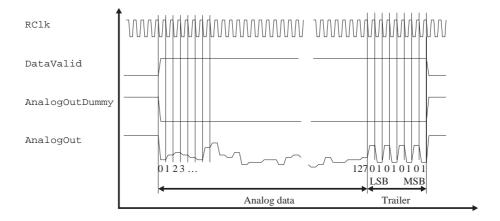

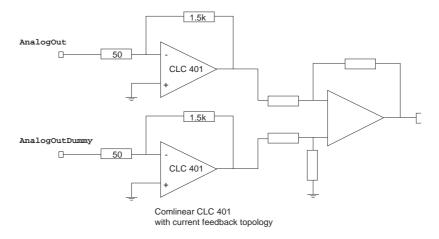

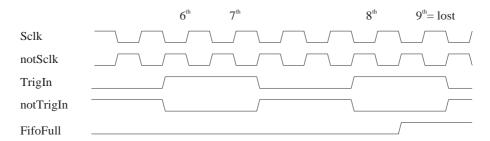

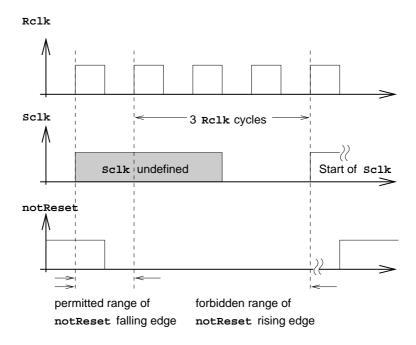

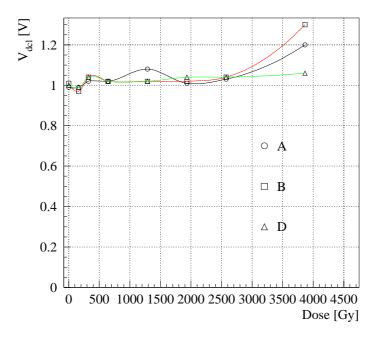

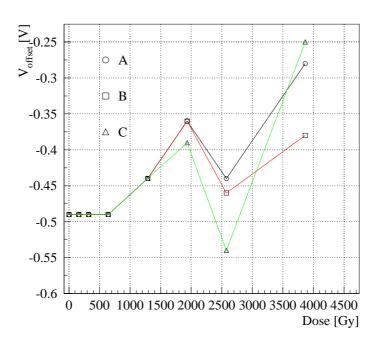

The HELIX128 is manufactured in AMS' CYE (0.8µm CMOS) process [AMS97/2] and consequently a charge sensitive amplifier was chosen.