### INAUGURAL-DISSERTATION

zur Erlangung der Doktorwürde der Naturwissenschaftlich-Mathematischen Gesamtfakultät der Ruprecht-Karls-Universität Heidelberg

vorgelegt von Dipl.–Phys. Wolfgang Fallot-Burghardt aus Saarbrücken

Tag der mündl. Prüfung: 24.06.1998

A CMOS Mixed-Signal Readout Chip for the Microstrip Detectors of HERA-B

Gutachter:

Prof. Dr. Karl-Tasso Knöpfle

Prof. Dr. Ulrich Straumann

Innerhalb der vorliegenden Doktorarbeit wurden die wesentlichen analogen Teile des CMOS Mixed-Signal Chips HELIX128S-2 entworfen und getestet; dieser Chip dient zur Auslese von Ladungssignalen aus Siliziumstreifen- und Gas-Mikrostreifen-Detektoren, die beim Nachweis von Elementarteilchen beim HERA-*B* Experiment (DESY, Hamburg) zum Einsatz kommen.

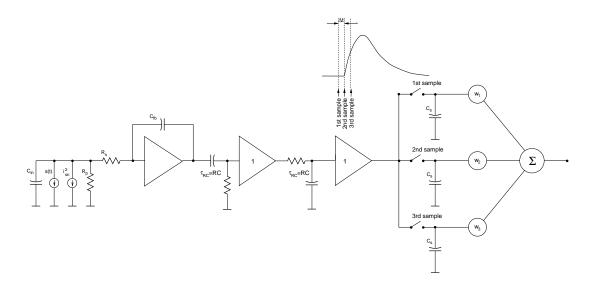

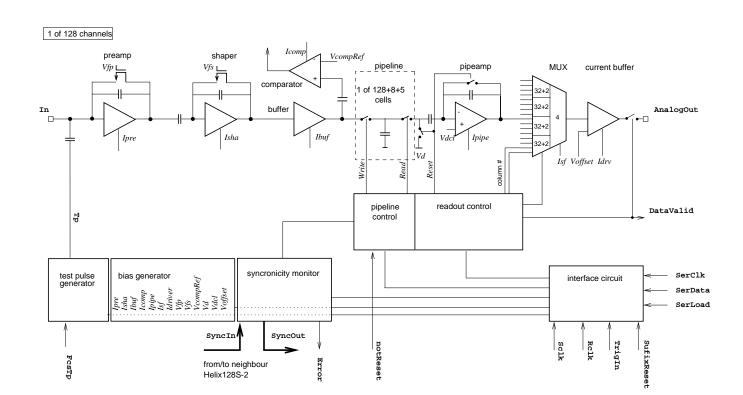

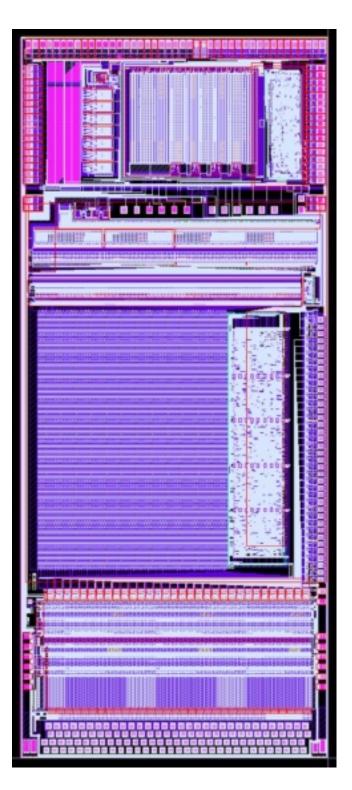

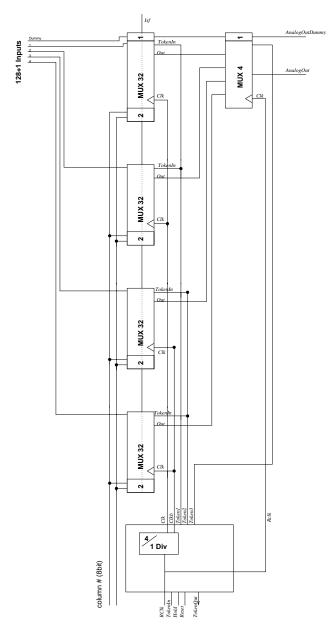

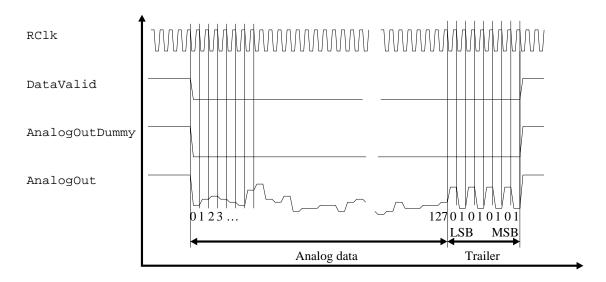

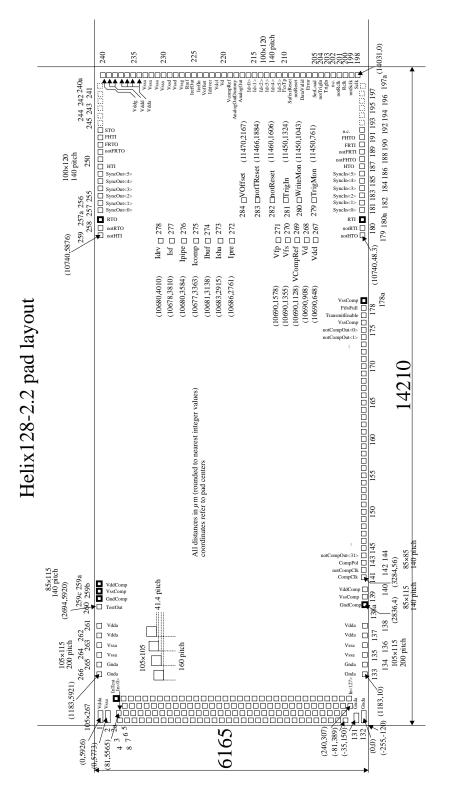

HELIX128S-2 integriert 128 Verstärkerkanäle, bestehend aus einem schnellen (Anstiegszeit ca. 50 ns), rauscharmen (ENC=474 e<sup>-</sup>+35 e<sup>-</sup>/pF  $\cdot C_{in}$ ) Ladungsverstärker, der die Vorverstärkung der Strom/Ladungssignale (typisch 4 fC) übernimmt; die langsam abfallenden Vorverstärkersignale werden von einem nachfolgenden Pulsformer in zeitlimitierte Pulse (Abfallzeit < 100 ns) umgewandelt, die anschließend mit 10 MHz Abtastrate in einer Kapazitätsmatrix zwischengespeichert werden. Auf ein Level 1 Triggersignal hin, das mit 10  $\mu$ s Verzögerung erfolgt, werden die Signalwerte durch einen weiteren Ladungsverstärker aus der Matrix ausgelesen, von einem 128 zu 1 Multiplexer auf eine Leitung gemultiplext und von einem schnellen Stromtreiber als Analogwerte ausgegeben (max. 40 MHz); hierbei erfolgt die Auslese der Matrixwerte totzeitfrei, d. h. ohne den Schreibvorgang zu stören. Zum schnellen Nachweis eines getroffenen Streifens generiert ein hinter dem Pulsformer angebrachter, kapazitiv gekoppelter Komparator (Schwelle gemeinsam für alle Komparatoren) ein digitales Signal, das zu vieren verodert als Open-Drain Signal zur Verfügung gestellt wird. Die Breite der Verstärkerkanäle darf wegen des Siliziumstreifenabstandes 50  $\mu$ m nicht überschreiten und beträgt bei dem vorgestellten Chip 42.2  $\mu$ m; die Größe des Chips beträgt 14.39 mm  $\times$  6.15 mm. Durch konsequenten Einsatz von Stromspiegeln mit konstantem Referenzstrom wird eine moderate Strahlenhärte (< 200 krad) erreicht.

Der entwickelte Chip erfüllt die vorgegebenen Spezifikationen; neben dem HERA-*B*-Experiment wird er auch beim ZEUS-Experiment (DESY) eingesetzt werden.

In the context of this dissertation the major part of the analog circuitry of the CMOS mixed-signal chip HELIX128S-2 has been developed and tested; it serves for the readout of charge signals from silicon-strip and microstrip gas-chamber detectors to be installed for the detection of elementary particles at the HERA-B experiment (DESY, Hamburg). HELIX128S-2 integrates 128 amplifier channels, consisting of a fast (rise time approx. 50 ns), low-noise (ENC=474 e<sup>-</sup>+35 e<sup>-</sup>/pF  $\cdot C_{in}$ ) charge amplifier which integrates the current/charge-signals (typically 4 fC); the slowly decaying preamplifier output signals are converted by a subsequent pulse shaper into time-limited pulses (decay time < 100 ns), which are stored at 10 MHz successively in a capacitor array ("pipeline"). In the event of a level one trigger which arrives with a delay of 10  $\mu$ s, the signal values are read out from the pipeline by a resetable charge amplifier; this happens without introducing dead time, i. e. the write-operation is not affected. The signals from different channels are multiplexed by a 128 to 1 multiplexer onto one bus line and are put out as analog values by a fast current buffer (max. 40 MHz). Additionally, each channel is equipped with an AC-coupled comparator behind the preamplifier/shaper. All comparators share a common threshold, the output of four neighbouring comparators being ORed and brought off-chip as open drain signals. The width of an amplifier channel may not exceed 50  $\mu$ m due to the silicon strip pitch and amounts to 42.2  $\mu$ m; the chip's overall size is 14.39 mm  $\times$  6.15 mm. By the use of current mirrors with constant reference current a moderate radiation hardness is obtained ( $\leq 200$  krad).

The chip developed fulfills the given specifications of HERA-B; it will also be employed by the ZEUS-experiment (DESY).

# Contents

| 1        | $\mathbf{Intr}$ | oducti  | on                                                                                                                                      | 11        |

|----------|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1             | HERA    | $-B$ Detector $\ldots$                                 | 12        |

|          | 1.2             | Silicon | $ Tarret Teter (SVD) \dots \dots$ | 15        |

|          |                 | 1.2.1   | Geometrical Layout                                                                                                                      | 15        |

|          |                 | 1.2.2   | Radiation Damage                                                                                                                        | 16        |

|          |                 | 1.2.3   | Electronic Readout                                                                                                                      | 17        |

|          |                 | 1.2.4   | Mechanics and Engineering                                                                                                               | 18        |

|          |                 | 1.2.5   | Alignment                                                                                                                               | 19        |

| <b>2</b> | Silio           | con De  | tectors                                                                                                                                 | <b>21</b> |

|          | 2.1             | Charg   | e Creation $\ldots$                                    | 21        |

|          | 2.2             | Signal  | Charge Transport                                                                                                                        | 25        |

|          | 2.3             | Silicon | Strip Detector                                                                                                                          | 27        |

| 3        | Gas             | eous I  | Detectors                                                                                                                               | 33        |

|          | 3.1             | Ioniza  | tion Process in Gases                                                                                                                   | 33        |

|          | 3.2             | Signal  | Charge Transport                                                                                                                        | 35        |

|          | 3.3             | Micros  | strip Gas Chamber (MSGC)                                                                                                                | 37        |

| 4        | Noi             | se in A | Amplifiers                                                                                                                              | 41        |

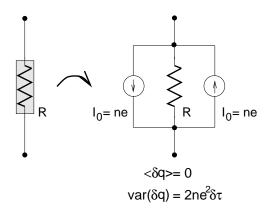

|          | 4.1             | Physic  | al Noise Models                                                                                                                         | 42        |

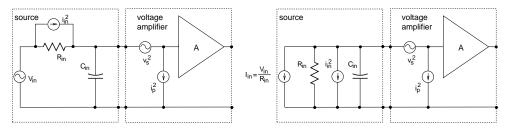

|          | 4.2             | Voltag  | e Amplifier                                                                                                                             | 45        |

|          |                 | 4.2.1   | Resistive Source Impedance                                                                                                              | 45        |

|          |                 | 4.2.2   | Resistive and Capacitive Source Impedance                                                                                               | 46        |

|          |                 | 4.2.3   | Charge Measurement with a Voltage Amplifier                                                                                             | 47        |

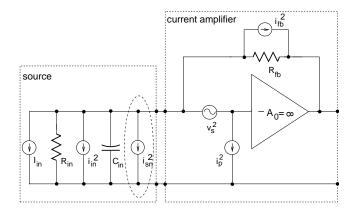

|          | 4.3             | Currer  | nt Amplifier                                                                                                                            | 48        |

|          |                 | 4.3.1   | Resistive and Capacitive Source Impedance                                                                                               | 48        |

|          |                 | 4.3.2   | Example: Photodiodes                                                                                                                    | 49        |

|          |                 | 4.3.3   | Charge Measurement with a Current Amplifier                                                                                             | 50        |

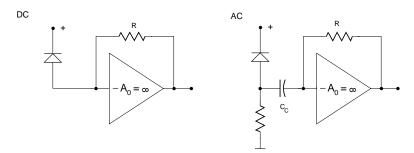

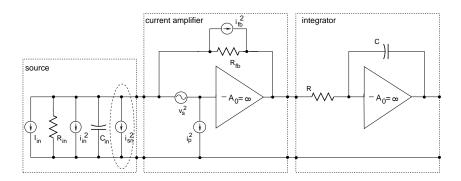

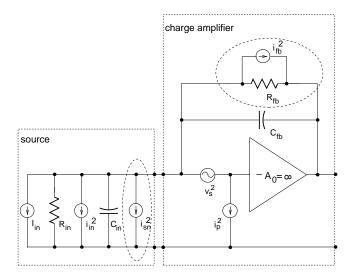

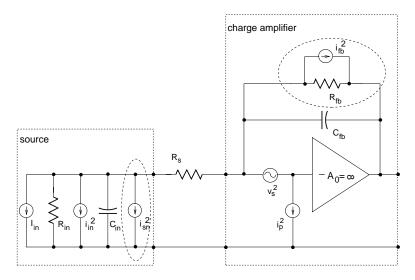

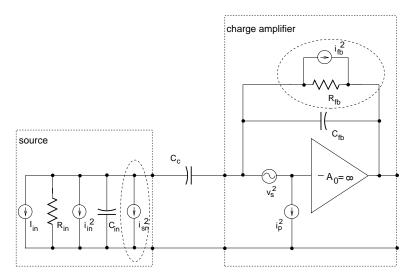

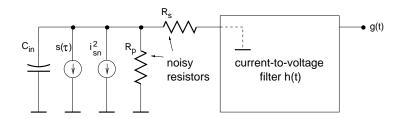

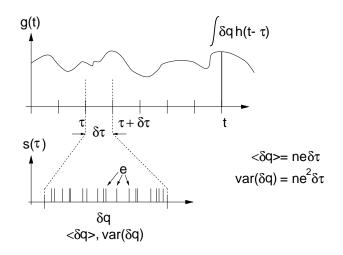

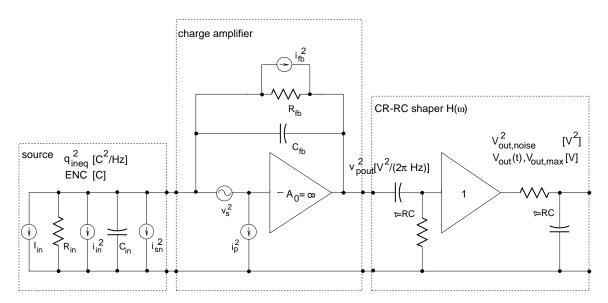

|   | 4.4  | Charge Amplifier                                                                                                                                         | 1          |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |      | 4.4.1 Parallel Resistive and Capacitance Source Impedance                                                                                                | 51         |

|   |      | 4.4.2 Example: Radiation Detectors                                                                                                                       | 52         |

|   |      | 4.4.3 Serial Resistive Source Impedance                                                                                                                  | 5          |

|   |      | 4.4.4 AC-Coupled Charge Amplifier                                                                                                                        | 6          |

| 5 | Ana  | log Signal Processing - Basics 5                                                                                                                         | 9          |

|   | 5.1  | Time Invariant Filters                                                                                                                                   | 60         |

|   |      | 5.1.1 Frequency Domain                                                                                                                                   | 60         |

|   |      | 5.1.2 Time Domain $\ldots \ldots \ldots$ | 51         |

|   | 5.2  | Time Variant Filters                                                                                                                                     | 58         |

|   |      | 5.2.1 Frequency Domain                                                                                                                                   | 58         |

|   |      | 5.2.2 Time Domain                                                                                                                                        | 58         |

| 6 | Ana  | log Signal Processing in Impulse-Technique 7                                                                                                             | 3          |

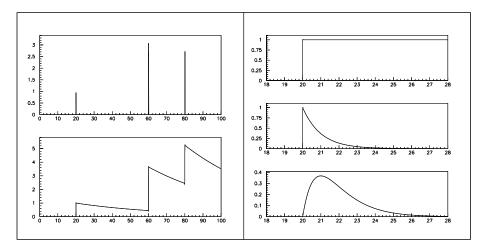

|   | 6.1  | Single Sampling                                                                                                                                          | 73         |

|   |      | 6.1.1 Sampling at Charge Amplifier Output                                                                                                                | 73         |

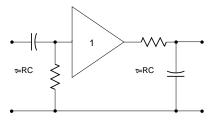

|   |      | 6.1.2 Sampling at CR-RC Filter Output                                                                                                                    | 7          |

|   | 6.2  | Double Correlated Sampling                                                                                                                               | <b>'</b> 9 |

|   |      | 6.2.1 Sampling at Charge Amplifier Output                                                                                                                | 30         |

|   |      | 6.2.2 Sampling at CR-RC filter output                                                                                                                    | 31         |

|   | 6.3  | Multiple Correlated Sampling                                                                                                                             | 33         |

|   |      | 6.3.1 Sampling at Charge Amplifier Output                                                                                                                | 33         |

|   |      | 6.3.2 Sampling at CR-RC Filter Output (Deconvolution)                                                                                                    | 37         |

|   | 6.4  | Optimum Pulse Processing                                                                                                                                 | )1         |

|   | 6.5  | Comparison of concepts                                                                                                                                   | 97         |

| 7 | Inte | egrated Charge Amplifier Design 10                                                                                                                       | 1          |

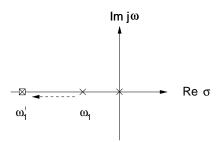

|   | 7.1  | Stability and Bandwidth                                                                                                                                  | )1         |

|   |      | 7.1.1 Introduction                                                                                                                                       | )1         |

|   |      | 7.1.2 Current Amplifier                                                                                                                                  | )2         |

|   |      | 7.1.3 Charge Amplifier                                                                                                                                   | )7         |

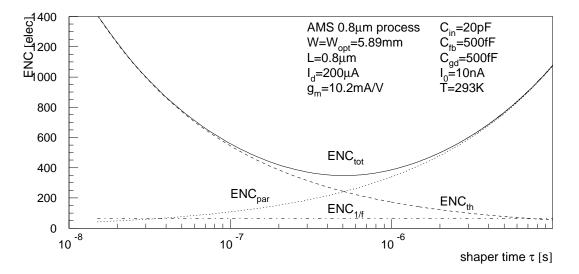

|   | 7.2  | Charge Amplifier Noise in Detail                                                                                                                         | .1         |

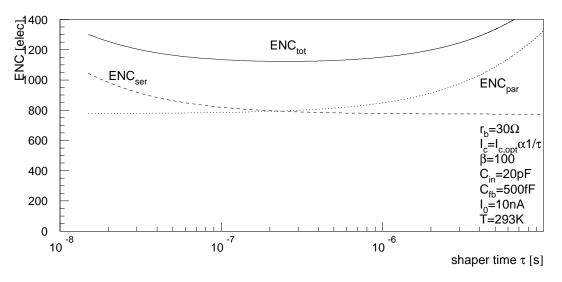

|   |      | 7.2.1 MOS Input Transistor                                                                                                                               | .1         |

|   |      | 7.2.2 Bipolar Input Transistor                                                                                                                           | .6         |

| 8            | $\mathbf{The}$                                              | HELIX Chip-Family                                                                                                                                                                                                                                                                                                                               | 123                                                                                                                                                       |

|--------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 8.1                                                         | Introduction                                                                                                                                                                                                                                                                                                                                    | 123                                                                                                                                                       |

|              | 8.2                                                         | Frontend - Preamplifier                                                                                                                                                                                                                                                                                                                         | 128                                                                                                                                                       |

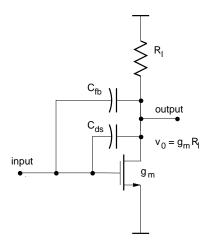

|              |                                                             | 8.2.1 Small Signal Model                                                                                                                                                                                                                                                                                                                        | 128                                                                                                                                                       |

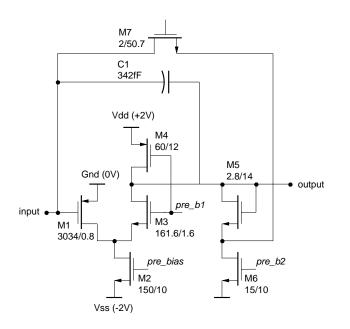

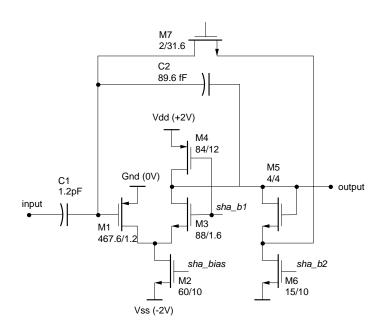

|              |                                                             | 8.2.2 Schematic                                                                                                                                                                                                                                                                                                                                 | 132                                                                                                                                                       |

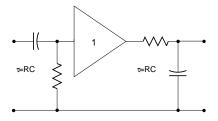

|              | 8.3                                                         | Frontend - Pulse Shaper                                                                                                                                                                                                                                                                                                                         | 134                                                                                                                                                       |

|              |                                                             | 8.3.1 Small Signal Model                                                                                                                                                                                                                                                                                                                        | 136                                                                                                                                                       |

|              | 8.4                                                         | Frontend - Buffer                                                                                                                                                                                                                                                                                                                               | 146                                                                                                                                                       |

|              | 8.5                                                         | Discriminator                                                                                                                                                                                                                                                                                                                                   | 147                                                                                                                                                       |

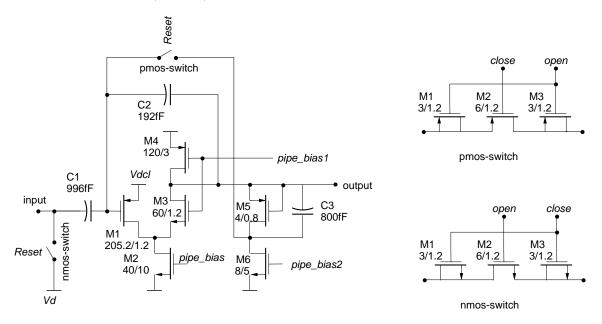

|              | 8.6                                                         | Pipeline                                                                                                                                                                                                                                                                                                                                        | 150                                                                                                                                                       |

|              | 8.7                                                         | Pipeline Readout Amplifier ("pipeamp")                                                                                                                                                                                                                                                                                                          | 154                                                                                                                                                       |

|              | 8.8                                                         | Multiplexer                                                                                                                                                                                                                                                                                                                                     | 159                                                                                                                                                       |

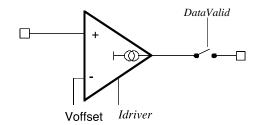

|              | 8.9                                                         | Current Buffer                                                                                                                                                                                                                                                                                                                                  | 163                                                                                                                                                       |

| 9            | Mea                                                         | asurement Results                                                                                                                                                                                                                                                                                                                               | 171                                                                                                                                                       |

|              | 9.1                                                         | Frontend                                                                                                                                                                                                                                                                                                                                        | 171                                                                                                                                                       |

|              | 9.2                                                         | Discriminator                                                                                                                                                                                                                                                                                                                                   | 172                                                                                                                                                       |

|              | 9.3                                                         | Overall Chip Performance                                                                                                                                                                                                                                                                                                                        | 172                                                                                                                                                       |

|              | 9.4                                                         | Conclusion                                                                                                                                                                                                                                                                                                                                      | 174                                                                                                                                                       |

|              |                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |

| $\mathbf{A}$ | Lap                                                         | lace-Transformation                                                                                                                                                                                                                                                                                                                             | 181                                                                                                                                                       |

|              | -                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |

| A<br>B       | Sma                                                         | all Signal Analysis                                                                                                                                                                                                                                                                                                                             | 183                                                                                                                                                       |

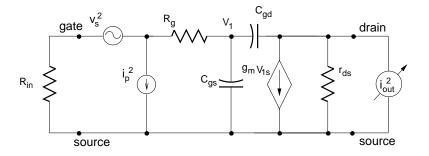

|              | Sma                                                         | all Signal Analysis<br>MOSFET                                                                                                                                                                                                                                                                                                                   | <b>183</b><br>184                                                                                                                                         |

|              | Sma                                                         | all Signal Analysis<br>MOSFET                                                                                                                                                                                                                                                                                                                   | <b>183</b><br>184<br>184                                                                                                                                  |

|              | Sma                                                         | all Signal Analysis<br>MOSFET                                                                                                                                                                                                                                                                                                                   | <b>183</b><br>184<br>184<br>185                                                                                                                           |

|              | Sma<br>B.1                                                  | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b><br>184<br>184<br>185<br>186                                                                                                                    |

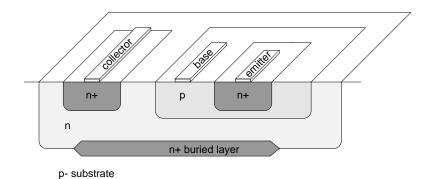

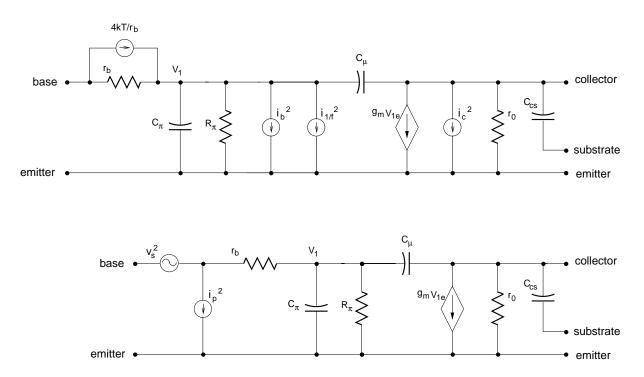

|              | Sma<br>B.1                                                  | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b> 184 184 185 186 189                                                                                                                            |

|              | Sma<br>B.1                                                  | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b> 184 184 185 186 189 189                                                                                                                        |

|              | Sma<br>B.1                                                  | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b> 184 184 185 186 189 189 190                                                                                                                    |

|              | Sma<br>B.1                                                  | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b> 184 184 185 186 189 189 190                                                                                                                    |

|              | Sma<br>B.1<br>B.2                                           | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <b>183</b> 184 184 185 186 189 189 190                                                                                                                    |

| В            | Sma<br>B.1<br>B.2                                           | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <ul> <li>183</li> <li>184</li> <li>185</li> <li>186</li> <li>189</li> <li>189</li> <li>190</li> <li>191</li> <li>193</li> </ul>                           |

| В            | <b>Sma</b><br>B.1<br>B.2<br><b>HEI</b>                      | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <ul> <li>183</li> <li>184</li> <li>185</li> <li>186</li> <li>189</li> <li>189</li> <li>190</li> <li>191</li> <li>193</li> </ul>                           |

| В            | <b>Sma</b><br>B.1<br>B.2<br><b>HEI</b><br>C.1               | All Signal Analysis         MOSFET                                                                                                                                                                                                                                                                                                              | <ul> <li>183</li> <li>184</li> <li>185</li> <li>186</li> <li>189</li> <li>189</li> <li>190</li> <li>191</li> <li>193</li> <li>193</li> </ul>              |

| В            | <b>Sma</b><br>B.1<br>B.2<br><b>HE1</b><br>C.1<br>C.2<br>C.3 | All Signal Analysis         MOSFET         B.1.1         Basics         B.1.2         Large Signal Model         B.1.3         Small Signal Model         Bipolar Transistor         B.2.1         Basics         B.2.2         Large Signal Model         B.2.3         Small Signal Model         LIX128S-2.x-Genealogy         HELIX128S-2.1 | <ol> <li>183</li> <li>184</li> <li>185</li> <li>186</li> <li>189</li> <li>189</li> <li>190</li> <li>191</li> <li>193</li> <li>193</li> <li>194</li> </ol> |

### Chapter 1

# Introduction

Symmetries and conservation laws are important objects of physical research. For example the electromagnetic interaction is invariant w. r. t. charge conjugation<sup>1</sup> C or parity transformation<sup>2</sup> P. From the invariance of physical systems follow important physical laws like the Coulomb-law of electrical force.

The weak interaction, however, violates C-symmetry as well as P-symmetry. The combined CP-symmetry was assumed to be conserved by weak interaction, until in 1964 CP-symmetry violation was observed in the decay of neutral  $K^0$ -mesons, too [Berg92, Na89, Povh96].

The experiment HERA-B [HB94/95, Hof93, SP97] will examine CP-violation in the decay of neutral *B*-mesons. In this decay a unique possibility exists to verify a theoretical explanation of CP-violation which has been introduced by M. Kobayashi and T. Maskawa [KM73]. They discovered that under certain circumstances the weak interaction would automatically cause CP-violation if there were at least 6 quarks.

*B*-mesons will be produced with a fixed-target experiment at the HERA proton storagering at DESY (Deutsches Elektronensynchrotron), Hamburg. When the high-energetic protons collide with the fixed target, neutral *B*-mesons are created by strong interaction, which decay (with small probability) according to

$$B^0 \to J/\Psi K_s^0 \to l^+ l^- \pi^+ \pi^- \qquad \overline{B^0} \to J/\Psi K_s^0 \to l^+ l^- \pi^+ \pi^-$$

which is reffered to as the "golden channel". If CP-symmetry was violated,  $B^0$  and  $\overline{B^0}$  would decay into the CP-eigenstate  $J/\Psi K_s^0$  with different probabilities (rates). The distinction between a  $B^0$ - and a  $\overline{B^0}$ -decay is achieved by "flavour tagging": because a *b*-quark is always created together with a  $\overline{b}$ -quark, there exists a second *B*-meson carrying the complementary flavour of the  $B^0$ - resp.  $\overline{B^0}$ -meson under investigation. Since *b*-quark and  $\overline{b}$ -quark carry different electrical charge, it is possible to conclude the quark-flavour from the charge of the second *B*-meson's decay products.

The major challenge of the experiment is the discovery of the above described decay in a large background of competing events; at the HERA proton-energy of 830 GeV  $B^0$ mesons are produced in only one out of  $1.3 \cdot 10^6$  collisions. Furthermore, the "gold-plated"

<sup>&</sup>lt;sup>1</sup>a particle is substituted by its anti-particle

<sup>&</sup>lt;sup>2</sup>space reflection

decay occurs only for one out of  $2.3 \cdot 10^4$  created  $B^0$ -mesons. The detector contributes according to estimations another factor of 10 due to unavoidable insufficiencies.

Considering all factors approx.  $3 \cdot 10^{11}$  collisions have to be examined in order to identify one  $B^0$ -decay into the golden channel; to make a quantitative statement about the intensity of CP-volation approx. 7000  $B^0/\overline{B^0}$ -decays must be collected, which leads to a collision rate of 30 MHz (at one year of data taking). This implies that – since the frequency of proton bunches is 10 MHz – at average 3-4 collisions have to take place per bunch crossing. It becomes evident that the construction of the particle detector and the trigger is an ambitious undertaking.

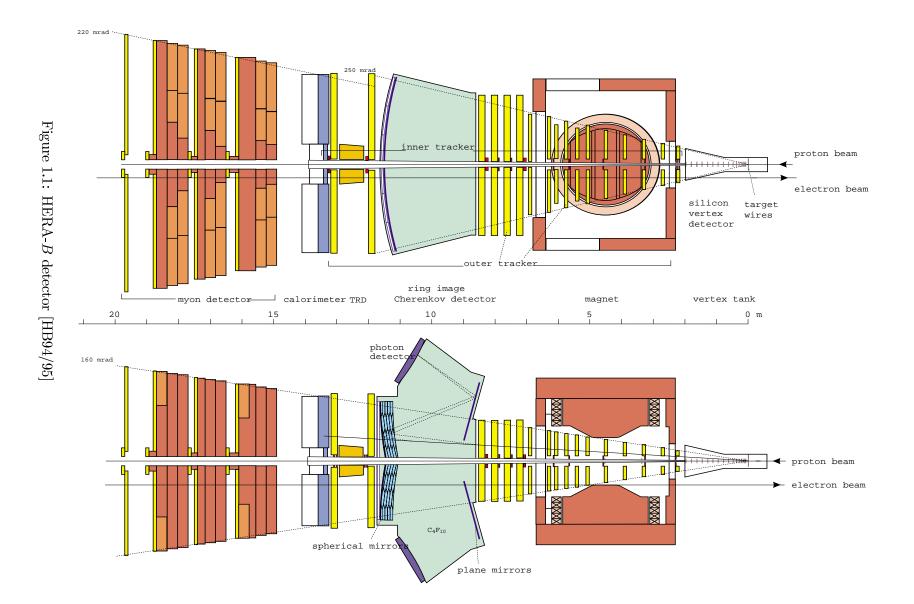

### **1.1 HERA-***B* Detector

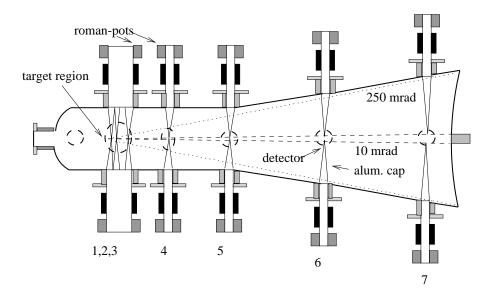

The HERA-B detector [HB94/95] (fig. 1.1) is a magnetic spectrometer; its main tasks are the identification of the particles created in the collision, a measurement of their momentum (for this a precise particle track measurement is essential), their energy and the determination of their point of nascence.

The  $B^0/\overline{B^0}$  mesons are produced by collision of a proton beam at a fixed target consisting of aluminium resp. copper ribbons which are located such that protons of the beamhalo (i. e. from the outer, less populated beam region) interact at 40 MHz rate. After generation in the ribbons, *B*-mesons move approx. 9 mm, before they decay. The decay vertex resolution required to study CP-violation is typically 10% of this value. The *silicon vertex detector (SVD)* [Knö95] which is located directly behind the target, has to find these displaced (w. r. t. the ribbons) *B*-decay vertices. The SVD will be discussed in further detail in section 1.2.

A central component of the HERA-B detector is the *dipole magnet* which creates a magnetic field behind the SVD approx. 4.5 m apart from the target. Due to the (momentum-dependent) Lorentz-force tracks of charged particles are bent which enables measurement of the particles' momentum. A particular challenge is the shielding of the electron beam which also traverses the magnet field. The electrical field may not exceed a few hundred Gauss inside the electron beam pipe. The problem is overcome by use of highly permeable steel as passive shielding and an active shielding of magnetic coils counteracting the dipole field.

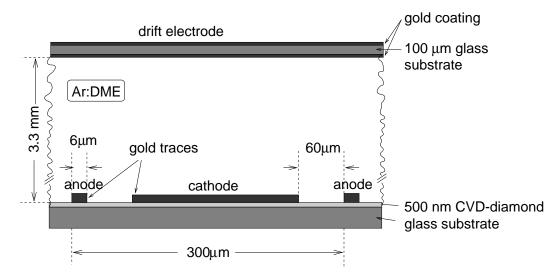

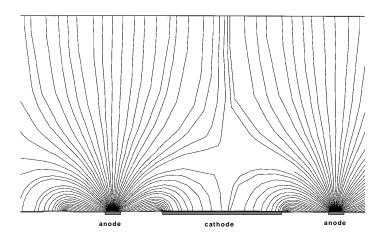

The inner tracker detector [Schm97] measures particle tracks near the proton beam pipe; it covers an angle from 10 mrad up to 20-25 cm distance from the beam pipe and is located along the beam axis from behind the SVD to approx. 13 m behind the target. It is made of microstrip gas chambers (MSGCs) (chapt. 3) which are positioned in ten super layers each consisting of two to eight layers of chambers with angles of 0° and  $\pm 5^{\circ}$  w. r. t. the vertical. The four chambers of a layer (one in each quadrant) overlap for better efficiency and for better relative alignment. The inner tracker detector has a total of approx. 135 000 channels to be read out, and - since it has to deliver fast information on hit channels for the level 1 trigger - approx. 18400 trigger output signals.

The outer tracker detector [Kap96] covers the larger angles starting from the outer edge of the inner tracker up to 200 mrad from the beam axis. Proportional drift chambers (see chapt. 3) with circular or hexagonal cross section and a mixture based on  $CF_4$  as fill gas will be taken for particle detection. The minimum diameter has been chosen to be 5 mm due to the danger of high voltage flash-over and due to the resolution distortion near the anode wire. The wire positioning should be precise to approx. 100  $\mu$ m in order not to deteriorate the intrinsic resolution of the chambers. The total number of channels will be 96000.

The ring image Čerenkov detector (RICH) [Kriz98] uses the Čerenkov-effect: elementary particles emit visible or UV-photons when traveling a medium with a velocity higher than that of light. The radiatior gas chosen is  $C_4F_{10}$ . The aperture of the light cone depends on the particle velocity and can be used together with a measurement of the particle's momentum or energy for determination of the particle's mass and hence for identification; at HERA-B it is mainly used for the identification of kaons. By proper design of a spherical mirror the cones are projected as rings onto a photon detection plane. The single photon detection is achieved by an array of multi-anode photomultipliers (quantum efficiency max. 20 %); the Hamamatsu H6568 photomultiplier under investigation has a bialkali photocathode with the anode divided into 16 pads of 4 mm × 4 mm each. The 12-stage, metal-foil dynode system allows for good single photoelectron resolution. The total number of channels will be in the order of 40000.

The electromagnetic calorimeter (ECAL) [Gol95] which is located 13.25 m from the target serves for the energy measurement of photons in the range of 5 to 200 GeV and for the separation of hadronic particles from leptons; the ECAL contributes to the level 1 trigger. A shashlik-calorimeter with tungsten resp. lead absorber plates alternating with scintillator plates has been chosen; the position resolution is between 1.1 mm close to the beam axis and 10 mm at larger angles. Photons are absorbed inside the alternating structure giving rise to showers of electrons, positrons and secondary photons. The energy delivered to the scintillating layers is transfered to visible light and amplified using photmultipliers or photo-diodes. A total of 6500 channels has to be read out from the ECAL.

A transition radiation detector (TRD) [Sav96] enables further meson/hadron-lepton separation (in particular pions shall be separated from electrons). When traversing an interface of materials of different refractive indices, elementary particles emit transition radiation in the soft x-ray region; the energy distribution depends on the particle type. In the TRD the transitions are achieved by alternating radiator/chamber-layers (36 layers in total). The photons are created when the particle exits the radiator and are detected by the proportional chambers. For the radiators polyethylene-foam resp. fibres are under investigation; the proportional chambers are filled with a gas mixture based on krypton. A total of 77000 channels has to be read out.

The muon-chambers [Zai98] are located at the end of the HERA-*B*-detector and serve for the identification of muons to be used in the level 1 trigger decision. Prior to the muonchambers an absorber made of iron and concrete filters all particles beside muons created in the target-collision. Similar to the tracker detectors the muon-chambers consist of four super-layers, the first two with 0° and  $\pm 15^{\circ}$ -orientation to the vertical, the last with only 0° orientation. The muon-chamber-layers are composed of gas-pixel-detectors (10 mm  $\times$  10 mm) in the central region and multiwire proportional chambers resp. proportional chambers with cathode-pad readout in the outer region. The fill gas to be used is a mixture based on argon. A total of 29500 channels must be read out.

### **1.2** Silicon Vertex Detector (SVD)

The silicon vertex detector (SVD) [Knö95] being one of the subdetectors of HERA-B supplied with the HELIX128S-2-readout chip shall be discussed in greater detail. It is the SVD's task to find the displaced B-meson decay vertices with a resolution of 500  $\mu$ m in z (beam)-direction and 25  $\mu$ m in transversal direction. The SVD comprises a total of 165000 channels. The following treatment has been taken from [Knö95].

### 1.2.1 Geometrical Layout

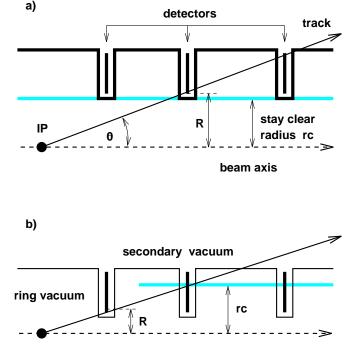

The ultimate limit of resolution of any vertex detector system is given by multiple scattering in the material between track vertex and the first point of the track measurement (i. e. not by the detector granularity itself !). Since the particles are created inside an evacuated beam pipe, the particles' path when traversing the pipe has to be minimized. As solution to this problem a "roman pot" [Rom1] configuration has been chosen where the beam pipe is folded around the detector planes (Fig. 1.2a) ).

Figure 1.2: a) Schematic layout of a forward vertex detector based on a roman pot system, i.e. a 'folded' beam pipe; b) A mobile roman pot system can be moved closer to the beam during data taking [Knö95].

Now, the particles hit the "pipe" almost perpendiculary so that the effective thickness of the wall material is minimized. Further reduction of the multiple scattering has been achieved by placing the detectors in a secondary vacuum so that the windows of the pot system could be chosen as thin as  $100\mu$ m.

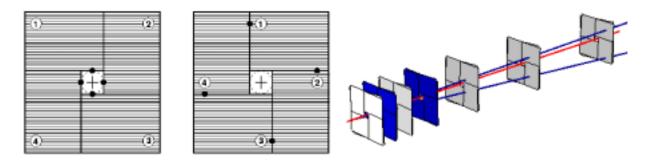

Fig. 1.3 shows the vertex detector to comprise 7 superlayers positioned between the wire targets (z = -55 mm and 0 mm) and the dipole magnet at z = 2.3 m. Its angular coverage is consistent with the overall HERA-*B*-detector's acceptance from 10 mrad polar angle

Figure 1.3: Left: alternative detector arrangements to reduce radiation damage to innermost detector regions; right: schematic 3-d plot of the SVD's 7 superlayers [Knö95]

(to the beam axis) to about 200 mrad corresponding to 90% of  $4\pi$  in the center of mass system.

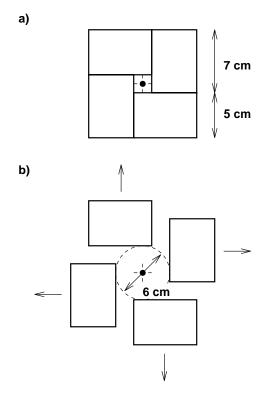

The individual detector planes of a superlayer (fig. 1.4) consist out of two double-sided detector elements which provide four views,  $\pm 2.5^{\circ}$  and  $90^{\circ} \pm 2.5^{\circ}$ . Each detector element has a sensitive area of  $50 \times 70 \text{ mm}^2$  so that it can be cut from a 4" wafer. The segmentation into quadrants allows the choice of two different detector arrangements which will be exploited to stagger the support posts of subsequent superlayers, and to rotate detector positions in order to distribute the radiation load over a larger detector area (fig. 1.3). During fills these elements will be retracted to safe positions as shown in fig. 1.4

#### 1.2.2 Radiation Damage

The radiation environment at HERA-B is described by a flux of particles which is, at a fixed perpendicular distance R to the beam axis, approximately independent of polar angle, and which falls off with  $1/R^2$ . The innermost edges of the silicon detectors will be exposed to a fluence of typically  $3 \cdot 10^{14}$  particles, mostly relativistic pions, per  $10^7$ seconds year. So far, no silicon vertex detector has ever been operated up to such a fluence, but intense research on radiation damage carried out by [Riech96] and in the context of LHC and SSC projects is indicating that silicon microstrip detectors of appropriate design can indeed tolerate such a fluence. The limiting factor is primarily not the increase of leakage current since the shot noise contribution is optimized by adequate signal filtering, but rather the change of effective doping concentration far beyond type inversion. Due to the permanent creation of acceptor-like defects, the bias voltage required for full depletion of a a  $280\mu$  thick silicon strip detector will be by far more than 200 V which is currently considered to be the limit for safe operation of these devices. Possible solutions to this problem include the use of thinner detectors (depletion voltages scale with the square of detector thickness), the implementation of novel guard ring structures, appropriate cooling of detectors to  $< 10^{\circ}$  C in order to take advantage of beneficial annealing while avoiding the detrimental reverse annealing effects, as well as

Figure 1.4: Arrangement of the 4 detector elements in a sublayer of the SVD: a) wafer positions at run time, b) wafers withdrawn during the beam filling process; arrows point towards readout chips and mounting structures. - The alternative detector arrangement w.r.t. a) is obtained by a 5 cm clockwise shift of wafers in horizontal respective vertical directions (see fig. 1.3)[Knö95].

rotation of detector positions at HERA-B to distribute the radiation load over a larger detector area.

#### **1.2.3** Electronic Readout

Efficient processing of the vertex detector's 165 000 channel's has to rely on custom-made VLSI readout chips. Chip size and readout pitch must be compatible with the 50  $\mu$ m readout pitch of silicon strip detectors (chapt. 2).

The basic functionality of the targeted chip can be summarized as follows: The charge generated by elementary particles inside silicon strip detectors must be amplified and successively stored in a ring buffer; in event of a (delayed) level one trigger the signal value associated to the trigger must be retrieved from the ring buffer and be transferred to the optical link. As a surplus the chip would also be suitable for the readout of microstrip gas chambers (chapt. 3).

The major specifications for the chip performance are constrained by [HB94/95]

- the expected signal charge of 5900 electrons per channel (worst case)

- the bunch crossing frequency of 10 MHz

- the level one trigger latency of  $\approx 10 \ \mu s$

- the level one trigger frequency of  $\approx 100$  kHz (this indicates 25 ns readout time per channel, if 256 channels have to be transferred in the given time window accounting for the statistical occurrence of the trigger)

- the anticipated effects from the radiation damage to the silicon detectors

The requirements on the HERA-B vertex detector readout closely ressemble those of the future ATLAS [ATL94] and CMS [CMS94] tracking detectors (both at CERN, Geneva). The development of the HELIX128S-2-frontend chip [Fal95-1, Fal95-2, Fal96, Fal97-2, Feu96, Tru97] (AMS 0.8  $\mu$ m-process [AMS95-2]) could therefore profit largely from the architecture developed by the CERN-research group "RD20" [RD20-1, RD20-2, RD20-3, RD20-4].

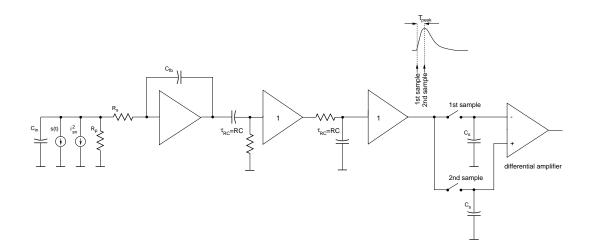

128 detector channels are handled by one HELIX128S-2-frontend chip. The channel architecture consists of a low noise charge-amplifier with subsequent shaper of approx. 50 ns peaking time the output of which is sampled at 10 MHz and stored in a 128 cell deep analog pipeline to await the level one trigger-decision. In the event of a level one trigger, the appropriate analog samples of 128 detector channels are multiplexed to one serial output line. Occuring concurrently with data sampling, readout is practically dead-timeless.

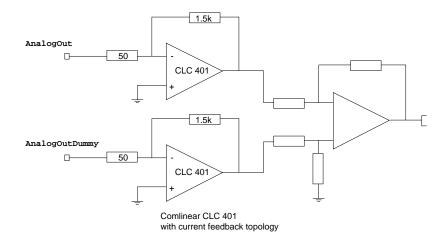

The time-multiplexed output signals of the frontend chips will be transmitted via optical analog fiber links to the counting room where subdetector specific readout boards will represent the interface to the detector wide data acquisition system. With regard to the vertex detector system, the minimum functionality of these readout boards comprises digitization and adequate buffering of the data received. Further desirable features include pedestal subtraction, common baseline shift correction, cluster finding and sparsification, as well as data formatting.

### 1.2.4 Mechanics and Engineering

The principal engineering problem encountered at HERA-B was to design a mechanical system that would take into account the various, sometimes rather contradictory requirements: retractable detector arrangement, invariant alignment of detectors over extended distance - within subgroups at least, low-mass support structure within the geometrical acceptance, and negligible impact on HERA's proton ring vacuum.

The detector system including the target wire assemblies are contained in a vacuum vessel (fig. 1.5) with an exit window and an integrated tapering beam pipe for the rest of the HERA-B experiment at one end and a connection to the standard beam line system at the other. The overall length of the vessel is about 2.5 m and its maximum radius is 58 cm. The exit window is kept as thin as possible, i.e. about 3 mm if fabricated of aluminium. The silicon wafers are maintained at a secondary vacuum of  $10^{-6}$  mbar and the main stainless steel vessel at  $10^{-8}$  mbar. The complete system is mounted on a vibration dampened platform, and the thermal and humidity environment has to be stabilized.

Each quadrant of a superlayer is contained in a removable pot assembly that can be displaced individually in lateral direction to the beam by an external motorized mobile bearing unit. The wafers of the three superlayers next to the target wires are contained in a single pot. The  $125\mu$ m thick aluminium shielding caps separate secondary and primary

Figure 1.5: Silicon vertex detector tank [Knö95]

vacumm and serve as protection against rf interference from the beam. Detectors and readout chips are cooled via separate cooling paths connected to cooling blocks located outside the acceptance cone. Desirable heat drain materials are characterized by a maximum product of radiation length and thermal conductivity.

### 1.2.5 Alignment

While the final detector positions will be established by software alignment using the actual tracks from the proton-wire collisions, sufficiently fast convergence of this procedure is only guaranteed if the relative locations of the detector wafers are know with adequate accuracy even after the periodic repositioning cycles. A novel long distance laser alignment system has been chosen to accomplish this task [BKW95]. The positions of pots along each quadrant row will be continously monitored by using collimated laser beams as alignment references and semi-transparent optical position sensors being attached to the pots. At an active area of  $2 \times 2$  cm<sup>2</sup>, these sensors are reported to deliver both the x and y coordinates with a precision on the order of 1  $\mu$ m which, if achieved also in field, would be clearly superior to any mechanical reference system exposed to varying forces and temperatures.

### Chapter 2

# Silicon Detectors

When elementary particles or photons interact with silicon material, charge carriers of opposite polarity (electrons, holes) are created; collecting and measuring the generated charge gives a measure for the incident particle's location and energy loss.

The processes involved resemble the interaction of particles with gases. There are, however, quantitative differences between the interaction of ionizing radiation with a semiconductor material and with a gas resp. a fluid. First, the energy necessary to generate an electron-hole pair in silicon amounts to approx. 3.6 eV, whereas there are (at average) 30 eV necessary in a gas. Secondly, the absorption of silicon (density 2.3 g/cm<sup>3</sup>) is considerably higher than that of gases with densities (depending on the gas pressure) of  $10^{-3}$  to  $10^{-1}$  g/cm<sup>3</sup>.

From a technical point of view, silicon as detector material is an attractive choice, since semiconductor processing is a well developed technology for the fabrication of integrated circuits. Silicon wafers of high purity can be obtained at comparably low cost; photolithographical methods can be employed to build electrode structures on top of the substrate.

The physical properties of silicon in combination with the technical aspects offer the possibility to construct particle detectors with high spatial and energy resolution as well as fast timing.

### 2.1 Charge Creation

When traversing silicon the ionizing particle transfers energy and momentum to the crystal lattice and electrons. Two different mechanisms can be separated:

- 1. Crystal vibrations (phonons) are excited by (mainly) momentum transfer; this effect is not desired, since phonons cannot be detected by means of electrical amplifiers

- 2. Electron-hole pairs are created by excitation of electrons from the valence band to the conduction band.

We will further on concentrate on the second mechanism. Neglecting channeling-, Čerenkovand transition radiation as well as high energy transfer processes ( $\delta$ -electrons) the mean energy loss per unit path length  $\langle \frac{dE}{dx} \rangle$  (also called stopping power) of a charged particle can be described by the Bethe formula [Beth33]

$$<\frac{dE}{dx}> = -\frac{4\pi q^4 z^2 nZ}{m_e v^2} \left\{ \ln\left[\frac{2m_e v^2}{I(1-\beta)}\right] - \beta^2 \right\}$$

(2.1)

v particle velocity

eta = v/cz charge of incident particle n atom density of medium Z atomic number of medium I average ionization potential ( $I_{Si}$ =172 eV)  $m_e$  electron rest mass q electron charge

The ionization potential to be used in the Bethe-formula is the value for the primary ionization processes when energy and momentum is transferred mainly to electrons of inner shells of the silicon atoms. It can be seen from eq. (2.1) that the energy loss increases at low particle velocities with  $1/v^2$ ; if a particle stops in a material, most of its total energy is delivered at the very end of its track (Bragg-peak).

The distribution of the energy loss per unit path length  $\frac{dE}{dx}$  is approximated by the Landau-distribution [Lan44]. The Landau-distribution is asymmetrical with a high-energetic tail the latter being due to occasional high energy transfer to single electrons ( $\delta$ -electrons).  $\delta$ -electrons ultimately limit the resolution of silicon strip detectors since they can travel several dozens of  $\mu$ m delivering energy to valence-band electrons before they finally stop (resp. escape the detector volume).

The variance of the Landau-distribution is considerably smaller than the so-called  $\sqrt{N}$ error of counting processes (which is subject to the Poisson distribution). It can be therefore be inferred that the ionization events along the track are not statistically independent. Since the Landau-distribution is often not at hand, a phenomenologic number F (the so-called Fano-factor) has been introduced [Kno97] which makes it possible to refer the variation observed to the Poisson-distribution:

$$\operatorname{var}(Q) = \sigma^2(Q) = F < Q > = F \frac{\langle E \rangle}{\epsilon}$$

(2.2)

< Q > average charge delivered in the detector

$\langle E \rangle$  average energy delivered in the detector

$\epsilon{=}3.6$  eV energy to create one electron-hole pair

${\cal F}$  Fano-factor

For a Poisson-distribution the Fano-factor would be 1; for silicon the Fano-factor varies between 0.084 and 0.143.

For a minimum ionizing particle (MIP) of elementary charge q like a 1-2 MeV electron the average energy loss per unit path length in silicon amounts to  $\langle \frac{dE}{dx} \rangle \approx 390 \text{ eV}/\mu\text{m}$ [PDG84] or 110 electron-hole-pairs per  $\mu\text{m}$ . The most probable energy loss (note the asymmetry of the Landau-distribution) is 290 eV/ $\mu$ m corresponding to 82 electron-holepairs per  $\mu$ m yielding 88 keV or 24600 electron-hole-pairs in a 300  $\mu$ m silicon detector. Hence, the average energy  $\epsilon$  for lifting an electron into the conduction band is approx. 3.6 eV which is larger than the bandgap of 1.12 eV.

Electrons and holes can recombine again creating photons and phonons; to separate the electron-hole pairs an external voltage is applied to the detector electrodes. However, with *homogenous* silicon being a semiconducting material, application of a high voltage would cause a significant current to flow due to the thermally excited electrons in the conduction band which would superimpose on the charge signal by elementary particles (the same argument holds for electronic silicon material).

By doping of the silicon spatially inhomogenous charge carrier densities are created; by appropriate order of the layers (pn-junction) and external biasing the thermally induced current is suppressed and measurements at room temperature can be performed.

| atomic mass                               | 28.09  amu                             |

|-------------------------------------------|----------------------------------------|

| crystal lattice                           | diamond                                |

| lattice constant                          | 5.43 Å                                 |

| relative dielectric constant $\epsilon_r$ | 11.9                                   |

| breakdown field strength                  | aprox. $3 \cdot 10^5$ V/cm             |

| bandgap (300 K)                           | $1.12  \mathrm{eV}$                    |

| intrinsic charge carrier density (300 K)  | $1.45 \cdot 10^{10} \mathrm{~cm^{-3}}$ |

| n-substrate doping concentration          | $1.5-2 \cdot 10^{12} \text{ cm}^{-3}$  |

| electron mobility $\mu_n$ (300K)          | $1380 \ {\rm cm^2/(Vs)}$               |

| electron diffusion constant $D_n$ (300K)  | approx. $35 \text{ cm}^2/\text{s}$     |

| hole mobility $\mu_p$ (300K)              | $450 \ {\rm cm^2/(Vs)}$                |

| hole diffusion constant $D_n$ (300K)      | approx. 11 $\rm cm^2/s$                |

Table 2.1: Physical properties of detector silicon [Sze81]

Doping is achieved by addition of certain impurities. Some of the silicon atoms in the crystal lattice are replaced by atoms of different elements; when adding phosphorus or arsenic ("donors"), each of which contributes five electrons, a loosely bound excess electron not involved in bonds to the neighbour atoms is created, which easily is excited into the conduction band. The material becomes conductive for electrons and is called n-type.

Adding atoms with three electrons ("acceptors") like boron or aluminium to the silicon substrate introduces vacancies (or holes) in the valence band. The material becomes conductive for holes and is called p-type.

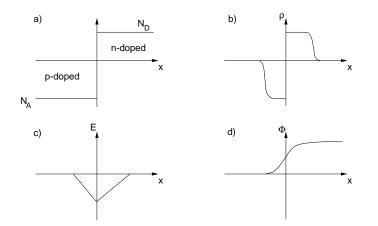

At the junction of p-doped and n-doped silicon regions a diffusion current flows due to the difference of charge carrier concentrations; a current of electrons flows from the n-type region to the p-type region and vice versa (see fig. 2.1 a) ). This double flow produces a double layer of static positive and negative charge on both sides of the junction fig. 2.1 b), setting up a potential difference  $V_D$  across the junction (fig. 2.1 c) ). In equilibrium, diffusion current and field induced current are equal; due to recombination of the free charge carriers nearly no free charge carriers exist in the junction region. It is important to recognize that this depletion layer is the only ionization sensitive volume of a detector since only there an electrical field is present.

Figure 2.1: Pn-junction in thermal equilibrium: a) doping profile, b) space charge density  $\rho$  c) electrical field E, d) potential  $\Phi$

Applying externally a voltage of the same polarity as  $V_D$  (reverse bias), the depletion zone increases into the n- and p-doped regions depending on doping- and charge carrier concentrations. The depth of the depleted layer is given by [AM81]

$$d_{n,p} = \sqrt{\frac{2\epsilon_0\epsilon_r(V_0 - V_D)}{q(n_D + n_A)}} \frac{n_A}{n_D} \quad . \tag{2.3}$$

$d_{n,p}$  depth of depletion layer in n- resp. p-doped regions

- $n_A$  acceptor concentration

- $n_D$  donor concentration

$\epsilon_0 \epsilon_r$  dielectric constant of silicon

$q = 1.6 \cdot 10^{-16}$  C electron charge

$V_0$  external voltage

For  $n_A \gg n_D$ ,  $V_0 \gg V_D$  and with the specific resistivity

$$\rho_n = (q\mu_n n_D)^{-1} \tag{2.4}$$

$\mu_n$  electron mobility

eq. (2.3) becomes

$$d_n = \sqrt{\frac{2\epsilon_0\epsilon_r V_0}{qn_D}} = \sqrt{2\epsilon_0\epsilon_r \mu_n \rho_n V_0} \quad . \tag{2.5}$$

The depletion depth increases with the square root of the reverse voltage  $V_0$  applied; the larger the purity resp. the resistivity  $\rho_n$  of a silicon substrate the easier large depetion depths can be reached. Typically one uses voltages  $V_0$  of 40V-140V to deplete high ohmic substrates of 300  $\mu$ m. At these voltages the wafer substrate is almost completely depleted and the whole detector depth becomes sensitive to ionizing radiation. Due to the pn-junction mechanism there is only a small diode leakage current flowing.

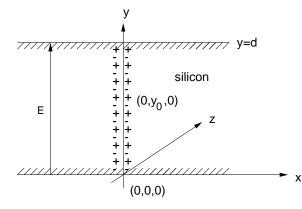

Figure 2.2: Silicon detector (schematic); a particle traverses the detector along the line x = z = 0. The drift of an electron-hole pair created at  $(0,y_0,0)$  is discussed in the text.

### 2.2 Signal Charge Transport

When a minimum ionizing particle traverses the silicon detector at t = 0 along the line x = z = 0, it creates a cylinder of electron-hole pairs of approx. 0.1  $\mu$ m radius (fig. 2.2) [Kno97].

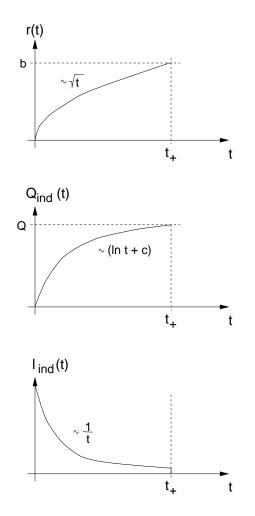

By applying an external field the electrons and holes are separated and drift to the electrodes. By induction a current is induced on the electrodes through the moving charges; it should be emphasized that the induction current obtained at the electrodes is sustained only during the charge migration inside the capacitor volume; once a charge has reached the electrode, the current goes to zero again. The total current is a superposition of the currents created by electrons and holes.

The electrical field inside the fully depleted detector (fig. 2.2) can be obtained by solution of the Poisson-equation and (in this first-order model) consists only of a y-component [Bel83]

$$E_y(y) = \left[\frac{V_0 - V_D}{d} + \frac{2yV_D}{d^2}\right]$$

(2.6)

which can be simplified for  $V_0 \gg V_D$  to the simple capacitor formula (2.7) [Kno97]

$$E_y(y) = \frac{V_0}{d} = E_0$$

. (2.7)

The charge migration y(t) now is obtained by integration of

$$dt = \frac{dy_{n,p}}{v_{n,p}} = \frac{dy_{n,p}}{\mu_{n,p}E_0}$$

(2.8)

yielding

$$y_{n,p}(t) = \pm \mu_{n,p} E_0 t + y_0 \tag{2.9}$$

where  $(0, y_0, 0)$  denotes the place of creation of the electron-hole pair.  $E_0$  is assumed to be constant, i. e. we assume the induced voltage  $dV_0$  due to the charge drift to be small w. r. t. the detector voltage  $V_0$ .

The drift time  $t_{n,p}(y_0)$  of an electron/hole to the anode/cathode plane at y = 0 resp. y = d is simply given by

$$t_n(y_0) = \frac{y_0}{v_n} = \frac{y_0}{\mu_n E_0} = \frac{y_0 d}{\mu_n V_0}$$

$$t_p(y_0) = \frac{d - y_0}{v_p} = \frac{d - y_0}{\mu_p E_0} = \frac{(d - y_0)d}{\mu_p V_0} \quad .$$

(2.10)

The potential energy dW/dy per unit path length delivered by the motion of a charge Q is given by

$$dW = QE_y(y) \, dy = QE_0 \, dy \quad . \tag{2.11}$$

This energy must come at the expense of the energy stored on the detector capacitance (we assume the detector to be floating)

$$dW = d(\frac{1}{2}CV_0^2) = CV_0 \, dV_0 = V_0 \, dQ_{ind}$$

(2.12)

where  $dQ_{ind}$  is the induced charge at the electrodes.

The induced charge  $Q_{ind}(t)$  can be obtained by equating eq. (2.11) and (2.12)

$$\frac{dQ_{ind-n,p}}{dy} = \frac{Q_{n,p}}{d} \quad . \tag{2.13}$$

By integration we obtain

$$Q_{ind-n+p} = q(\frac{v_n}{d}t + \frac{v_p}{d}t)$$

(2.14)

for the combined electron-hole current. Eq. (2.14) holds for the case that both electrons and holes contribute to the current, i. e. none of them has already reached an electrode. By substitution of the drift times eq. (2.10) into eq. (2.14) the totally induced charge  $Q_{ind-n+p}$  is found to be equal the charge Q produced by ionization.

The current is easily derived by dividing eq. (2.14) by t

$$I_{ind-n+p} = \frac{q}{d}(v_n + v_p)$$

(2.15)

which holds when both sorts of charge carriers contribute. Thus, the current delivered by the planar detector is constant in time and is zero at latest after the hole collection time  $t_p(y_0 = 0)$ . For  $V_0=100$ V and a 300  $\mu$ m thick silicon detector  $t_p(y_0 = 0)$  is 20 ns. Experimental evidence of the charge collection time inside silicon strip detectors [Ru94] yields that 90% of the charge is collected within 12 ns for 100 V of detector bias, which drops to 7 ns for 300 V.

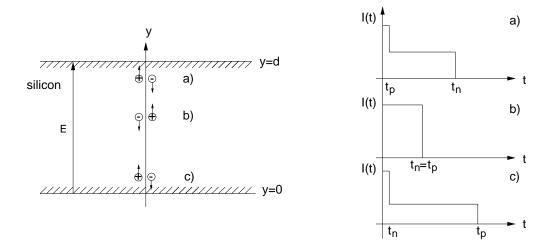

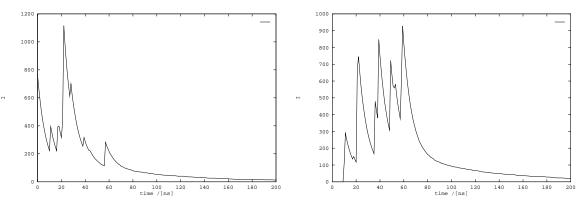

In the following chapters we will approximate the current pulses delivered by the silicon detector as  $\delta$ -shaped without comitting a large error (e. g. the preamplifier risetime equals  $\approx 50$  ns). A schematic plot of the current for various ionization loacations in the silicon detector is given in fig. 2.3

The total movement of the charge created along the particle track in the detector is superimposed by the field-independent diffusion parallel to the electrode plates and the field-induced drift in y-direction as given by eq. (2.15); by appropriate substitution and integration one can obtain the drift time distribution resp. the induced current as well as the spatial distribution of the signal charge at the electrodes.

Figure 2.3: Current induced at the electrodes by drift of an electron-hole pair in the detector; a), b), and c) denote the different ionization locations. The current is zero at latest after the collection time for a hole created at the anode  $(y_0=0)$ .

### 2.3 Silicon Strip Detector

Position sensitive detectors aim at measuring the point in one or two dimensions where a particle crosses the detector. Two principles are currently employed:

- 1. By segmentation of the p- resp. n-implantations the overall detector area is subdivided into many single diodes. With a particle crossing such a detector only the strips in the neighbourhood of the track collect charge. By appropriate weighting the spot of the particle incidence can be determined (siliccn strip detector, pixel detector).

- 2. By appropriate geometry of the electrode implantations the electrical field can be formed such that the signal charge drifts to a single electrode. By measuring the drift time the distance of the particle track to this electrode can be determined (silicon drift chamber).

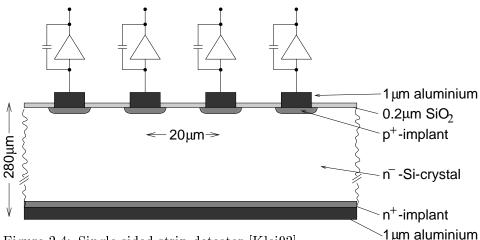

On silicon strip detectors, which follow the first principle, strip-like  $p^+$ -implantations (the "+" denotes a heavy dotation) are located perpendicularly to the drawing plane in fig. 2.4, each of them being read out by an own amplifier channel. The low-input-impedance amplifier keeps the  $p^+$ -implantations at ground potential. The reverse bias voltage is applied to the  $n^+$ -implantation on the detector back side.

Assuming a point-like (in the x-z plane) signal-charge distribution the position resolution  $\sigma$  obtainable depends only on the strip-spacing b [Lutz87] (also referred to as binary readout resolution):

$$\sigma = \frac{b}{\sqrt{12}} \tag{2.16}$$

If the charge cloud created by an ionizing particle reaches two or more strips, a centerof-gravity interpolation can determine the coordinate of the point of particle incidence;

Figure 2.4: Single-sided strip-detector [Klei92]

with the optimistic assumption of a rectangular charge distribution of width b (i. e. the strip-spacing) and the signal-to-noise ratio S/N of the detector/electronics system one obtains [Lutz87]

$$\sigma^{2} = \left(\frac{b}{S/N}\right)^{2} \sum_{i=1}^{n} \left(\frac{x_{1} - x}{b} + (i - 1)\right)^{2} \quad . \tag{2.17}$$

S/N signal-to-noise ratio

x calculated center-of-gravity

i strip index

$n,\;n\geq 2$  number of strips used in the calculation of the center-of-gravity

$x_1$  first strip used in the calculation

It follows that the optimum resolution is obtained when the signal of only two adjacent strips is evaluated; in this case and for a particle crossing in the middle of two strips eq. (2.17) simplifies to

$$\sigma^2 = \frac{b^2}{2 \cdot (S/N)^2} \quad . \tag{2.18}$$

For a strip spacing  $b = 25\mu$ m and a signal-to-noise ratio S/N=20 formula (2.18) gives a spatial resolution of 0.88  $\mu$ m (this was obtained under the optimistic assumption of a charge cloud of width b). In practical operation 10  $\mu$ m is already considered to be a good value.

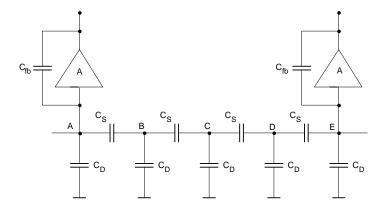

To reach high position resolution very small strip spacings are necessary which leads to high numbers of electronics channels. By using capacitive charge sharing [Kötz85] of adjacent strips this number can be decreased at little resolution degradation (fig. 2.5). In this scheme every n-th diode strip (n=2..5) is connected to an amplifier channel. By use of a high-ohmic connection the non-connected strips are kept on equal potential to assure a homogenous field distribution in the detector and a linear charge sharing.

Traverses a particle the detector at the non-connected strip B, the generated charge Q is collected at the corresponding diode strip. Due to the inter-strip capacitances  $C_S$  mirror charges are created at points A and E, where they are measured. Neglecting the backplane capacitances  $C_D$  the mirror charges obtained are  $Q_A = 3/4Q$  and  $Q_B = 1/4Q$ .

Figure 2.5: Capacitive charge sharing: every 4th strip is connected to a charge amplifier with input capacitance  $A \cdot C_{fb}$ . If a charge Q is put on node B, mirror charges can be obtained at nodes A and E where  $Q_A/Q_E=3$ .  $Q_A + Q_E < Q$  due to "charge loss" on the  $C_D$ 's [Bau90].

Hence by the use of capacitive charge sharing the charge distribution after ionization is broadened and fewer amplifier channels are needed.

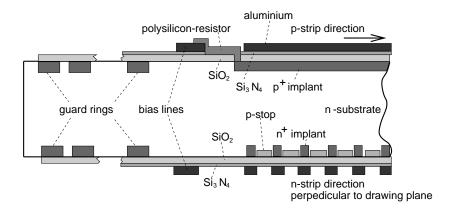

Fig. 2.6 shows the double-sided strip-detectors as used in the HERA-*B* silicon vertexdetector [Bis93, Riech98]. Strip-like electrodes have been implanted on both front- and back-plane; the p<sup>+</sup>-doped strips on the so-called p-side of the detector form a pn-junction with the n<sup>-</sup>-doped substrate; the n<sup>+</sup>-doped strips on the n-side which are rotated by 90 ° w. r. t. the strips on the p-side, form an ohmic contact to the n-substrate. By biasing the n<sup>+</sup>-strips with a positive high voltage w. r. t. the p<sup>+</sup>-strips, a detector depletion can be achieved as in the case of the single-sided detector.

At the n-side additional p-stop implants are necessary to operate the detector safely; this is due to the fact that the always present positive oxide charge in the silicon dioxide layer at the detector surface causes an n-inversion layer beneath (in analogy to MOSFET inversion) which causes a conductive path between adjacent  $n^+$ -strips; this effect worsens during the life time of the detector since the oxide charge augments during irradiation (this is also well known from MOSFET-physics). The p-stops introduce a reverse biased pn-junction decoupling the  $n^+$ -strips.

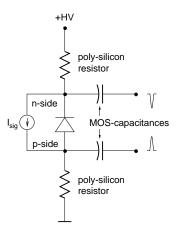

The detector depicted in fig. 2.6 is an AC-coupled detector, i. e. there is an oxide-layer between metallic contact and implant (MOS-structure); the advantage is that diode leakage currents do not flow into the amplifier inputs causing saturation. In the present design the coupling capacitances are 140 pF on the p-side and 100 pF on the n-side [Abt98]. An additional silicon nitride layer reduces the probability of shorts increasing the yield of "good" strips. In order to provide a DC-path for the detector biasing polysilicon resistors in the M $\Omega$ -range (see also fig. 2.7) connect the strips to the bias lines.

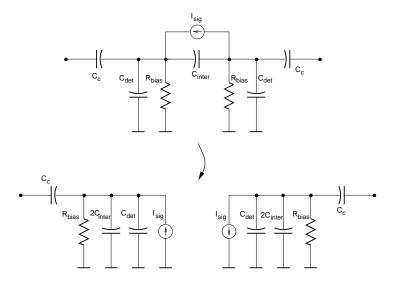

A (large signal) electrical model is given in fig. 2.7 (cf. appendix B); the charge/current generated by a particle is assumed to flow completely through a single n<sup>+</sup>- and p<sup>+</sup>-strip. Fig. 2.8 shows the small signal model without the noise sources (these will be added in chapt. 4). Since the current through n<sup>+</sup>- and p<sup>+</sup>-strip is equal, the combined system can be separated applying circuit regrouping techniques. It is interesting to notice that the capacitance  $C_{inter}$  between the signal-carrying n<sup>+</sup>- and p<sup>+</sup>-strip is doubled. This

Figure 2.6: AC-coupled double-sided strip-detector [Riech98]

Figure 2.7: Large signal model of a single diode on a double-sided strip-detector; in principle every  $n^+$ -strip forms a diode with every  $p^+$ -strip.

might worry the experienced reader, since, as we will see in chapt. 4, the serial noise of a charge amplifier is proportional to the input capacitance. However, because  $C_{inter}$  is only a very small fraction of the total capacitance of a strip (in particular, a strip has the same  $C_{inter}$  to all (n-1) strips of the opposite detector side), this effect is negligible. The impedance looking into the bias resistor  $R_{bias}$  in parallel to the strip capacitance  $\approx C_{det}$ should be much larger than the impedance looking into the couple capacitor  $C_c$  in series with the amplifier input impedance; if this condition is fulfilled, one can obtain nearly the full AC-current at the amplifier input. AC- vs. DC-coupled detectors are discussed from the noise point of view in chapter 4.

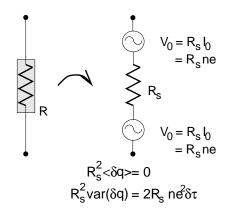

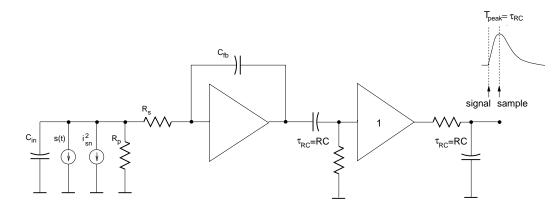

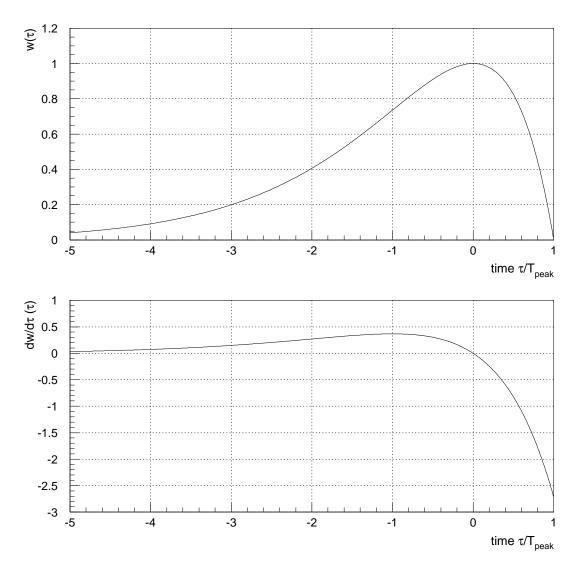

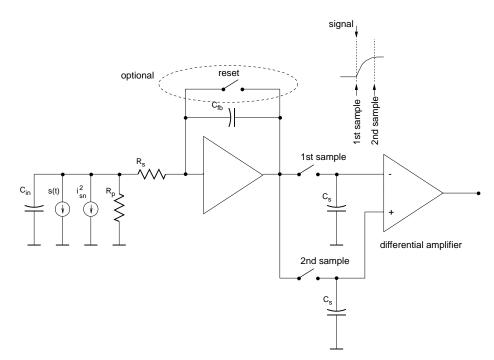

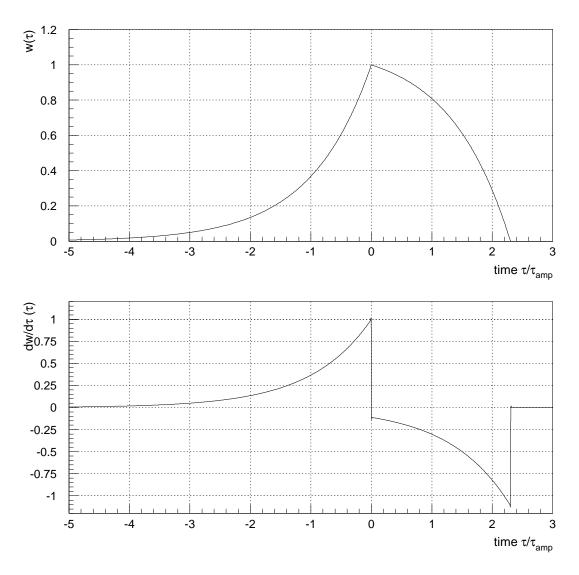

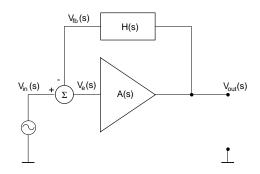

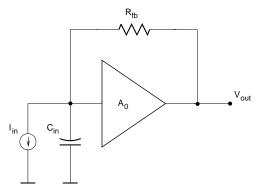

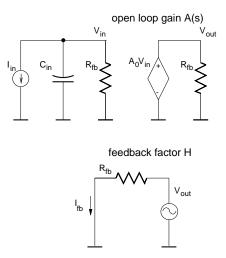

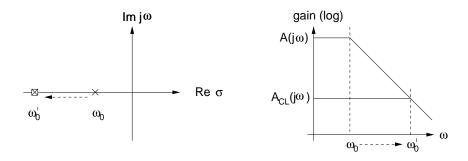

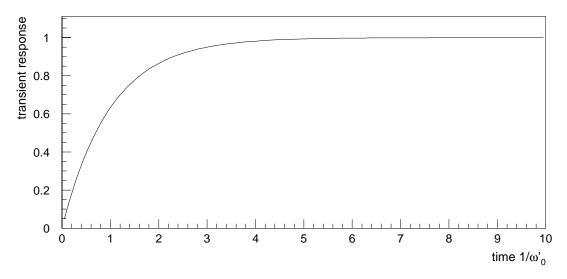

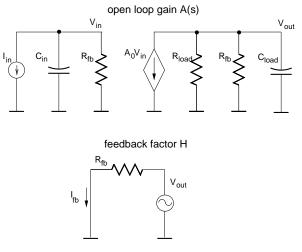

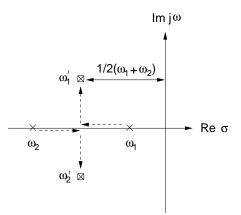

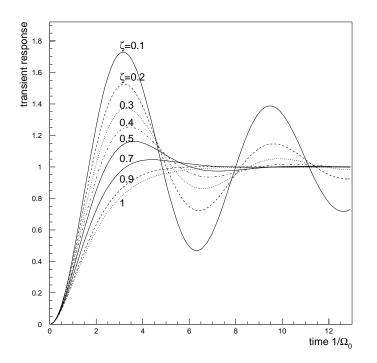

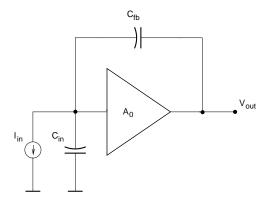

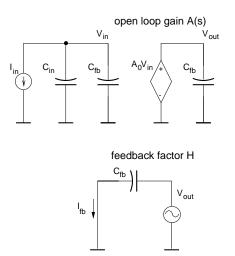

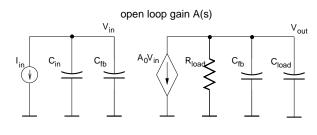

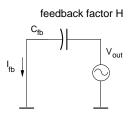

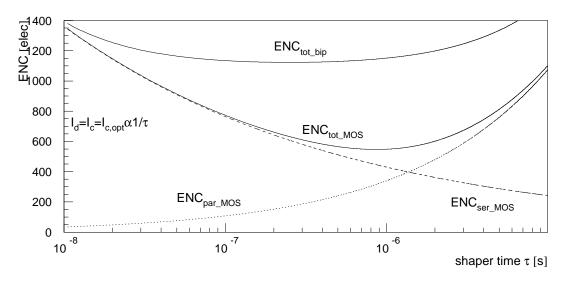

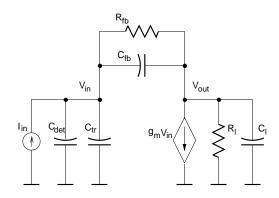

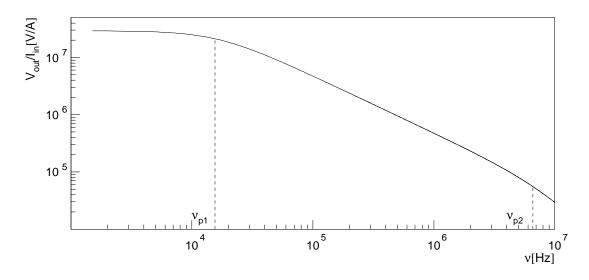

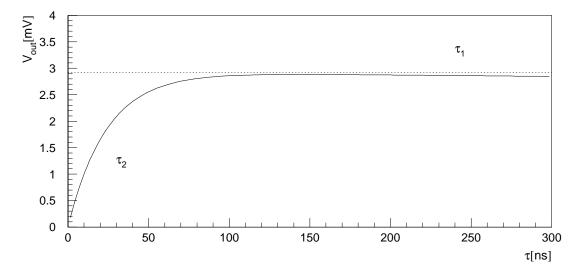

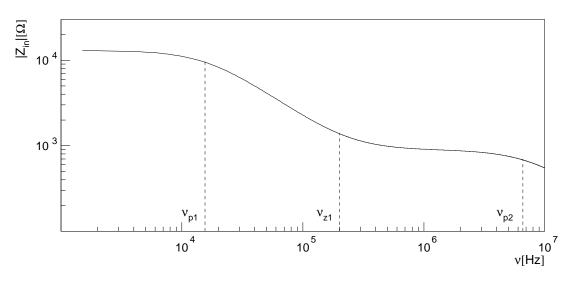

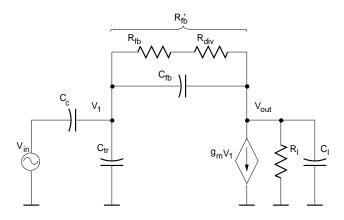

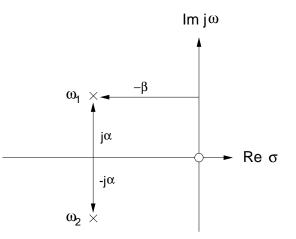

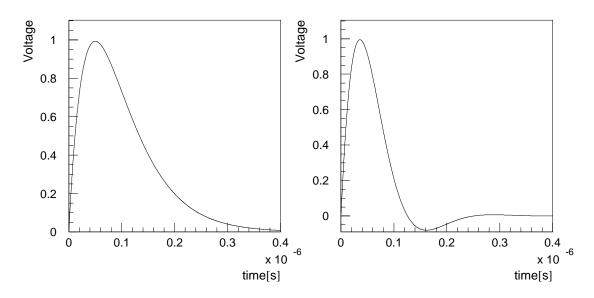

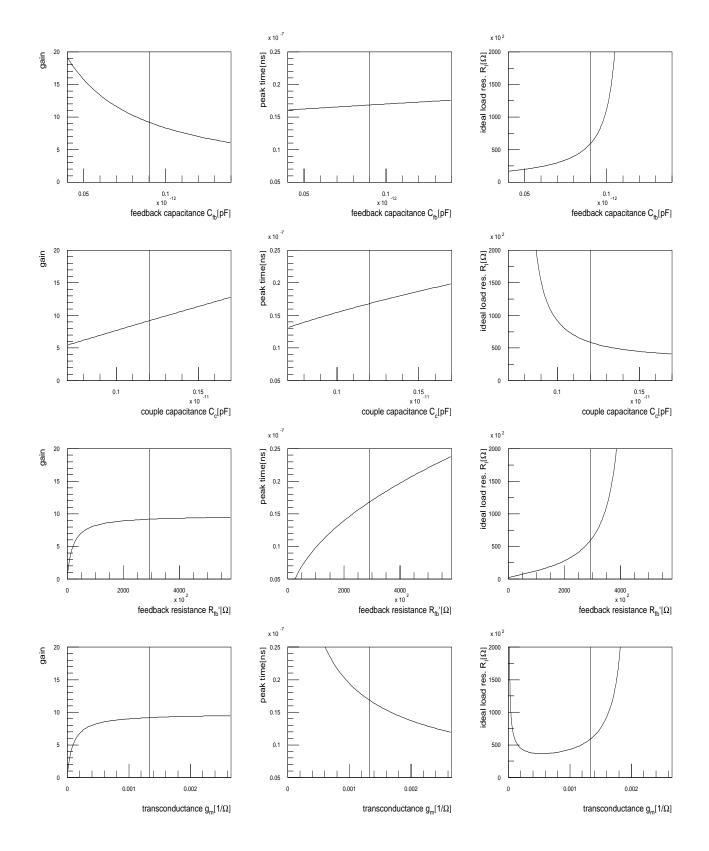

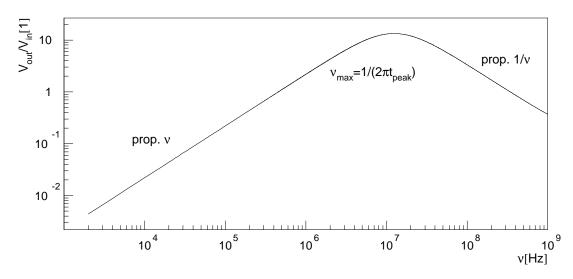

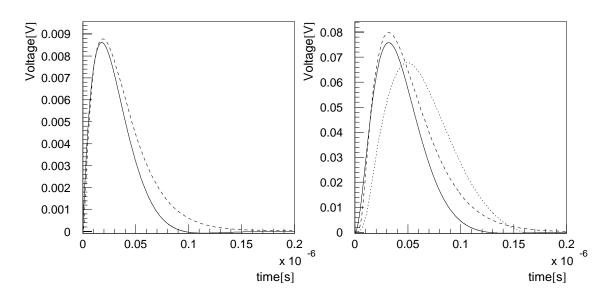

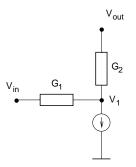

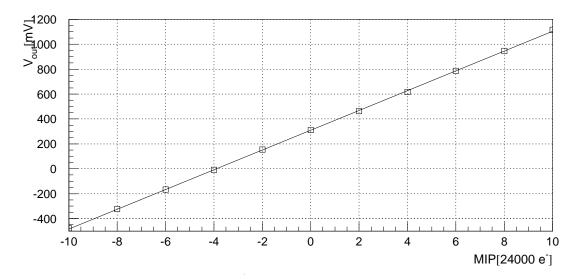

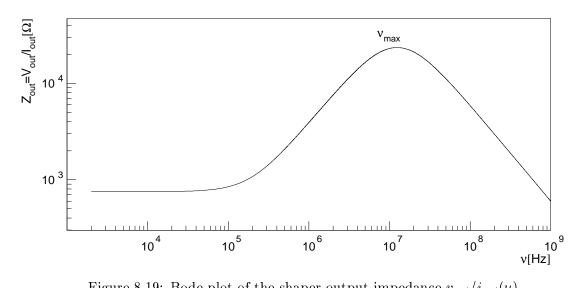

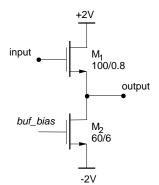

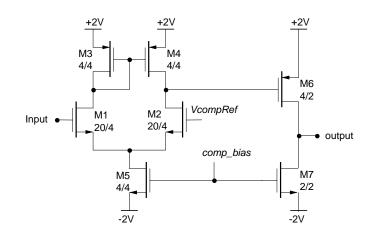

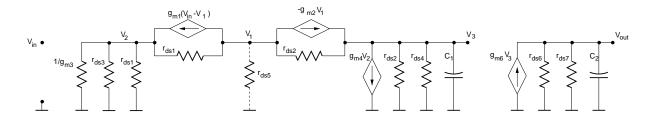

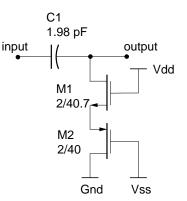

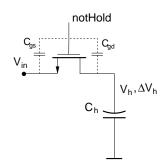

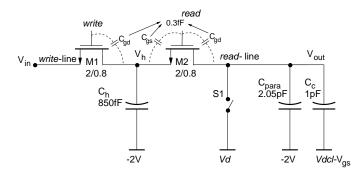

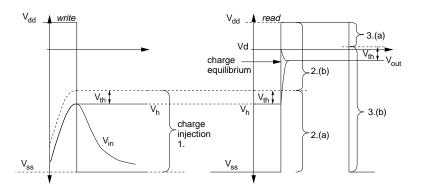

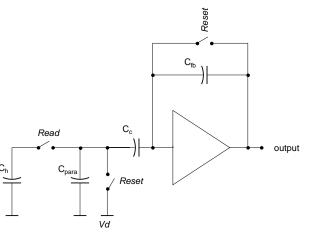

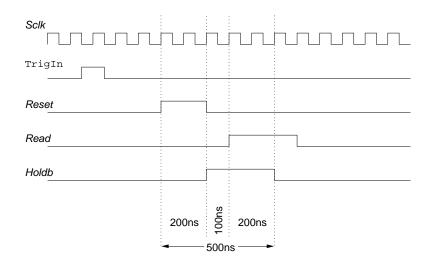

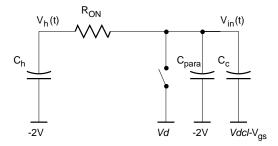

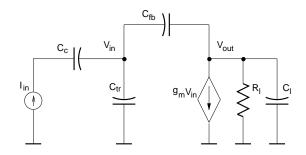

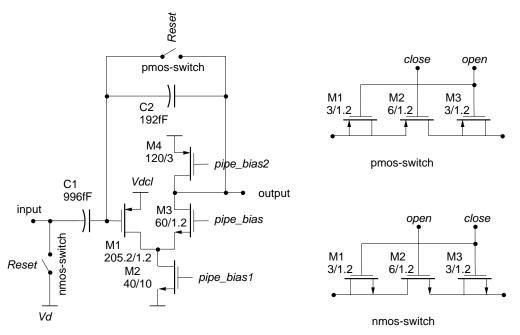

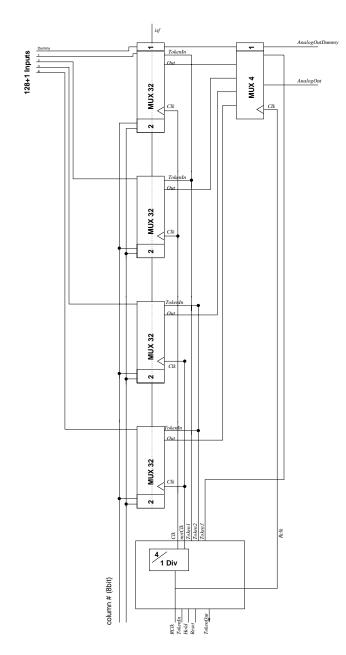

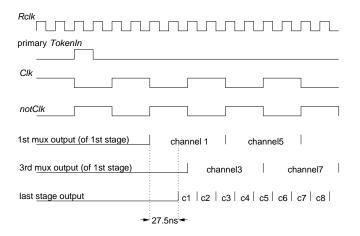

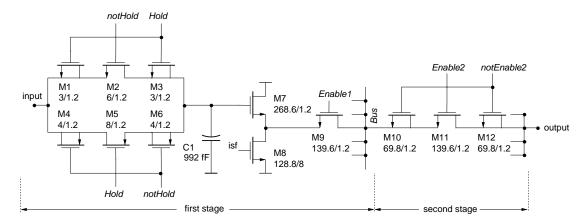

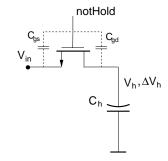

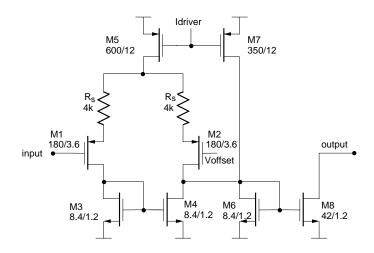

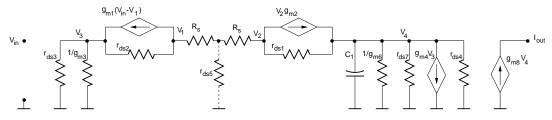

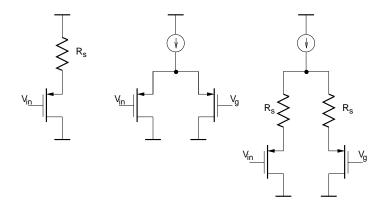

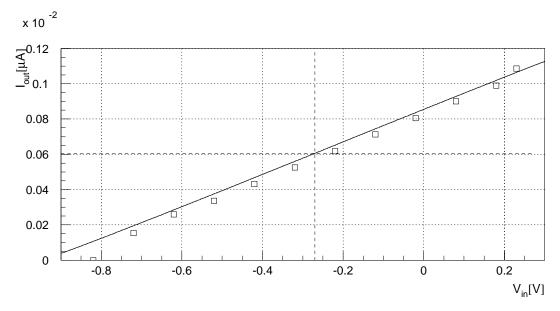

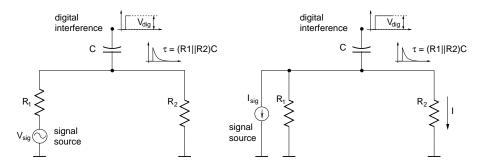

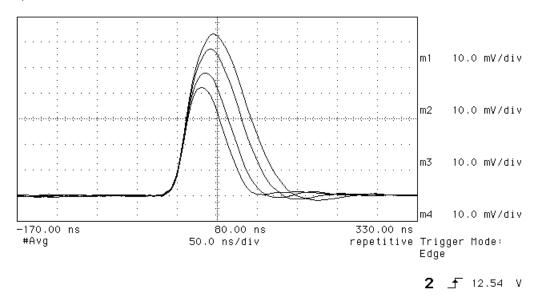

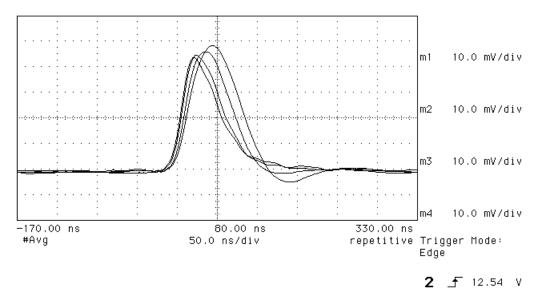

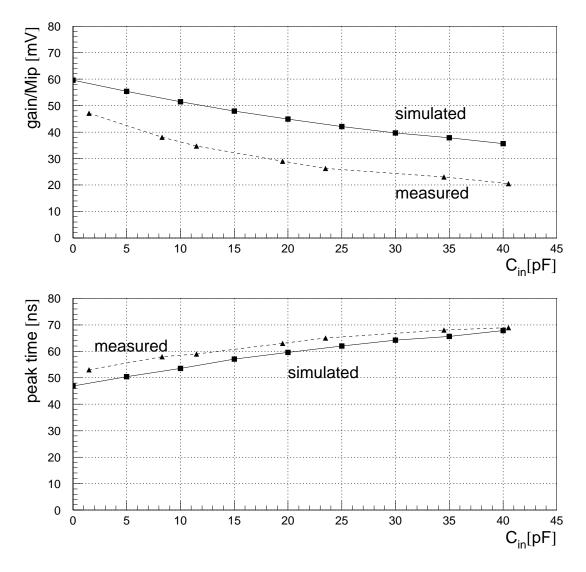

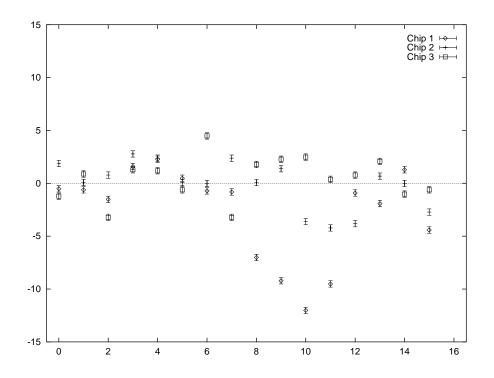

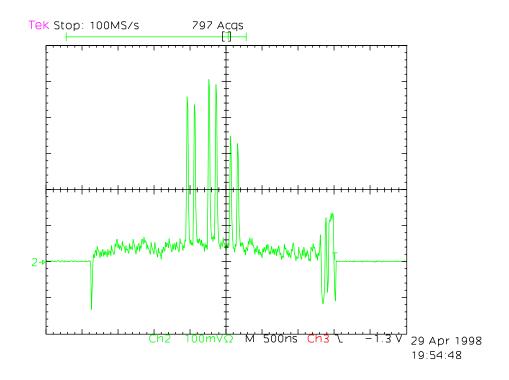

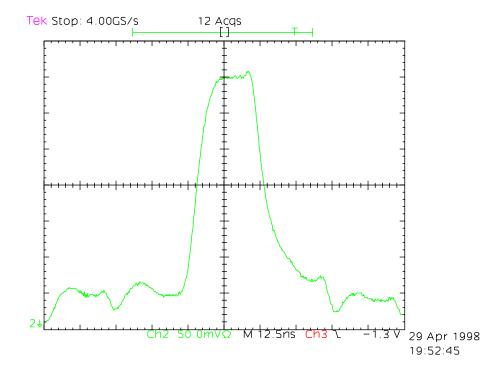

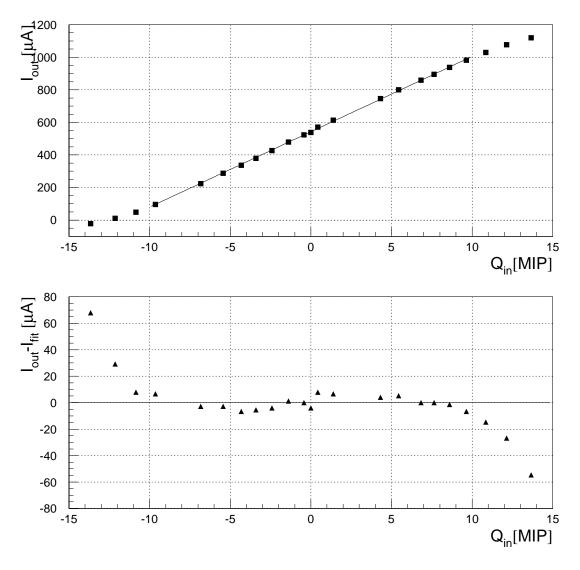

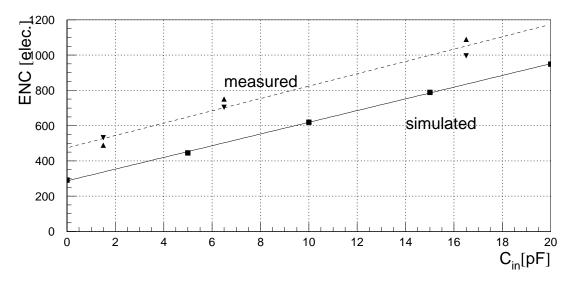

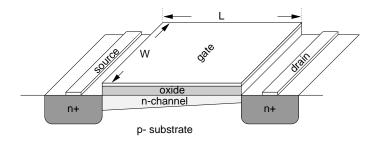

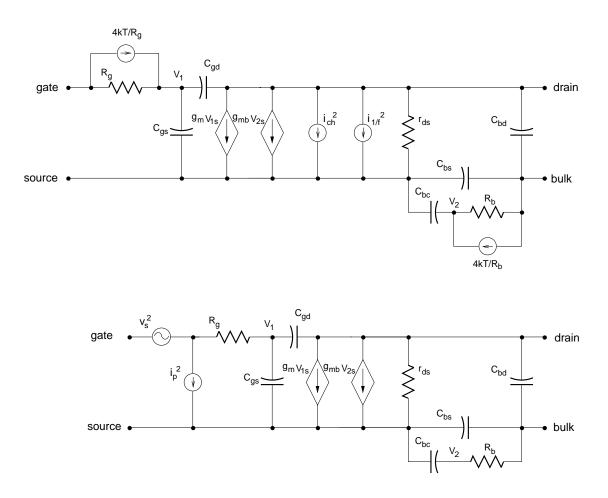

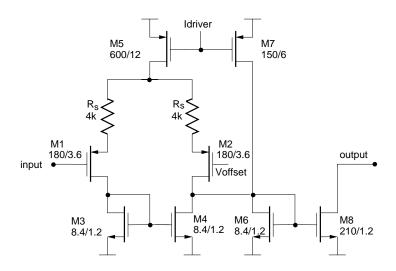

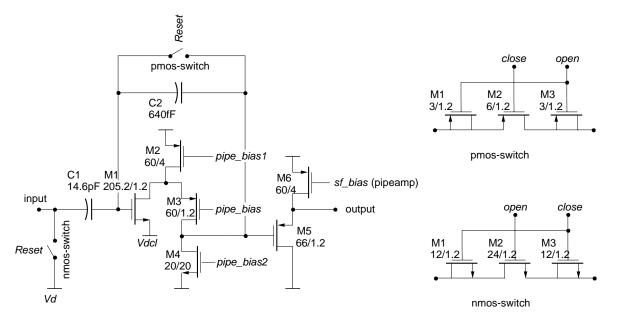

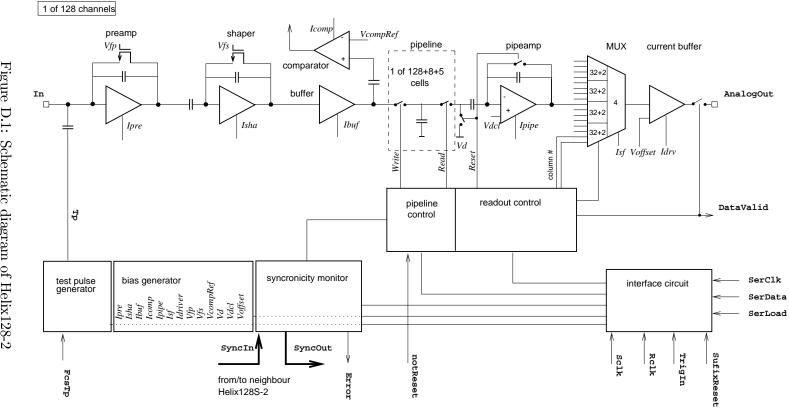

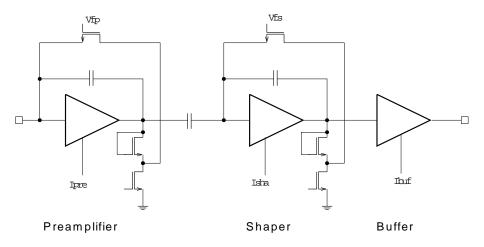

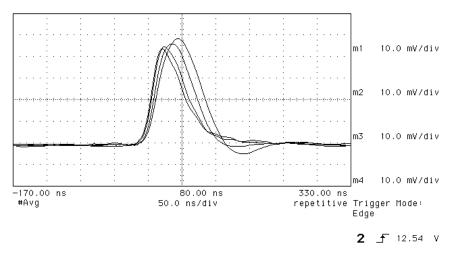

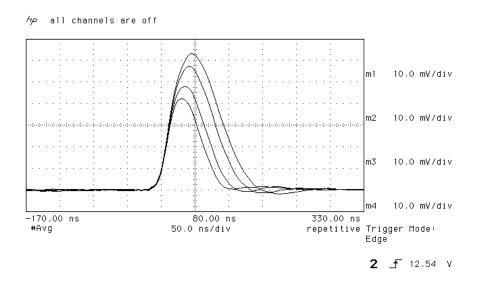

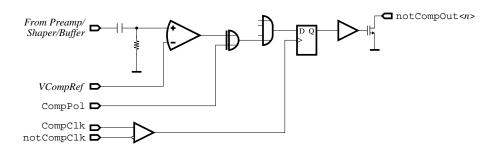

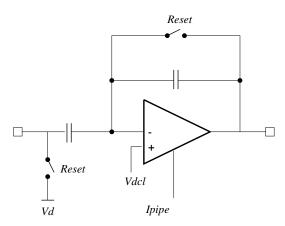

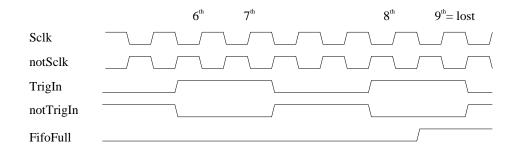

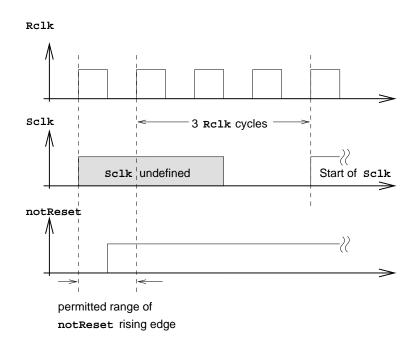

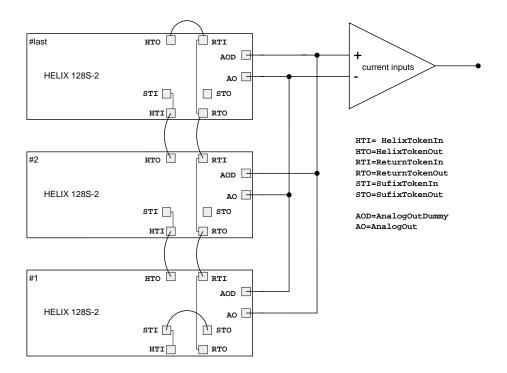

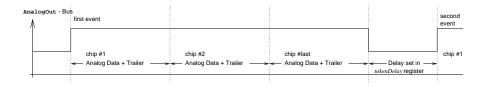

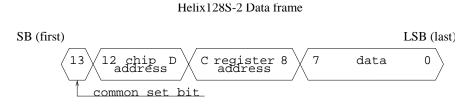

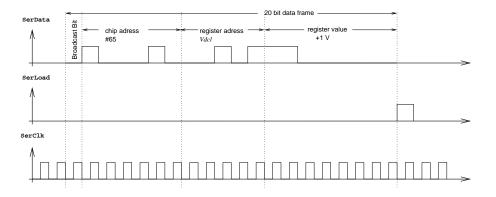

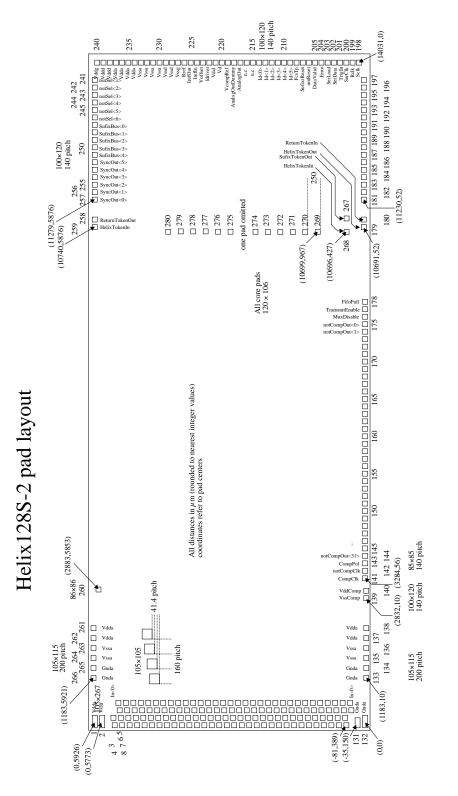

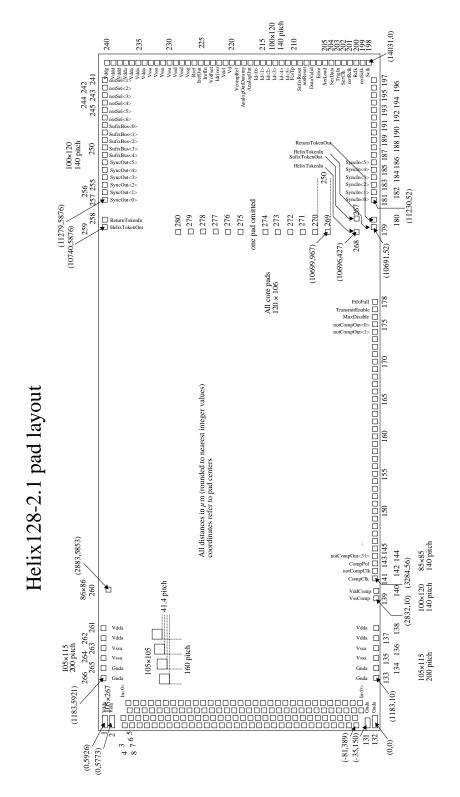

The silicon strip detectors used at HERA-*B* have a total active area of  $50 \times 70 \text{ mm}^2$  with 1280 strips of pitch 54.6  $\mu$ m on the n-side and 1024 strips of pitch 51.7  $\mu$ m on the p-side.