# **Department of Physics and Astronomy**

University of Heidelberg

**Master Thesis**

in Physics

submitted by

## Simon Rosenkranz

born in Jena, Germany

2024

# High-Speed Link Stability Improvements for Neuromorphic Multi-Chip Systems

This Master Thesis has been carried out by

### Simon Rosenkranz

at the

KIRCHHOFF-INSTITUTE FOR PHYSICS

Ruprecht-Karls-Universität Heidelberg

under the supervision of

Dr. rer. nat., Priv.-Doz. Johannes Schemmel

## High-Speed Link Stability Improvements for Neuromorphic Multi-Chip Systems

The BrainScaleS-2 neuromorphic hardware (BSS-2) enables the accelerated emulation of spiking neural networks on a mixed-signal substrate. Being the principal building block of this system, the High Input Count Analog Neural Network with HAGEN Extensions (HICANN-X) application-specific integrated circuit (ASIC) employs a total of 512 neuron circuits. In the framework of this thesis, a multi-chip system for the BSS-2 neuromorphic system has been designed to allow the realization of more complex networks. The presented platform offers the possibility to interconnect up to four HICANN-X ASICs in a star-topology by employing a field programmable gate array (FPGA) as the central connecting node. Successful communication tests have been performed with the commissioned setup in single-chip operation. Networks with sizes of up to 2048 neurons at an expected event transmission latency of 1 ms in biological time scale can be realized with further development efforts. This work further focuses on the stabilization of the HICANN-X high-speed communication interface. When scaling the network size in a multi-chip approach, an increasing amount of event data must be exchanged between the network constituents and the experiment control nodes. A testing routine has been developed to quantify the link stability in terms of a probability for link lost events. In-hardware probing enabled the optimization of the clock-to-data alignment algorithm, reducing the probability for follow-up link failures. Investigations of relevant ASIC system parameters show a dependency of the observed link losses on the core supply voltage. A simple test for calibration and commissioning was developed that allows hardware users to find a good operating point for their system.

## Verbesserung der Stabilität von Hochgeschwindigkeitslinks in Neuromorphen Multi-Chip Systemen

Das neuromorphe Hardware-System BrainScaleS-2 (BSS-2) ermöglicht das Emulieren von spikenden neuronalen Netzen auf beschleunigten analogen Schaltungen. Der mit 512 analogen Neuronschaltkreisen ausgestattete High Input Count Analog Neural Network with HAGEN Extensions (HICANN-X) application-specific integrated circuit (ASIC) ist der Grundbaustein des Systems. Für komplexere Netze wurde im Rahmen der vorliegenden Arbeit ein Multi-Chip System für BSS-2 entwickelt. Das System ermöglicht die Verbindung von bis zu vier HICANN-X ASICs in einer Sterntopologie durch ein zentrales field programmable gate array (FPGA). Kommunikationstests mit einem einzelnen Chip konnten erfolgreich durchgeführt werden. Erweiterungen des Systems für Netzwerke von bis zu 2048 Neuronen bei einer erwarteten Event-Latenz von 1 ms sind möglich. Weiterhin wurde die Stabilisierung der Hochgeschwindigkeitskommunikationsschnittstelle des HICANN-X behandelt. Wenn die Größe der neuronalen Netze durch die Einbindung mehrerer Chips skaliert wird, muss eine größer werdende Menge an Daten zwischen den Netzwerkpartnern und den Kontrollinstanzen des Experiments ausgetauscht werden. Für die Quantifizierung der Linkstabilität wurde eine Testroutine entwickelt. Die Optimierung der Angleichung von Takt und Daten mittels In-Hardware Probing führt zu einer Verringerung von Folgefehlern der Links. Untersuchungen der Systemparameter der ASICs zeigen eine Abhängigkeit zwischen der Core-Versorgungsspannung und den beobachteten Linkausfällen. Ein einfacher Test wurde entwickelt, um Benutzer\*innen der Hardware die Stabilisierung der Eventübertragung durch Kalibration zu ermöglichen.

# CONTENTS

| 1 | Intr | oductio | n                                         | 1               |

|---|------|---------|-------------------------------------------|-----------------|

| 2 | Mul  | ti-Chip | Platform                                  | 4               |

|   | 2.1  | Design  | Planning                                  | 5               |

|   |      | 2.1.1   | Theoretical Considerations                | 5               |

|   |      | 2.1.2   | Design Constraints                        | 8               |

|   |      | 2.1.3   | Network Size and Latency                  | 10              |

|   | 2.2  | Hardw   | are Commissioning                         | 11              |

|   |      | 2.2.1   | Setup Overview                            | 11              |

|   |      | 2.2.2   | Mezzanine Card                            | 12              |

|   |      | 2.2.3   | FPGA Implementation                       | 19              |

|   |      | 2.2.4   | Single-Chip Setup                         | 22              |

|   | 2.3  | Summa   | ary and Discussion                        | 23              |

| 3 | Hial | h-Snoor | I Link Stabilization                      | 25              |

| 3 | 3.1  | -       | uisites and Current State                 | <b>25</b><br>26 |

|   | 5.1  | 3.1.1   |                                           | 20<br>26        |

|   |      | 3.1.2   | Time to First and Second Failure          | 28              |

|   |      | 3.1.2   | Testing Routine                           | 28<br>29        |

|   |      | 3.1.3   |                                           | 29<br>30        |

|   | 3.2  |         | Example: Development Cube System          | 35              |

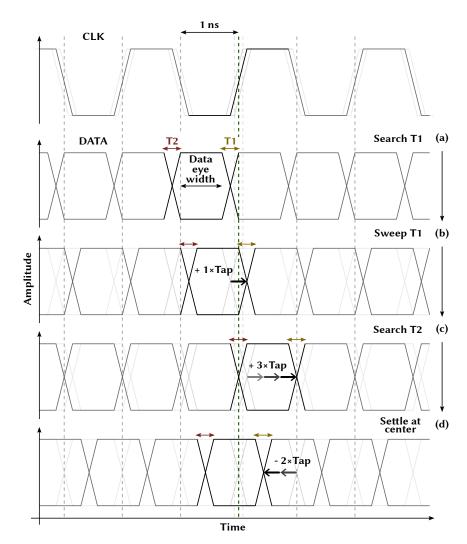

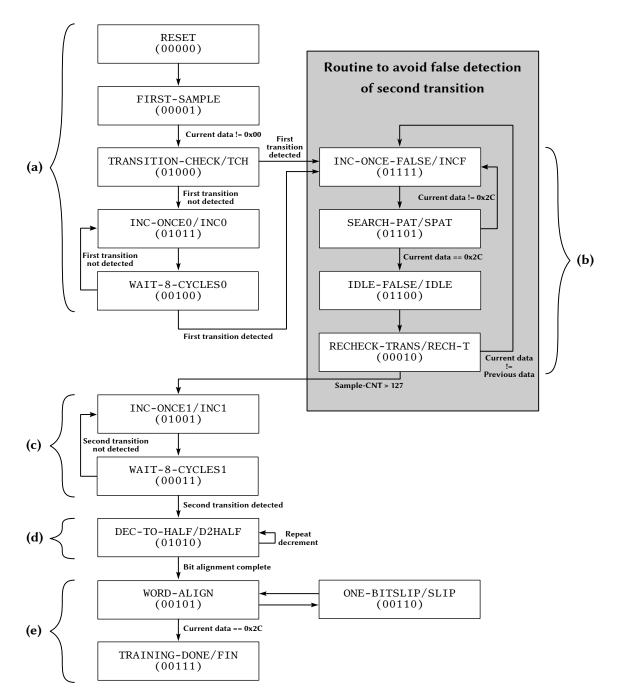

|   | 5.2  | 3.2.1   | raining                                   | 35<br>36        |

|   |      |         | Current Training Algorithm                |                 |

|   |      | 3.2.2   | Bit Align Machine                         | 38              |

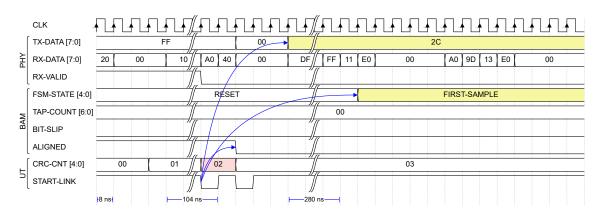

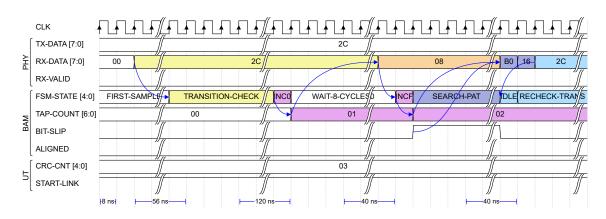

|   |      | 3.2.3   | Method: In-Hardware Probing               | 41              |

|   | 0.0  | 3.2.4   | Working Link Training Example             | 43              |

|   | 3.3  |         | ng Errors and Corrections                 | 49              |

|   |      | 3.3.1   | Failing Deterministic Jitter Check        | 50              |

|   |      | 3.3.2   | Premature Re-training                     | 54              |

|   |      | 3.3.3   | Missing Bad State Timeout                 | 56              |

|   |      | 3.3.4   | Zero Word Timeout                         | 58              |

|   |      | 3.3.5   | Performance Comparison                    | 59              |

|   | 3.4  |         | gation of Relevant ASIC System Parameters | 62              |

|   |      | 3.4.1   | Testing Routine                           | 64              |

|   |      | 3.4.2   | Results                                   | 66              |

|   | 3.5  | Summa   | ary and Discussion                        | 73              |

| 4 | Con  | clusion | and Outlook                               | 75              |

# **1** INTRODUCTION

In the field of computational neuroscience, emulation of biologically inspired neural network models can be carried out with *neuromorphic* hardware. In contrast to simulation-based approaches, the modeling of the network dynamics is not done through numerically solving the underlying differential equations. Neuromorphic systems rather aim to realize a physical representation of the system to be studied. In doing so, these highly specialized machines offer an improvement in efficiency, speed and scalability for neuroscientific modeling over traditional Von-Neumann architectures (Petrovici 2016).

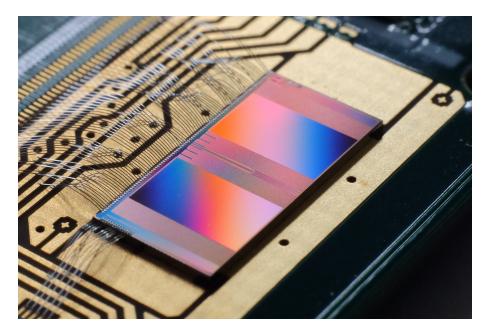

The *BrainScaleS-2 neuromorphic hardware* (BSS-2) architecture implements a mixed-signal, accelerated, physical emulation of bio-inspired *spiking neural networks* (SNNs) (Pehle et al. 2022). The principal building block of the BSS-2 system is the *High Input Count Analog Neural Network with HAGEN Extensions* (HICANN-X) *application-specific integrated circuit* (ASIC) (cf. Figure 1.1), a custom analog accelerator core with a tightly coupled digital plasticity processing unit and a digital event-routing network (Schemmel et al. 2022). The analog core of a single HICANN-X ASIC consists of 512 neuron circuits that mimic the action potential dynamics of real biological neurons. As the intrinsic time constants of the analog circuitry are several orders of magnitude smaller than the processes that happen on a biological time scale, the emulation of the network dynamics is accelerated by a factor of approximately 1000 compared to biology.

Figure 1.1: Photograph of a HICANN-X ASIC, the principal building block within the BSS-2 architecture, bonded to a chip carrier. Photo by Eric Müller, taken from https://wiki.ebrains.eu/bin/ view/Collabs/neuromorphic/BrainScaleS/ (accessed 29 Nov, 2023).

At the present time, experiments with the BSS-2 architecture are most commonly executed on so-

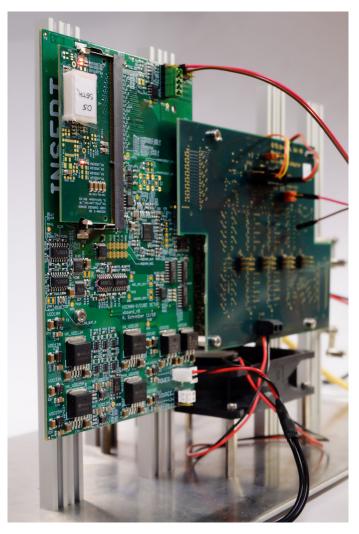

called *Cube*<sup>1</sup> systems (cf. Figure 1.2), a hardware setup consisting of several *printed circuit boards* (PCBs). The Cube implements full host-to-chip communication for a single HICANN-X ASIC by employing a *field programmable gate array* (FPGA) for real-time control during experiment execution. The FPGA buffers stimulus and output data, manages memory access for the plasticity processing unit and provides connection to and from the host system (Pehle et al. 2022). Injection of timed spike stimuli is done through a high-speed communication interface between the ASIC and the FPGA.

Figure 1.2: Photograph of a Cube system, taken from Pehle et al. 2022.

Although heavily utilized during prototyping and commissioning, the limitation of the Cube system to a single neuromorphic chip with 512 neurons limits the execution of complex experiments. Current design efforts for BSS-2 target the development of multi-chip systems which integrate multiple standalone HICANN-X ASICs into a larger system. The realizability of such systems depends on a robust inter-chip connection interface that manages to fulfill the high bandwidth demands implied by the event transmission rates of the accelerated network dynamics. While this communication framework exists for the BSS-2 architecture, it has in the past been observed to be afflicted with faulty link behavior. This limits the event throughput and can seriously impact the feasibility of the targeted multi-chip systems.

<sup>&</sup>lt;sup>1</sup>The denomination stems from the form factor of the enclosing rack, not fully depicted in Figure 1.2.

In the scope of this thesis, two aspects of developing a multi-chip platform have been covered: Firstly, a multi-chip setup has been designed that targets the interconnection of four HICANN-X ASICs through a centralized node FPGA. The setup has been commissioned up to single-chip operation with successful first communication tests having been carried out. However, the further development of the platform was hindered due to a hardware defect. Secondly, the high-speed communication interface between ASIC<sup>2</sup> and FPGA has been investigated with respect to the observed link lost failures. The stability of the high-speed links has been characterized by means of a time to failure and a link lost probability. By probing the FPGA implementation with in-hardware logic analyzing tools, faulty behavior of the delay training algorithm has been detected and corrected. An examination of ASIC system parameters yielded an additional improvement of the link stability.

The thesis at hand is structured as follows: Chapter 2 describes the planning and design of the multi-chip platform and outlines the commissioning process from a hardware design point of view. Chapter 3 describes the observed link stability issues and defines a stability criterion. A testing routine is outlined to gather statistics that are comparable across a variety of systems. Subsequently, the clock-to-data alignment procedure is described along an example recorded from in-hardware probing. Potential errors in the algorithm are pointed out along with giving corrections that address the faulty link training examples. The chapter concludes with an examination of additional sources of error that may be linked to ASIC system parameters. Lastly, Chapter 4 provides a summary of the work and an outlook on future developments.

<sup>&</sup>lt;sup>2</sup>Note that throughout this document, the HICANN-X will frequently just be referred to as *the ASIC*.

# **2 Multi-Chip Platform**

The computational power of neural networks stems to a large extent from their complexity in terms of constituent numbers. Naturally, one of the main challenges in brain-inspired computing is the realization of networks that are comprised of an increasing number of neurons to enable the execution of ever more complex experiments. In a physical modeling approach to building such systems – as is targeted with the BSS-2 architecture – the network size is especially tightly coupled to the size of the physical substrate. That is, in order to realize more complex network structures it is required that the neuromorphic architecture is *scaled*.

Within the BSS-2 architecture, the HICANN-X is designed as a structural building block with a clear purpose: It serves as a testing unit that allows to first be well understood and controllable by thorough verification and execution of standalone experiments before being integrated into larger systems. While the total number of 512 neurons in a single HICANN-X is sufficient for testing and smaller experiments, the network size can quickly become an issue. For instance, when the total neuron count is traded against equipping the network constituents with a sub-structure – as is for instance done in compartment neurons (Kaiser et al. 2022) – the neuron count of a single HICANN-X can be considered as a limiting factor.

Although the ultimate goal behind the BSS-2 architecture is to accomplish wafer-scale integration as achieved with the *BrainScaleS neuromorphic hardware* (BSS) architecture, the realization of such large-scale systems is a time and resource consuming process. The upgrade path of the system hence foresees the realization of medium size systems on the order of ten HICANN-X ASICs. This would allow researchers to run experiments that are more involved than those running on a single chip, but do not require the availability of full wafer-scale resources.

The HICANN-X is constructed in a way that in principle allows for the exchange of event data at high throughput with other individual chips. Therefore, the enlargement of the available analog substrate is also possible through the interconnection of single chips. The buildup of such *multi-chip* networks is one of the most important topics within the current development efforts of the BSS-2 platform.

This chapter introduces a design for a multi-chip setup that has been developed in the framework of this thesis. The presented platform offers the possibility to interconnect up to four HICANN-X ASICs. Section 2.1 describes the considerations made during the planning phase of the system – highlighting the design choices made and their potential advantages and disadvantages – and the constraints that are imposed on the system by interfacing hardware elements. Section 2.2 outlines the concrete hardware development steps that have been taken in commissioning the system up to first communication tests in single-chip operation. The chapter concludes with a summary and discussion of the current development state of the platform in Section 2.3.

## 2.1 Design Planning

The upscaling procedure presented in this thesis is performed in a modular fashion. The idea is to use as many of the already existing hardware components as possible that the BSS and BSS-2 architectures offer to minimize the design overhead. This section provides a brief overview over the planning efforts to develop such a multi-chip platform for the BSS-2 architecture. First, some theoretical considerations will be presented that outline the further design goals for the platform. Subsequently, the design constraints posed by the existing hardware stack that is to be incorporated in the system will be presented. Lastly, an estimation of the expected network size and latency for the targeted system will be given.

## 2.1.1 Theoretical Considerations

In order to build up a network of individual components, one needs to first address the underlying network topology that is targeted for the system. This choice greatly impacts the constraints that the design needs to adhere to. Hence, an overview over the considered upscaling approaches will be presented in the following.

### Topology

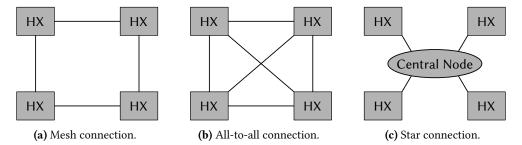

There are plenty of topologies available to assemble a set of single components in a fully connected network, and all of them come with specific advantages and disadvantages. Figure 2.1 shows a couple of examples for possible interconnection variants imaginable to set up a large-scale network of HICANN-X ASICs.

Figure 2.1: Set of exemplary interconnection topologies for multi-chip systems.

In the following, a network of four ASICs will be considered in which each chip may send and receive events to and from all three other partners.

A straightforward way to set up a connection scheme for the network constituents could be to arrange them on a two-dimensional grid with horizontal and vertical nearest-neighbor connections like in Figure 2.1a. This mesh-type connection scheme would require only four edges in total to allow for each node to talk to every other network constituent. However, this approach inherits a certain complexity in how nodes that are not directly connected via an edge are able to send data to each other. Some kind of event routing logic is required at every node. This ensures that data, which is received from a neighboring node, but intended for the second directly connected

partner, is properly transmitted through the mesh. The issue becomes more complex with an increasing number of network constituents. Moreover, the routing logic must be attachable to every single node, which requires a significant amount of hardware resources to be added to the existing architecture. An advantage of this approach is that the network can in principle scale well in two dimensions, as the transmission lines between network partners can be kept short<sup>1</sup>.

An alternative option would be to equip every node with direct connections to every other network partner, such as shown in the all-to-all arrangement in Figure 2.1b. This topology bypasses the need for a more involved routing scheme as every node has direct access to all partners, but it quickly becomes infeasible to add more components to the network. The number of required edges for a total of N nodes grows as  $\frac{N}{2}(N-1)$  and hence quadratic in network size. So for smaller networks, this could be an option, but as the goal is to interconnect several hundreds of chips eventually, this connection topology does not serve as a suitable option.

Lastly, the star configuration displayed in Figure 2.1c has been considered. In this topology, all nodes share access to a central connecting node. The central component handles the routing of the events between all network constituents. Thereby, the topology is somewhat similar to the mesh-type configuration in that it also requires the existence of a dedicated routing scheme. On the other hand, the overhead for additional hardware resources is greatly reduced, given that the central node is powerful enough to handle the large amount of data that is piped through it. There very likely are limitations to the number of possible connections to the central node as it cannot provide an infinite amount of *input and output* (IO) resources. Yet, medium-size networks of tenths of chips could be imaginable. The main disadvantage of this approach is that the network is greatly dependent on the performance of the central node, but the simplicity of the hardware requirements somewhat alleviates this issue.

Overall, the star configuration promises to strike a good balance between the realizable network sizes and the required engineering efforts. It is therefore the topology of choice for a medium-size multi-chip platform on the order of ten interconnected ASICs.

#### **Central Node**

With the star topology targeted as the desired configuration for the multi-chip system, the question arises what could serve as the central node in the setup. In the approach presented in this thesis, the interconnection is realized through an FPGA.

#### FIELD-PROGRAMMABLE GATE ARRAY

A *field programmable gate array* (FPGA) is an *integrated circuit* (IC) that provides a set of configurable logic elements and routing resources which together can be programmed to realize a user-defined circuit. That is, in contrast to an ASIC, the circuit that is realized with an FPGA does not need to be specified upfront, before the IC is manufactured. It can be defined at a later point in time while, in many cases, using the same fabric or device is possible. Typically, the logic elements within the FPGA fabric are arranged in arrays and can vary in their functional complexity. The simplest elements provide basic combinatorial logic functions while more complex ones realize specialized functions. Among others, these can be dedicated blocks for handling IO to the fabric,

<sup>&</sup>lt;sup>1</sup>For instance, the wafer-scale integration of ASICs in the BSS architecture used this kind of topology.

memory elements, advanced functions such as multipliers or even complete processors. In many cases, the dedicated IO cells also support various signaling standards. FPGAs therefore provide lots of flexibility during the development cycle of digital designs and can be employed in a vast range of applications.

Readily available for the setup targeted in this thesis has been a Xilinx Virtex UltraScale+ VU9P FPGA. It provides access to roughly  $2.6 \times 10^6$  system logic cells<sup>2</sup> (AMD 2024), which is roughly equivalent to 16 times the resources of a Kintex-7 FPGA that is used as an experiment control node in the BSS-2 architecture. The FPGA is embedded in an *AMD Virtex UltraScale+ FPGA VCU118 Evaluation Kit* (VCU118) (AMD 2023), which is displayed in Figure 2.2. The VCU118 is a  $24 \times 18 \text{ cm}^2$  PCB that provides many IO options to the user for prototyping a design with the FPGA in early development phases. In the case of the multi-chip platform, most interesting are the 192 user-configurable IO pins and 24 multi-gigabit transceivers that are connected to the FPGA and accessible via two high-pin-count *FPGA Mezzanine Card* (FMC) connectors at the upper edge of the board.

**Figure 2.2:** Photograph of the VCU118, taken from AMD 2023. The FPGA is assembled at the center of the PCB (*grey*). At the upper edge of the board, two high pin count FMC and *FPGA Mezzanine Card Plus* (FMC+) connectors (*black*) are located that provide a large portion of the IO to the FPGA. The FMC+ connector corresponds to the left of the two connector arrays and is slightly larger than the FMC connector to its right due to a higher pin count.

With the vast amount of logic resources available, the FPGA on the VCU118 should in theory be able to handle the experiment control logic needed for multiple HICANN-X ASICs while leaving enough headroom for the extension with a dedicated routing protocol to link between the single control entities.

<sup>&</sup>lt;sup>2</sup>Marketing term employed by Xilinx to give a metric for the complexity of a design that can be fit onto a device.

## 2.1.2 Design Constraints

As briefly mentioned before, the VCU118 provides access to most of the FPGA fabric through two *high pin count* (HPC) FMC and FMC+ connectors, respectively. These connectors adhere to the *ANSI/VITA 57.1-2019 FPGA Mezzanine Card (FMC) Standard* (VITA 2019) and the *ANSI/VITA 57.4-2018 FPGA Mezzanine Card Plus (FMC+) Standard* (VITA 2018). They are large arrays of 400 and 560 pins, respectively, with standardized locations of, for instance, user configurable IO, power distribution, clocking or high-speed transceiver resources. The idea behind this standardization is to bundle the IO of the FPGA in a single component so that when utilizing a board such as the VCU118 the user only has to adhere to a single standard. The specific IO requirements of the application are outsourced to a *mezzanine* PCB that can be attached to the FMC connectors on the *carrier* board hosting the FPGA. The mezzanine board needs to be specified and designed by the user. When the IO requirements change at a later point in development, only the mezzanine board has to be re-designed and the carrier board can be re-used.

So, in order to interface with the VCU118, a custom mezzanine PCB is needed. A prototype for such a mezzanine card has been developed in the scope of this thesis. An overview of the board is provided in Section 2.2.2.

With the interface to the central node being defined through the mezzanine card, the hardware interface towards the HICANN-X needs to be defined as well. In BSS-2 systems, the HICANN-X ASICs are bonded on dedicated *chip carrier* boards – an example is displayed in Figure 2.3 – that provide a low-cost solution to change and upgrade the neuromorphic substrate without needing to build up entirely new setups.

Figure 2.3: Photograph of the HICANN-X chip carrier board.

The chip carrier interfaces to other components through a board-edge connector, which provides access to power, high-speed links for communication with the experiment control node and configuration via JTAG. In the currently employed single-chip Cube systems, the chip carriers interface to the *xBoard*, which generates the supply voltages of the HICANN-X and provides the reference voltage and current for the analog circuitry, among other things. However, for the multi-chip setup, the xBoard is planned to be replaced with a new *ASIC Adapter Board* (ASIC-AB) developed for the *just a Bunch Of ASICs* (jBOA) system that aims to replace the Cube systems in the long run<sup>3</sup>.

<sup>&</sup>lt;sup>3</sup>Personal communication with Joscha Ilmberger.

An example of the latest version of the ASIC-AB is displayed in Figure 2.4. The feature set of the ASIC-AB includes

- low-dropout regulators (LDOs) for regulation of the supply voltages of the ASIC,

- generation of the reference current for the ASIC,

- buffering of a differential reference clock that needs to be provided single-ended to the *phase-locked loop* (PLL) of the ASIC,

- level shifters for the reset, JTAG and *general purpose input/output* (GPIO) pins of the ASIC and

- forwarding of the high-speed communication interface between FPGA and ASIC.

The connectivity from the experiment control node side to the ASIC-AB is again realized through a board-edge solution. The full interface towards the ASIC-AB from this side includes

- 1. eight high-speed *low voltage differential signaling* (LVDS) data signals from FPGA to ASIC with one LVDS clock signal,

- 2. eight high-speed LVDS data signals from ASIC to FPGA with one LVDS clock signal,

- 3. single-ended slow control via Inter-Integrated Circuit bus (I2C) and JTAG,

- 4. one asynchronous reset signal,

- 5. one LVDS reference clock signal for the PLL,

- 6. 1.2 V ASIC core supply voltage,

- 7. 2.5 V ASIC IO supply voltage,

- 8. 3.3 V ASIC auxiliary supply and standby voltage,

- 9. 12 V ASIC auxiliary supply voltage,

- 10. 1.8 V FPGA IO voltage used in the level shifters of the slow control signals and

- 11. one power enable pin for the ASIC supply voltages.

When considering multiple pairs of chip carriers and ASIC-ABs, the signals listed under bullet point 1 to 5 in the previous list need to be supplied to each ASIC-AB individually. In total, this sums up to 45 individual signals to be routed towards the ASIC-AB per HICANN-X to be integrated in the network. The two FMC+ and FMC connectors on the VCU118 offer a total of 192 user configurable pins, so in theory a maximum of four ASICs with 180 signal connections could be connected to the central node with full high-speed interface bandwidth.

Figure 2.4: Photograph of the ASIC-AB.

Additional connections could be realized by exploiting the 24 transceiver connections and interposing a Kintex-7 FPGA node board for interfacing to each HICANN-X before establishing the connection towards the central node FPGA on the VCU118. This option has been considered in the early planning phase of the multi-chip platform, but ultimately rendered not possible to be realized within the time limit of this thesis.

## 2.1.3 Network Size and Latency

In Section 2.1.2 it was discussed that a total of four HICANN-X ASICs at full 8 Gbit/s event data throughput towards the experiment control node can in theory be aggregated on the VCU118 FPGA when utilizing the user configurable IO pins. With 512 neurons per chip, a maximum of 2048 neurons could be aggregated in the resulting multi-chip network, offering a rather moderate upgrade in terms of the total neuron count compared to the currently employed single-chip Cube setups. However, since the footprint of the setup is mainly dominated by the dimensions of the VCU118, the multi-chip platform can offer a significant upgrade in neuron density while exhibiting a comparable or even smaller form factor than the Cube system.

The intrinsic acceleration of the neuron activity within the analog SNNs in the BSS-2 architecture additionally poses critical demands on the latency that is introduced during event transmission. In order to route an event from a neuron located on one HICANN-X to a network partner located on a different ASIC, the transmission delays from the ASIC to the FPGA and vice versa need to be taken into account. An estimation of the from-chip and to-chip delays is provided in Karasenko 2020 and sums up to a worst-case latency of approximately 1  $\mu$ s for a full ASIC-to-FPGA and FPGA-to-ASIC loop. Additionally, the routing of the event within the central node FPGA needs to be considered. The delay introduced by the routing logic is expected to be on the order of a couple of system clock cycles of the FPGA. This would, for instance, correspond to some clock cycles at a frequency of 125 MHz<sup>4</sup>. Therefore, the delay of the routing logic should be negligible compared to the total from- and to-chip delay of 1  $\mu$ s, which is then expected to dominate the total latency. The latency corresponds to roughly 1 ms in biological time per event transmission, when taking the implicit 1000-fold acceleration factor of the BSS-2 hardware into account. Compared

<sup>&</sup>lt;sup>4</sup>Personal communication with Joscha Ilmberger.

to typical neuron parameters, this can be considered as significant. The typical neuron response latency is of the order of 0 ms to 8 ms (Müller 2017), so the latency in the multi-chip system is expected to be of the same order of magnitude. However, it should be located on the lower end of the latency range and may potentially be compensated for during training, if the latency is deterministic and not heavily affected by jitter<sup>5</sup>.

## 2.2 Hardware Commissioning

With the theoretical design constraints for the multi-chip platform outlined in Section 2.1.1, the following section describes the steps that have been taken to realize a working single-chip system ready to be extended for the incorporation of additional ASICs. However, a defect of the VCU118 prohibited the further development of the platform for full multi-chip support. This section provides a schematic overview over the targeted multi-chip system before detailing the design choices for the mezzanine card that completes the required hardware stack. Further, the necessary adjustments of the existing FPGA design for single-chip operation to comply with the VCU118 will be described. Lastly, the results of first single-chip hardware tests before the defect of the VCU118 will be described and discussed.

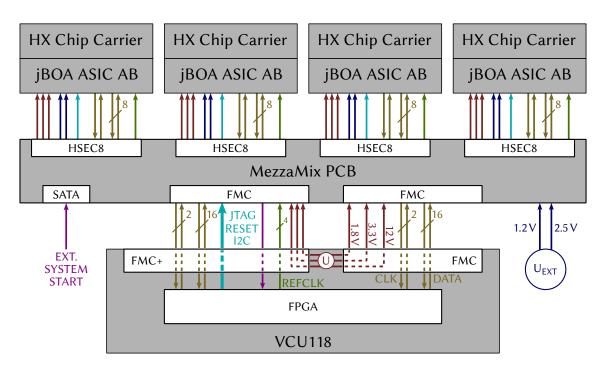

#### 2.2.1 Setup Overview

A schematic overview of the multi-chip platform developed in this thesis is provided in Figure 2.5. The mezzanine card prototype developed for this configuration – which will be described in more detail in Section 2.2.2 – is referred to as *Mezzanine card for Mixed multi-chip setup evaluation* (MezzaMix), as it provides the IO necessary to evaluate two distinct upscaling paths: On the one hand, it features the connectors to directly attach four ASIC-ABs, which interface with the user configurable IO pins of the FMC and FMC+ connectors, and on the other hand, it features four USB-C receptacles<sup>6</sup>, each of which connect to one multi-gigabit transceiver on the VCU118 FPGA. As briefly touched upon in Section 2.1.1, the upscaling path utilizing the transceivers of the VCU118 has not been possible to be evaluated in the limited time of this work, but nevertheless the integration of the required interface on the MezzaMix is mentioned here for completeness.

For the direct attachment of ASIC-AB and chip carrier pairs, the MezzaMix PCB must be able to perform the following tasks:

- Distribute all required supply voltages to the ASIC-AB and the HICANN-X.

- Forward the high-speed communication interface between FPGA and ASIC.

- Connect slow control and auxiliary signals from the FPGA to the HICANN-X.

The schematic shown in Figure 2.5 summarizes how all required signals are distributed between the central node FPGA and the ASICs through the MezzaMix PCB. The major portion is routed through the FMC+ connector, as it provides a larger amount of accessible pins, while the FMC

<sup>&</sup>lt;sup>5</sup>Personal communication with Joscha Ilmberger.

<sup>&</sup>lt;sup>6</sup>Not depicted in Figure 2.5

**Figure 2.5:** Schematic overview of the multi-chip platform with the MezzaMix PCB interfacing between the VCU118 serving as central node and four HICANN-X chip carrier and jBOA ASIC-AB pairs. Component sizes are not to scale. *Color coding: Yellow* arrows correspond to the full-duplex high-speed links with one differential clock and eight differential data signals per ASIC and direction. Sixteen links and two clock pairs are routed per FMC and FMC+ connector, respectively, aggregating all links of single chips at separate IO banks of the FPGA. *Turquoise*: Bundled slow control signals providing JTAG and I2C connectivity as well as an asynchronous reset for each ASIC. *Green*: One differential 50 MHz reference clock signal per ASIC is forwarded to the PLL. *Red*: 3.3 V, 12 V and 1.8 V power is shared across all ASIC-ABs and supplied by the VCU118. *Blue*: 1.2 V and 2.5 V power are supplied externally. *Purple*: External reference clock and system start differential signals are forwarded to the VCU118 to optionally synchronize the experiment start.

connector is mainly used to distribute the high-speed connectivity for two ASICs (*yellow*) and facilitate power distribution (*red*). The high-speed links are connected in such a way that all signals corresponding to single ASICs are bundled at distinct IO banks within the FPGA. This is done to facilitate the clock distribution and ultimately the timing closure for the system. Slow control (*turquoise*), differential reference clock (*green*) and external synchronization signals (*magenta*) are routed through the FMC+ connector. The ASIC 1.2 V core and 2.5 V IO supply voltages are supplied externally (*blue*).

## 2.2.2 Mezzanine Card

The full schematic of the MezzaMix PCB is a twenty-three page document in hierarchical structure, consisting of pages with size up to A2. It is therefore not included in this document, but it can be accessed through the *Electronic Vision(s)* group internal *git* server in a dedicated pcb-mezzamix repository<sup>7</sup>. In the context of this thesis, the layout of the PCB will be discussed by referencing

<sup>&</sup>lt;sup>7</sup>URL: https://gerrit.bioai.eu:9443/c/pcb-mezzamix/+/22076;

Commit hash at production state: 78c8b668a900c046c9444b8437ac8c4e98f8e48c.

the manufactured and assembled board shown in Figure 2.6 and 2.7. Besides the components shown explicitly on the top and bottom surface of the PCB, the routing of signals on the inner layers is highlighted.

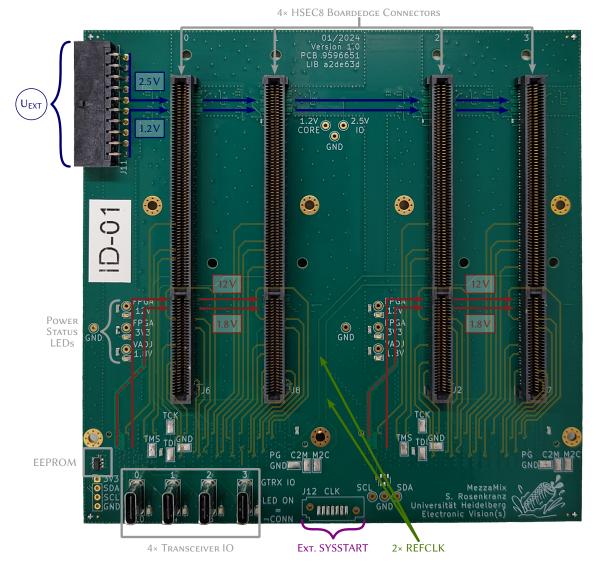

**Figure 2.6:** Photograph of the MezzaMix PCB top side. Connectors and other components are highlighted explicitly. *Color coding: Yellow:* High-speed differential clock and data signals routed on a dedicated inner layer. Additional traces are routed on the top and the bottom layer of the PCB and are not highlighted explicitly. *Red:* Routing of power signals supplied by the VCU118 on the top and a dedicated inner layer. *Blue:* Routing of externally supplied ASIC IO and core voltages on a dedicated inner layer. Each voltage rail is fed into the board through an equally split number of pins on a  $2 \times 10$  pin through hole connector. *Green:* Highlighted routing of two traces for 50 MHz reference clock signals to the two rightmost ASIC-AB slots. The signals to the connectors on the left side are not highlighted for visual clarity. *Purple:* Landing pad of the connector<sup>8</sup> for optional system synchronization signals.

Figure 2.6 shows the top side of the MezzaMix card. It is an eight layer  $13.9 \times 13.75 \text{ cm}^2$  PCB. The central feature are four *Samtec HSEC8-1100-01* connectors (Samtec 2024b) that allow for boardedge

<sup>&</sup>lt;sup>8</sup>Not assembled.

attachment of the ASIC-ABs. Their placement has been chosen such that the fanout of the critical high-speed LVDS signals (*yellow*) from the FMC and FMC+ connectors results in short trace lengths, while guaranteeing the landing of all signals from a single ASIC on a dedicated IO bank of the FPGA. The 1.2 V core and the 2.5 V IO supply voltages for the ASICs are provided through a *Wuerth WR-MPC3 66202021022*  $2 \times 10$  pin through hole connector (Wuerth 2016) (*blue*). The 12 V auxiliary and 1.8 V FPGA IO voltages are routed on dedicated inner layers from the locations of the FMC and FMC+ connectors on the bottom, similar to the 3.3 V auxiliary supply voltage shown in Figure 2.7 (*red*). For these power rails, status *light-emitting diodes* (LEDs) are provided.

**Figure 2.7:** Photograph of the MezzaMix PCB bottom side. Connectors and other components are highlighted explicitly. *Color coding: Turquoise*: Single-ended slow control signals and asynchronous reset routed on a dedicated inner layer. *Red*: Routing of power signals supplied by the VCU118 on a dedicated inner layer.

The 50 MHz differential reference clock signals for the PLL are routed on the top side of the PCB (*green*). Since these signals require to be connected to some of the limited clock capable outputs

of the FPGA, their routing has been prioritized and the placement of other signals adapted to the resulting spatial constraints. A *Molex SATA 0678005005*<sup>9</sup> connector can optionally be assembled to provide system synchronization signals to the FPGA (*purple*). An I2C addressable 2 kbit *Microchip 24AA025UID Electrically Erasable Programmable Read-Only Memory* (EEPROM) (Microchip Technology Inc. 2013) is located at the bottom left and can be used to specify configuration data for the setting of the adjustable 1.8 V FPGA IO voltage. Also visible on the bottom left are four vertical *Hirose CX80B1-24P USB3.2 Type-C* receptacles (Hirose Electric Co., LTD. 2024) interfacing to the multi-gigabit transceivers.

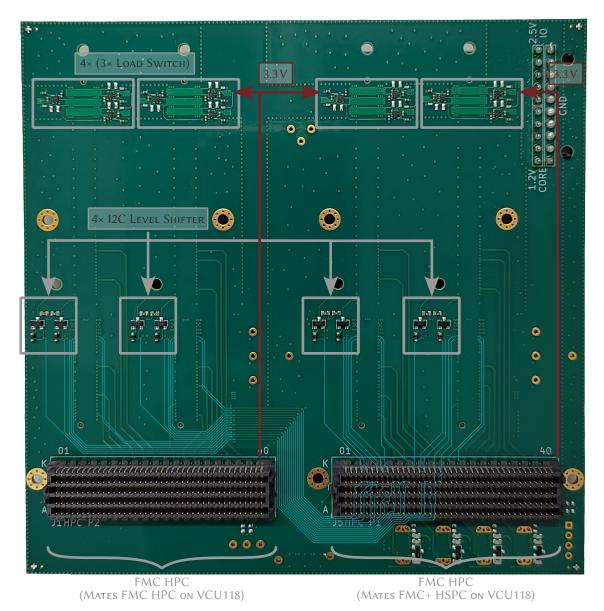

The bottom side of the PCB shown in Figure 2.7 features two identical *Samtec ASP-134488-01* connectors (Samtec 2024a) that are mechanically and electrically compatible with both the FMC and the FMC+ connector on the VCU118. Slow control signals to each ASIC-AB are provided by the FMC+ mating connector and routed on a dedicated inner layer (*turquoise*). The I2C signals are passed through a level shifting circuit to convert from 1.8 V on the FPGA side to 3.3 V on the ASIC-AB side. The 3.3 V auxiliary supply voltage is provided by the VCU118 and routed from the FMC connectors to the upper edge of the board. Together with the 1.2 V and 2.5 V supply voltages, it is fed to distinct *Texas Instruments TPS22992RXP* load switches (Texas Instruments Incorporated 2021) that limit the inrush current on these rails towards the ASIC-AB such that power sequencing can be controlled.

#### Layer Stack-Up

Due to the high pin count and dense arrangement of signals in the vicinity of the FMC connectors, a stack-up of eight layers for the MezzaMix PCB has been chosen. Table 2.1 summarizes the layers and their primary functionality.

### **High-Speed Signal Integrity Measures**

When the frequencies of transmitted signals on PCBs are high, the wavelengths of the frequency components that contribute to the signal eventually shrink to the order of the wire length that they are transmitted along. In this case, there may be multiple bits sent along the transmission line at the same point in time, which may lead to undesired mutual degradation of the digital pulses, if no special care is taken in the design phase to mitigate these effects. There is plenty of good literature on high-speed signal integrity such as for instance Hall 2009.

In many cases, approximative formulas are sufficient to describe the transmission properties of PCBs at high frequencies – at least relative to the accuracy that can be achieved by the manufacturer during the production process. To get an approximate idea whether special signal integrity measures have to be considered for the MezzaMix PCB, the following estimations have been made: In the case of the targeted multi-chip platform, the high-speed LVDS links between FPGA and ASIC represent the fastest changing signals, which run at a clock frequency of f = 500 MHz. The components with the highest frequency in the signal are defined by the rise and fall time of the square wave edges, which is not exactly known. So, for the following estimations f = 500 MHz will be used to get a *best case* estimate for the critical harmonics.

<sup>&</sup>lt;sup>9</sup>No data sheet was available by the manufacturer at the time of thesis submission; More information can be found, for instance, via third party distributors such as DigiKey.

| Layer name | Function                                                                                                                   |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ТОР        | Connector landing pads                                                                                                     |  |  |  |

|            | Routing of PLL reference clock                                                                                             |  |  |  |

|            | Routing of high-speed LVDS signals                                                                                         |  |  |  |

|            | Partial routing of slow control signals                                                                                    |  |  |  |

|            | Partial distribution of 1.8 V power rail                                                                                   |  |  |  |

| IN1        | Ground                                                                                                                     |  |  |  |

| IN2        | Routing of high-speed LVDS signals                                                                                         |  |  |  |

| IN3        | Distribution of 1.2 V, 2.5 V and 3.3 V power rails<br>Ground                                                               |  |  |  |

| IN4        | Distribution of 1.8 V, 3.3 V and 12 V power rails<br>Ground                                                                |  |  |  |

| IN5        | Routing of slow control signals                                                                                            |  |  |  |

| IN6        | Ground                                                                                                                     |  |  |  |

| BOT        | Connector landing pads<br>Routing of high-speed LVDS signals<br>Partial distribution of 1.2 V, 2.5 V and 3.3 V power rails |  |  |  |

Table 2.1: Summary of layer functions for the MezzaMix PCB.

The wavelength  $\lambda$  of a signal propagating along a transmission line can be given in terms of the relative dielectric permittivity  $\epsilon_r$  of the dielectric used in the PCB:

$$\lambda = \frac{c}{\sqrt{\mu_r \epsilon_r} \cdot f}.$$

(2.1)

In this equation, c corresponds to the vacuum speed of light  $c = 3 \times 10^8$  m/s and  $\mu_r$  to the relative magnetic permeability of the dielectric, which can be considered as  $\mu_r = 1$  for most materials in this context. For transmission lines on a PCB, the exact value of  $\epsilon_r$  often corresponds to an effective value of the various media that enclose the copper trace. A common dielectric used in PCBs is FR4 with a relative dielectric permeability of approximately  $\epsilon_r \approx 4$ . Hence, for the high-speed links between FPGA and ASIC

$$\lambda \approx \frac{3 \times 10^8 \,\mathrm{m/s}}{\sqrt{4} \cdot 500 \,\mathrm{MHz}} = 30 \,\mathrm{cm}. \tag{2.2}$$

Equation 2.2 provides somewhat of an *upper boundary* for the *smallest wavelengths* of the contained harmonics, which very likely are significantly smaller. For instance, it is known that the LVDS drivers of the ASIC operate at a high, fixed slew rate, meaning that the signal contains harmonics with a comparably high frequency<sup>10</sup>. The etch length of the copper traces of the links along the four different PCBs in the setup shown in Figure 2.5 spans across several cm in length. This means that the smallest wavelengths contributing to the high-speed signals are expected to very

<sup>&</sup>lt;sup>10</sup>Personal communication with Johannes Schemmel and Joscha Ilmberger.

likely be of the same order. Hence, considerations have been made to mitigate the most critical effects for high-speed signal transmission in the design phase, which will be outlined briefly in the following. As a guideline for this process, two application notes (Weiler, Pakosta, and Verma 2006 and Texas Instruments Incorporated 2018) provided by *Texas Instruments Incorporated* have been used.

#### PROPAGATION DELAY

In differential signaling standards, the difference of two complementary signals of opposite polarity across a pair of wires is used to define the logical level of a digital signal. If the wire pair is routed properly, then this approach can help to cancel out noise coupling in from external sources, as the noise couples into both traces with the same polarity. Taking the difference of the individual signals then largely eliminates the disturbance. If, however, the lengths of the traces are mismatched, then the noise does not couple into both traces symmetrically and is not accounted for at the receiver. Additionally, the quality of the square signal is further degraded at the receiver by part of the signal difference coupling into the common mode, which is ultimately rejected. In most cases, the mismatch is due to board layout constraints not allowing for a symmetric routing of the traces, which can be accounted for by purposefully stretching the shorter trace close to the mismatched end. Care must be taken though, as the stretching – which is typically done by drawing a wavy trace shape – can lead to an increased susceptibility to crosstalk.

Due to the tight layout constraints posed onto the routing of the high-speed signals at the ball grid array of the FMC connectors, a maximum intra-pair skew s of roughly  $s \approx 860 \,\mu\text{m}$  has been measured. Similar to before, the phase velocity  $v_p$  of a harmonic of the signal on the transmission line can be approximated via

$$v_p = \frac{c}{\sqrt{\epsilon_r}} \approx \frac{3 \times 10^8 \,\mathrm{m/s}}{2}.$$

(2.3)

The resulting temporal delay  $\Delta t$  of the signal between the mismatched wires hence corresponds to

$$\Delta t = \frac{s}{v_p} \approx 5.8 \,\mathrm{ps.} \tag{2.4}$$

Relative to the period  $T = \frac{1}{f}$  of the 500 MHz high-speed clock, this corresponds to a mismatch of

$$\frac{\Delta t}{T} = \frac{5.8 \,\mathrm{ps}}{1 \,/ \,500 \,\mathrm{MHz}} \approx 0.3 \,\%. \tag{2.5}$$

For the fastest signal components, this ratio is expected to be larger. However, regarding the FPGA side of the links, the *ANSL/VITA Standard* specifies the skew between user defined pins to be kept smaller than 10% of the unit interval for the targeted data rates to maximize performance (VITA 2019). As the maximum skew on the MezzaMix is expected to be well below this, the propagation delay has not been optimized further.

#### Impedance Matching

Another important guideline to consider for high-speed signal routing is to account for impedance discontinuities along the full path of the signal between transmitter and receiver. When an electromagnetic wave propagates across the interface of two transport media with different characteristic impedances  $Z_0$  – for instance through a connector between two different PCBs – then part of the wave is transmitted through the interface to the next transmission line while part of it is reflected back along the initial transmission line to the source. This phenomenon can lead to over- and undershoots of the transmitted wave and ultimately a degraded signal quality at the receiver. For two transmission lines 1 and 2 with characteristic impedances  $Z_{01}$  and  $Z_{02}$ , respectively, the reflection coefficient  $\rho$  provides a measure for how much of the wave's amplitude is reflected back to the source:

$$\rho = \frac{Z_{02} - Z_{01}}{Z_{02} + Z_{01}}.$$

(2.6)

In the extreme case, where  $Z_{02} \rightarrow \infty$  – corresponding to an open circuit – then  $\rho \rightarrow 1$ . That is, all of the wave's amplitude is reflected. In order to minimize the reflections,  $\rho = 0$  demands that  $Z_{01} = Z_{02}$ . So the characteristic impedances of the different transmission lines need to be matched. For single-ended signaling, typically  $Z_0 = 50 \Omega$  is targeted, while for differential signaling  $Z_0 = 100 \Omega$  is used – given that the transmission line is terminated accordingly at the receiver.

The characteristic impedance  $Z_0$  of the transmission line is constrained by the properties of the employed materials on the PCB and the specific geometry used. Therefore, most manufacturers provide impedance calculators for their respectively employed production process. This allows the designer to adapt the trace widths and spacings – in the case of differential signaling – to match the targeted impedances. During the design process of the MezzaMix PCB, the constraints provided by a *defined generalized layer stack-up* from *Multi Leiterplatten GmbH* (Multi Leiterplatten GmbH 2024) have been used to fix the differential trace geometries on the different layers of the PCB. To match the targeted impedances on the inner layers, the trace widths w and differential pair spacings h have been cross-checked with an impedance calculator tool in *Cadence Allegro*. Note that in general, to fully account for critical effects, extensive simulations to solve Maxwell's equations for the given geometry and boundary conditions need to be performed to compute the characteristic impedance  $Z_0$ , which has been considered to not be within the scope of this thesis<sup>11</sup>. Additionally, the impedances of the single-ended slow control signals have not been optimized as they are not expected to greatly diminish the signal quality at low frequencies<sup>12</sup>.

| PCB layer   | Targeted impedance $Z_0 [\Omega]$ | Trace width $w \; [\mu m]$ | Pair spacing $h \ [\mu m]$ | Approximated impedance $Z_0 \left[ \Omega \right]$ |

|-------------|-----------------------------------|----------------------------|----------------------------|----------------------------------------------------|

| TOP and BOT | 100                               | 120                        | 115                        | 98.6                                               |

| IN2         | 100                               | 100                        | 160                        | 97.5                                               |

Table 2.2: Impedance matched differential signal geometries for the MezzaMix PCB.

<sup>&</sup>lt;sup>11</sup>Personal communication with Joscha Ilmberger.

<sup>&</sup>lt;sup>12</sup>Personal communication with Joscha Ilmberger, Andreas Grübl and Lars Sterzenbach.

#### Crosstalk

Lastly, measures have been taken to minimize the susceptibility of individual traces to crosstalk. The term *crosstalk* describes the mutual influence of closely routed traces due to inductive and capacitive coupling. The trace that carries the signal – referred to as the *aggressor* – influences another nearby trace – called the *victim* – by inducing forward and backward currents in the victim trace. For differential signal pairs, the tight coupling between the aggressor and victim is actually desired, but this can only be achieved, if other differential signal pairs are kept sufficiently far away. For high-speed data transmission, a minimum distance of five times the width w of the traces in the differential pairs is recommended, which has been adhered to during the routing process for the MezzaMix PCB.

### 2.2.3 FPGA Implementation

With the hardware stack-up completed by adding the MezzaMix PCB, the next step in the setup commissioning procedure is to realize the communication between the VCU118 and a single HICANN-X. To this end, the basic FPGA implementation used in, for instance, the Cube systems must be adapted to the new platform. In general, this requires only minor changes regarding the IO constraints, clocking and memory utilization. No major re-design of the communication protocol is needed as the Kintex-7 and the Virtex UltraScale+ architectures are similar enough and the FPGA on the VCU118 offers considerably more logic resources such that small-scale optimizations are not considered to be required for the moment<sup>13</sup>. In the following, a brief overview over the implemented FPGA design will be provided and differences to the current state of the Cube systems highlighted.

#### Constraints

The assignment of the user definable pins of the FMC and FMC+ connectors relative to the MezzaMix PCB requires to specify IO constraints in order to set the IO cells to the desired signaling standard. As a basis for this step, a publicly available, open source, predefined constraints list<sup>14</sup> has been used and adapted further. The constraints are specified by means of *Xilinx Design Constraints* (XDC) commands of the following form:

|   | <pre>set_property -dict {LOC P37 IOSTANDARD LVDS DIFF_TERM TRUE} \</pre> |

|---|--------------------------------------------------------------------------|

|   | <pre>[get_ports {I_CHIP_DAT_RX_P[0][1]}]</pre>                           |

|   | <pre>set_property -dict {LOC N37 IOSTANDARD LVDS DIFF_TERM TRUE} \</pre> |

|   | [get_ports {I_CHIP_DAT_RX_N[0][1]}]                                      |

| _ |                                                                          |

This example defines the two signals routed to pin P37 and N37 of the FPGA fabric as an input LVDS pair with enabled  $100 \Omega$  differential termination. The signal names such as I\_CHIP\_DAT\_RX\_P[0][1] need to match the declaration in the top-level port list of the design. This denomination corresponds to the differential signal with positive polarity coming from link 1 of the ASIC located at slot 0 on the MezzaMix PCB. Similar constraints have been added for the other high-speed links and the slow control signals towards the HICANN-X.

<sup>&</sup>lt;sup>13</sup>Personal communication with Joscha Ilmberger.

$<sup>^{14} \</sup>mbox{Provided by Alex Forencich via $GitHub: https://github.com/alexforencich/verilog-ethernet.} \label{eq:alexapprox}$

### TOP-LEVEL

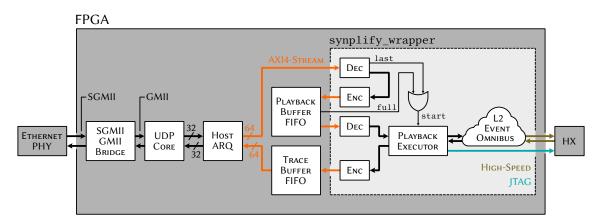

A schematic of the MezzaMix FPGA top-level for single-chip communication is provided in Figure 2.8. It corresponds to a mixture of existing FPGA implementations for the Cube systems and for host communication to the VCU118 via Ethernet<sup>15</sup>. In the latter, an interface has been introduced to connect the *Host Automatic Repeat-Request* (Host ARQ) protocol – used as a transport layer for host communication in the BSS-2 architecture – and an *User Datagram Protocol* (UDP) core that ultimately establishes the connection to an Ethernet port on the VCU118. The MezzaMix FPGA top-level displayed in Figure 2.8 implements features of both top-level specifications.

**Figure 2.8:** Schematic representation of the MezzaMix FPGA top-level for single-chip communication. Two FIFOs buffer the playback program and the response data to and from the playback executor. The transmission of application data to the Host ARQ and the synplify\_wrapper is performed via an AXI4-Stream bus protocol.

Within the FPGA implementation of the BSS-2 architecture, the major part of the experiment control logic is wrapped in a synplify\_wrapper<sup>16</sup> module. This module can be thought of as the single highest level entity within the FPGA implementation that can communicate with the HICANN-X ASIC. For the targeted multi-chip platform, the synplify\_wrapper can be considered as a fixed design component and hence is implemented as-is for the MezzaMix top-level<sup>17</sup>. It contains a *Playback Executor* module that allows for the timed release of events to the HICANN-X. It does so by executing pre-buffered *Playback Programs* that contain a sequence of timed read and write instructions that, for instance, may be used to modify the weight of a specific synapse during runtime. The response data from the HICANN-X needs to be buffered by the FPGA to be accessible to the user.

In order to be able to send and receive data to the HICANN-X from a host computer, application data must be transferable from the Host ARQ to the synplify\_wrapper. Similar to the Cube FPGA implementation, this in done through a 64 bit *Advanced eXtensible Interface* (AXI) for the MezzaMix FPGA top-level (*orange*). Data transferred from the Host ARQ to the synplify\_wrapper is first piped to a *decoder* stage that translates the application data to instructions for the Playback Executor<sup>18</sup>.

<sup>&</sup>lt;sup>15</sup>URL: https://gerrit.bioai.eu:9443/c/hxfpga/+/19261/6;

Commit hash 8b663f304877d7514c807e9703458a630b549d25.

<sup>&</sup>lt;sup>16</sup>For legacy reasons, the synthesis of the synplify\_wrapper is done in *Synopsys Synplify*, hence the denomination of the module.

<sup>&</sup>lt;sup>17</sup>Personal communication with Joscha Ilmberger.

<sup>&</sup>lt;sup>18</sup>The decoder and encoder stages are explained in more detail in Section 3.1.1.

In an additional *encoder* stage, the instructions are encoded back to 64 bit words and streamed to a *playback buffer*. Within the MezzaMix FPGA implementation, the buffering is realized by employing a Xilinx *intellectual property* (IP) *first-in-first-out buffer* (FIFO) with a depth of 8192. Due to the large depth desired for the buffering of playback data, *UltraRAM* (URAM) blocks<sup>19</sup> are utilized for the FIFO. The buffered data is then held back until the Playback Executor releases the newly decoded instructions via the high-speed communication interface – denoted as *Layer 2* (L2) – for the transmission of timed event data and *Omnibus* configuration data<sup>20</sup> to the HICANN-X. The execution of the playback program is either started when the decoder recognizes that the last instruction has been sent or when the playback buffer is almost full.

The response data from the HICANN-X is then encoded again to 64 bit words and stored in a *trace buffer* FIFO. In this implementation, the depth is again set to 8192, which is a rather arbitrary choice as the VCU118 FPGA offers a vast amount of logic resources. Optimization of the memory utilization could be done when extending the implemented design for communication with more than one ASIC. When the user requests the readout of the response data, the buffered data is streamed back to the Host ARQ again.

Table 2.3 summarizes the resource utilization for the full communication logic from a host computer to the HICANN-X in the VCU118 FPGA.

| Resource | Available | Full Design<br>Utilization | Full Design<br>Rel. Utilization | synwrap<br>Utilization | synwrap<br>Rel. Utilization |

|----------|-----------|----------------------------|---------------------------------|------------------------|-----------------------------|

| LUT      | 1182240   | 39535                      | 3.34 %                          | 19458                  | 1.65 %                      |

| LUTRAM   | 591840    | 3102                       | 0.52~%                          | 1794                   | 0.30 %                      |

| FF       | 2364480   | 40757                      | 1.72~%                          | 14134                  | 0.60~%                      |

| BRAM     | 2160      | 167                        | 7.73%                           | 50.5                   | 2.34~%                      |

| URAM     | 960       | 12                         | 1.25~%                          | 0                      | 0 %                         |

| DSP      | 6840      | 42                         | 0.61 %                          | 39                     | 0.57~%                      |

| ΙΟ       | 832       | 274                        | 32.93 %                         | 0                      | 0 %                         |

| BUFG     | 1800      | 16                         | 0.89%                           | 2                      | 0.11~%                      |

| MMCM     | 30        | 2                          | 6.67 %                          | 0                      | 0 %                         |

| PLL      | 60        | 5                          | 8.33 %                          | 0                      | 0~%                         |

**Table 2.3:** Resource utilization of the VCU118 FPGA for single chip communication. Summarized arethe resources spent on the entire design and on a single instance of the synplify\_wrapper(synwrap). Note that the IO resource utilization of the full design implies the constraintsspecified for the full available pin out on the FMC and FMC+ connectors, that is, for four directlyattached HICANN-X ASICs.

The relative utilization of the IO resources of the full design displayed in Table 2.3 includes the entire pin out of the FMC and FMC+ connectors, that is, for four directly attached HICANN-X ASICs. While the design utilizes about 7.7% of the available *block random-access memory* (BRAM), the synplify\_wrapper only accounts for roughly 2.3% of the available elements. Also, the utilization of the remaining logic elements is quite small such that it is expected that the experiment control logic can be instantiated multiple times for additional chips without reaching capacity limits soon.

<sup>&</sup>lt;sup>19</sup>Essentially, this is high storage capacity BRAM.

<sup>&</sup>lt;sup>20</sup>Initial configuration of the HICANN-X is performed via JTAG until the high-speed interface is accessible.

The full FPGA implementation for the MezzaMix is available via *git* in the hxfpga repository<sup>21</sup>.

## 2.2.4 Single-Chip Setup

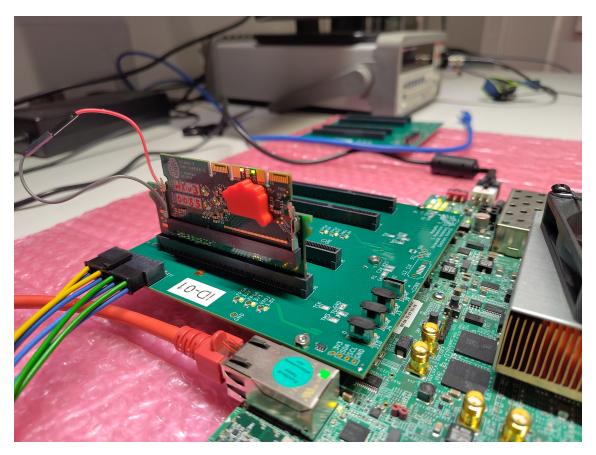

After completing the hardware stack-up with the MezzaMix PCB and adapting the Cube and VCU118 Ethernet FPGA implementations to allow for full Host-to-ASIC communication, the multi-chip platform has been assembled. Figure 2.9 and 2.10 display the setup during operation with a single HICANN-X. The programming of the FPGA is done using a JTAG adapter, while the host communication to the ASIC is established via Ethernet.

Figure 2.9: Top-view photograph of the assembled multi-chip setup during operation with a single HICANN-X.

First connectivity tests for the connection between host and FPGA, as well as between FPGA and ASIC have been performed, which will be summarized briefly on a qualitative level: Loop-back data tests between host and FPGA were successful, including the transmission of application data to and from the Playback Executor. Additional loop-back tests have been performed to test the data throughput on the high-speed links between the FPGA and the HICANN-X. Compared to the Cube systems, a lower throughput at the high-speed interface has been determined. The degraded performance could potentially be due to electrical problems on the MezzaMix PCB or uncompensated clock-to-data skew at the FPGA high-speed LVDS de-serializers.

<sup>&</sup>lt;sup>21</sup>URL: https://gerrit.bioai.eu:9443/c/hxfpga/+/22197;

Commit hash at state of writing this thesis: 62b414f012cef9179e5d4dc571306844d4a0d792.

Figure 2.10: Close-up photograph of a chip carrier board during operation in the multi-chip setup.

However, it was not possible to further investigate the performance of the high-speed links on the multi-chip platform due to a defect of the VCU118 rendering the board insusceptible for additional tests.

## 2.3 Summary and Discussion

Up to this point, an operational single-chip setup with the VCU118 has been commissioned. The development included the design of the MezzaMix PCB – a mezzanine board to the VCU118 – that closes the gap in the hardware stack to connect up to four HICANN-X ASICs to a single FPGA. Additionally, the FPGA implementation for single-chip communication with the Virtex UltraScale+ FPGA on the VCU118 has been fully established for each of the four individual slots. First connectivity tests have been performed, showing promising results regarding the operation with a single HICANN-X.

The single-chip system can be extended into a *multi-single-chip* setup that would allow for communication between host and multiple HICANN-X ASICs through a single FPGA. In order to complete the system in this fashion, additional experiment control blocks – that is, an additional synplify\_wrapper for each ASIC – would need to be instantiated, accompanied by an attached Host ARQ block, respectively. To address the individual ASICs, a multiplexing stage would need to be introduced between the UDP core and the Host ARQ instances.

To develop the platform into a *full multi-chip* system, the FPGA implementation needs to be extended further by means of a router core that interconnects the experiment control logic on the L2 level. This core is currently under active development.

With the defect of the VCU118, however, it was not possible to continue these efforts in the scope of this work, as no second board for replacement was available within the thesis time constraints. This also highlights a crucial drawback of the design choices outlined in Section 2.1.1: In the targeted star topology for the interconnection of chips, the central node is the most critical network constituent. If it fails, the connection of the entire network breaks down until the failure is corrected or the node replaced. Without adapting the topology, there is little protection of the network against such failures. This issue needs to be considered in further attempts to extend the BSS-2 architecture for multi-chip operation.

# **3 HIGH-SPEED LINK STABILIZATION**

During experiment execution with the BSS-2 family of devices, experiment data needs to be transferred between the experiment control host and the neuromorphic substrate. This includes, but is not limited to, experiment configuration data such as neuron parameters, real time injection of spike events, or readout of experiment data. This information is used for network re-configuration or further processing in the evaluation of the experiment. As for example described in Karasenko 2020, the injection of spike events requires precise timing due to their analog and asynchronous nature and the 1000-fold acceleration factor compared to biological real time of the analog substrate.

In addition to posing critical demands on latency and jitter, the small time scales in play call for a high-speed event interface between the control host and the substrate. The HICANN-X therefore employs LVDS (de-)serializers (Scholze et al. 2012). A variant of the (de-)serializer macro also exists at the L2 of the FPGA design within the experiment control unit (cf. Figure 2.8) by employing, for example, the *input serial-to-parallel converter* (ISERDESE2) and *output parallel-to-serial converter* (OSERDESE2) primitives provided for Kintex-7 FPGAs (Xilinx, Inc. 2018).

Within the BSS-2 architecture, eight (de-)serializer pairs form the high-speed communication interface between the host FPGA and the ASIC (Karasenko 2020). Each of the (de-)serializer pairs corresponds to a point-to-point, byte aligned, full-duplex link with one differential data pin and a shared differential clock pin for all eight data pins per direction. The data transfer in each direction is realized source synchronously in *double data rate* (DDR) fashion at a clock frequency of 500 MHz, allowing for a data transfer rate of 1 Gbit/s<sup>1</sup> per each of the eight links<sup>2</sup>.

The (de-)serializer macros described in Scholze et al. 2012 implement an automatic link-training mechanism that is run during link initialization. This routine aims to align the data patterns sent by the serializer at the transmitting end and seen by the de-serializer at the receiving end. The mechanism works by using a combination of programmable delay elements and flip-flop registers in the de-serializer. This allows for compensation of clock-to-data skew – for instance accumulated through the routing on the PCB – and bitwise alignment of the delayed data pattern to correctly recognize the first and the last bit in the transmitted word. For a more detailed description of the link training mechanism the reader may be referred to Section 3.2.

Section 2.2.4 describes performance limitations in the high-speed link communication between FPGA and ASIC when performing a high-speed data loop-back test in a single-chip configuration on the MezzaMix setup. Similar, yet less frequent issues have been observed on other systems as well, for instance on the Cube or the BSS-2 mobile systems. Due to a defect on the VCU118 – rendering the board insusceptible for further analysis of this problem on the multi-chip platform

<sup>&</sup>lt;sup>1</sup>Technically, the ASIC PHY can operate at data rates up to 2 Gbit/s. The data rate is limited by the FPGA.

<sup>&</sup>lt;sup>2</sup>As a side note, a single link is commonly referred to as a PHY in the BSS-2 architecture, a convention that will be adopted and used interchangeably throughout the chapter.

- the decision was made to continue with the investigation on the existing Cube systems<sup>3</sup>.

The Cube and the MezzaMix setups are not exactly comparable as they come with different PCB layouts, transmission line lengths, impedance discontinuities across connectors and so on. Yet, first qualitative investigations on the MezzaMix setup have at least shown some similarities in the behavior of the links to the Cube systems. There are single links that tend to fail more often than others, failures seem to occur on different timescales – that is, almost immediately after link initialization as well as some seconds later – and some links tend to fail a second time, immediately after they have been re-trained due to a first detected failure.

In this chapter, a deeper analysis of the stability of the high-speed links on BSS-2 systems will be given. Section 3.1 provides an overview over the relevant statistics that will be used to quantify the stability of the links and introduces a routine to sample them systematically. As a representative example for the current state of the high-speed links, stability results from a Cube system are presented. Section 3.2 explains the training algorithm run during link initialization in detail and shows trace data from an in-hardware debugging method for both working and failing link trainings. Corrections to the observed flaws in the training procedure are presented and the performance of the updated algorithm is evaluated. The chapter concludes with an investigation of the influence that the configuration of the ASIC receiver exerts on the link stability in Section 3.4 and a discussion of the gathered results in Section 3.5.

## 3.1 Prerequisites and Current State

This section aims to define a criterion suitable for evaluating the stability of the high-speed links. After introducing the relevant statistics to be investigated and outlining a routine to systematically test the link stability on different setups an example of the current state of the high-speed links is provided.

## 3.1.1 Stability Criterion

The usual way to characterize the *qualitity* of a link is to define a *bit error rate* that counts the number of bits which have been altered on their way between the transmitting and receiving end of a communication channel. In many cases this can be caused by electrical problems such as noise on the transmission line or crosstalk coupling in from neighboring data channels. Another cause of failure can be synchronization issues that may lead to false detection of the bit logic value by sampling the voltage level on the transmission line at suboptimal points in time. However, the raw bit error rate is not always easy to quantify. It requires access to and knowledge about the raw data transmitted via the communication channel by digging deep into the *PHYsical layer* (PHY) of the system under test, which is not always possible. To circumvent this issue, it is useful to define the quality of the link on a different level of abstraction, for instance by assessing the data handled on the link layer.

In case of the BSS-2 systems, the link layer is comprised of so called *Universal Translator* (UT) modules that interface to the (de-)serializer and serve as encoders, respectively decoders, between

<sup>&</sup>lt;sup>3</sup>Personal communication with Johannes Schemmel

data words accessible to the user on the application layer and bytes transmitted on the PHY (Karasenko 2020). The encoding scheme in the UT offers the possibility to append *cyclic redundancy check* (CRC)<sup>4</sup> information to a data word which is being handed over to the serializer, allowing for automated error detection at the far end of the communication channel. Consequently, the UT module also provides a link checking mechanism that is able to detect link errors by evaluating CRC data. When CRC errors are detected, the UT module issues a re-training command to the (de-)serializer, rendering the corresponding link unaccessible for transmission of user data until it is re-initialized anew.

It is important to note that a single CRC error is not the sole condition that can lead to a re-training of a link. In particular, the UT requires two consecutive CRC errors to be reported, while it also implements additional sanity checks to monitor the health state of the link. More specifically, one of the following conditions must be met:

- 1. Two consecutive CRC validations must fail,

- 2. the validation of header information specific to the employed encoding scheme must fail or

- 3. a user configurable timeout since the last successful CRC validation is met.

For a more detailed description of this behavior the reader may again be pointed to Karasenko 2020.

Important to note is that the re-training of a link after failure cannot be conducted independently for the two endpoints – FPGA and ASIC – of the communication channel. Triggering the re-training on either of the two endpoints leads to transmission of a predetermined training signal to the other link partner, who now essentially tries to decode garbage data (Karasenko 2020). By failing to validate the non-existing header information in the training pattern, the UT within the second endpoint issues a re-training command as well, ultimately resulting in a complete re-training of the link.

Besides the link checking mechanism, the UT also provides information about the link status to the user by accessing the event queue of the Playback Executor. A 5 bit status value – that is, one bit for each of the failure conditions listed above and two additional bits for a successful training after system initialization and re-training after failure – together with the 3 bit ID of the corresponding link is annotated with a 43 bit time stamp and buffered for readout to the experiment host. Thus, whenever a link is (re-)initialized or a link check condition is met that leads to a re-training of a link, a status notification is generated. In the current implementation, this information is however limited to the FPGA side of the communication channel. The peculiarity of the link being re-trained in both directions – regardless of the location at which the first critical failure has been detected – still guarantees that all link failures are reported, although one needs to be careful when interpreting the status information as it only gives insight about the FPGA side of the link.

Due to its well-defined implementation and ease of access, the time-annotated status information of the UT located in the FPGA can be considered as a suitable data structure to gain insight about the link stability. Since not only the failures but also the (re-)initializations of a link are reported

<sup>&</sup>lt;sup>4</sup>Roughly speaking, a CRC involves polynomial division of the data word to be transmitted to calculate a check value which can be checked against by performing the same calculation on the received data word.

and time-stamped, it is possible to construct well-defined time intervals in which the link has been *stable*, that is, in a state after a successful (re-)initialization with no error having been detected yet.

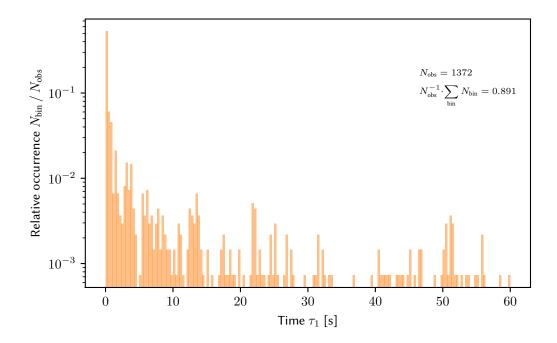

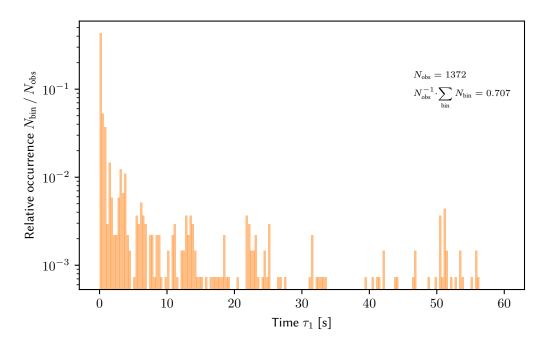

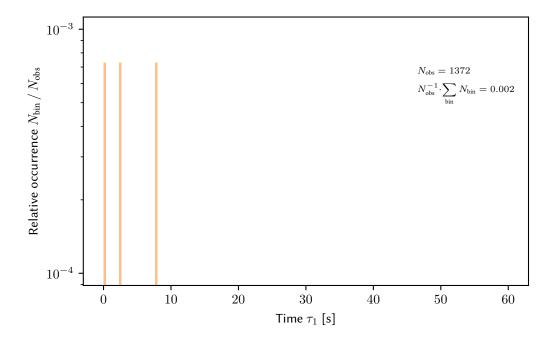

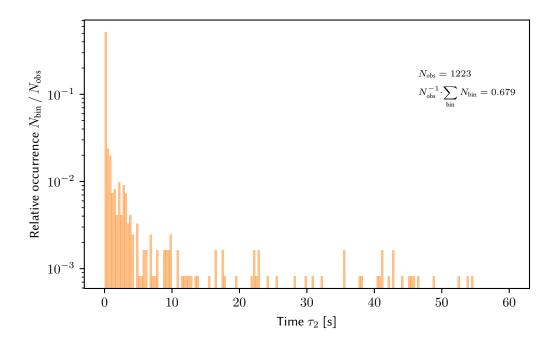

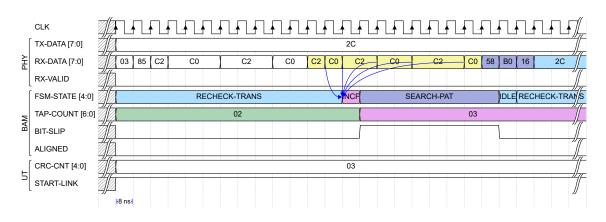

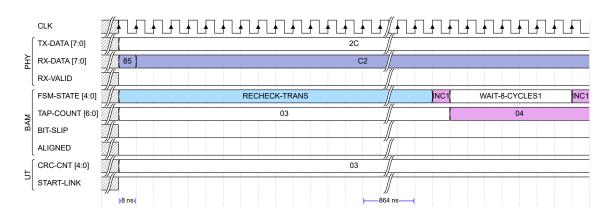

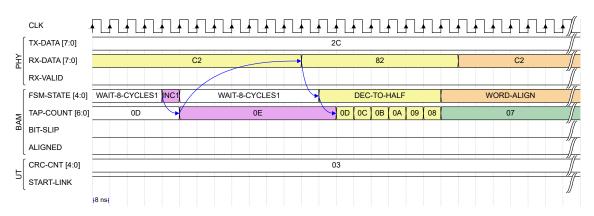

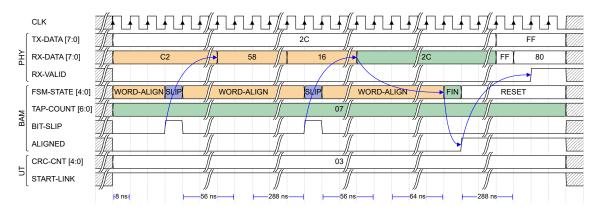

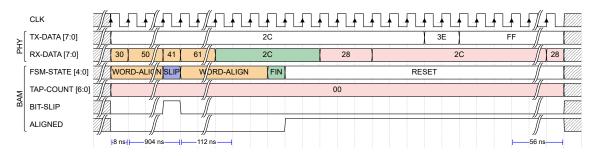

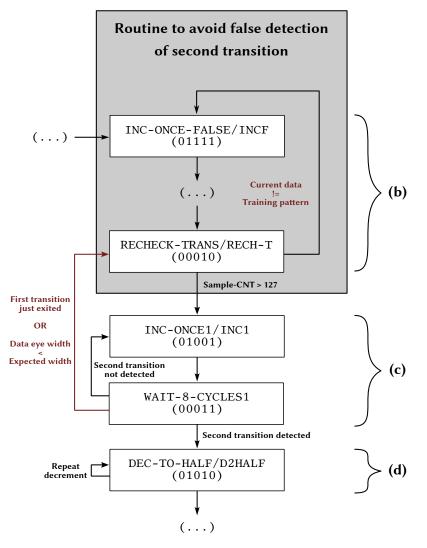

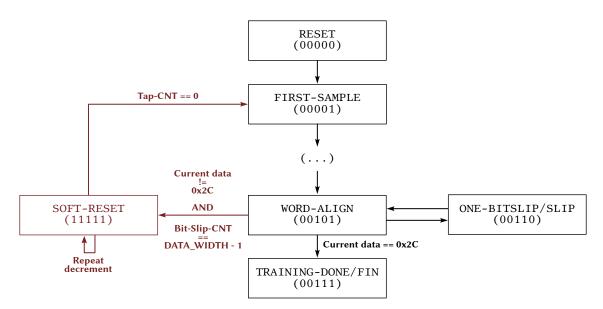

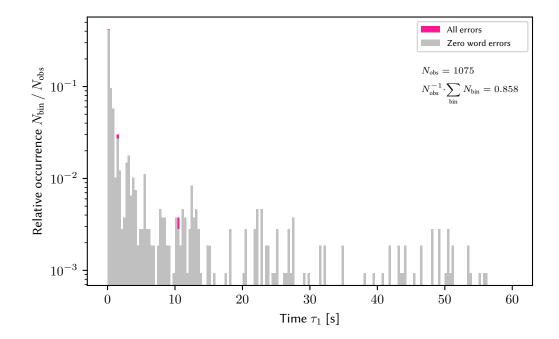

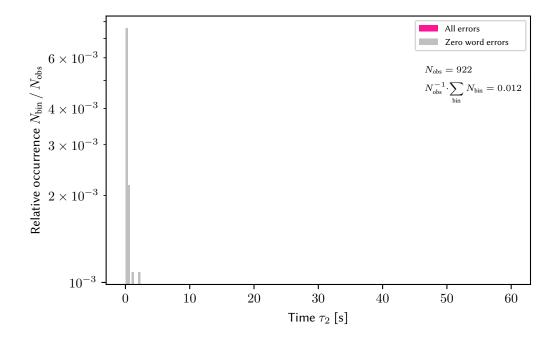

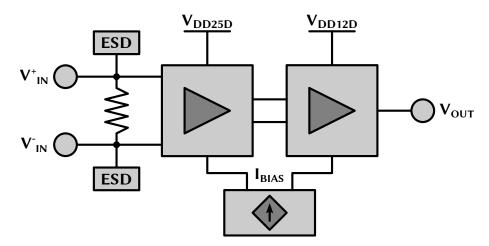

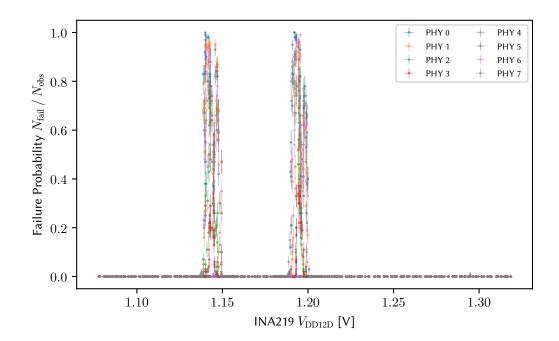

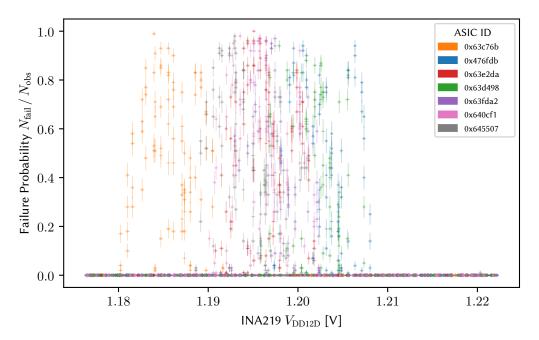

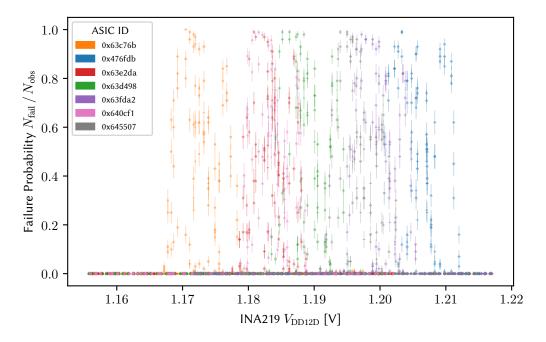

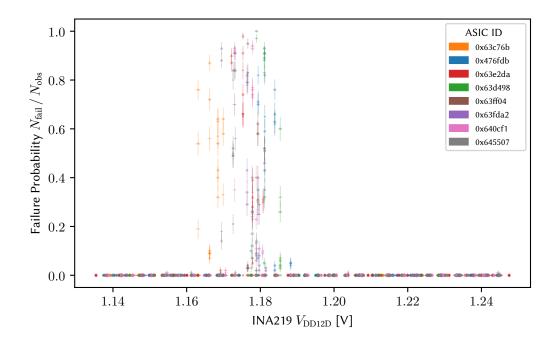

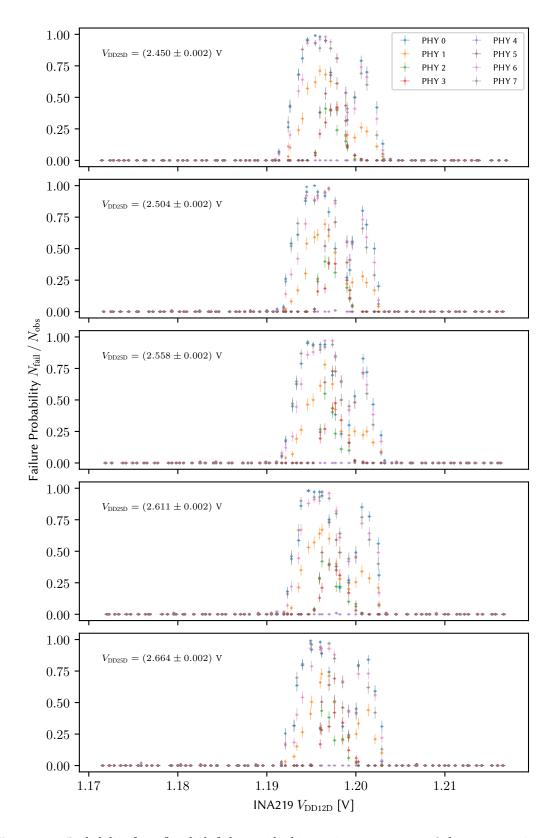

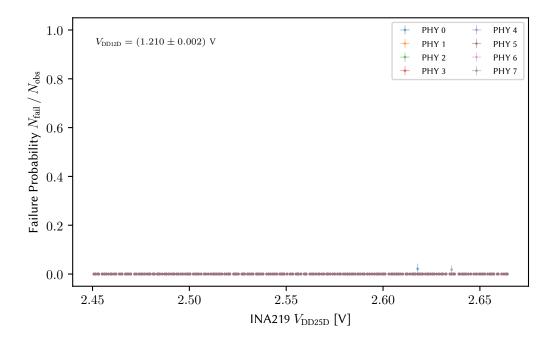

### 3.1.2 Time to First and Second Failure