# Department of Physics and Astronomy Heidelberg University

Bachelor Thesis in Physics submitted by

# Kaspar Frieder Haas

born in Karlsruhe (Germany)

$\boldsymbol{2023}$

Parameterized circuits for accelerated design and simulation

This Bachelor Thesis has been carried out by Kaspar Frieder Haas at the Kirchhoff Institute for Physics in Heidelberg under the supervision of PD Dr. Johannes Schemmel

## Abstract

In the development of increasingly complex analog neuromorphic chip designs, the use of flexible and scalable design parts can be of great advantage. This is because chips created using these so called Parameterized Cells (PCells) can become more flexible, while at the same time opening the possibility for wider use cases of these cells.

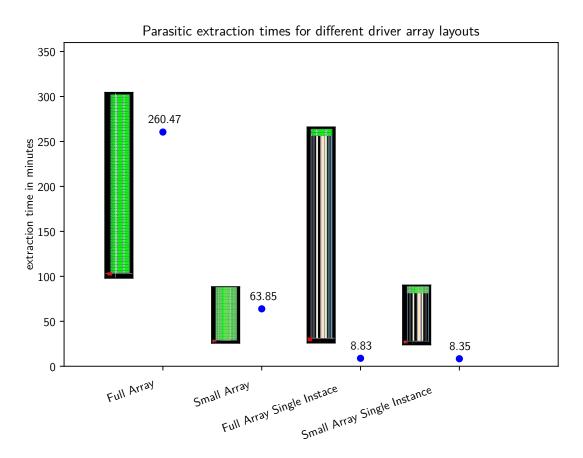

The work presented here demonstrates this by creating a scalable synapse driver array for use in the BrainScaleS-2 (BSS-2) system. Here the creation process of the array, including the creation of a second PCell, an address decoder, as well as some simulations will be shown. The results produced can even be seen as a first step towards the creation of a fully scalable BSS-2 core. To achieve this the described parameterization process has to be expanded to the other parts of the chip. Furthermore the simulations performed using the created synapse driver array show a possible speed gain when using the flexibility of PCells, by comparing the simulation times of the differently instantiated arrays to each other.

# Kurzfassung

Bei der Entwicklung immer komplexerer analoger neuromorpher Chips kann die Verwendung von flexiblen und skalierbaren Designteilen von großem Vorteil sein. Die Gründe hierfür sind, dass die Chips, welche mit den parametrisierbaren Zellen erstellt werden, selbst flexibler werden und dass die parametrisierten Zellen in mehr Anwendungsfällen verwendet werden können.

Die vorliegende Arbeit zeigt dies anhand der Erstellung eines skalierbaren Synapsen Treiber-Arrays, welches im BrainScaleS-2 (BSS-2) System verwendet wird. Hierbei werden der Erstellungsprozess des Treiber-Arrays, der auch die Erstellung eines parametrisierbaren Adressdekoders enthält, sowie die durchgeführten Simulationen des Treiber-Arrays präsentiert. Weiter kann die Arbeit als erster Schritt in Richtung eines vollständig parametrisierbaren BSS-2-Kerns gesehen werden. Um diese vollständige Parametrisierung zu erreichen, müsste der hier vorgestellte Parametrisierungsprozess auf die anderen Chipteile angewendet werden. Darüber hinaus zeigen die durchgeführten Simulationen mögliche Zeitgewinne abhängig von der gewählten Parametrisierung des Arrays. Diese werden durch einen Vergleich von unterschiedlich parametrisierten Synapsentreiber-Arrays dargestellt.

|--|

| 1      | Intro                                   | oduction                                                                                                                                                                                                                                  | 1                                                                                                                                  |

|--------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 2      | Back<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | kground         Microelectronics and CMOS production         The BrainScaleS-2 System         VLSI design flow         PCells         Simulation and parasitic extraction                                                                 | <b>1</b><br>2<br>4<br>6<br>8<br>9                                                                                                  |

| 3      | Met<br>3.1<br>3.2<br>3.3                | Cadence <sup>®</sup> Virtuoso <sup>®</sup>                                                                                                                                                                                                | <b>12</b><br>12<br>13<br>13                                                                                                        |

| 4      | <b>Crea</b><br>4.1<br>4.2<br>4.3        | Fixed synapse driver arrayAddress decoder4.2.1Parameters4.2.2Cellviews4.2.3Verification of the address decoder PCell4.2.4SimulationFlexible synapse driver array4.3.1Layout4.3.2Schematic4.3.3Symbol4.3.4Sparce array for fast simulation | <ol> <li>13</li> <li>14</li> <li>14</li> <li>21</li> <li>24</li> <li>25</li> <li>26</li> <li>28</li> <li>29</li> <li>30</li> </ol> |

| 5<br>6 | $5.1 \\ 5.2$                            | Extraction                                                                                                                                                                                                                                | <ul> <li>31</li> <li>32</li> <li>36</li> </ul>                                                                                     |

| 7      |                                         | Decoding                                                                                                                                                                                                                                  | <b>38</b><br>38<br>39<br>40                                                                                                        |

# 1 Introduction

Modern microelectronics and electronic circuits have been experiencing an explosive growth over the last decades (Razavi, 2013, p. 1). This includes the development of many different kinds of electronic devices, for example cellphones, digital cameras or computers. One thing all these devices have in common is the fact that without the rise and rapid development of integrated circuits, or so called ICs, none of them would be able to exist in their current form. As developments progressed, these ICs became larger and larger, enabling the creation of faster and more powerful electronic devices. An example often used to demonstrate this massive growth is Moore's law, stating that the complexity of minimum cost components has and will continue to increase with a factor of two per year (Moore, 2006), resulting in a doubling of transistors used in integrated circuits every year. Comparing this statement with the actual number of transistors per microchip, growing from just over 2000 in 1971 to 58.2 billion in 2021 (Our World in Data, 2023), one can easily see that Moore's prediction was quite accurate. This also meant that the tools used to create integrated systems had to change over time. Nowadays most of VLSI, or Very-Large-Scale Integrated Circuit design is done using software like the design suite provided by Cadence<sup>®</sup>. Cadence<sup>®</sup> is one of the key leaders when it comes to electronic system design, cooperating with manufacturers like TSMC or UMC.

As these circuits grow in size, the design process is expected to become more and more complex too. As a result it is desired to break down the different parts of a design into smaller chunks which then can be used as building blocks or so called cells in larger designs. When creating these cells with future projects or possible changes in mind it only seems plausible to wish for Parameterized Cells, so that the created cell is flexible or scalable and can be reused in different designs. A possible way of creating these flexible cells is the creation of so called PCells in the design suite of Cadence<sup>®</sup>, Virtuoso<sup>®</sup>.

This work shows one possible implementation of such a scalable design in analog neuromorphic systems, by using the synapse driver array of the BrainScaleS-2 system as an example. To achieve the mentioned scalability a parameterized address decoder has been created as a PCell using the programming language SKILL. With this address decoder the old driver design was modified, now allowing the user to choose a configurable number of driver outputs.

The second part of this work gives an introduction into physical parasitic effects that must be taken into account when creating and simulating analog circuits. Here an extraction and simulation of the driver array in two different configurations will be performed, showing the difference in speed and accuracy when working with increasingly complex designs.

# 2 Background

The following sections will give an introduction into the topics covered within this thesis and will also mention some resources for further reading. After a short introduction into microelectronics and CMOS factoring some information about neuromorphic hardware with focus on the BrainScaleS-2 (BSS-2) system will follow. Then the concept of VLSI design using Virtuoso<sup>®</sup> and creating PCells for this application will be explained. The introduction will close on information about parasitics in chip design as well as hint at simulation uses of these parasitics.

### 2.1 Microelectronics and CMOS production

The rise of electronic devices started about a 100 years ago, arguably with the invention of the vacuum tube in 1904. This evolution, driven by the extended use of vacuum tubes and later semiconductors, for example in amplifying circuits, changed the world. While in the beginning this development seemed quite slow, it picked up speed in the 1940s with the discovery of the transistor by Shockley, as well as Brattain and Bardeen, working in the same research group (Riordan, Hoddeson, and Herring, 1999). With this discovery the foundation for modern semiconductors was laid. Even then, it was not until the 1960s that the microelectronics and especially ICs really took off (Razavi, 2013). One reason for this was that early ICs only contained a handful of devices. This changed rapidly with the invention of the CMOS process in 1967 (Wanlass, 1967), which allowed for larger and more complex designs to be created.

Talking about the use and implementation of transistors in these ICs the question "What exactly is a transistor?" may arise. Essentially there are two types of transistors: The so called bipolar transistor and the metal-oxid-semiconductor transistor (MOS) (Phillip E. Allen, 1987, p. 29). While the bipolar transistor has been the cheaper transistor for many years, the MOS transistor has fallen in costs so dramatically, that today it is widely used in all kinds of applications. Because of this widespread use and the fact that this work does not touch electronics with bipolar transistors, this introduction will only focus on the MOS transistors.

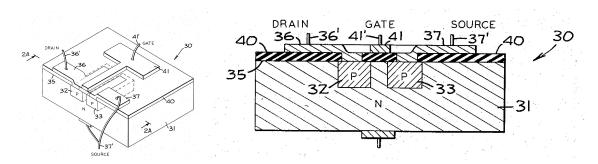

Simply put, a transistor can be seen as a controlled current source. Talking about MOS transistors, this control is achieved by controlling an electric field using a voltage. To generate this field different doped silicon layers, n+ and p+, are used. If these doped silicon layers, together with an oxide insulator, are placed in the right geometry, for a PMOS two p regions placed inside an n substrate as seen in figure 1, they form two pn-junctions between the n doped substrate and the p doped source and drain contacts.

Additionally, it can be seen that the gate and the substrate are forming the parallel plates of a capacitor, allowing for the construction of an electric field between these two contacts (Phillip E. Allen, 1987, p. 49). This electric field can change the sizes of the depletion regions created by the pn-junctions, allowing for the regulation of a current flowing from drain to source. In conclusion this means, that a voltage between the substrate, in figure 1 still called source, and the gate can be used to control the current flowing through the transistor. When using a PMOS as shown in the schematic in figure 2 this means that when the voltage between the gate and the source is smaller than a certain threshold, the

Figure 1: Layout drawing of a PMOS transistor as seen in the patent US3356858A by Wanlass (1967). The left side shows an overview of the wafer, while the right side shows the cross section.

current can flow from drain to source. If the potential difference increases, the current flowing through the transistor will increase accordingly.

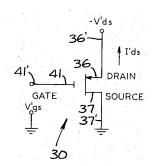

Figure 2: Schematic drawing of a PMOS transistor as seen in the patent US3356858A by Wanlass (1967) with the terminals wired to the according voltage sources.

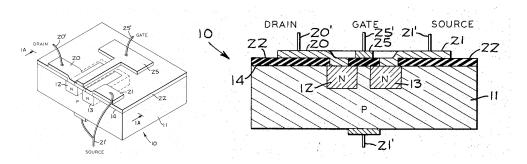

Looking at an NMOS transistor, the doping of the substrate and therefore the doping of the connections is switched, see figure 3, resulting in an opposite reaction. For gate-source voltages below a threshold, the current from drain to source is basically zero. When increasing the potential difference, the resulting current also increases.

Figure 3: Layout drawing of an NMOS transistor as seen in the patent US3356858A by Wanlass (1967). The left side shows an overview of the wafer, while the right side shows the cross section.

For deeper explanations of the different functions and operation options of the transistors one can refer to different kinds of standard electronic teaching materials. Suggested readings that have already been mentioned would be (Razavi, 2013) and (Phillip E. Allen, 1987) as well as (Jaeger and Blalock, 2011). After briefly introducing the two different MOS transistors, a short explanation, why it can be beneficial to have PMOS and NMOS transistors on the same silicon wafer, will be given. One use case utilizing both transistor types is the inverter. Here an NMOS and a PMOS are wired in parallel to an input, with the PMOS drain connecting to VDD and the NMOS source connecting to GND. This configuration essentially creates an output of VDD, if the input is set to GND and vice versa.

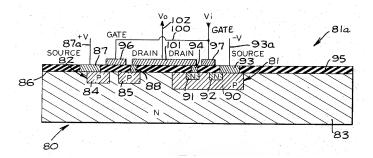

However, creating both of these transistor types in the same silicon is not as easy as it may sound. When looking at the doping type of the substrate, it's clearly visible that the PMOS transistor is sitting in n-doped silicon, while the NMOS transistor is sitting in a p-doped substrate. The idea of CMOS is to combine these substrates by creating a p-well inside the n-doped substrate, which allows placing the NMOS next to the PMOS. In most common processes used today the doping is reversed, resulting in the creation of an n-well inside a p-doped silicon wafer. But whatever the difference in doping, today's processes are based on the patent presented by Wanlass (1967) introducing the CMOS technology. A sketch of his idea is presented in figure 4.

Figure 4: Cross section of a CMOS layout with an NMOS and a PMOS on the same wafer, as seen in the patent US3356858A by Wanlass (1967). The shown configuration represents an inverter.

### 2.2 The BrainScaleS-2 System

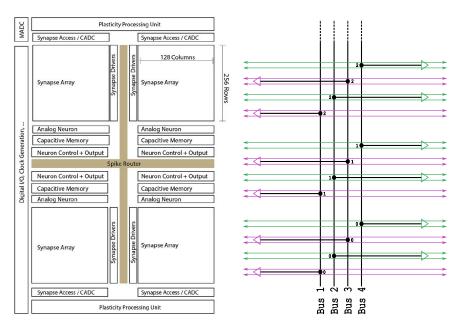

As mentioned in the introduction, this work involves the creation of a scalable synapse driver array for use in the BrainScaleS-2 (BSS-2) neuromorphic system. The term neuromorphic describes hardware used to mimic nerve structures, especially those of the human brain (Billaudelle, 2017). One of these neuromorphic systems is the BSS-2 system created and maintained by the Electronic Vision(s) group at the University of Heidelberg. The research group introduced their first mixed-signal neuromorphic chip, Spikey, which was based on a 180nm CMOS technology, with the work by Schemmel et al. (2006). Back then the system contained 384 neurons and 256 synapses (Pfeil et al., 2013). The latest system is the already mentioned BSS-2 system, which is manufactured in a 65nm process, containing 512 neurons with 256 synapses per neuron (Pehle et al., 2022). It is based on an analog model of physically implemented neurons and synapses that, when combined, result in an analog neuromorphic accelerator which uses a continuous-time to emulate the spike-based dynamics of a neural network. Interestingly, while the number of synapses and neurons falls short compared to the real world example, the time scales in this system are up to a thousand times shorter than the real world comparison, resulting in a high acceleration in time compared to the biological counterparts (Schemmel et al., 2020). A single BrainScaleS-2 core includes the full custom analog part holding a synaptic crossbar combined with neuron circuits, analog parameter storage, two digital control- and plasticity-processors, and an event routing network responsible for spike communication. A schematic floorplan is shown in figure 5. Here you can see that the design was split into four quadrants containing 256 by 128 synapses each.

Figure 5: The left side shows a schematic floorplan of the BrainScaleS-2 system as described in the work of Pehle et al. (2022), while the right side shows a representation of a synapse driver schematic. The bus lines are depicted in black, connecting the drivers shown as triangles. The driver outputs as well as the drivers are colored green and pink depending on the position (left or right) of the drivers. The right picture can be understood as zoomed in on the synapse driver on the left.

This floorplan further shows synapse drivers, which are used as the interface between the event routing bus and the analog core of the chip. In other words, the drivers take the inputs from the digital part and feed them into the analog part of the chip. Here the digital event handling logic is used to inject these events into different decoders, acting as a custom CMOS-level bus and distributing the spike events across the array of synapse drivers. To achieve this, the synapse drivers derive timing signals for the synapse circuits and drive them across the synaptic rows using a 6-bit synapse address as well as an enable signal (Grübl et al., 2020). Four of these 6-bit busses are used to activate the corresponding synapse drivers. Here each synapse driver manages two synaptic rows per side resulting in four synapse rows per driver (Billaudelle, 2017, p. 12). On focusing only on the top half of the chip, one can draw a simplified connection plan of the synapse drivers as shown in figure 5. This is possible since the lower half of the chip is essentially a mirror image of the upper half.

Furthermore, the synapse drivers also implement the short-term plasticity model (STP), following the pre-synaptic implementation approach as tested in the previous chip generations (Grübl et al., 2020). However, with the aim of this work in mind, it can be concluded that the detailed implementation of this model is not relevant. Therefore no further information about the STP implementation is given.

A closer look at the floorplan of the BSS-2 system shows that the system is quite complex, and therefore also quite space consuming, resulting in the need for a large die-area. This is not a problem in itself, but it does mean that each individual chip, especially when considering smaller improvements from one generation to the next, is quite expensive to manufacture. One of the reasons is the direct relation between cost and chip area used. While these large die-area chips are indispensable in some instances, for example when scaling up systems, most of the time it is possible to test changes of smaller components individually. When testing the individual components, the production of small scale chips or so called mini asics, keeping costs for each iteration at a minimum, would be optimal. Coming back to the BrainScaleS-2 system, the question on how to achieve these small scale chips arises. Here the idea was to find a way how the design could be shrunken down for testing purposes. Based on this, the objective of the work set out in this thesis was to be able to scale down the system in number of synapses and neurons. To achieve this, the first three main components that have to become scalable in design are the synapse driver array, the synapse array and the neuron array. Out of these components the synapse driver array is dealing with different connections the most. This is the reason why it was chosen to serve as an example and possibility check for creating a scalable neuromorphic design using PCells.

#### 2.3 VLSI design flow

To understand what is meant by the term PCell and why it is desirable to use them in circuit design one first has to understand the design process behind VLSI systems. The term Very-Large-Scale Integrated Circuit (VLSI) is used to describe the ever growing integrated circuits (ICs) on a single silicon wafer. These integrated circuits or ICs describe the realization of a large number of components, mainly transistors, on one wafer with the main benefit that the devices share quite similar characteristics due to the equal manufacturing conditions. This ability to create devices with nearly matching characteristics has resulted in the development of special circuit techniques taking advantage of these similarities (Jaeger and Blalock, 2011, pp. 1046–1049).

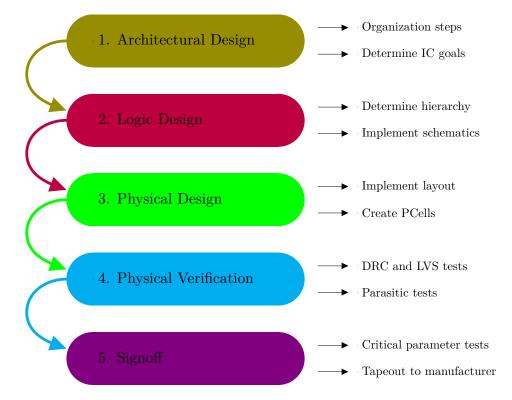

The design process of these integrated circuits is based on many different steps. While there is no perfect design flow used by everyone, the key steps of these flows will still be quite similar. To showcase a possible design flow, an introduction into 5 crucial steps will be given. The naming of these steps can be subject to changes depending on the process in question. In terms of naming and step order, this work is based on the workflow presented by Cadence<sup>®</sup>(Cadence Design Systems, 2023b) as a result of the later use of their design tools.

Following these recommended design steps, all processes should start with an "architectural design" part. This means thinking about what exactly is to be achieved. Furthermore, all the organizational steps, such as the expected costs and use cases of the IC, are taken into account. After the requirements as well as the boundaries regarding a specific IC are fixed, the "logic design" begins. Here one takes the requirements from the "architectural design" and tries to break them into increasingly smaller blocks. This helps to create a hierarchical idea of the aspired design. When all small building blocks are determined, either preexisting similar blocks are used and modified when possible, or new ones, solving the design challenges are created. This process mainly works on the schematics of a design. After finishing the schematics of the desired IC, it is advised to perform the first simulation tests verifying that the idea and function of the desired circuit have been achieved. If these tests prove successful, the next step is to create the "physical design" of the IC. In this step, all the small building blocks from the schematics have to be implemented in the layout of a chip. Here one has to determine the location, size and shape of all the different modules, effectively drawing the masks used for producing the wafers. It is advisable to re-verify each small building block against its schematic counterpart to ensure that no mistakes are made. With increasingly higher hierarchical levels it also becomes increasingly difficult to find and extract errors.

Combining this "physical design" step with the hierarchical design of the chip also provides the first strong argument for creating scalable and reusable design parts. One option to achieve this would be to copy the small design parts each time they shall be used and then modify them according to the specific needs. But as one can imagine, over a longer period this becomes space and time consuming, being the reason why this option is not really desirable. Another reason why this option is not optimal is the fact that the results are not scalable without a considerable amount of work. For example, if one wanted to double the size of an old design, one would have to double everything by hand which is a quite time consuming process. One option to resolve these issues are so called PCells, or Parameterized Cells, which can be created using Cadence<sup>®</sup> Virtuoso<sup>®</sup>. These can then be used as the small building blocks of the design. Here it is also possible to incorporate these small parametrizable cells into bigger Parameterized Cells, which finally can result in a fully scalable and modifiable IC design.

Coming back to the last two steps of the design process, the step after completing the "physical design" of the IC is to verify the created designs. This process is also called "physical verification". Here the physical design on the masks for the wafer is primarily

tested both for design rule violations, assuring that the design is manufacturable, as well as for differences between the layout and the schematics from step two. If these tests are successful, simulations of the actual layout, taking into account real life effects like crosstalk and resistances, are carried out. Most of the time the design is also tested at the edges of the manufacturing variations, thereby checking the stability of the design. With all the desired tests passed, the final step of the process is the "signoff". In this step the most critical parameters are verified again, including timings, power consumptions and signal strengths. If all necessary steps are taken, the circuit will be sent to a manufacturer, where there will be some final testing, followed by the manufacturing of the wafers. This design flow is also modeled in a flowchart shown in figure 6.

Figure 6: Design flow chart for ICs inspired by the explanation from Cadence Design Systems (2023b) and the work by Patni (2021). The design flow chart shows the different steps of the process in the colored boxes with short explanations of these steps on the right.

### 2.4 PCells

As motivated in the previous paragraphs it can be quite desirable to implement scalable and reusable designs when creating ICs. Here the PCell from Cadence<sup>®</sup> Virtuoso<sup>®</sup>, as mentioned above, is a powerful tool to achieve this flexibility. In short, a PCell is a layout, schematic or symbol of a cell used in Virtuoso<sup>®</sup>. The distinctive feature of these cells is that they have parameters attached to them, allowing for customized appearances when inserted into a design. One of the smallest examples for a PCell would be a transistor, most of the times supplied as part of the process design kit belonging to a CMOS technology. Here some cell parameters would include the length and the width of the gate, as well as for example the number of fingers or multipliers a transistor holds. When changing these parameters for instances inside a design, the model of the transistor changes accordingly. The same holds for the use of the PCell in a layout. Here a parameter change results in physical change of the drawn transistor. Using the example of the transistor one can easily show that it is possible to use the same basic design, in this case the transistor, in many different implementations. Cadence<sup>®</sup> allows the user to create such PCells on their own, thereby providing quite a powerful tool for the purpose of IC design.

Working with these PCells, Virtuoso<sup>®</sup> provides two options on how to create them. One can either create the PCells graphically, using the options inside the PCell menu, or textually, using the programming language of Cadence<sup>®</sup>, SKILL (Cadence Design Systems, 2004). While it might be appealing to create the PCell graphically, the complexity of the PCells created that way is quite limited. When creating the PCells using SKILL, the options, and therefore the possible complexity of these PCells, are nearly unlimited. This is a direct result of the fact that everything the design software Virtuoso<sup>®</sup> is capable of can also be achieved using the correct SKILL commands. This for example is reflected in the parameters, which can be used quite freely, resulting in very little to no boundaries when creating PCells for own designs. Because of the greater flexibility, and the option to create schematic and symbol PCells, the method used to create the cells shown in this work is using SKILL.

In addition to scalability and reusability, PCells carry the following advantages when used in design processes. They are able to save disk space by using only paths back to the original cell instead of saving all cells individually, they speed up the layout data by eliminating the need for duplicated parts, their designs can be maintained way easier because all changes can be done in the parent cell and finally, they allow for much easier changes in the designs by using parameters instead of having to go through a stack of layout layers (Cadence Design Systems, 2004).

#### 2.5 Simulation and parasitic extraction

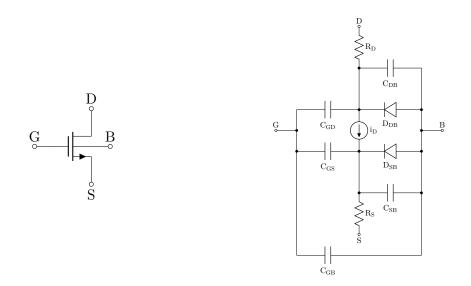

When looking at the design flow of ICs as explained above, it is visible that in addition to actually creating the circuits, a big part of designing is simulating and testing the different designs at varying design stages. When working with schematics, this can be achieved by creating a so called netlist of the drawn circuits. These netlists are used for simulating the designs by applying different component models or calculating the different behaviors according to basic electronic equations. Most of the time the software used to generate these simulations is based on SPICE (Simulation Program with Integrated Circuit Emphasis). SPICE in its core is an open source circuit describing language used for simulations of complex circuits by replacing the used components with different models. When simulating the circuit all components, as well as their connections, get translated into a netlist which itself is used to generate equations describing the circuit. These detailed equations are mostly solved numerically, with a precision that is not achievable by hand in a reasonable time (Jaeger and Blalock, 2011, p. 167). To get an understanding of the complexity of these component models the level-1 SPICE model of an NMOS is represented in figure 7.

Figure 7: The left side shows the symbol of an NMOS transistor as used in modern processes. The right side shows the Level 1 SPICE representation of this NMOS as seen in the book by Jaeger and Blalock (2011, p. 167) or Phillip E. Allen (1987, p. 104)

Here it becomes clear that even for a "simple" MOSFET the number of equations describing the whole system can become a nuisance.

In addition, these netlists used for simulations can be extracted from the layout using the GDSII data and for example the tool Calibre. Using this functionality it is now possible to compare these two netlits of layout and schematic against each other. The process of comparing these two is also known as layout versus schematics (LVS). Here it is possible to spot differences or errors in the designs, which may have been missed when creating the layout. Naturally, if it is possible to create a netlist from the layout, it is also possible to use this netlist for simulations. Interestingly the simulation options for the layout exceed the ones of the schematics. The reason for this are the so called parasitic extractions of the layout generating a netlist not only containing the connections, but also the physical effects, like crosstalk or line capacitance, that the shapes drawn for the wafer masks will likely have on each other. These extractions are needed, because the extended use of lower resistive conductors on chips combined with the increasingly tight on chip timing requirements, resulted in an increased visibility of unwanted effects (Kao et al., 2001). To calculate these parasitic effects different methods of extracting can be used. Providing a better understanding of these extractions, some of the widely used models will be introduced in the following paragraphs.

When talking about these parasitic extractions the main contributors are the resistance, the capacitance and the inductance among the interconnected wires. Of these, the calculation of the capacitance is playing the most significant role. To extract these parasitic capacitances, two main processes, the field solver method and the pattern-matching method (Ma et al., 2023), are used. The field solver works by directly stimulating the electrostatic field and saving the results, therefore achieving highest accuracy. As always, this accuracy comes with the penalty of quickly rising computing times as well as massive memory consumption. It therefore is only suitable for smaller designs or isolated design parts (Yu, Song, and Yang, 2021).

The method based on pattern-matching is the one used for working with circuits of increasing size or even full chip extractions. It also is the foundation of most industry adopted extraction tools like Calibre by Siemens. This method works by combining three steps of extraction, of which only one is executed on a per design basis. These three steps are: first the generation of different wire patterns covering a wide range of possible designs, second the calculation of capacitance models for these structures, and third an extraction of the actual circuit layout, from which the found wire structures are mapped to the pre calculated models. The advantage of these pre calculated models is that they only have to be calculated once for each process technology and therefore are independent of the actual design. This means that they are supplied with the rest of the technology files. These pattern capacitance libraries are created using a field solver, as mentioned above, and can consist of several thousand structure patterns, see the work of Yu, Song, and Yang (2021).

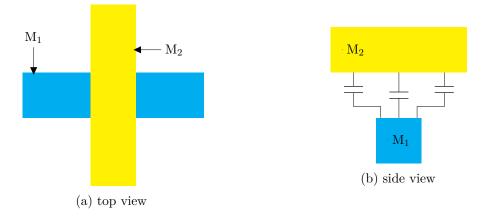

Interestingly there are different models for capacitance field solvers, mainly differing in the dimensional complexity of the extractions. During the ongoing developments of these extraction models, they evolved from taking into account the 1-D effects, over 2-D and 2.5-D to considering 3-D effects. Each of these model revisions surpassed the lower dimension ones in the accomplished accuracy. While the 1-D extraction only accounted for the area and perimeter of interconnected geometries, combined with an average environment of these wires, the 2-D extraction included capacitive effects in relations between wires of the same lateral metal layer. Because it is not as trivial as it seems to extend these 2-D extractors into the third dimension, a 2.5-D solver has been developed (Kao et al., 2001). The 2.5-D extraction works by orthogonally combining two 2-D extractions. To achieve this, the layout is first extracted horizontally and then vertically. Combining these two extractions allows for the modeling of most 3-D effects. Examples of how these two views might look like are shown in figure 8.

Nowadays mostly 3-D solvers are used for the extractions. While there are the traditional deterministic methods, like the boundary element method (BEM), or the finite difference method (FDM), numerically solving the maxwell equations and describing all the different metal layers in three dimensions (SimTech, 2023), current research tries to reduce the computation time and power as well as the memory space needed for these extractions. One attempt on completing this task is the implementation of a floating random walk to generate the dependencies, as shown in Yu, Song, and Yang (2021). This work shows

Figure 8: Schematic depiction of 2.5-D modeling for two metal lines in different layers. Inspired by the work from Kao et al., 2001

the importance of speeding up the extraction and simulation process, without having to reduce the complexity of the designs. Moreover, this gives a foundation for the second goal of this work, trying to decrease the simulation times needed for big repetitive designs. This shall be achieved by configuring the synapse driver array as a PCell in a way that it becomes possible to replace most of the repeating design parts with extracted models, essentially speeding up the simulations, while also keeping the accuracy of the simulations at a reasonable error.

# 3 Methods

In the process of creating and simulating the PCell of the synapse driver array for the BrainScaleS-2 system different tools have been used. The following few paragraphs are going to give a short introduction explaining the tools used as well as their purpose.

### 3.1 Cadence<sup>®</sup> Virtuoso<sup>®</sup>

Most of the work regarding this thesis was done via the Cadence<sup>®</sup> Virtuoso<sup>®</sup> software. Virtuoso<sup>®</sup> is mainly used to create custom IC designs in schematic and layout. The software also includes a tool for analysis and circuit simulation. The Virtuoso<sup>®</sup> studio software is the world leader regarding circuit and chip design. Regarding the software Cadence<sup>®</sup> is cooperating with chip manufacturing companies like TSMC and UMC. The simulation solution, Spectre, which is integrated into Virtuoso<sup>®</sup> is capable of performing both analog and digital simulations, as well as mixed signal simulations. While it is based on SPICE, Cadence<sup>®</sup> claims that the simulation speed is up to ten times faster than ordinary SPICE simulations (Cadence Design Systems, 2023a).

# 3.2 Calibre

The Calibre design solutions portfolio is a piece of software that is maintained by Siemens and can be used in the IC sign off verification and optimization process. In the context of this work Calibre was used to perform the layout versus schematic (LVS) and Design Rule Checks (DRC), as well as to extract the parasitics of the designs using the parasitic extraction (PEX) tool. The checks were executed using the allowed integration of third party software into the Virtuoso<sup>®</sup> design suite by running the Calibre verification tools directly from the cellviews graphic interface.

# 3.3 SKILL

As mentioned before, the PCells in this work have been created using the programming language SKILL. SKILL as a programming language is a dialect based on a dynamic scoped Lisp interpreter. It was developed to be used as an extension language for CAD systems with the goal of providing tools and design control for the user on a level unachievable otherwise. Because it was developed with the user in mind, the actual parser is quite less restrictive than usual Lisp. This simplified parser for example allows a far more C-like syntax (Barnes, 1990). Nowadays SKILL is tightly integrated into the Virtuoso<sup>®</sup> design suite, allowing for full control over the designs and software by only using the command line.

# 4 Creation of synapse driver and address decoder PCells

After introducing the main topics of this thesis, the following chapters will deal with the parametrization process as well as the challenges and solutions that arose during the process of creating a parametrized synapse driver array. Here the different steps and decisions will be discussed, while also giving code examples for implemented solutions. The work regarding the scalability of the synapse driver was started by taking a dive into the design blocks of the fixed array, used in the latest BSS-2 system.

# 4.1 Fixed synapse driver array

The old synapse driver array was designed and constructed following the traditional design flow as explained before. This means that it was constructed out of many different layers of instances, used in an ever growing hierarchy. Specifically, this means that all the different parts of the design, such as the bus, the drivers or the SRAM decoder were all created and placed by hand. Further this layout was extended using a custom SKILL script creating the decoding via patterns on top of the instances, as well as using a second custom SKILL script, creating the labels used for net naming and simulation on top of the layout. In some places, where the features of the array have been expanded over time, metal shapes, used for those features, were drawn right on top. Starting from this, the first task in changing this array into a scalable PCell was trying to replace the via script, creating the decoding pattern in the incoming bus lines, again see figure 5, with a changeable decoder that, making use of its flexibility, hopefully will be used in many different upcoming designs. The process of creating this decoder, ultimately achieving the desired functionality, is highlighted in the following paragraphs.

### 4.2 Address decoder

Combining the argument of trying to get rid of custom built solutions for each new design with the almost infinite possibilities provided when creating PCells, the first decision that had to be made during the creation process of this changeable decoder design was the parameter selection. Here the parameters one would likely use in the future as well as their implementation had to be chosen.

#### 4.2.1 Parameters

#### Addressbits

Deciding on the parameters, the first one to be implemented was the number of address bits for the input bus. This parameter takes the form of an integer, allowing to choose any whole number larger than zero. Implementing this parameter was fairly straightforward, because the usage of an integer meant that it could just be passed into the design. Setting this parameter defines the number of address lines, hence the naming, while in the same step also defining the number of routing outputs.

#### **Custom Length and Maximum Bit**

To accompany this parameter two further parameters allowing for a smaller number of outputs have been added. The reason for this was that sometimes one has an input of a certain number "a" of address bits, but does not need all  $2^{a}$  outputs. If this parameter is not used, the number of outputs is determined automatically. The first parameter added allows a reduction in output numbers and therefore is called custom length. It is implemented as a boolean with the default false (nil). When set to true (t), the second parameter is revealed. This normally hidden parameter is called maximum bit and is also implemented as an integer. When used with a value smaller than  $2^{a}$ , the PCell only calculates, and therefore creates, routing outputs up to the specified number.

During the process of creating these two parameters two challenges arose. The first one was faced while creating parameters that normally are hidden and uneditable, but turn into "real" parameters, depending on the values of other parameters. Here the first idea was to use a callback attached to the custom length parameter, changing the value of the display option from the maximum bit parameter. Unfortunately, that did not work, which is the reason why the current implementation is making use of the ?display option directly attached to the maximum bit parameter. The code used to implement this functionality is shown below.

```

cdfCreateParam( cdfId

?name "maxBit"

?type "int"

?prompt "Maximum Bit"

?defValue 2**8

?display "cdfgData~>customlength~>value == t"

?editable "cdfgData~>customlength~>value == t"

)

```

The second problem that had to be solved was that in SKILL nil is used for the boolean false as well as for undefined values. This resulted in a rather strange behavior where, if the default of a parameter is set to nil, the parameter still gets created and is accessible, but unfortunately, the changing of the boolean value is not registered internally. To derive the type of the parameter, a statement defining which nil was meant, by stating a "boolean" before using nil, has been implemented. Looking at the decoder code, this can, for example, be seen in the parameter defining part at the beginning of each view type. (Code 6)

#### **Decoding and Custom Decoder List**

Following the parameter creation, the next parameter implemented is the decoding. Here one can choose between a "standard" backward or forward decoding as shown for example in figure 19. Further a custom decoding option was added, which stays hidden, using the same method as the parameter code shown above in Code 1. In this custom decoding one can enter an arbitrary decoding represented by a list. An example of this, containing 3 address bits, would be (0 2 4 8 1 3 5 7), resulting in a separation of even and odd addresses. In the actual code this is implemented by calculating the bitwise representation of each routing output, following the given list, and then using an if query to decide which input the output should be connected to. This will be explained in more detail in the layout section later on. Looking only at the schematic and symbol of the decoder these parameters are the ones actually used inside the PCell. However, for creating the layout of the decoder further parameters have been created.

#### Routing Layer, Address Layer and Inverse Address Layer

One big flexibility the design has to account for in the layout are the different metal layers one can and has to choose from when drawing the conducting metal lines. To achieve this flexibility three further parameters were added into the design. These parameters allow the user to choose between different metal options for the routing layer, as well as for the address and inverse address layer individually. Here one really nice design feature is that

Code 1: Code used for defining the Maximum Bit parameter with the display and editable option.

the options presented to the user change depending on prior choices. In explicit terms this means that when for example "metal 3" is chosen for the routing layer, the address and inverse address lines only can be drawn on the layers "metal 2" or "metal 4". One of the reasons why this restriction was implemented is that in most use cases the broader option overcomplicates things by allowing the user to create vias that can connect through more than one hierarchical metal layer at once. Keeping this in mind the restriction can provide a bit of support for the user implementing this decoder into a new design. To achieve these dynamic choices, a callback in the definition of these parameters is used. From there the options of the other two parameters are altered by creating a list, depending on the own settings. An example of this code, in this case showing the callback from the routing layer parameter, looks as follows.

```

cdfCreateParam(cdfId

```

```

?name "routingLayer"

?type "cyclic"

?prompt "Routing Layer"

?defValue ""

?choices list("" "M1" "M2" "M3" "M4" "M5" "M6" "M7" "M8" "M9")

?callback "

layeroptions = list(\"\")

layeroptions = append(layeroptions list(strcat(\"M\" sprintf(nil \"%d\"

$\rightarrow atoi(substring(cdfgData->routingLayer~>value 2))-1))))

layeroptions = append(layeroptions list(strcat(\"M\" sprintf(nil \"%d\"

$\rightarrow atoi(substring(cdfgData->routingLayer~>value 2))-1))))

cdfgData~>addressLayer~>value = \"\"

cdfgData~>addressLayer~>value = \"\"

cdfgData~>invaddressLayer~>choices = layeroptions

"

```

```

)

```

```

Code 2: Code used for defining the Routing Layer parameter with the callback option

used to change the values of the Address Layer and Inverse Address Layer

parameters.

```

### Metalwidth

Another parameter used only inside the layout of the decoder is the width of the drawn metal lines. Here the parameter is implemented as a string, allowing the user to input values like for example "0.18u". This parameter is used for the width of the address lines, as well as for the routing lines. Here it would be possible to argue that it may be beneficial to add a separate width for each type of metal, nevertheless, the decision was taken to use only one metal width allowing easier via placement, as well as creating a simpler interface. The other thing that automatically changes with the metal width is the position and the number of placed vias. This enables a good connection between the address and routing lines by increasing the number of placed vias according to the cross section.

#### Address Position, Inverse Address Position, Routing Position and Routing Pitch

Another important parameter added for creating the metal shapes is the position of the lines in respect to each other. To achieve a flexibility in the changeable pitch between the lines, four parameters, all implemented as a string, are used. The four parameters that are used are called "Address Position", "Inverse Address Position", "Routing Position", and "Routing Pitch". The first three are used to calculate the exact positions on which the respective metal lines will be centered, while the routing pitch simply is the distance from the first row of bundled routing outputs to the second row.

In each of these parameters, the user has to specify a simple arithmetic expression. Fulfilling the purpose of generating the positions, the given strings are evaluated making use of increasing variables, for the address line "b", and for the routing line "i". This allows the user to create a wide range of arrangements of pitches, for example by using if statements for the individual positions, while also maintaining a quite simple interface for creating "standard" pitches. Examples for these possible pitches are shown in figure 9.

Creating these string interpreters, again different challenges had to be overcome. The biggest of these challenges was trying to prevent the possibility for malicious attacks exploiting the strings when evaluated with an evalstring(). When only executing an evalstring() on the parameter string, it is possible to gain full access to the underlying system by exploiting the parameter textbox as a command line. To create a defence against the possibility of exploiting this function, an implementation of the Automate Expression language (AEL) interpreter from SKILL has been tested.

However, the limited application potential combined with the compatibility problems between the AEL functions and PCells (Cadence Design Systems, 2004), resulted in the decision to not use the AEL interpreter. Problematically, this again led back to the use of a simple evalstring(). To solve this problem, a regular expression checker was added to the code. Now it is possible to expand the allowed functions or symbols in the parameter as needed, while still assuring that an attack exploiting this evalstring() is quite unlikely. The current implementation works by checking the string with a custom SKILL function given below.

```

procedure( allowedString(input)

let((var res)

rexCompile("mod")

var = rexReplace(input "000" 0)

rexCompile("if")

var = rexReplace(var "00" 0)

rexCompile("then")

var = rexReplace(var "0000" 0)

rexCompile("nth")

var = rexReplace(var "000" 0)

rexCompile("[^0-9\\*\\.\\+\\/\\ \\(\\)ibunp\\<\\>\\=\\-]\'")

if( rexExecute(var) == nil then

res = t

else

res = nil

)

res

)

)

```

Code 3: Code defining a function that is used to check an inserted string for words and characters that are allowed for use in the definition of the layer positions. The function returns t or nil, depending on the outcome of the check.

This code works by taking a given string and mapping the allowed functions exactly onto the string. Then these allowed functions are replaced with "0"s, ultimately removing the allowed functions from checking. This is achieved by making use of the rexReplace() function. Once the allowed functions are replaced, the string is checked for the allowed singular characters. In the code example above the allowed singular characters, containing mathematical symbols such as \* or +, as well as some single letters used as units, like u and n, or as the variables b and i, can be seen. Further the few allowed functions mod(), if(), then() and nth() can be found.

If the string inserted to the parameter does not contain any illicit characters or functions, the check function returns a boolean t. Otherwise it returns nil. The function checking the inserted code is called with a callback attached to the parameter resulting in an execution each time the value is changed and most importantly before the string is passed into the different views for evaluation. If nil is returned, the parameter will not be forwarded and instead an error will be presented inside the text field for the user. The code used in the callback looks like this.

```

?callback "

if(allowedString(cdfgData~>routingSpace~>value) == nil then

cdfgData~>routingSpace~>value = \"not allowed function detected\"

)

"

```

Code 4: Code defining the callback of the parameters used for metal positions. The allowedString() function shown in Code 3 is executed and the string is parsed according to the return.

To further present the capabilities of this string interpreter some functions generating different metal arrangements will be shown. This showcase will include some simple functions like b\*1u+0.5u for address placements, as well as some rather complex functions like nth(i '(0 1 2 3 4 10 9 8))\*0.3u for the routing lines. The functions used for this showcase, as well as the created layout placements, can be seen in figure 9. Here all metal widths stay fixed at 0.24µm.

#### Address Lines, Draw, and Inverse Address Lines, Draw

Allowing a reproduction of the via script previously used, the option to turn off the drawing of the metal lines has been added. Here the user can deactivate the drawing of the address, inverse address and routing lines individually, ultimately creating a cell that only places the vias at the positions where the metal lines would cross. At first glance this might seem like an unnecessary option to add, but when creating cells with repeating designs it can be the case that the metal lines of the routing are already drawn in the cell of a lower hierarchy. If this is the case, the metal lines already are part of the design and do not have to be redrawn in this higher hierarchy.

#### Help

To guide the user through the process of setting up the via matrix, especially in the light of the more advanced features, a help button was added as a further parameter. When pressed, this button opens a file containing an explanation for each parameter, as well as some examples on how to use them. To achieve this functionality, the file containing these explanations has to be accessible to every user that implemented the code in their library. To ensure this, a way to create the file directly through SKILL was implemented. Here the functions outport1 = outfile("path"), fprintf(outport1 "content"), drain(outport1) and close(outport1) have been used.

Combining all these parameters, the input mask created for this PCell can be seen in figure 10.

This input mask concludes the main parameter creation process and also provides an overview of the parameters and functionalities created. While there might be special cases in which the parameters created here may not be sufficient enough, the further course of

(a) Address Position: b  $\cdot$  1u, Inverse Address Position: b  $\cdot$  1u + 0.5u, Routing Position: i  $\cdot$  0.5u, Routing Pitch: 5u

(b) Address Position: b·2u+mod(b+1 2)·1u, Inverse Address Position: b·2u+mod(b+1 2)·1u+0.5u, Routing Position: i · 0.5u, Routing Pitch: 5u

(c) Address Position: b · 1u, Inverse Address Position: b · 1u + 0.5u, Routing Position: nth(i '(0 1 2 3 4 10 9 8)) · 0.3u, Routing Pitch: 5u

| b-Ø | if(mod( |      | ) | - ø | ther |     | -   | nth(mod(                |    | 3) '(5        | 'u 1Øu) | )) if(mod | (10 | 2) • |     | 1 th  | en t | - nth(m  | od(1 | 8 3) | '(8L |               |   | ) b  |     |

|-----|---------|------|---|-----|------|-----|-----|-------------------------|----|---------------|---------|-----------|-----|------|-----|-------|------|----------|------|------|------|---------------|---|------|-----|

| b=Ø | if(mod( | 9 2) |   | ø   | chen | b   |     | th(mod(9                | 3) | '(5u          |         | if(mod(9  | 2)  |      |     | then  | b =  | nth(mod( | 9-3) | '(8u |      | 9u)))         | Ь |      | Bu  |

| b=Ø | if(mod( | 8-2) |   | ø   | then | b : |     | th(mod(8                | 3) | '(5u          |         | if(mod(8  | 2)  |      |     | then  | b =  | nth(mod( | 8-3) | '(8u |      | 9u)))         | b |      | 1Øu |

| b=Ø | if(mod( | 7 2) |   | ø   | then | ы   |     | th(mod(7                | 3) | '(5u          |         | if(mod(7  | 2)  |      |     | then  | b =  | nth(mod( | 7-3) | '(8u |      | 9u)))         | ь |      | 6u  |

| b=Ø | if(mod( | 6-2) |   | ø   | then | b : |     | th(mod(6                | 3) | '(5u          | 1Øu)))  | if(mod(6  | 2)  |      |     | then  | b =  | nth(mod( | 6-3) | '(8u |      | 9u)))         | b |      |     |

| b-Ø | if(mod( | 5 2) |   | ø   | chen | b i |     | th(mod(5                | 3) | '(5u          |         | if(mod(5  | 2)  |      |     | then  | b    | nth(mod( | 53)  | '(8u |      | 9u <b>)))</b> | b |      | 9u  |

| b=Ø | if(mod( | 4 2) |   | ø   | then | b   | = n | th(mod(4                | 3) | '(5u          |         | if(mod(4  | 2)  |      |     | then  | b -  | nth(mod( | 43)  | '(8u |      | 9u <b>)))</b> | Ь |      |     |

| b=Ø | if(mod( | 3 2) |   | ø   | then | Ь   |     | th(mod(3                | 3) | '(5u          |         | if(mod(3  | 2)  |      |     | then  | b =  | nth(mod( | 3-3) | '(8u |      | 9u <b>)))</b> | Ь |      | 8u  |

| b=Ø | if(mod( | 2 2) |   | ø   | then | ь   |     | th(mod <mark>(</mark> 2 | 3) | ' <b>(</b> 5u |         | if(mod(2  | 2)  |      |     | then  | b =  | nth(mod( | 2 3) | '(8u |      | 9u)))         | b |      | 1Øu |

| b=Ø | if(mod( | 1 2) |   | ø   | :hen | ы   |     | th(mod(1                | 3) | '(5u          |         | if(mod(1  | 2)  |      | 1 t | hen b | -    | nth(mod( | 3)   | '(8u | 6u - | 9u)))         |   | -> ) |     |

| b=Ø | if(mod( | Ø 2) |   | ø   | chen | b : | = n | th(mod(Ø                | 3) | '(5u          |         | if(mod(Ø  | 2)  |      |     | then  | b =  | nth(mod( | ø 3) | '(8u |      | 9u <b>)))</b> | ь |      |     |

- (d) Address Position:  $b \cdot 1u$ , Inverse Address Position:  $b \cdot 1u + 0.5u$ , Routing Position:  $i \cdot 0.5u$ , Routing Pitch: b = 0 if(mod(i 2) == 0 then b = nth(mod(i 3) (5u 7u 10u))) if(mod(i 2) == 1 then b = nth(mod(i 3) (8u 6u 9u))) b

- Figure 9: The layout of the decoder PCell showcasing some different possibilities in creating and placing the metal lines. The parameters used for generating the depicted layouts can be seen in each shown subfigure.

|            | Ad                 | d Instance X                               |  |  |  |  |  |  |  |  |  |  |

|------------|--------------------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Library    | examplelib         | Browse                                     |  |  |  |  |  |  |  |  |  |  |

| Cell       | viaplacer          | <b></b>                                    |  |  |  |  |  |  |  |  |  |  |

| View       | symbol             |                                            |  |  |  |  |  |  |  |  |  |  |

| Names      |                    | Pcell                                      |  |  |  |  |  |  |  |  |  |  |

| 🗹 Add Wi   | Add Wire Stubs at: |                                            |  |  |  |  |  |  |  |  |  |  |

| Array      | Rows               | 1 Columns 1                                |  |  |  |  |  |  |  |  |  |  |

|            | Rotate             | Sideways 🚭 Upside Down                     |  |  |  |  |  |  |  |  |  |  |

| Addressbi  | ts                 | 8                                          |  |  |  |  |  |  |  |  |  |  |

| Custom Le  | ength              | ⊻                                          |  |  |  |  |  |  |  |  |  |  |

| Maximum    | Bit                | 256                                        |  |  |  |  |  |  |  |  |  |  |

| Decoding   |                    | 🔾 Forward 🔾 Backward 🧕 Custom              |  |  |  |  |  |  |  |  |  |  |

| Custom D   | ecoder List        |                                            |  |  |  |  |  |  |  |  |  |  |

| Routing La | ayer               |                                            |  |  |  |  |  |  |  |  |  |  |

| Metalwidt  | h                  |                                            |  |  |  |  |  |  |  |  |  |  |

| Address L  | ines:              | 🥑 draw 🔾 don't draw                        |  |  |  |  |  |  |  |  |  |  |

| Address    | s Layer            |                                            |  |  |  |  |  |  |  |  |  |  |

| Address    | Position           |                                            |  |  |  |  |  |  |  |  |  |  |

| Inverse A  | ddress Lines:      | 🥑 draw 🔾 don't draw                        |  |  |  |  |  |  |  |  |  |  |

| Inverse    | Address Layer      |                                            |  |  |  |  |  |  |  |  |  |  |

| Inverse    | Address Position   |                                            |  |  |  |  |  |  |  |  |  |  |

| Routing Li | nes:               | 🧕 draw 🔾 don't draw                        |  |  |  |  |  |  |  |  |  |  |

| Routing    | Position           |                                            |  |  |  |  |  |  |  |  |  |  |

| Routing    | Pitch              |                                            |  |  |  |  |  |  |  |  |  |  |

|            | HE                 | LP                                         |  |  |  |  |  |  |  |  |  |  |

|            | <u>H</u> ide       | <u>Cancel</u> <u>Defaults</u> <u>H</u> elp |  |  |  |  |  |  |  |  |  |  |

Figure 10: Input mask of the address decoder PCell that is opened when the decoder is inserted into a design in Cadence<sup>®</sup> Virtuoso<sup>®</sup>.

this work will hopefully show that using the PCell parameters as implemented all options the further work requires are sufficiently covered. Before showcasing the use of the decoder inside the synapse driver array, the creation of the decoder cellviews with their respective problems, as well as some tests and simulations, will be shown.

### 4.2.2 Cellviews

### Layout

Most of the problems that occurred during the layout creation of the decoder PCell had to do with calculating the right positions of the metal lines and placing the vias. Concerning the size of the vias it is important to stick to the design rules, on the one hand, regulating the size and spacing of the vias, while on the other hand trying to maximize the possible contact area between the metal layers. To achieve this, an **if** query was implemented, handling all metal widths below the size of 0.2  $\mu$ m. For all vias that have to be placed on wiring with a metal size wider than 0.2  $\mu$ m, the positions are calculated by a create vias function, that given a centerpoint and area fills the given area with as many vias as allowed by the design rules. This function can be found in the file defining all functions

used in different code parts, as well as in Code 8.

Another challenge was the creation of the decoding inside the layout. To solve this challenge an approach using bit conversion as mentioned before was implemented. Here the decoding, given as a list of decimals, is iteratively converted into the associated binary representation. In this process the address bit parameter is used to determine the number of bits for the binary representation. Using this binary representation the connections between the metal lines are established. In case of a 0, the output is shorted to an inverse address bit, and vice versa.

Explaining this concept an example of the number 5 decoded in a 4-bit address system is shown. When the loop calculating the output decoding reaches the 5 inside the decoding list, it will be converted into 0101. A second loop will take one character of the 0101 string for each routing line within that output. This means that the coordinates of the first routing line will be merged with the ones from the inverse address line 4, the coordinates from the second will be merged with the ones from the address line 3 and so on. Essentially this implements a simple binary representation of a given decimal decoding number by combining the according line positions into via positions.

The remaining implementation of the layout was fairly simple. One thing that was added at the end of the design process was the creation of error messages drawn directly into the design, for the cases where the address or routing positions are not specified. If either one of these position defining parameters is left empty, the decoder will not be drawn. Instead a label stating the missing parameter will be created.

#### Schematics

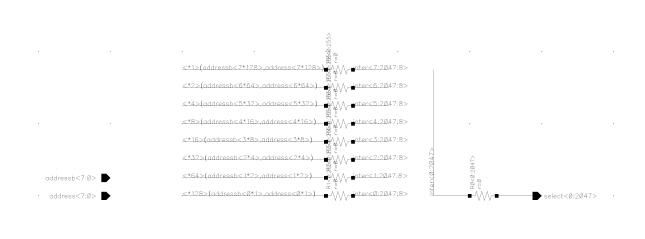

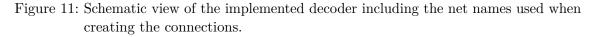

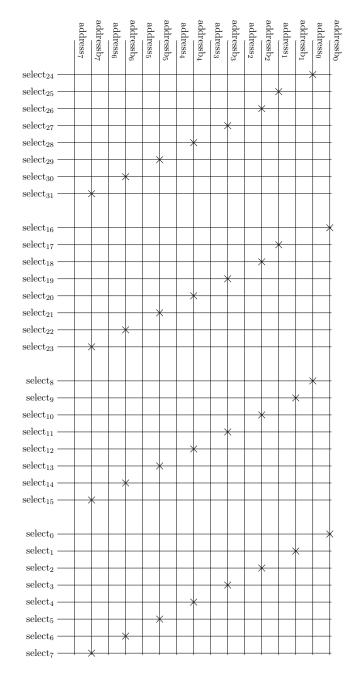

Regarding the creation of the schematics the most challenging part was implementing a working net naming creating connections between named nets using SKILL. While the order and net naming of the address inputs stay the same for all parameters, the naming of the outputs has to be adjusted based on the decoding. To achieve this, a normal forward decoding is implemented using net naming to create the desired connections. For an 8-bit decoder this is shown as an example in figure 11.

Allowing for different decodings the select net is renamed according to the desired order. So for example when the decoding is set to backward, the name is changed to select<2047:0>. Accordingly for custom decodings a large net name following the net naming conventions as well as the decoding requirements is created. To achieve these connections and finally create these nets of different names, the problem of attaching the net names to the wires had to be solved. When creating schematics by hand including nets of different names, a viable option often used to connect these is the so called patch cord "instance". Here an incoming net can be connected to an outgoing net in differing orders by stating a patch cord expression defining the connections. These patch cords are working without any problems when implemented by hand, but can not be used in PCells in a straightforward fashion. The reason for this is that patch cords are not real instances, but rather components that provide hints to the schematic editor to generate the right

underlying connections (Beckett, 2023). This meant that to create the connections between the nets, representing the decoding, the easiest solution was to name the nets in such a fashion that the decoding aimed for arose from the naming order. Generating these net names attached to the wires turned out to be the next challenge. To achieve the creation of these so called wire labels, which save the net name for connections, different options were explored. In the end three possible implementations were found. Interestingly all three implementations create labels that look exactly the same to the GUI user, with only one implementation actually working in PCells. These three implementations look like this.

```

net = dbCreateNet(cv "name")

wire = dbCreateLine(cv list("wire" "drawing") list(x1:y1 x2:y1))

dbAddFigToNet(wire net)

; Option 1

dbCreateTextDisplay(net wire list("wire" "label") t x1:y1 "lowerLeft" "RO" "stick" 0.0625 nil nil t

\low nil t)

; Option 2

schCreateWireLabel(cv wire x1:y1 "name" "lowerLeft" "RO" "stick" 0.0625 nil)

; Option 3

text = dbCreateLabel(cv '("wire" "label") x1:y1 "name" "lowerLeft" "RO" "stick" 0.0625)

text->parent = wire

```

Code 5: Different code options trying to implement the net naming in the schematic. Only option 3 is working inside PCells.

Of these implementations only the third works in combination with the PCell requirements. While the first option displays the net name as expected, all name information is lost during the check and save process of a design.

The second implementation is a direct representation of the function that is executed

when using the "add name" option for wires in the schematic cellview. This function works without problems as long as the PCell is not leaving the schematic design environment. But as soon as the PCell leaves this environment, for example when executing an LVS check, an error complaining about an unknown function appears.

Using the third option all labels and connections are created and all tested simulations complete without errors. This option is also check and save compatible, resulting in no further problems when reusing this PCell in other designs.

#### Symbol

When it comes to the creation of a symbol for this decoder some terminal names had to be matched with the ones already calculated in the schematic. Because the code creating these pin names was already created, the implementation went rather smooth without further problems. Now that a layout, a schematic and a symbol of the decoder were created, the designs were subject to testing.

#### 4.2.3 Verification of the address decoder PCell

Regarding the design tests, the first test executed has been a DRC of the layout for the created decoder placement. Here the PCell passes the test successfully. To verify that the PCell is DRC clean for more than some cherry picked values, the tests were repeated with a lot of different parameters. Tests at the parameter boundaries have been carried out as well, thereby demonstrating that for the normal use cases of a decoder the design appears to be stable and stays DRC clean.

After verifying the design rules for the layout, the next step was to execute an LVS check. Here the next problem surfaced. While the netlisting of the schematic, now containing the right net names, worked without any problems, the LVS aborted as soon as Calibre tried to generate a netlist of the layout representation. The created error reported that the netlisting did not find any instances in the layout, or in other words that the layout was empty. As a short look revealed that the layout in fact was not empty and that the metal lines had labels and pins attached, the LVS was restarted. Surprisingly the extraction aborted with the same error.

To finally fix this problem, resistors were added in front of the input of the decoder. The layout netlisting then was able to identify some instances and compared these with the ones in the schematic. Now the LVS completed without any errors and reported no differences when comparing the design views. Again different parameters as well as different decodings were tested to ensure that the layout and the schematic match. After this verification process of the PCell first with Calibre DRC and then with Calibre LVS the next step was to simulate the design using the schematics with the purpose of validating the connections.

#### 4.2.4 Simulation

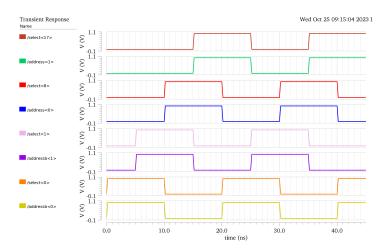

Creating the simulations which are used for checking the connections, a cellview with multiple voltage sources has been put together. After that these voltage sources were connected to some of the inputs. The rise and fall time of these voltages were defined in a way, that the voltage of each input would rise at a different point in time. Selecting different in and outputs allowed the simulation of different connections inside the decoder. One of these simulations is shown in figure 12.

Figure 12: Simulation results for digital signals passing the decoder. Nets that are related to each other are plotted next to each other.

Here the connections as shown in figure 19 can be seen. The selection of the plotted output is based on the idea of only showing the most interesting results. Therefore the first select output, which is connected to each address input, has been plotted. In this simulation the metal length differences between outputs of lower and higher numbers in the layout, which could result in for example longer signal times, could not be shown. The reason for this is that this simulation only was executed on the schematic without considering any parasitic effects.

#### 4.3 Flexible synapse driver array

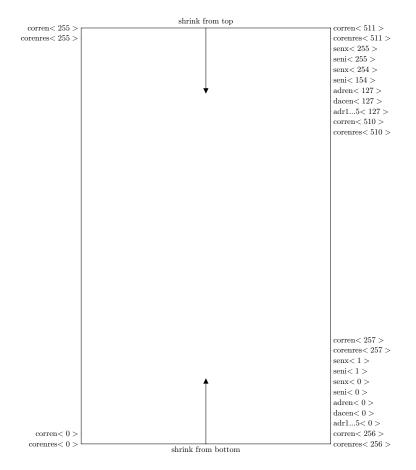

Now that a working replacement for the via pattern in the fixed synapse driver array was created, the transformation of the driver array into a flexible PCell was executed. The goal of this transformation was to allow the user to choose a number of synapse driver outputs from a list while simultaneously allowing them to choose if they should be instantiated starting from the top or from the bottom of the array. Besides, an additional option allowing for the instantiation of a single driver row surrounded by parasitic model cells, used for faster simulations, has been implemented. The following chapters will provide insight into the creation process of this PCell. For this the explanation is divided into the different cellviews, highlighting the thought processes that went into solving the different challenges that had to be overcome during the creation process. Because the creation of this PCell did not require as many parameters as the decoder, the parameters implemented here are discussed in less detail than before. Keeping this in mind, the order of cellviews that are going to be explained will stay the same, starting with the explanation of the layout creation.

#### 4.3.1 Layout

The creation of the scalable layout started by using the newly created decoder cell to replace the vias, previously placed in an extra step using SKILL. Here the different parameters were tested by fitting the cell to the vias and then noted for the instantiation process in the PCell. In this step the possibility of defining the routing position using mathematical expressions proved to be advantageous because the connections of the SRAM address bits are placed in a quite challenging order. For example the function defining the routing position of these addresses looks rather complex "if(i<7 then b=0.2u\*i) if(i==4 then b=2u) if(i==5 then b=1.8u) if(i==6 then b=1.6u) b". After figuring out the right parameters, all vias from the previous SKILL script that were used for decoding purposes could be replaced using the newly created decoder PCell. Interestingly some further vias, not used for decoding purposes but located in fixed places, were found. Because the purpose of the decoder was not to replace vias placed in a fixed pattern, the code generating these vias has been reused for the PCell creation.

Finishing the move of these vias, the next step was to move the different design parts of the driver into the PCell. To achieve this, the various designs used in the creation of the fixed driver array were inspected and instantiated inside the PCell by using the according SKILL functions. Deleting the moved designs from the old layout revealed some remaining shapes that previously had not been part of any hierarchical designs. This meant that these shapes could not be accounted for by simply moving the design parts from the old cell into the PCell. The leftovers included some metal shapes at the top and bottom of the design as well as at the sides. Here the pieces at the top and bottom were bundled up in two layout designs, one containing all the metal left at the bottom, and one containing all the metal left at the top. These leftover cells then could be instantiated from inside the PCell, while the metal lines drawn at the side were integrated directly into the PCell code, allowing for a later needed length scaling.

The last thing that had to be moved from the old layout to the new one created by the PCell were the connection labels. Here the script creating these labels for the old design was picked apart so that the labels needed were transferred into the new design. Once this transfer was completed, an LVS against the old schematic proved that everything was migrated successfully. After moving the old layout into the PCell the parameterization process began.

To achieve this, a parameter specifying the number of output synapses was added. A scaling of four drivers per step has been chosen, resulting in 8 output rows, driving 16 synapses per step. Why this decoding seemed intuitive will become clear when looking at figure 5. Here it is shown that the drivers are connected to the busses in such a fashion, that if the address of each bus increases by one, the number of instantiated drivers goes up by four. While it would be possible to only add one additional driver to one bus, this seems quite unsensible considering the symmetry of the design.

To achieve the desired scaling, the number of synapse outputs is used to calculate different parameters used throughout the design. In the decoder for example it is used to calculate the maximum number of routing outputs. Implementing this directly results in a shrinking of the decoder depending on the chosen number of outputs. A challenge faced at this point was the implementation of the option for shrinking the synapse driver array, and therefore shrinking the decoder, not only from the top down but also from the bottom up.

Because the option restricting the maximum number of outputs for the decoder always starts shrinking from the highest output, meaning the output that is only connected to the address lines, the shrinking from the bottom up, resulting in a cutting of the lowest outputs, had to be implemented using a small trick. If the decoding is switched from forward to backward, the highest and lowest output essentially switch places, output 0 is now connected to address, instead of inverse address. If the expressions stating the positions of the address and inverse address lines are swapped, the via placement in the layout appears to be the same. The difference however is that for the decoder the highest output now is at the bottom, and not at the top, because all address lines are connected to the output at the bottom, while all inverse address lines are connected to the output at the top. Implementing this switch between forward and backward decoding, while also switching the positions of the address and inverse address lines, therefore allows the decoder to skip the lowest outputs, instead of the highest, when limiting the number of outputs. Using this trick when shrinking the array from the bottom up, an offset in the y-direction had to be applied to the cells, essentially moving the decoder to a new starting position in the layout.