# FACULTY OF Physics and Astronomy

Heidelberg University

DIPLOMA THESIS IN PHYSICS

SUBMITTED BY Heiko Engel Born in Sinsheim, Germany

JUNE 2009

# Development of a Fault Tolerant Softcore CPU for SRAM based FPGAs

This diploma thesis has been carried out by Heiko Engel at the

**Kirchhoff Institute for Physics**

under the supervision of

Prof. Dr. Udo Kebschull

#### Entwicklung einer fehlertoleranten Softcore CPU für FPGAs

In Umgebungen mit erhöhter Teilchenstrahlung ist der fehlerfreie Betrieb SRAM-basierter feldprogrammierbarer Hardware nicht mehr garantiert. Radioaktive Strahlung kann sowohl die Konfiguration, als auch den Zustand dieser Geräte und damit ihr Verhalten ändern. Gängige Ansätze benutzen dreifach redundante Logik (TMR) mit Mehrheitsentscheiden um strahlungsbedingtes Fehlverhalten zu kompensieren. Dies bringt jedoch ein erhebliches Maß an zusätzlicher Logik mit sich. Diese Diplomarbeit stellt eine fehlertolerante Softcore-CPU für FPGAs vor, die durch die Kombination von zweifach redundanter Logik und kontinuierlichem Schreiben der FPGA-Konfiguration mit einem geringeren Maß an zusätzlicher Logik auskommt. Die Wirksamkeit der angewandten Methoden konnte sowohl mit Fehlersimulationen, als auch im Teilchenstrahl Experiment nachgewiesen werden.

#### Development of a Fault Tolerant Softcore CPU for FPGAs

In radiative environments, the accurate operation of SRAM based field programmable hardware cannot be guaranteed. Radiation can alter configuration and state of these devices and thus change their behavior. Common approaches use *triple modular redundancy* (TMR) in combination with majority voters to compensate radiation induced errors. However, this comes with a large area overhead. This thesis proposes a fault tolerant softcore CPU for FPGAs with reduced area overhead by using double modular redundant logic in combination with continuous FPGA configuration writing. The effectiveness of the applied methods could be verified with both error simulation and particle beam experiments.

# Contents

| 1                                 | Intro | oduction and Motivation                               | 15 |

|-----------------------------------|-------|-------------------------------------------------------|----|

| 2                                 | FPG   | A Architecture                                        | 17 |

| 3                                 | Radi  | iation Effects in SRAM-based FPGAs                    | 21 |

|                                   | 3.1   | Theoretical Background                                | 21 |

|                                   |       | 3.1.1 Electric Conductivity in Semiconductors         | 21 |

|                                   |       | 3.1.2 MOSFET Basics                                   | 22 |

|                                   |       | 3.1.3 Passage of Particles through Matter             | 23 |

|                                   | 3.2   | Radiation Effects in SRAM Cells                       | 25 |

|                                   |       | 3.2.1 Cumulative Effects                              | 25 |

|                                   |       | 3.2.2 Single Event Effects                            | 27 |

|                                   | 3.3   | SEU Categories                                        | 30 |

|                                   |       | 3.3.1 Routing Effects                                 | 30 |

|                                   |       | 3.3.2 SEUs in Slices                                  | 32 |

|                                   |       | 3.3.3 SEUs in I/O Buffers                             | 32 |

|                                   |       | 3.3.4 SEUs in BRAMs                                   | 33 |

|                                   |       | 3.3.5 SEUs in further Parts of the FPGA               | 33 |

|                                   | 3.4   | Multi Bit Upsets                                      | 33 |

| 4                                 | Stat  | e of the Art                                          | 35 |

| 4.1 Radiation Hardened CMOS Logic |       | 35                                                    |    |

|                                   | 4.2   | Radiation Tolerant FPGA Architectures                 | 36 |

|                                   |       | 4.2.1 Flash FPGAs                                     | 36 |

|                                   |       | 4.2.2 Antifuse FPGAs                                  | 37 |

|                                   |       | 4.2.3 Radiation Tolerant Xilinx FPGAs                 | 38 |

|                                   | 4.3   | Redundancy                                            | 39 |

|                                   |       | 4.3.1 Triple Modular Redundancy                       | 39 |

|                                   |       | 4.3.2 Double Modular Redundancy                       | 40 |

|                                   |       | 4.3.3 Temporal Redundancy                             | 41 |

|                                   | 4.4   | Error Detection and Correction                        | 42 |

|                                   | 4.5   | Scrubbing                                             | 43 |

|                                   | 4.6   | FastBoot                                              | 44 |

|                                   | 4.7   | Shielding                                             | 44 |

|                                   | 4.8   | Automated and Combined SEE Mitigation Implementations | 44 |

|                                   | 1.0   |                                                       |    |

|   | 4.9                    | Fault                                                                                            | Tolerance in Higher Abstraction Layers          | 46       |

|---|------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|----------|

| 5 | Ann                    | roach                                                                                            |                                                 | 47       |

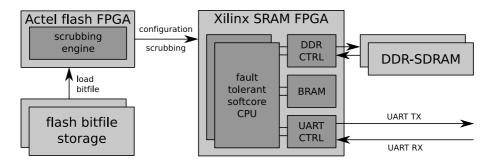

| • | 5.1                    |                                                                                                  | tion Tolerance in a Multilayer System           | 47       |

|   | 5.2                    |                                                                                                  | SEU Mitigation Techniques for the lowest Layers | 48       |

|   | 5.3                    |                                                                                                  | cal System Layout                               | 49       |

|   | 5.4                    | 5                                                                                                | sing a suitable Softcore CPU                    | 50       |

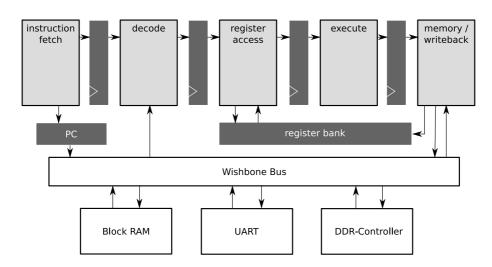

|   | 5. <del>1</del><br>5.5 |                                                                                                  | ase CPU                                         | 52       |

|   | 5.5                    | 5.5.1                                                                                            | Interrupt and Exception Handling                | 53       |

|   |                        | 5.5.2                                                                                            | The Wishbone Bus and its Peripherals            | 53<br>54 |

|   | 5.6                    |                                                                                                  | ring Fault Tolerance                            | 54<br>54 |

|   | 5.0                    | 11.2                                                                                             | 0                                               | 55       |

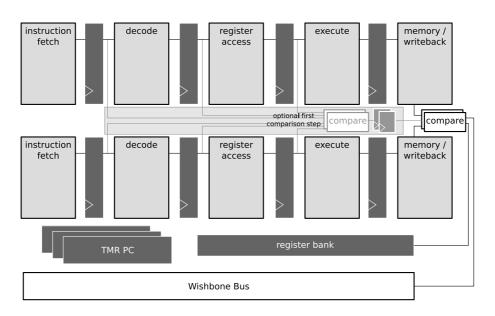

|   |                        | 5.6.1                                                                                            | Duplicating the Pipeline                        |          |

|   |                        | 5.6.2                                                                                            | Duplicating the Compare Logic                   | 56       |

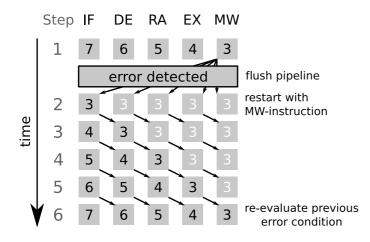

|   |                        | 5.6.3                                                                                            | Reacting on Errors                              | 57       |

|   |                        | 5.6.4                                                                                            | Triplicating the Program Counter                | 58       |

|   |                        | 5.6.5                                                                                            | Register Bank                                   | 58       |

|   |                        | 5.6.6                                                                                            | Securing the Wishbone Bus with Hamming Codes    | 60       |

| 6 | Imp                    | lementa                                                                                          | ation of the Fault Tolerant MIPS CPU            | 61       |

|   | 6.1                    | Target                                                                                           | t Devices and Tool Flow                         | 61       |

|   | 6.2                    | The A                                                                                            | ctel Flash FPGA                                 | 62       |

|   | 6.3                    | Hierai                                                                                           | rchy of the SRAM FPGA Design                    | 64       |

|   | 6.4                    | Imple                                                                                            | mentation of the Fault Tolerant CPU             | 65       |

|   |                        | 6.4.1                                                                                            | The Pipelining Concept                          | 65       |

|   |                        | 6.4.2                                                                                            | Description of the Pipeline Stages              | 66       |

|   |                        | 6.4.3                                                                                            | Hardware Multiplier and Divider                 | 68       |

|   |                        | 6.4.4                                                                                            | HDL Dual Pipeline Implementation                | 69       |

|   |                        | 6.4.5                                                                                            | Register Bank Organization                      | 70       |

|   |                        | 6.4.6                                                                                            | Register Bank Implementation                    | 73       |

|   |                        | 6.4.7                                                                                            | Program Counter Implementation                  | 74       |

|   |                        | 6.4.8                                                                                            | Error Detection and Error Handling              | 75       |

|   | 6.5                    | Wishb                                                                                            | oone Bus                                        | 77       |

|   |                        | 6.5.1                                                                                            | The Wishbone State Machine                      | 79       |

|   |                        | 6.5.2                                                                                            | Fault Tolerance Aspects of the Wishbone Bus     | 80       |

|   |                        | 6.5.3                                                                                            | Adding new Peripherals                          | 80       |

|   |                        | 6.5.4                                                                                            | The current Address Mapping                     | 81       |

|   | 6.6                    |                                                                                                  | nerals                                          | 81       |

|   | -                      | 6.6.1                                                                                            | UART                                            | 81       |

|   |                        | 6.6.2                                                                                            | Block-RAM                                       | 82       |

|   |                        | 6.6.3                                                                                            | DDR-SDRAM Controller                            | 83       |

|   |                        | 6.6.4                                                                                            | SEU-Analyzer                                    | 83       |

|   | 6.7                    |                                                                                                  | g Techniques for Redundant Logic                | 84       |

|   | 0.7                    | $\sim$ County rectainques for redundant Logic $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ |                                                 | 01       |

|    | 6.8                                      | The non-hardened CPU                              | 85          |  |  |  |

|----|------------------------------------------|---------------------------------------------------|-------------|--|--|--|

|    | 6.9                                      | Running Software on the CPU                       | 86          |  |  |  |

|    |                                          | 6.9.1 Creating Own Applications                   | 86          |  |  |  |

|    |                                          | 6.9.2 Changing BRAM Contents                      | 90          |  |  |  |

| 7  | Part                                     | al Bitfiles and SEU Simulation                    | 93          |  |  |  |

|    | 7.1                                      | Xilinx Configuration Protocol                     | 93          |  |  |  |

|    | 7.2                                      | Creating Partial Bitfiles                         | 93          |  |  |  |

|    |                                          | 7.2.1 Full bitfile format                         | 94          |  |  |  |

|    |                                          | 7.2.2 Removing BRAM Contents                      | 95          |  |  |  |

|    |                                          | 7.2.3 Getting Rid of the Reset Commands           | 96          |  |  |  |

|    |                                          | 7.2.4 Automating the Creation of Partial Bitfiles | 96          |  |  |  |

|    |                                          | 7.2.5 Partial Bitfiles Used for Scrubbing         | 98          |  |  |  |

|    | 7.3                                      | Error Injection through Partial Reconfiguration   | 98          |  |  |  |

|    |                                          | 7.3.1 Floor-Planning                              | 99          |  |  |  |

|    | 7.4                                      | CPU Testing 1                                     | 100         |  |  |  |

| 8  | Res                                      | lts 1                                             | L <b>03</b> |  |  |  |

|    | 8.1 Resource Usage and Power Consumption |                                                   | 103         |  |  |  |

|    | 8.2                                      |                                                   | 105         |  |  |  |

|    |                                          |                                                   | 105         |  |  |  |

|    |                                          |                                                   | 106         |  |  |  |

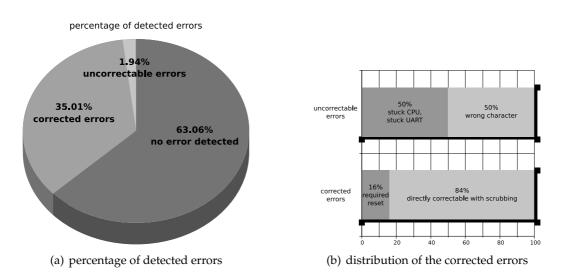

|    |                                          | -                                                 | 108         |  |  |  |

|    | 8.3                                      | ,<br>,                                            | 109         |  |  |  |

|    | 8.4                                      |                                                   | 113         |  |  |  |

| 9  | Con                                      | clusion 1                                         | 15          |  |  |  |

| Α  | Imn                                      | emented Instruction Set                           | 17          |  |  |  |

|    |                                          |                                                   |             |  |  |  |

| Bi | Bibliography                             |                                                   |             |  |  |  |

# List of Figures

| Simplified floor-plan of a Virtex-4 FX20 FPGA                     | 17                     |

|-------------------------------------------------------------------|------------------------|

|                                                                   | 18                     |

| 8                                                                 | 19                     |

| SRAM cell                                                         | 20                     |

| Simplified sketch of NMOS functionality                           | 22                     |

| Single ionizing particle going through a p-n junction             | 27                     |

| Comparison of Virtex-II and Virtex-4 SEU heavy ion cross sections | 28                     |

| SEU sensitive volumes of SRAM cells                               | 29                     |

| Effects of SETs in a synchronous design                           | 30                     |

| Overview of SEU effects in routing and look-up tables             | 31                     |

| Resistor hardened and DICE SRAM cells                             | 36                     |

| Flash and antifuse principles                                     | 37                     |

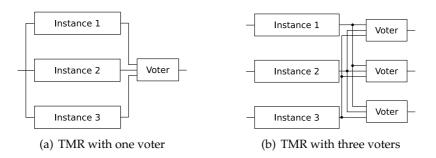

| TMR implementation with one or three voters                       | 39                     |

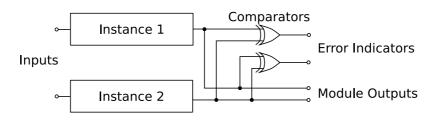

| Implementation of DMR/DWC                                         | 40                     |

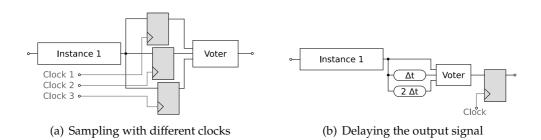

| Examples for temporal sampling                                    | 41                     |

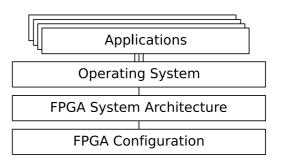

| Layer structure of modern FPGA based embedded systems             | 48                     |

| System layout                                                     | 49                     |

| Pipeline stages and bus concept of the implemented MIPS CPU       | 53                     |

|                                                                   | 55                     |

|                                                                   | 57                     |

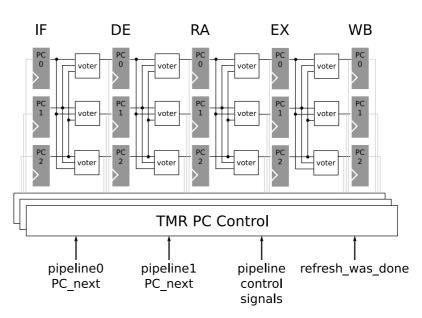

| Triplicated program counter                                       | 58                     |

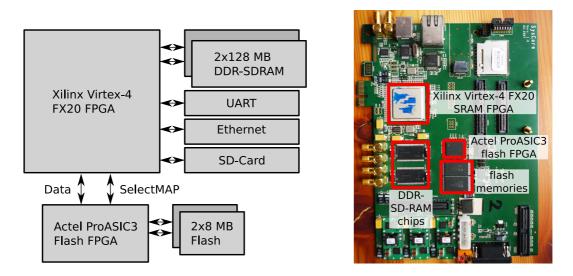

| Sketch and photo of the Syscore 1 board                           | 62                     |

|                                                                   |                        |

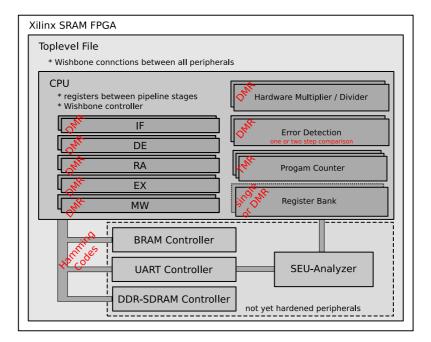

| 1                                                                 | 64                     |

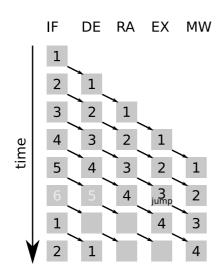

|                                                                   | 65                     |

|                                                                   | 69                     |

|                                                                   | 71                     |

|                                                                   | 73                     |

|                                                                   | 74                     |

|                                                                   | 76                     |

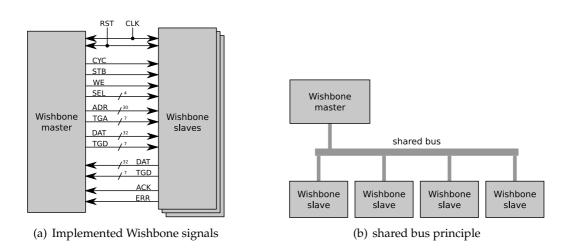

| Wishbone bus signals and shared bus principle                     | 77                     |

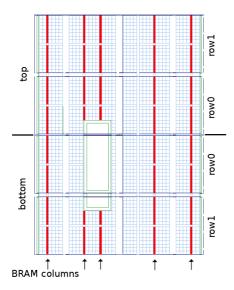

|                                                                   | CLB and slice contents |

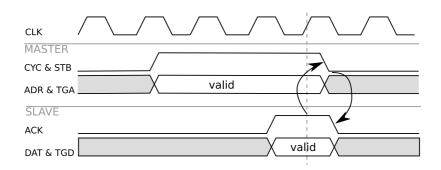

|     | Wishbone read cycleBehavior of the Wishbone state machine            |     |

|-----|----------------------------------------------------------------------|-----|

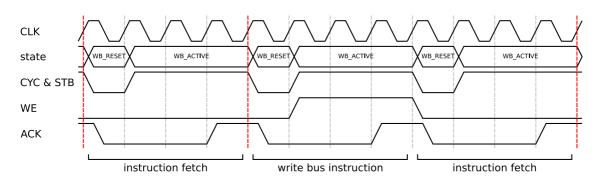

| 7.1 | BRAM organization within the FPGA                                    | 95  |

| 7.2 | Sketch of the floor-plan for SEU simulation                          |     |

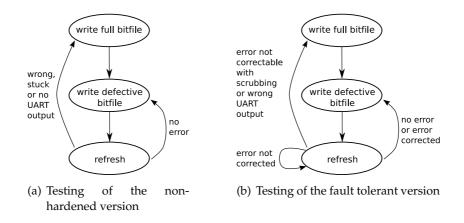

| 7.3 | Test procedures for both versions of the CPU                         |     |

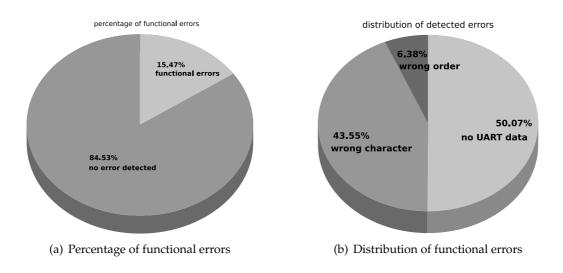

| 8.1 | Functional errors in the non-hardened CPU                            | 105 |

|     |                                                                      | 106 |

| 8.3 | SEU simulation results for the single register bank implementation   | 107 |

| 8.4 | SEU simulation results for the single step comparison implementation | 108 |

| 8.5 | Sketch and photo of the beam test arrangement                        | 109 |

| 8.6 | SEU cross section vs. LET                                            | 110 |

| 8.7 | Two examples of log files during the beam test                       | 112 |

# List of Tables

| 6.1 | General purpose registers                                                     | 70  |

|-----|-------------------------------------------------------------------------------|-----|

| 6.2 | Implemented co-processor 0 registers                                          | 71  |

| 6.3 | Status register format                                                        | 71  |

| 6.4 | Cause register format                                                         | 72  |

| 6.5 | Implemented exceptions                                                        | 72  |

| 6.6 | Implemented Wishbone address mapping                                          | 81  |

| 6.7 | Address mapping for the UART and status bit explanation                       | 82  |

| 6.8 | UART status bit explanation                                                   | 82  |

| 6.9 | Encoding of the SEU-analyzer diagnosis output                                 | 84  |

| 7.1 | Comparison between full and partial bitfile                                   | 97  |

| 7.2 | Row contents of a Virtex-4 FX20 configuration row                             | 98  |

| 7.3 | Number of configuration frames per element in Virtex-4 FPGAs                  | 99  |

| 8.1 | Comparison of synthesis results for all tested versions of the CPU $\ldots$ . | 104 |

| 8.2 | Current consumption                                                           | 104 |

# **1** Introduction and Motivation

With the invention of the transistor in the middle of the 20th century, a new era in electronic devices was started. The previously used tubes could gradually be replaced with these low voltage, low area, highly flexible circuit elements. Research over the years led to continuously decreasing structure sizes allowing the creation of systems with millions of transistors on a single chip. However, creating custom application specific integrated circuits (ASICs) is a time consuming and expensive task. The manufacturing costs can only be mitigated by producing large numbers of chips. An approach to make microelectronic devices available to a broader spectrum of applications was the development of microcontroller systems, starting in the 1970s. Several different modules, all produced in large series and thus cheap, can be combined to form a custom electronic system. But even with increasing functionality, these devices cannot reach the performance of ASICs and their hardware based functionality is fixed once assembled.

This gap has been recognized by Ross Freeman, founder of Xilinx<sup>1</sup>, in 1984. He invented the field programmable gate array (FPGA). The patented idea was to supply a single chip with "a plurality of configurable logic elements variably interconnected in response to control signals to perform a selected logic function" [Fre89]. Freeman postulated this device to be affordable for customers due to decreasing costs for transistors over time. Xilinx is now a multi billion dollar enterprise and "the worldwide leader in programmable logic solutions" [Xilun]. The possibility to use the same chip for arbitrary circuits opened a new field of applications. Complex tasks previously implemented as sequential microprocessor instructions can be parallelized in FPGAs. The concrete functionality of an FPGA has only roughly to be specified during the construction of an electronic device and thus significantly increases the time-to-market. The possibility for users to change the configuration of the FPGA offers the potential to supply several different applications with the same device or "upgrade" an existing implementation with bug-fixes or new functionality. FPGAs developed from ASIC prototyping platforms to solutions for digital signal processing, high performance computing, defense, aerospace and high energy physics applications.

Especially in high energy physics experiments, FPGAs have become an important part. Data rates produced by current particle detectors are orders too high to be saved completely. A trigger system is required to select the interesting events to be saved for further

<sup>&</sup>lt;sup>1</sup>http://www.xilinx.com

analysis. This trigger decision requires a lot of calculations and data management impossible with common sequential processor systems. Fast ASIC solutions are very expensive for small production series and give no flexibility once implemented, so FPGAs are used to parallelize these calculations and evaluate a trigger condition. Another FPGA application is the implementation of embedded systems for controlling tasks. FPGAs are able to run full operating systems. The flexibility on both, the hardware and the software aspects opens a broad field of applications. FPGAs have successfully been integrated in the current experimental buildup at CERN<sup>2</sup> and play a key role in the development of the *Condensed Baryonic Matter*<sup>3</sup> (CBM) experiment at GSI Darmstadt.

However, there are some problems in using commercial off-the-shelf (COTS) FPGAs in particle detectors, avionics or space missions. These FPGAs are susceptible to radiation induced configuration and user logic changes. The FPGA itself is usually not damaged, but its current configuration is altered due to radiation. The correct behavior of the circuit in a radiative environment can therefore not be guaranteed.

This work addresses mitigation strategies for radiation induced effects in SRAM based FPGAs applied on a fault tolerant softcore CPU. Chapter two describes the targeting FPGA architecture and chapter three explains the possible effects of radiation on these FPGAs. Chapter four shows an overview of previously done work to mitigate radiation effects. This work's approach, in contrast to others, and how it was implemented is described in chapter five and six. The effectiveness of the applied methods on the implemented designs have been verified with both error simulation and particle beam test as described in chapters seven and eight. Finally, all relevant aspects of the work will be drawn together in chapter nine.

<sup>&</sup>lt;sup>2</sup>http://www.cern.ch

<sup>&</sup>lt;sup>3</sup>http://www.gsi.de/fair/experiments/CBM/

## 2 FPGA Architecture

A Field Programmable Gate Array (FPGA) is an array of several different logic elements packed into a single semiconductor device. In contrast to common electronic devices, the logic functions of the single internal elements and their connection with each other are volatile and can be programmed by the user at any time. Several input and output pins can easily be used to make connections to almost any other electronic component with the common electrical signalling standards. Only FPGAs from Xilinx<sup>1</sup> have been used in this work, so architectures from other vendors have been neglected in the following descriptions.

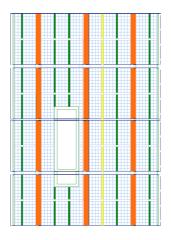

The elements forming the array structure in a Xilinx Virtex-4 FPGA are called *Configurable Logic Blocks* (CLB). As the name implies, the behavior of these logic blocks and their connection with each other are configurable by the user. A configurable switch matrix attached to any CLB grants access to the chip wide routing network. The CLBs are arranged periodically in rows and columns and cover the main part of the FPGA. Apart from the CLBs, there are some further configurable columns containing *Block-RAMs* (BRAM) as on-chip storage, *Digital Signal Processors* (DSP) for specific calculations, *Multi Gigabit Tranceivers* (MGT) for fast serial communication, and *Input/Output Buffers* (IOB) as connection into and out of the FPGA. The FPGAs from Xilinx' FX line have also hard wired *IBM PowerPC RISC Processor Cores* [Xil08d]. A sample arrangement is shown in figure 2.1.

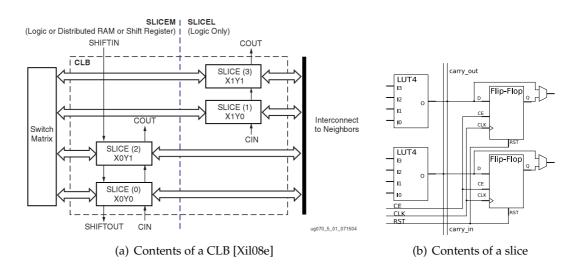

The CLBs are subdivided into finer grained programmable logic blocks called *slices*, fast connections between them and connections to the chip-wide routing network. There are two types of slices called SLICEM and SLICEL, M standing for *memory* and L for *logic*. The look-up tables in the SLICEM components possess the additional ability that their config-

**Figure 2.1:** Simplified floorplan from Xilinx PlanAhead for a Virtex-4 FX20 FPGA. The blue bordered rectangles are CLBs, BRAMs are colored green, IOBs orange, DSPs yellow. The white rectangle in the center is a PowerPC core.

uration doesn't need to be completely static during runtime, so they can be used as cheap distributed memories or shift registers. Both types of slices are available in equal numbers. A CLB consists of two columns, each with two slices. The left column contains

<sup>&</sup>lt;sup>1</sup>http://www.xilinx.com

Figure 2.2: Arrangement of slices within a CLB (left) and simplified internals of a slice (right)

SLICEMs, the right SLICELs. Each CLB is connected to its neighbors and a chip-wide configurable routing network. A sketch of a CLB is shown in figure 2.2(a).

The slices mainly consist of look-up tables (LUT), flip-flops (FF), Multiplexers (MUX), and some basic gates. Look-up tables are small programmable memory blocks that produce an output vector to any input vector. The input vector can be understood as an address-line selecting one of the memory values and giving this value to the LUT-output. Current FPGA architectures have look-up tables with four to six inputs and one to two outputs. With the according configuration, any boolean function of the input vectors can be realized. Therefore FPGAs do not need to supply basic gates like AND, OR, NOT, XOR etc. as any combination of those gates can be realized with look-up tables. Unlike the gate implementation, the propagation delay through a LUT is independent of its logic function.Virtex-4 FPGAs have look-up tables with four inputs and one output. The flip-flops can be used as edge-triggered D-type flip-flops or as level sensitive latches. The control signals *reset*, *set* and *clock\_enable* can be used as synchronous or asynchronous signals and the initial- and reset-values can be specified via configuration. Two LUTs and two flip-flops are grouped with some basic gates and multiplexers to form a slice. Both flip-flops in a slice use the same *clock*, *reset*, *set* and *clock\_enable* signals which cannot come directly from a LUT within the same slice. These flip-flop control signals have the ability to be inverted at the entrance to the slice. The flip-flop's data input line is connected to the preceding LUT's output and the slices' output can come from the FF or directly from the LUT. Furthermore, there are *carry* and *shift* lines connecting proximate slices to allow the implementation of fast adders, comparators or shifters. Figure 2.2(b) illustrates the components within a slice, a more detailed description can be found in the Virtex-4 User Guide [Xil08e].

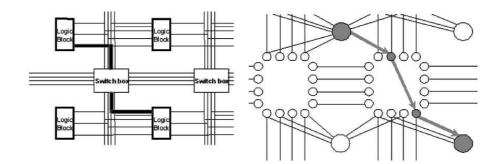

The routing between and within the different elements is done with multiplexers and

**Figure 2.3:** Model of the FPGA routing net. The connections between the available wires are configurable with programmable interconnect points (PIP). (Source: [SV06]).

programmable interconnect points (PIP). Multiplexers with statically configured select lines control the signaling within the slices. Outside the slices, the routing is done via static wires. Only the connection between, not the wires themselves are configurable with PIPs. A model of the PIP based routing network is shown in figure 2.3. The PIPs are grouped in switch matrices on CLB level as shown in figure 2.2(a).

The clock signals for synchronous designs have a second, separate routing net spanning throughout the whole device. This global clock net can reach any clock inputs within the FPGA and can be controlled with clock buffers and digital clock managers (DCM). Apart from the global clock net, the FPGA is further divided into several clock regions to allow different local clocks for specific parts of the design.

All of the elements mentioned above have an underlying layer controlling their behavior. Any look-up table to be used must be filled with initial values to act like the desired logic function. Connections between two logic elements must be made by combining according parts of the routing net via switchable interconnect points. Any flip-flop can hold a reset value and can be defined as synchronous or asynchronous. Any IO-Buffer can be used as input or output, with several possible voltage levels just by setting the according configuration bits. This configuration layer is read- and writable for the user and thus makes the FPGA *field programmable*.

The configuration of the FPGA can be done by using one of the vendor supplied configuration interfaces. All of these interfaces are fed with a bitfile containing the values for any configuration bit in the FPGA. Details on the configuration interfaces and the configuration process are further described in chapter 7.

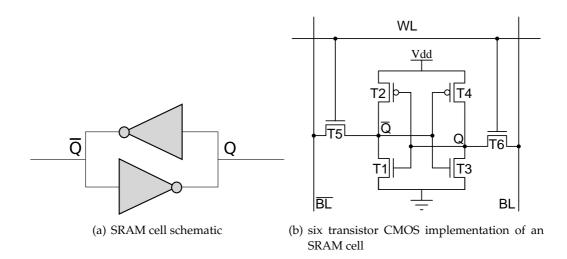

The whole FPGA used in this thesis, including configuration and user logic, is made of SRAM cells. SRAM stands for *Static Random Access Memory*. "Static" in this case means that the memory cell will keep its current value as long as it is powered on. This is in contrast to *dynamic* RAM (DRAM), which stores its values in small capacitors that lose their charge if not refreshed periodically. If the device is powered off, both types

**Figure 2.4:** SRAM cell schematic as bistable inverters (left) and its six transistor CMOS implementation (right)

of memory lose their contents. *Random Access* means that the memory contents can be read and written at any time. A SRAM cell is a bistable circuit element. It can easily be understood by imagining two oppositely arranged parallel inverters as shown in figure 2.4(a). The cell always holds two values: the value Q and its inversion  $\overline{Q}$ . As long as the drive strength on Q and  $\overline{Q}$  is smaller than the drive strength of the inverters, the current value will be held as long as power is applied to the inverters. If the drive strength on Q and  $\overline{Q}$  exceeds this limit, a new value is written into the cell, according to the levels of Q and  $\overline{Q}$ . The actual CMOS implementation shown in figure 2.4(b) is only little more complicated. On reads, both bit lines BL and  $\overline{BL}$  are precharged weakly. By selecting the cell with its word line (WL), the transistors T5 and T6 get conductive and therefore Q and  $\overline{Q}$  drive the bit lines to their stored values. On writes, the bit lines are driven stronger than T1-T4 can do. By selecting the cell with its word line the previously stored values get overwritten with the values of BL and  $\overline{BL}$ . For more information about field effect transistor (FET) properties or circuits see [HH89].

# **3** Radiation Effects in SRAM-based FPGAs

After a brief theoretical background, this chapter gives an overview on any possible effects of radiation on semiconductor electronics. A focus is set on their impact on SRAM based FPGA applications.

### 3.1 Theoretical Background

#### 3.1.1 Electric Conductivity in Semiconductors

The correct theoretical explanation of electrical conductivity in crystalline solids is a highly complex problem requiring quantum mechanical calculations of the time dependent Schrödinger equation in external fields. However, it is mostly sufficient to use semiclassical models of electron wave packets with effective mass and speed, derived from their interaction with the crystal lattice in form of electron-phonon-scattering, electrondefect-scattering or electron-electron-scattering. This leads to a theory of electrical conductivity being highly dependent on temperature, lattice structure and its defects like foreign, missing, additional or displaced atoms.

The conductivity can be described with a band structure represented by an orbital-like model of atoms in a lattice. There are two bands: the valance and the conduction band. Charge carriers in the valence band are bound to lattice atoms, whereas the carriers in the conduction band are free to move. By exciting an atom in the lattice, an electron is lifted to the conduction band, leaving a hole in the valence band. With an electric field attached to this solid, the now free electron will move along the field. The left hole is filled with electrons from a neighbor atom by leaving a hole there. Thus, the hole effectively moves to the opposite direction. Both, the electrons and the holes give their share to the conductivity, but one can easily imagine, that the mobility of electrons is higher than the mobility of the holes. More information about models of electric conductivity and band structures in solids can be found in [Kit04].

A solid is an electrical conductor if there are always free electrons in the conduction band, and it is an isolator if there are no free carriers in this band. As thermal energy can excite atoms, this is a temperature dependent issue. Semiconductors are solids with a small band gap of one to four eV and they are isolators for small temperatures. The conductivity increases with temperature as more and more electron hole pairs can be excited with

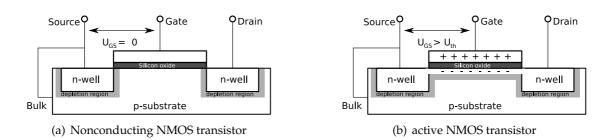

Figure 3.1: Simplified sketch of NMOS functionality

the thermal energy. Conductivity can further be affected by adding foreign atoms into the lattice (doping). Adding atoms with more or less valence electrons than the base material results in a n- or p-doped semiconductor. This creates states for electrons or holes between the former valance and conduction bands and therefore moves the Fermi energy of the solid. Combining p and n-doped silicon gives the well known depletion regions and potential effects exploited by diodes and transistors.

#### 3.1.2 MOSFET Basics

A metal oxide semiconductor field effect transistor (MOSFET) is a voltage controlled current source. It has four connections: drain, source, gate and bulk. The gate is isolated from the other ports with a thin layer of silicon oxide and the current from source to drain is controlled by the voltage applied between gate and source. The bulk connection is used to keep the substrate on a well defined potential and is usually directly connected to the source. The functionality is exemplary shown on a n-type MOSFET (NMOS) in figure 3.1. The p-substrate holds a lot of free holes, but only few free electrons, whereas the n-wells hold more free electrons than holes. Without a positive voltage applied between gate and source, the connection between source and drain acts like a reverse biased diode and only small sub-threshold leakage currents can flow. By applying a positive voltage between gate and source, an electric field between gate and bulk is formed. Exceeding a specific threshold voltage, this field pushes the holes away and pulls some of the free electrons in the p-substrate to the interface between bulk and gate oxide. This forms a n-conducting channel between source and drain. The voltage applied on the gate can therefore control the current between source and drain.

Devices with the opposite doping of NMOS are PMOS transistors. In PMOS transistors the bulk substrate is n-doped and the source and drain wells are p-doped. The functionality is quite similar, but the PMOS is conducting without a gate source voltage applied and is based on the holes as charge carriers. PMOS transistors are therefore slower than their n-doped counterparts. PMOS transistors can be placed on the same substrate as NMOS transistors, if a n-doped region for the whole PMOS is created in the p-substrate or vice versa. The combination of both, PMOS and NMOS transistors on the same substrate is called *Complementary MOS* (CMOS) technology and is nowadays one of the most frequently used logic family. Any logic gates can be created with CMOS. The SRAM cell in figure 2.4(b) is an example, too.

#### 3.1.3 Passage of Particles through Matter

Almost any kind of radiation and particle can have an effect passing through matter. The effect depends on the incoming particle, its energy and the target material. Concerning radiation effects in semiconductors, the following radiation particles and effects can be distinguished:

- charged leptons like electrons or muons

→ bremsstrahlung and ionization effects

- charged hadrons like protons or *α* particles up to heavy ions

→ ionization and nuclear effects

- charge less hadrons like neutrons

→ no direct ionization, nuclear effects only

- $\gamma$  particles

- $\rightarrow$  ionization, coulomb scattering, pair production

Both charged leptons and charged hadrons can interact with matter by ionizing atoms in the target material. The incoming particle ionizes the target material's atoms by scattering with their electrons. This ionization process creates electron hole pairs along the particle's way through the target material. The electron hole pairs can recombine within a short time as long as they are not separated by external electric fields. The energy required for the creation of a single electron hole pair in silicon semiconductors has been measured to 3.6 eV [Lut07], whereas in silicon oxide 17 eV are required [Sch96]. The energy loss for charged hadrons due to ionization can be calculated with the Bethe-Bloch-formula giving an energy loss per distance:

$$\frac{dE}{dx} = 2\pi N_0 r_e^2 m_e c^2 \rho \frac{Z}{A} \frac{z^2}{\beta^2} \left[ ln(\frac{2m_e \gamma^2 v^2 W_{max}}{I^2} - 2\beta^2 - \delta) \right]$$

(3.1)

with  $N_0$  the Avogadro Number,  $r_e$  the classical electron radius  $\frac{e^2}{4\pi m_e c^2}$ ,  $m_e$  the electron mass, Z and A the atomic number and weight of the medium, *z* the charge of the incident particle,  $\rho$  the density of the medium, *I* an effective ionization potential, *v* the velocity of the incident particle,  $\beta = \frac{v}{c}$ ,  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$ ,  $\delta$  a density correction and  $W_{max}$  the maximum energy transfer in a single collision. The calculation of *I*,  $\delta$  and  $W_{max}$  can be found in [Leo94] chapter 2.2.2.

The resulting unit of the energy loss is  $\left[\frac{MeV}{cm}\right]$ . A typical unit in radiation tests of electronic devices is the Linear Energy Transfer (LET) defined as  $\left[\frac{MeVcm^2}{mg}\right]$ . This can be achieved by

dividing formula 3.1 by the target material's density  $\rho$ . The Calculation of the energy loss of a specific particle going through a defined material can easily be done for the entry point to the material, but gives non trivial differential equations, if the particle significantly slows down within the material. There are some simulators for energy loss determinations like SRIM<sup>1</sup>, FLUKA<sup>2</sup> or the TVDG LET Calculator<sup>3</sup> to simplify life with these calculations. The ionization losses as calculated above cover the main part of energy transfer for heavy ion and hadron scattering. This model is not sufficient for light charged particles like electrons.

Bremsstrahlung occurs, when light charged particles are influenced by the electric field of the target material's atom nuclei. The nuclei change the trajectory of the incoming particle due to acceleration in the nuclei's electric field. Any acceleration of a charged particle leads to an emission of bremsstrahlung in form of a photon. The energy loss due to Bremsstrahlung is dependent on the incoming particle's energy, the screening of the target material's nucleon charge and therefore the target material itself. Due to the small lepton mass, bremsstrahlung covers the main part of energy loss for charged leptons above a few MeV ([Leo94], p.37). For low energies, ionization is dominating over Bremsstrahlung. The energy loss of charged leptons is therefore a sum of ionization losses and bremsstrahlung losses. The formula for calculating the ionization losses for electrons is quite similar to the Bethe-Bloch formula shown above, but takes into account that electrons are much lighter than hadrons and therefore their trajectory significantly changes on collisions. Furthermore, the scattering is now done between identical, indistinguishable particles. For calculation details and examples, see [Leo94] chapter 2.4.

Nuclear effects occur due to the scattering of incoming particles with the nuclei of the target material. This includes elastic and inelastic scattering resulting in movement, excitation or decay of the target nuclei. Moving atoms in a semiconductor can lead to lattice defects having a direct impact on the semiconductor's band structure. Nuclear scattering is not directly ionizing, but the results from scattering induced nuclear reactions can be. A typical neutron induced nuclear reaction in silicon is the decay of p-doping Boron-10 into Lithium and an ionizing  $\alpha$  particle.

$\gamma$  particles interact with the electrons of the target material. This can result in electrons being excited to higher orbitals or atoms being ionized. For high energies, the  $\gamma$  particles can change to fermion anti-fermion pairs like electron and positron or quark and antiquark within the target material (pair production). These particles can then interact with the material via ionizing or nuclear effects as described above.

<sup>&</sup>lt;sup>1</sup>http://www.srim.org

<sup>&</sup>lt;sup>2</sup>http://www.fluka.org

<sup>&</sup>lt;sup>3</sup>http://tvdg10.phy.bnl.gov/LETCalc.html

## 3.2 Radiation Effects in SRAM Cells

The radiation processes affecting the correct behavior of semiconductor circuits in general, and particularly SRAM cells, are mainly ionization and nuclear scattering. An ionizing particle going through a semiconductor leaves a number of electron hole pairs along its way. These electron hole pairs would recombine within short time if they are not separated by electric fields. A running semiconductor device however holds a lot of electric fields because every single transistor relies on them. These fields are quite strong because the distances between two electric poles are in the order of several nanometers down to a few atom layers for the gate oxide. The electron hole pairs created from a charged particle going through a transistor with strong electric fields will not be able to completely recombine before they are separated by the electric field. The consequence are additional free charges in the semiconductor with different mobilities. The mobility of the electrons is higher than the mobility of the holes as described in chapter 3.1.1. Nuclear scattering processes play a role as these interactions can create ionizing particles or move atoms in the semiconductor's lattice structure. Both of these processes lead to two independent effects: cumulative effects and single event effects. Single event effects result, as the name implies, from single radiation particles, whereas the cumulative effects rely on the accumulation of effects from several particles during the whole device's lifetime.

### 3.2.1 Cumulative Effects

Cumulative effects are gradual effects during the whole lifetime of the radiated device. They rely on the accumulation of radiation effects and lead to a failure when a certain limit is reached. There are two types of cumulative effects: total ionizing dose (TID) and displacement.

TID effects result from charge collection in the transistor's gate oxide, at the silicon-tooxide interface or in the field oxide between transistors. If electron hole pairs in the oxide do not recombine immediately after the particle strike, they get separated by the electric field. The electrons can leave the oxide quickly due to their higher mobility. The transportation of holes according to the external field is much slower than for electrons as they need to *hop* between localized states in the oxide [Sch96]. During their way to the gate-to-oxide or silicon-to-oxide interface, the holes may get trapped, forming positive oxide charges for both p- and n-channel transistors. These charges screen or increase the electric field from gate to bulk and thus shift the threshold voltage and affect the leakage current. These trapped oxide charges however can be annealed even with room temperature over time.

A further effect of holes moving through the oxide is the release of hydrogen ions out of the oxide structure. These ions can move to the silicon-to-oxide interface where they may

become interface traps [Sch96]. These traps form states in the band gap of the semiconductor exactly at the silicon-to-oxide interface being responsible for the voltage controlled conductivity of the transistor. For p-channel transistors, these traps are predominantly in the lower part of the band gap allowing positive charges. Traps in the upper part of the band gap are mostly formed for n-channel transistors enabling negative charges. In combination with the trapped positive charge in the oxide, these effects may compensate or add up. The interface traps do not anneal with room temperature like the oxide charge buildup and degrade the device with shifted threshold voltage and decreased carrier mobility [Sch96]. This leads to timing errors, increased current or uncontrollable transistors switching.

The TID value used for device characterization is the energy deposited in the material of interest in form of ionization. The unit of the TID is *Gray* or *rad* where  $1 \frac{Joule}{kg} = 1 \text{ Gray} = 100 \text{ rad}$ . The value for the TID rate in a particle beam experiment can be derived from the LET value calculated with the Bethe-Bloch formula 3.1 or one of the simulators:

$$TID \ rate \ [\frac{rad}{s}] = 100 \cdot LET \cdot \phi \cdot e/A \tag{3.2}$$

The factor 100 is for the conversion from *Gray* to *rad*, *LET* is the calculated energy transfer in  $\left[\frac{eV \ cm^2}{kg}\right]$ ,  $\phi$  the particle flux through the FPGA in  $\left[\frac{1}{s}\right]$ , *e* the elementary charge  $1.602 \cdot 10^{-19}$  *Joule* and *A* the contributing FPGA area in  $[cm^2]$ . This calculation is due to its units independent of the thickness of the contributing oxide volume.

The maximum total ionizing dose an FPGA can handle depends on its silicon oxide and gate size and therefore its manufacturing process technology. There is a military standard testing method for TID resistance called *MIL-STD 883 Test Method 1019* [Dep97] to allow comparison between different electronic devices. TID measurements from Xilinx [FDLH08] according to this testing procedure gave a maximum TID resistance of 100 krad for the early Virtex devices with 220 nm technology. Decreasing technology size reduced the volume of TID susceptible silicon oxide and the gate volume and therefore led to an increased TID resistance. The Virtex-II architecture manufactured in 150nm technology already had a tolerance of about 200 krad and the following Virtex-II Pro FP-GAs reached 250 krad according to test procedure 1019. The Virtex-4 devices used in this work are manufactured in 90nm technology and have a total ionizing dose resistance of around 300 krad. According to [FDLH08], the modern architectures in 90nm technology can handle doses up to 1 Mrad with "proper design margins". Virtex-5 devices in 65nm technology are supposed to handle even more.

A further cumulative effect is displacement. The recoil from a high energetic radiation particle can move the target particle in the semiconductor's lattice structure. The moved lattice atom generates an interstitial and leaves a vacancy. With enough energy, the hit atom can displace further lattice atoms and generate a defect cascade. These defects generate traps, can influence the carrier mobility or increase the thermal generation of electron hole pairs. According to [Sch96], about 90% of interstitial vacancy pairs recombine

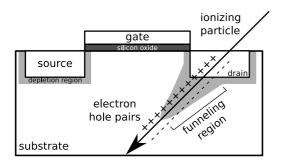

**Figure 3.2:** Single ionizing particle going through a p-n junction. The particle creates electron hole pairs that may get separated by electric fields before they can recombine. The resulting charge can have several effects. The charge in the funneling region contributes to the charge collection. Charges in deeper substrate regions do not affect the device.

within a minute after irradiation and the displacement effects are relatively unimportant for MOS transistors.

#### 3.2.2 Single Event Effects

Single event effects (SEE) are the effects of single ionizing particles going through semiconductor electronics. The deposited charge can have different effects from temporary or correctable *soft errors* up to permanent and uncorrectable *hard errors*. As described above, an ionizing particle creates a high density electron hole plasma along its way through the semiconductor. The energy deposited within the semiconductor is defined as the linear energy transfer (LET) and can be calculated as shown in chapter 3.1.3. Under normal circumstances, only the charges deposited in the top silicon region should actually affect the circuit. But a charged particle going through a p-n junction extends the depletion region along its path. This effect is called *funneling*. The electron hole pairs in the funneling region therefore contribute to the total accumulated charge. If this total charge is big enough, it can considerably affect the circuit's behavior. But even if funneling significantly extends the volume from which the charge may be accumulated into the substrate, the contributing volume is in the top few micrometers of the substrate.

#### Hard Errors

Hard errors are errors that result in a physical damage of the radiated device. These errors cannot be recovered. Hard errors can be distinguished between single event burnout (SEBO), single event gate rupture (SEGR) and single event latch-up (SEL). They mostly induced by heavy ion particles because a lot of energy has to be deposited to cause these effects. Single event burnout affects solely high power devices like power MOSFETs, IG-BTs and power diodes. Particles going through these multi-layered p-n devices can create a positive feedback of internal parasitic transistors getting conducting until breakdown and destruction of the device. Single event gate rupture is an effect in mainly power MOSFETs, but has also been observed in MOS transistors [Wro87]. Under normal conditions, the electric field between gate and substrate is large, but not large enough to

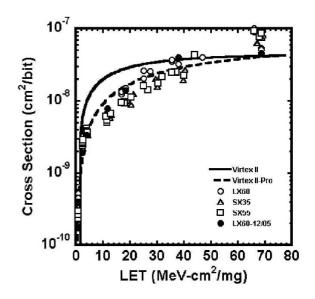

**Figure 3.3:** Comparison of Virtex-II and Virtex-4 heavy ion SEU cross sections vs. linear energy transfer (LET). The cross section starts increasing from a certain threshold LET and goes into saturation for high values of LET. The measured curves can be fitted using a Weibull fit. (Source: [GKS<sup>+</sup>06])

rupture the isolating silicon oxide layer. In case of an ion striking through gate oxide and substrate leaving an electron hole plasma, this plasma may get conducting. With a strong electric field, the resulting current could melt the oxide and destroy the device. Single event latch-up is an effect of closely placed p- and n-channel MOSFETs on the same substrate. The combination of differently doped regions automatically leads to parasitic transistors. This is no problem as long as all of these regions are kept to a fixed and well defined potential. But the situation can easily change if an ionizing particle deposits charge in the parasitic devices. The change of state of a single transistor can produce a positive feedback by enabling surrounding parasitic transistors leading to a latch-up. This latch-up can be interrupted by cutting the power supply, otherwise the device will be destroyed.

Hard errors are usually not a concern for CMOS circuits in space or particle detector applications because these errors are either very unlikely or the radiation energy is too low.

#### Soft Errors

Soft errors are errors that do not cause physical damage to a semiconductor device. These errors are temporary or can be corrected by reconfiguring the device. There are two types of soft errors: single event transients (SET) and single event upsets (SEU).

Single event upsets (SEU) are flipped bits of memory cells. As this work addresses SRAM based FPGAs, SRAM cells are here used for explanation. If an ionizing particle deposits enough charge in an SRAM cell, the content of the memory cell can change. Further, not any point within an SRAM cell will be eligible to change the memory content with any amount of charge. Thus, to produce an SEU a critical amount of charge in a sensitive

**Figure 3.4:** SEU sensitive volumes of SRAM cells. Only particle strikes within these colored areas and with enough energy are able to flip the memory cell. (Source: [Xila])

volume must be exceeded. The sensitive volume of an SRAM cell is sketched in figure 3.4. Particles with less energy or outside the sensitive volume will therefore just give a short current pulse without changing the memory cell's content. The dependency of SEU cross section and linear energy transfer (LET) is exemplary shown for a Virtex-4 FPGA and heavy ion radiation in figure 3.3. Below a certain threshold LET, there will not be any SEUs possible, because the deposit charge in the sensitive area will not be sufficient. Exceeding this threshold LET, more and more SEUs can be induced. This cross section seems to saturate for high values of LET and therefore simply depends on the probability of hitting the right parts of the SRAM cell. The shape of this cross section vs. LET behavior can mathematically described with a Weibull fit. A detailed explanation of the shape of this cross section vs. LET curve in combination with the mathematical formulas describing the Weibull model can be found in [Edm96]. In an FPGA single event upsets show up as flipped memory bits, in both, the device configuration and the user logic flip-flops. The possible effects of SEUs in an FPGA are shown in chapter 3.3

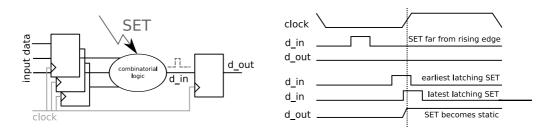

The second class of soft errors are single event transients (SET). SETs are based on the same radiation effect as SEUs, but do not require to hit the sensitive area of an SRAM cell. The deposit of charge in the semiconductor leads to short current pulses. The magnitude of these pulses highly depends on the deposited charge and the capacity of the hit line. These pulses are usually in the order of 100 to 200 picoseconds in CMOS circuits and can propagate as glitches in the user logic [ME00]. SETs can have serious consequences if the affected signal is sampled by a system clock as shown in figure 3.5. As long as a SET arrives at a flip-flop's data input in the absence of the sampling clock edge, the SET will not have an effect. This changes, if both, the SET glitch and the sampling clock edge come approximately at the same time. A SET being sampled correctly at a clock edge becomes static and has the same effects as a direct SEU. A SET occurring at a certain moment may violate setup or hold times and therefore produce unpredictable or even metastable flip-flop outputs. Further, the clock or reset lines may be affected by SETs, too. This could lead to desynchronized or spontaneously reseted parts of the FPGA. The rate of SETs becoming glitches is dependent of the flux and energy of the ionizing radiation. However, the probability of a SET being sampled and becoming an SEU is additionally dependent on the clock frequency. The more often a value is sampled, the higher the chance to hit a glitch.

**Figure 3.5:** Effects of SETs in synchronous designs. The SET induced glitch on  $d_{in}$  does not have an effect on  $d_{out}$  as long as it occurs apart from a rising clock edge at the flip-flop's input. A SET being sampled at a rising clock edge becomes a static upset and shows the same effects as a direct SEU. If the glitch violates setup or hold times, the flip-flop's output may be unpredictable or even metastable.

Single event upsets (SEU) and single event transients (SET) are the mainly observed effects when using semiconductor electronics in a radiative environment.

### 3.3 SEU Categories

The Virtex-4 FX20 FPGA used in this work has about 7 million configuration bits and around 17.000 user flip-flops. The probability of changing an user flip-flop is therefore small compared to the probability of changing a configuration bit. A single event upset in the device configuration can have several effects on the running design. A classification of possible SEU effects in a Virtex-I FPGA has been done in [GCZ03]. According to this source, around 80% of all SEUs affect the routing. The majority of remaining SEUs can be identified as look-up table value changes and upsets of the bits controlling miscellaneous functionality of the whole CLB or IOB. An overview of the most common SEU effects is shown in figure 3.6

#### 3.3.1 Routing Effects

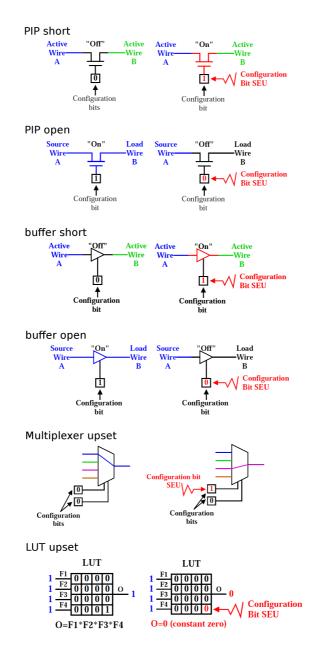

The SEU effects on the FPGA routing net have extensively been studied for Virtex devices by Xilinx [GCZ03] and Sterpone & Violante [SV06]. As described in chapter 2, the routing of signals through the FPGA is done with programmable interconnect points (PIP). The behavior of these PIPs is controlled by configuration bits. Long lines may be assisted with switchable buffers. A SEU in a PIP may open or shorten two wires. An open simply disconnects the two lines, so no further signal transmission between them is possible. A PIP short can affect both sides of the PIP as both logic levels now depend on each other. SEUs in the buffer control bits only affect the driven wire and do not have a direct feedback effect. Another routing effect are SEUs in the select line configuration of multiplexers (MUX). If these bits are changed, a different signal will be forwarded through the MUX.

**Figure 3.6:** Overview of SEU effects in routing and look-up tables. Programmable interconnect points (PIP) in the routing net can be shortened or opened affecting both sides of the PIP. Shorts or opens in buffers have only an effect on the load wire. Multiplexers controlled by configuration bits can select wrong signals on SEUs. A SEU in the LUT values leads to a change of the implemented logic function. SEU effects on flip-flops, CLB control bits or on any other FPGA block beside the CLBs are not shown in this picture. These images are taken from [GCZ03].

Both MUX, buffer and PIP shorts may increase the current consumption as wires driven with  $V_{dd}$  could get connected to grounded wires. According to the work of Sterpone & Violante, a single event upset can even have multiple effects on pairs of routing nets. The authors claim, that a single event upset can shorten two nets, delete multiple connections or re-route an existing net by deleting the old and adding a new net due to a decoded PIP configuration in Virtex FPGAs. Unfortunately, no studies on SEU routing effects for Virtex-4 devices could be found. The architecture and the arrangement of blocks in the FPGA changed since Virtex-I, but the principles should have stayed the same.

#### 3.3.2 SEUs in Slices

The main contents of the slices are a look-up table (LUT), a flip-flop (FF), several multiplexers, gates and wires connecting anything with each other as described in chapter 2. A single event upset in a LUT changes one of the memory cells. This implies a change of the currently implemented logic function and therefore can lead to a change of the device's functionality. The look-up tables of SLICEMs have the ability to be used as distributed memory or shift register. The operating mode is defined with configuration bits and can thus be changed by SEUs. Upsets in a flip-flop can directly change its content, but can also change its configuration. The initial- and reset values plus whether it is used as latch or flip-flop is defined with configuration bits. Another set of configuration bits controls whether the *clock*, *clock\_enable* or *reset* inputs are inverted. A SEU in these bits is likely to produce timing errors as the flip-flop may get its control signals at the wrong clock edge. The multiplexers and routing lines within the slices can be affected in the same way as described for the inter-slice routing.

#### 3.3.3 SEUs in I/O Buffers

The Virtex input/output buffers (IOBs) deliver a lot of configuration options. This configuration decides whether the buffer is used as input, output or bi-directional tri-state buffer and defines the electrical standard to be used out of 16 possibilities. Furthermore, each IOB contains three flip-flops to enable registering of the values read or to be written. Radiation induced configuration changes in these bits could have a large impact on the whole system of FPGA and its peripherals. The behavior of the Virtex IOBs in the presence of SEUs has been studied by Wirthlin, Rollins, Caffrey and Graham in 2002 [RWCG02]. They recognized that only one single bit out of 324 IOB configuration bits and two two-bit-combinations of flipped configuration bits were able to flip the IOB's output value or to actually change an input pin to an actively driven output pin for Virtex FP-GAs. The probability of destabilizing a whole system due to SEUs in the FPGA IOBs is therefore relatively low. As for the routing effects, no explicit Virtex-4 characterization of IOB SEU susceptibility could be found, but it looks like the IOBs did not change a lot.

#### 3.3.4 SEUs in BRAMs

The block RAM (BRAM) memories are made of SRAM storage cells as well, so they are also susceptible to SEUs. According to a Virtex-4 SEU study from George, Koga, Swift, Allen, Carmichael and Tseng in 2006 [GKS<sup>+</sup>06], the BRAMs have an even higher cross section for SEUs than the CLB configuration bits. The authors assume an explanation for this result in differences in the manufacturing. The CLB SRAM cells have larger channels, a thicker oxide and contain more metal than the BRAM cells. The actual cross sections for BRAMs and CLBs compared to Virtex-II devices in proton and heavy ion beam tests can be found in [GKS<sup>+</sup>06]. However, the number of BRAM bits on the FPGA is smaller than the number of CLB/IOB configuration bits, so the reduced probability of hitting a BRAM instead of an non-BRAM bit may mitigate this increased BRAM SEU cross section.

#### 3.3.5 SEUs in further Parts of the FPGA

According to [GKS<sup>+</sup>06], SEUs in Virtex-4 FPGAs can also affect the power-on-reset (POR) circuit initiating a full or partial reset of the FPGA. Furthermore, the configuration ports like JTAG or SelectMAP could be hit, interrupting configuration processes or requiring a power cycle to reconfigure the FPGA. An upset characterization of the PowerPC hard core processor implemented in the Xilinx FX series was done for both Virtex-II and Virtex-4 by Allen, Swift and Miller in 2007 [ASM07]. As the PowerPC core will not be available anymore in the further Virtex-6 / Spartan-6 devices, these characterizations become obsolete. A specific upset study on DSP-blocks, MGT-blocks or clock managers could not be found. Another effect that can be found in literature is the SEU susceptibility of *half latches*. Half latches keep a line on a defined potential and are more efficient than doing the same by using LUTs. These circuit elements showed an SEU susceptibility in the Virtex and Virtex-II FPGAs but are no concern for Virtex-4 FPGAs [ASCT07].

### 3.4 Multi Bit Upsets

The recent technology changes lead to continuously decreasing device structure sizes, whereas the regions affected by ionizing radiation remain unchanged. The probability of single ionizing particles affecting several transistor structures or several SRAM cells increases with decreasing technology size. The consequences are increasing numbers of multi bit upsets (MBUs), single particle strikes changing several SRAM cells at a time. The cross sections for multi bit upsets in Virtex, Virtex-II, Virtex-II Pro and Virtex-4 FP-GAs in proton and heavy ion beams are published in [QGK<sup>+</sup>05]. According to this source, MBUs have hardly been a problem in the first Virtex FPGAs but are an increasing concern for the newer devices. In proton tests with Virtex-4 devices, around 3% of all upsets can be identified as multi bit upsets. Heavy ion tests with Virtex-II and Virtex-II Pro FPGAs

demonstrated that up to a third of all events at the highest tested LET value were MBUs. The newer Virtex-5 FPGAs tested in  $[QMG^+07]$  reached even 59% of MBUs in all upsets with heavy ion tests.

## 4 State of the Art

This chapter gives an overview of the commonly known and used SEU and SET mitigation techniques. There are mitigation strategies for all abstraction layers starting from modified CMOS circuits applying at the lowest level up to radiation tolerant FPGA architectures. Redundancy and data encoding can be applied in the user logic to detect or correct upsets. The exploitation of FPGA features and combinations of several methods have shown an increased radiation tolerance. Mitigation aspects for higher abstraction layers are touched in the last part of this chapter.

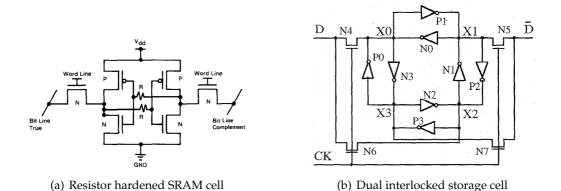

### 4.1 Radiation Hardened CMOS Logic

Any of the radiation effects described above rely on the principle of connecting differently doped silicon areas and voltage levels. A first effort would therefore be, to harden these CMOS cells against single event and cumulative effects. On the one hand, the amount of possible charge collection from a single particle can be decreased, one the other hand, the amount of charge required in a sensitive volume to flip a bit can be increased.

An approach to the first method is the use of an insulating layer between the doped areas and the substrate. These Silicon-on-Insulator (SOI) devices significantly reduce the amount of collectible charge as the depletion- and funneling regions are limited by the insulating layer. The complete isolation between n-well and p-well structures gives additionally an increased latch-up resistance, because parasitic pnpn-structures do not exist anymore [Fac99]. Another positive effect of SOI-structures is the reduced capacitance improving power consumption and maximum frequency. This layer is mostly made of silicon oxide or sapphire (Silicon-on-Sapphire, SOS). A similar approach, but with an increased area consumption, is the use of isolating guard rings around the transistors to remove parasitic transistors and to keep the substrate on a fixed potential [Bak07].

In order to increase the critical charge required in the sensitive volume, the capacitance of the nodes can be increased by increasing their size. A higher capacitance leads to a lower voltage swing with the same amount of charge collected. A popular approach is the use of additional resistors within the memory cell. These resistors affect the timing parameters of the cell and can compensate short current pulses. According to [Sch96], these resistors may not even increase the circuit area. A sample implementation is shown in figure 4.1(a).

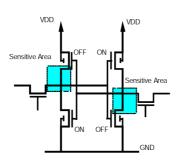

**Figure 4.1:** The resistor hardened memory cell (left) can compensate short current pulses. The image is taken from [KSR<sup>+</sup>88]. The principle of a dual interlocked storage cell (DICE) is shown on the right. The image is taken from [CNV96]. Both approaches decrease the SEU susceptibility of SRAM cells.

There are further approaches hardening SRAM cells by using different design techniques. An example is the dual interlocked storage cell (DICE) [CNV96] shown in figure 4.1(b). This cell uses redundancy on CMOS level to store multiple instances of the desired values. Even if one part of the cell is modified by SEUs, the remaining instances restore the correct state of the hit part. The advantage of approaches like this is that they just require a change in the cell design, not in the manufacturing process like the SOI approach. A similar approach was chosen in [BV93] by creating a heavy ion tolerant memory cell (HIT cell).

The main disadvantage of all of these CMOS techniques is the effort to build an FPGA with them. They are a good option for custom ASIC designs but would be too expensive for small series of FPGAs with radiation tolerant CMOS designs.

## 4.2 Radiation Tolerant FPGA Architectures

The commercial off-the-shelf (COTS) SRAM based FPGAs have shown to be susceptible to both, radiation induced single event effects and cumulative effects. Apart from these devices, there are several architectures and technologies delivering increased radiation tolerance to FPGAs. The main representatives are flash FPGAs, antifuse FPGAs and radiation hardened SRAM FPGAs.

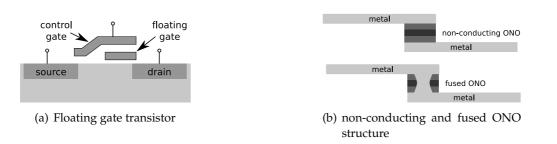

#### 4.2.1 Flash FPGAs

Flash memories are unlike SRAM cells non-volatile and therefore do not lose their stored value when powered off. The principle of flash memories relies on the use of floating gate

Figure 4.2: Flash and antifuse principles

transistors. The gates of these transistors are completely isolated from the other parts of the device. Above this floating gate is another control gate. By applying voltages on the control gate, the floating gate can be charged and uncharged by exploiting tunneling effects. Once the charge is deposited on the floating gate, it will remain there, regardless of whether the device is connected to a power supply or not. This non-volatile gate charge leads to a decreased power consumption compared to SRAM based implementations.

The main advantage of flash FPGAs regarding the operation in radiative environments is that the floating gate requires much more charge than a single ionizing particles can deposit or compensate. According to  $[SWC^+99]$ , a heavy ion with a LET of  $37 \frac{MeVcm^2}{mg}$  can only contribute less than 1% of the total charge on a floating gate. FPGAs built with this flash technology are therefore mostly resistant against single event upsets in the configuration memory. The user flip-flops are expected to be as susceptible to SEUs as their SRAM counterparts from the same manufacturing technology. SETs on the routing nets are still a concern. The effects of single event gate rupture (SEGR) are possible during configuration and the flash technology delivers no increased total ionizing dose resistance compared to SRAM based architectures of the same manufacturing process [SWC<sup>+</sup>99].

The disadvantage of flash based FPGAs is that they require additional manufacturing steps beyond the standard CMOS process and are therefore often some technology generations behind the newest CMOS technologies. Furthermore, the array structure of user configurable logic elements (*tiles*) is much simpler than in the Xilinx Virtex architectures and the supported clock frequencies are lower. The current flash FPGAs offer also on-chip RAM, but are missing things like digital signal processors (DSPs), multi gigabit transceivers(MGTs) or integrated Ethernet PHYs. Actel<sup>1</sup> is one of the most important manufacturers for flash based radiation hardened FPGAs.

## 4.2.2 Antifuse FPGAs

Another possibility to achieve increased radiation tolerance is the use of antifuse FPGAs. Actually antifuse FPGAs are more similar to ASICs than to SRAM FPGAs, as they are

<sup>&</sup>lt;sup>1</sup>http://actel.com

non-volatile and their configuration is writable only once. After that initial write, the configuration is static and cannot be changed anymore. These FPGAs use antifuse switches consisting of an oxide-nitride-oxide (ONO) layer sandwich. The programming can be done by applying high voltage pulses to the desired ONO structures and therefore fusing them. The TID resistance of current antifuse FPGAs is in the order of 300 krad [Act08] and the configuration can, due to its static nature, not be modified by SEUs. There are even antifuse FPGAs with SEU-hardened registers and integrated SRAM scrubbers like the Actel *RTAX-S/SL RadTolerant FPGA* [Act08] available for space applications. Those devices allow an excellent implementation of radiation tolerance, but their static nature denies any application requiring the ability to change the currently implemented design. An antifuse FPGA implementation of the LEON3FT fault tolerant softcore SPARC CPU system for avionic and space applications has been done by Actel in their *RTAX-S/SL* chips. The LEON3FT uses error correcting codes in any memories for up to four errors per 32 bit word or cache tag. A more detailed description of the LEON3FT Actel implementation can be found in [Aer09].

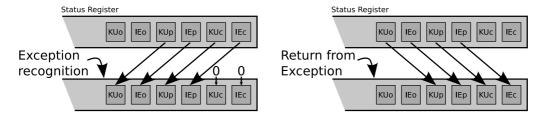

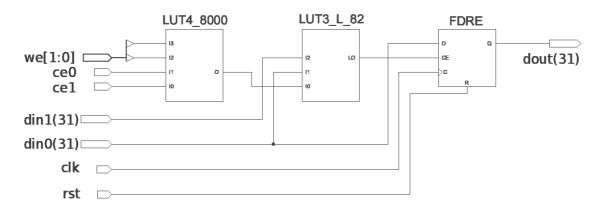

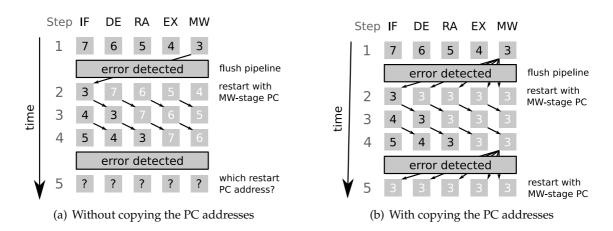

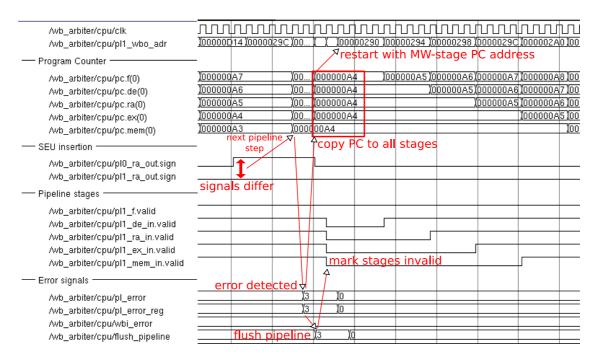

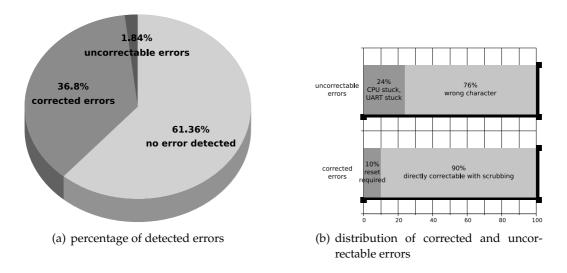

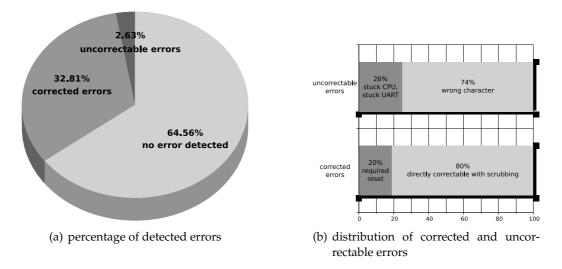

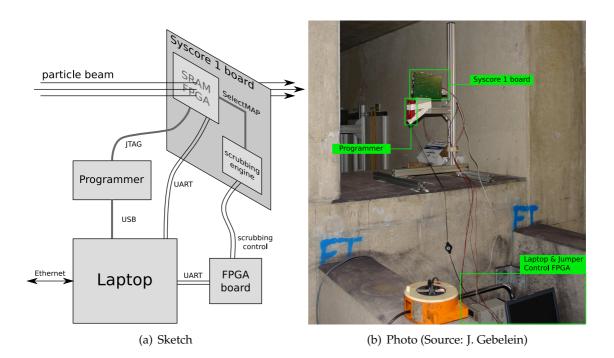

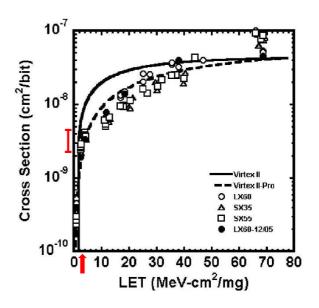

## 4.2.3 Radiation Tolerant Xilinx FPGAs