### DISSERTATION

submitted to the Combined Faculties for the Natural Sciences and for Mathematics

of the Ruprecht-Karls-Universität Heidelberg, Germany

for the degree of Doctor of Natural Sciences

presented by **Dipl.-Phys. Stefan Philipp**born in Hannover, Germany

Date of oral examination: July 2, 2008

Design and Implementation of a Multi-Class Network Architecture for Hardware Neural Networks

Referees: Prof. Dr. Karlheinz Meier

Prof. Dr. Ulrich Rückert

### Entwurf und Implementierung einer mehrklassigen Netzwerkarchitektur für Neuronale Netze in Hardware

Die vorliegende Arbeit beschreibt den Entwurf und die Implementierung einer Netzwerkarchitektur, welche Techniken von leitungsvermittelnden und paketvermittelnden Netzwerken verbindet, um zwei verschiedene Dienstgüten anzubieten: isochrone Verbindungen und paketbasierte Verbindungen mit bestmöglicher Zustellung. Isochrone Verbindungen verwenden reservierte Netzwerkresourcen, um eine verlustfreie Übertragung sowie eine niedrige Ende-zu-Ende Verzögerung mit begrenzter Varianz zu garantieren. Die Synchronisierung aller Netzwerkknoten sowie die Berechnung einer kompakten Reservierungsbelegung werden durch effiziente Algorithmen gelöst. Paket basierte Übertragungen verwenden die verbleibende Bandbreite. Das Multiplexen beider Verkehrsklassen wird von einem neuartigen Bypass-Switch geleistet, der skalierbar ist in der Anzahl der Schnittstellen sowie in der externen Bandbreite und ohne eine interne Beschleunigung auskommt. Die Netzwerkarchitektur kommt in der Forschung innerhalb des FACETS Projektes mit großskaligen künstlichen neuronalen Netzen in Hardware zum Einsatz, für die Vernetzung eines verteilten Systems aus VLSI neuronalen Netzen. Axonale Verbindungen zwischen Neuronen werden mit Hilfe von isochronen Verbindungen modelliert, wohingegen paket basierte Übertragung die Grundlage für eine systemweite gemeinsame Speicherarchitektur bildet. Der zur Laufzeit ausgeführte Teil des Netzwerkes ist in programmierbarer Logik implementiert und arbeitet mit einer externen Übertragungsrate von 3.125 Gbit/s. Die Arbeit diskutiert die anwendungsbezogenen Anforderungen an das Netzwerk, sowie dessen Entwurf und Referenzimplementierung in programmierbarer Logik und Software. Theoretische Überlegungen über die Leistungsfähigkeit werden durch Messungen und Simulationen verifiziert. Obwohl die Netzwerkarchitektur für die spezielle Anwendung mit neuronalen Netzen entworfen wurde, stellt sie eine generelle Lösung für alle Netzwerkumgebungen dar, welche isochrone Verbindungen und Paketvermittlung mit niedriger Komplexität benötigen. Die Architektur ist insbesondere für den Einsatz in der nächsten Stufe der Hardwareentwicklung des FACETS Projektes zur Vernetzung künstlicher neuronaler Netze auf Wafer-Ebene geeignet.

### Design and Implementation of a Multi-Class Network Architecture for Hardware Neural Networks

This thesis describes the design and implementation of a network architecture that combines techniques from circuit switching and packet switching to provide two different service classes: isochronous connections and best-effort packet transfers. Isochronous connections use reserved resources to provide loss-less transmissions as well as a low end-to-end delay with bounded jitter. Synchronization of all network nodes as well as computation of a compact reservation scheme is achieved by means of efficient algorithms. Best-effort packet transfers use the remaining bandwidth. Both traffic classes are multiplexed by a novel Bypass-Switch architecture, which is scalable in terms of port numbers and line speed and does not require internal speedup. The network architecture is employed within the experimental framework of the FACETS project for research into large-scale hardware neural networks, for which it interconnects a distributed set of VLSI neural networks. Isochronous connections model axonal inter-neuron connections whereas best-effort packet transfers are the basis for a framework-wide shared memory subsystem. The online part of the network architecture is implemented within programmable logic and operates at external line rates of 3.125 Gbit/s. The thesis discusses the service requirements of this kind of application, the design and the reference implementation of the network architecture in programmable logic and software. Theoretical results about the provided services are verified by means of measurements and simulations. Although implemented for a specific application, the developed network architecture is a general solution for all network environments that require isochronous connections and packet processing with low online complexity. It is particularly suitable for use within the next stage of the hardware development within the FACETS project for waver-scale interconnection of hardware neural networks.

# Contents

| Introd | uction   |                                         | 1  |

|--------|----------|-----------------------------------------|----|

| Chapte | er 1 - ( | Computer Networks                       | 5  |

| 1.1    | Netwo    | rk Topologies                           | 5  |

| 1.2    |          | nce Models                              | 6  |

|        | 1.2.1    | The OSI Reference Model                 | 7  |

|        | 1.2.2    | Alternative Models                      | 10 |

|        | 1.2.3    | Encapsulation of Data Formats           | 10 |

| 1.3    | Circui   | t Switching and Packet Switching        | 11 |

| 1.4    | Qualit   | y of Service                            | 12 |

|        | 1.4.1    | Services Guaranteed by the Network      | 13 |

|        | 1.4.2    | Techniques to Provide QoS               | 14 |

| 1.5    | Packet   | Switching Architectures                 | 16 |

|        | 1.5.1    | General Architecture of a Packet Switch | 16 |

|        | 1.5.2    | Output-Queued Crossbar Switches         | 17 |

|        | 1.5.3    | Input-Queued Crossbar Switches          | 18 |

|        | 1.5.4    | Combined Input-Output Queued Switches   | 19 |

|        | 1.5.5    | Further Switch Architectures            | 20 |

| 1.6    | Queui    | ng Schedulers                           | 20 |

|        | 1.6.1    | Schedulers to Access a Single Resource  | 21 |

|        | 1.6.2    | Crossbar Schedulers                     | 23 |

| 1.7    | Summ     | ary                                     | 27 |

| Chapte | er 2 - I | Framework Description                   | 29 |

| 2.1    | Artific  | ial Neural Network ASICs                | 29 |

|        | 2.1.1    | The HAGEN Chip                          | 30 |

|        | 2.1.2    | The Spikey Chip                         | 34 |

| 2.2    | The F.   | ACETS Stage 1 Framework                 | 39 |

|        | 2.2.1    | Nathan Network Module                   | 39 |

|        | 2.2.2    | Backplane and Control PC                | 42 |

|        | 2.2.3    | Connectivity                            | 42 |

|        | 2.2.4    | SlowControl and PowerPC Operation       | 44 |

| 2.3    | Neura    | l Network Experiments                   | 46 |

|        | 2.3.1    | Experimental Setups                     | 46 |

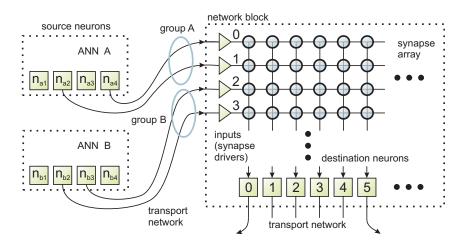

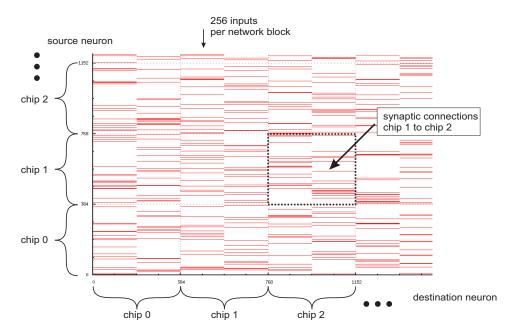

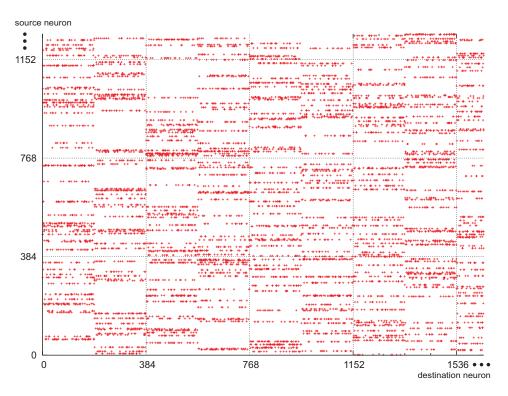

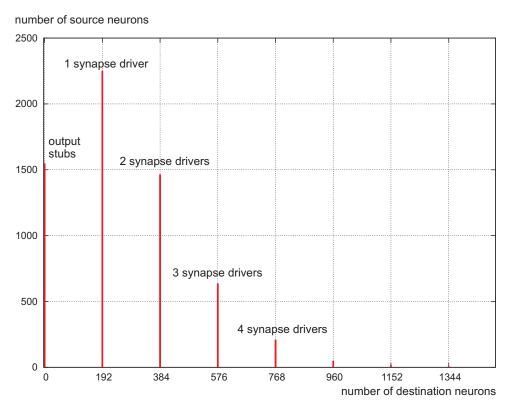

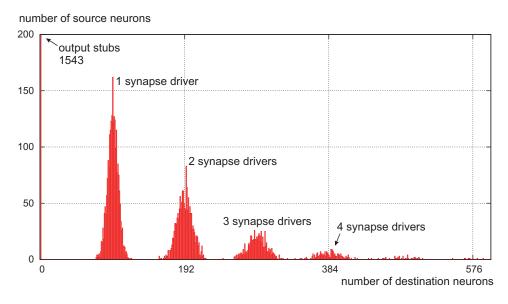

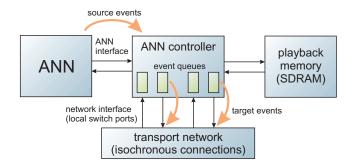

|        | 2.3.2    | Interconnecting Multiple ANN Chips      | 48 |

|        | 2.3.3    | Neuron Mapping                          | 49 |

II CONTENTS

| 2.4   | The T                 | ransport Network                                     |

|-------|-----------------------|------------------------------------------------------|

|       | 2.4.1                 | Design Considerations                                |

|       | 2.4.2                 | Transport of Neural Network Data                     |

|       | 2.4.3                 | Transport of Non-Neural Network Data                 |

|       | 2.4.4                 | Summary of the Service Requirements                  |

|       | 2.4.5                 | Existing Solutions                                   |

|       | 2.4.6                 | Concept of the Transport Network                     |

| 2.5   | Summ                  | ary                                                  |

| Chapt | or?                   | The Multi-Class Gigabit Network Architecture 65      |

| 3.1   |                       | iew                                                  |

| 9.1   | 3.1.1                 | Merging of Traffic Classes                           |

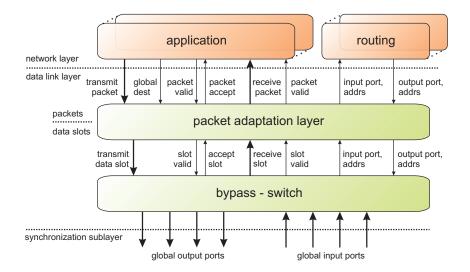

|       | 3.1.1                 | Network Protocol Stack                               |

| 3.2   |                       | ng Strategy                                          |

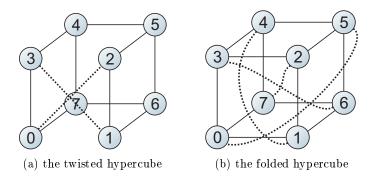

| J.∠   | 3.2.1                 | Network Topology                                     |

|       | $\frac{3.2.1}{3.2.2}$ | Formal Description                                   |

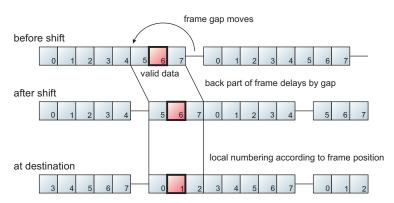

|       | $\frac{3.2.2}{3.2.3}$ | Framing of Bandwidth                                 |

| 9 9   |                       | ork Initialization Phase                             |

| 3.3   | 3.3.1                 |                                                      |

| 9.4   |                       | Parameter Selection                                  |

| 3.4   | 3.4.1                 | Model of the Isochronous Switch                      |

|       | 3.4.1 $3.4.2$         |                                                      |

|       | $\frac{3.4.2}{3.4.3}$ |                                                      |

|       | $\frac{3.4.5}{3.4.4}$ | v .                                                  |

|       | 3.4.4 $3.4.5$         | 11 0                                                 |

|       | $\frac{3.4.5}{3.4.6}$ | 0                                                    |

| 3.5   |                       |                                                      |

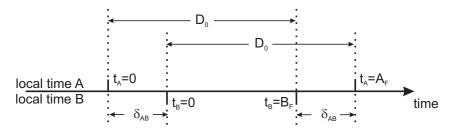

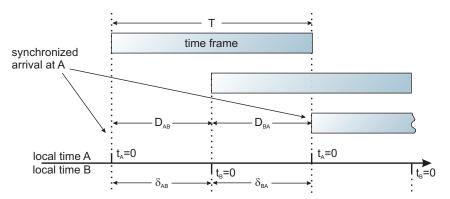

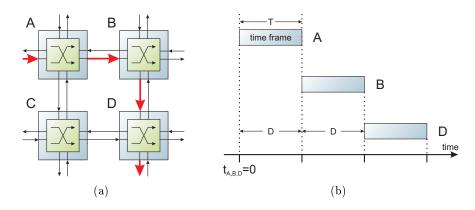

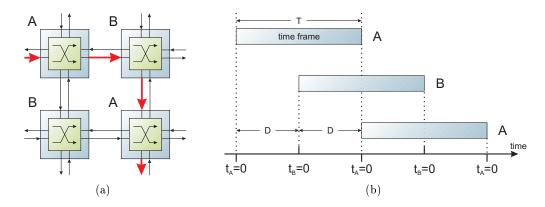

| 5.5   | 3.5.1                 | l Synchronization                                    |

|       | $\frac{3.5.1}{3.5.2}$ |                                                      |

|       | 3.5.2                 | ±                                                    |

|       | 3.5.4                 |                                                      |

|       | 3.5.4 $3.5.5$         | Timing Scheme of the Switch                          |

|       | 3.5.6                 |                                                      |

|       |                       | 8                                                    |

|       | $\frac{3.5.7}{3.5.8}$ | Synchronization Result                               |

| 3.6   |                       |                                                      |

| 5.0   | 3.6.1                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|       | 3.6.2                 |                                                      |

|       | $\frac{3.0.2}{3.6.3}$ | Bandwidth Quantization                               |

|       | $\frac{3.0.3}{3.6.4}$ | 9                                                    |

|       |                       | 9                                                    |

|       | $3.6.5 \\ 3.6.6$      | Overall Algorithm Result                             |

| 9 7   |                       | Further Remarks                                      |

| 3.7   | •                     | Results for Isochronous Connections                  |

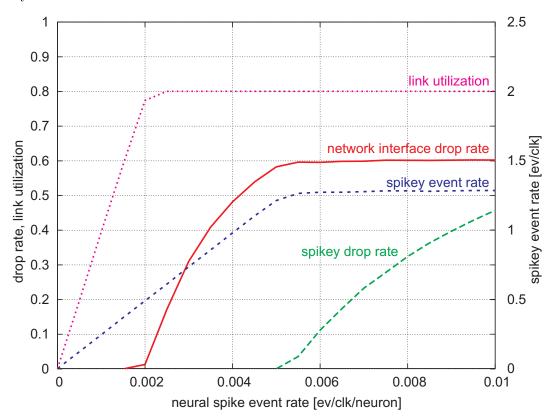

|       | $\frac{3.7.1}{2.7.2}$ | Throughput and Drop Rate                             |

|       | $\frac{3.7.2}{2.7.2}$ | Reliability                                          |

|       | $\frac{3.7.3}{2.7.4}$ | Delay                                                |

|       | 3.7.4                 | Jitter                                               |

CONTENTS

|       | 3.7.5  | Summary                                                                                                                 | 119 |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------|-----|

| 3.8   | Servic | e for Packet-Based Transports                                                                                           |     |

|       | 3.8.1  | Packet Embedding                                                                                                        |     |

|       | 3.8.2  | Packet Format                                                                                                           |     |

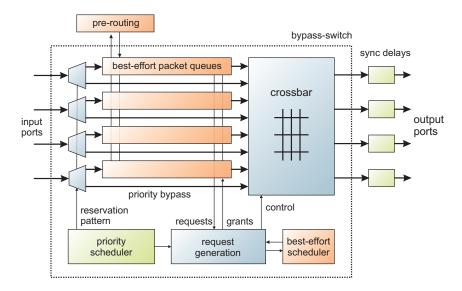

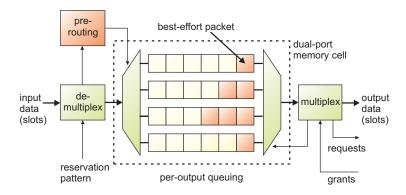

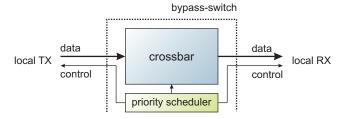

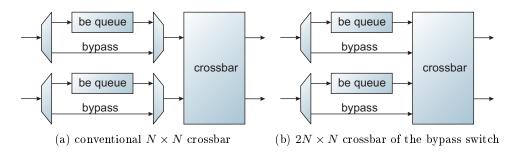

|       | 3.8.3  | The Bypass-Switch                                                                                                       |     |

|       | 3.8.4  | Interface to Upper Layers                                                                                               |     |

|       | 3.8.5  | Packet Routing                                                                                                          |     |

| 3.9   | Scalab | oility and Complexity                                                                                                   |     |

|       | 3.9.1  | Space Complexity                                                                                                        |     |

|       | 3.9.2  | Time Complexity                                                                                                         |     |

| 3.10  | Summ   | nary                                                                                                                    |     |

|       |        | Future Work                                                                                                             |     |

| Chant | on 1   | Implementation of the Transport Naturals                                                                                | 135 |

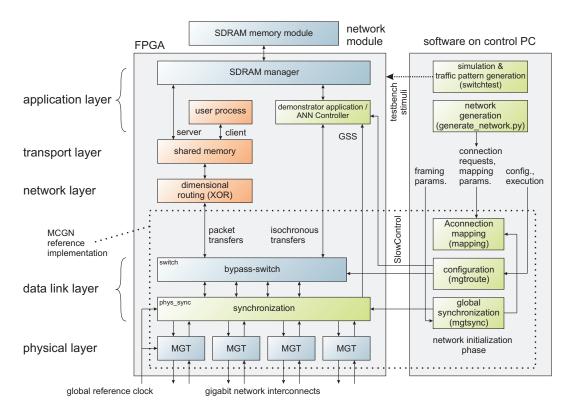

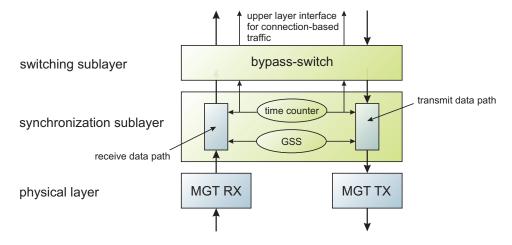

| 4.1   |        | $egin{aligned} 	ext{Implementation of the Transport Network} \ 	ext{iew} & \dots & \dots & \dots & \dots \end{aligned}$ |     |

| 4.1   |        | ng and Packet Encoding                                                                                                  |     |

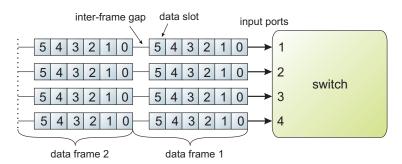

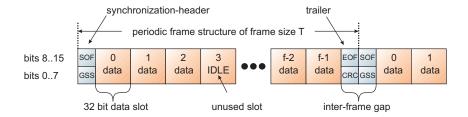

| 4.2   | 4.2.1  | Format of a Data Frame                                                                                                  |     |

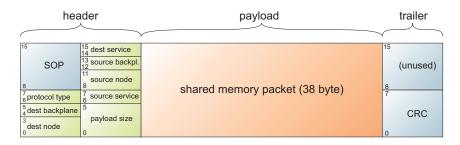

|       | 4.2.1  | Format of a Best-Effort Packet                                                                                          |     |

|       | 4.2.3  | Notification of the Slot Usage                                                                                          |     |

| 4.3   |        | Physical Layer                                                                                                          |     |

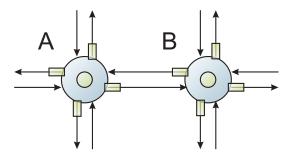

| 4.0   | 4.3.1  | Network Topology                                                                                                        |     |

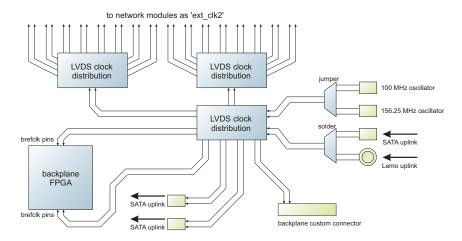

|       | 4.3.2  | Distribution of the Global Reference Clock                                                                              |     |

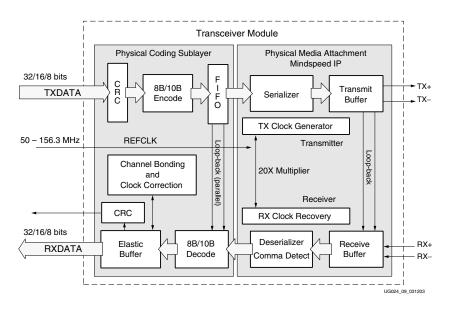

|       | 4.3.3  | The Multi-Gigabit Transceiver                                                                                           |     |

|       | 4.3.4  | Configuration of the MGTs                                                                                               |     |

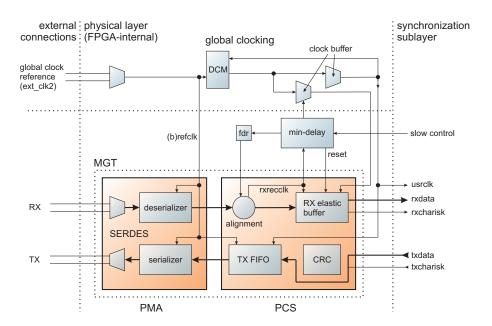

| 4.4   |        | ynchronization Sublayer                                                                                                 |     |

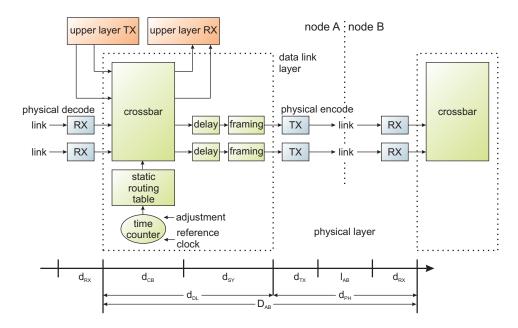

| 1.1   | 4.4.1  | Timing of the Network Node                                                                                              |     |

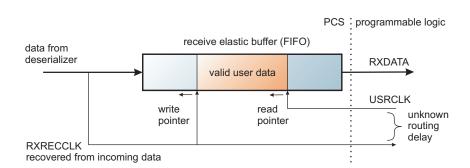

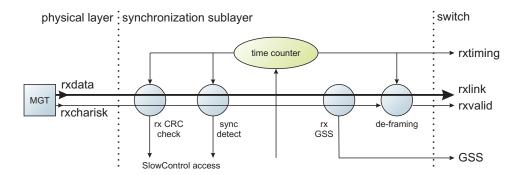

|       | 4.4.2  | Reception of Data                                                                                                       |     |

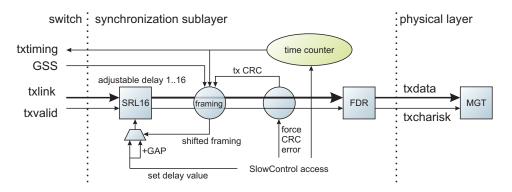

|       | 4.4.3  | Transmission of Data                                                                                                    |     |

|       | 4.4.4  | Selection of the Synchronization Parameters                                                                             |     |

|       | 4.4.5  | Global Synchronous Signals                                                                                              |     |

| 4.5   |        | mentation of the Bypass-Switch                                                                                          |     |

| 1.0   | 4.5.1  | Characterization                                                                                                        |     |

|       | 4.5.2  | Overview of the Switch                                                                                                  |     |

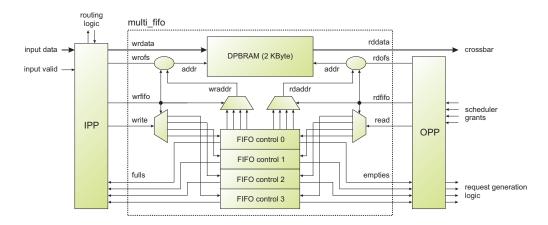

|       | 4.5.3  | Implementation of the Input Buffers                                                                                     |     |

|       | 4.5.4  | Implementation of the Switch Core                                                                                       |     |

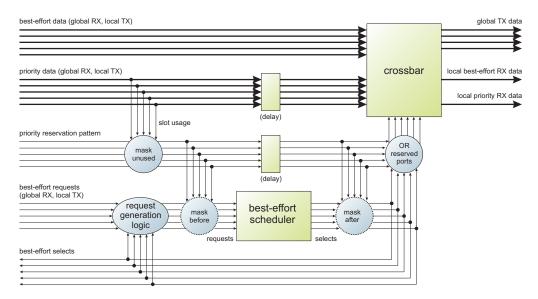

|       | 4.5.5  | Implementation of the Central Crossbar                                                                                  |     |

|       | 4.5.6  | Interface to the Best-Effort Scheduler                                                                                  |     |

|       | 4.5.7  | Interface to Upper Network Layers                                                                                       |     |

| 4.6   |        | mentation of the Best-Effort Scheduler                                                                                  |     |

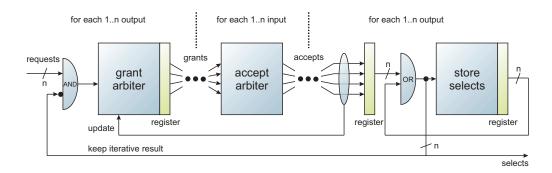

|       | 4.6.1  | Implementation of the iSLIP Scheduler                                                                                   |     |

|       | 4.6.2  | Implementation of Two-Dimensional Schedulers                                                                            |     |

|       | 4.6.3  | Summary                                                                                                                 |     |

| 4.7   |        | ng of Best-Effort Packets                                                                                               |     |

|       | 4.7.1  | Description of the Implemented Algorithm                                                                                |     |

|       | 4.7.2  | Summary                                                                                                                 |     |

| 4.8   | Trans  | port of Neural Network Data                                                                                             |     |

|       | 4.8.1  | Provided Transport Service for Neural Network Data                                                                      |     |

IV CONTENTS

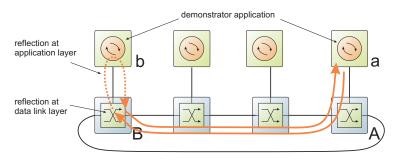

|         | 4.8.2    | Demonstrator Application for Isochronous Transfers           |             |

|---------|----------|--------------------------------------------------------------|-------------|

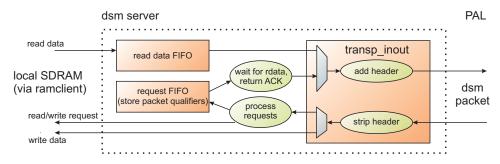

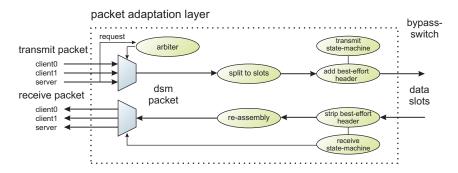

| 4.9     | Distrib  | buted Shared Memory                                          | 183         |

|         | 4.9.1    | Overview                                                     | 184         |

|         | 4.9.2    | Functional Description                                       | 185         |

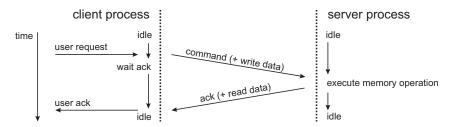

|         | 4.9.3    | The Client Process and the User Interface                    | 187         |

|         | 4.9.4    | The Server Process                                           | 188         |

|         | 4.9.5    | The DSM Packet Adaptation Layer                              | 189         |

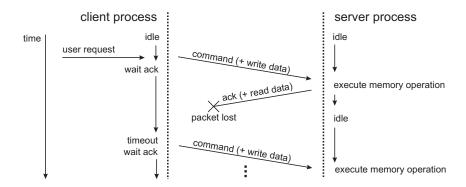

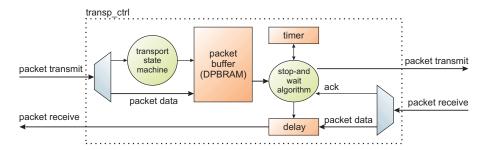

|         | 4.9.6    | Transport Control Protocol                                   | 190         |

|         | 4.9.7    | DSM Performance                                              | 193         |

|         | 4.9.8    | Summary                                                      | 197         |

| 4.10    | Softwa   | are Development                                              | 197         |

|         | 4.10.1   | Synchronization                                              | 198         |

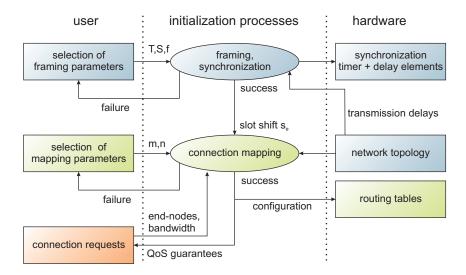

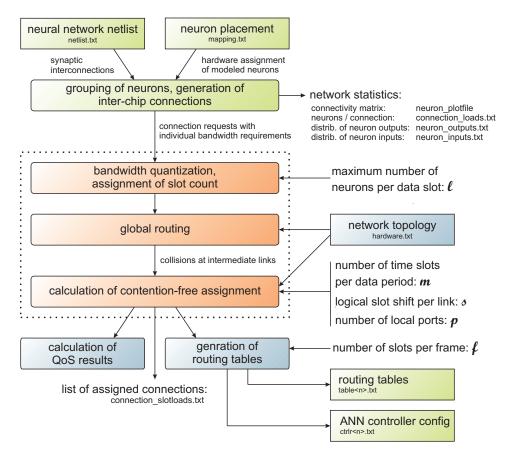

|         | 4.10.2   | Connection Mapping                                           | 200         |

|         | 4.10.3   | Configuration of the Routing Tables                          | 203         |

|         | 4.10.4   | Generation of Pseudo-Random Networks                         | 204         |

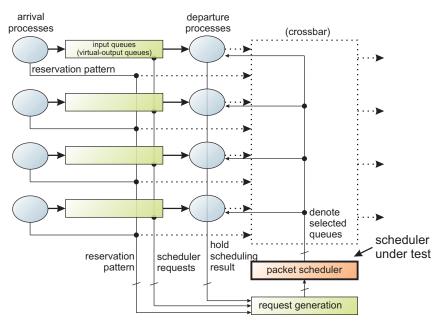

|         | 4.10.5   | High-Level Simulation of the Packet-Switch incl. Scheduler . | 205         |

| 4.11    | Summ     | ary                                                          | 208         |

| Chapt   | er 5 - 1 | Evaluation                                                   | 211         |

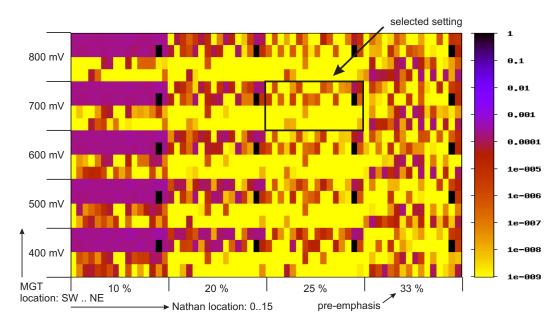

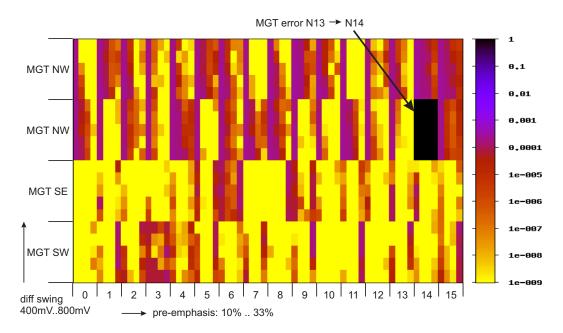

| 5.1     | Evalua   | ation of the Physical Layer                                  | 211         |

|         | 5.1.1    | Measurement of the Data Reliability                          | 211         |

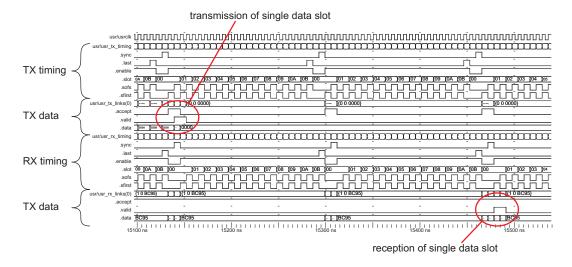

| 5.2     | Evalua   | ation of the Synchronization Sublayer                        | 213         |

|         | 5.2.1    | Measurement of the Transmission Delays                       | 213         |

|         | 5.2.2    | Establishment of the Synchronization                         | 214         |

| 5.3     | Verific  | ation of the Transport of Isochronous Data                   | 216         |

|         | 5.3.1    | Measurement of Application-Layer Delays                      | 216         |

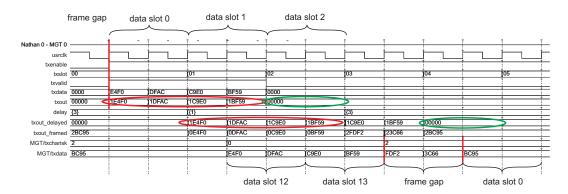

|         | 5.3.2    | Verification of Isochronous Transfers                        | 218         |

| 5.4     | Discus   | ssion of the Neural Network Topologies                       | 220         |

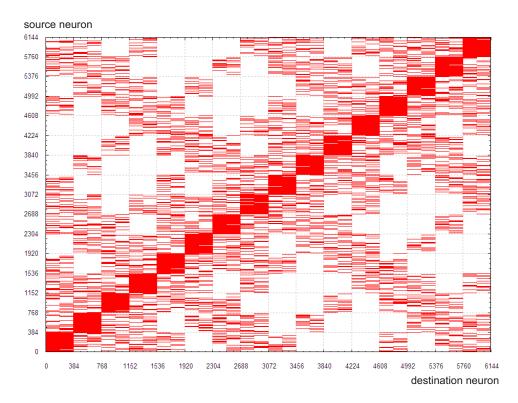

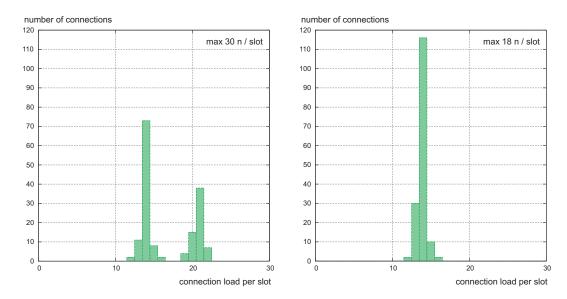

|         | 5.4.1    | Characterization of Neural Network Topologies                | 221         |

|         | 5.4.2    | Calculations for Neural Networks on the Backplane            | 223         |

|         | 5.4.3    | Homogeneous Pseudo-Random Networks                           |             |

|         | 5.4.4    | Modified Pseudo-Random Networks                              | 226         |

|         | 5.4.5    | Summary of the Evaluated Network Topologies                  | 233         |

| 5.5     | Evalua   | ation of the Connection Mapping Algorithm                    | 233         |

|         | 5.5.1    | Evaluated Qualifiers                                         | 234         |

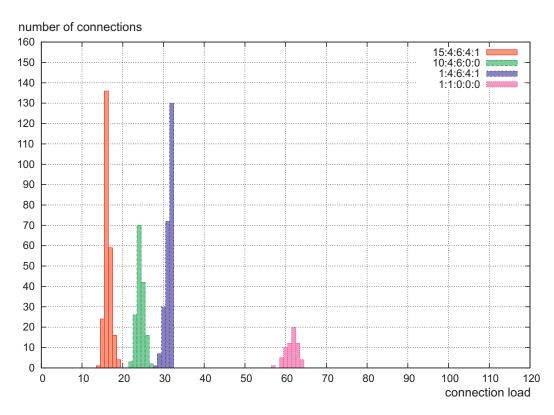

|         | 5.5.2    | Mapping Results of Pseudo-Random Networks                    | 236         |

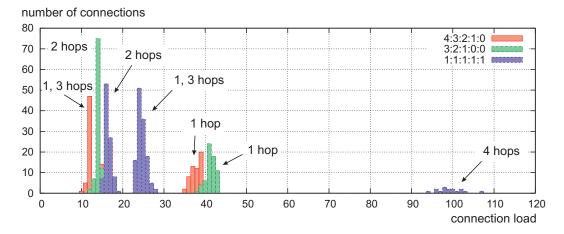

|         | 5.5.3    | Mapping Results of Networks with non-Intrinsic Hop Ratios .  | 237         |

|         | 5.5.4    | Mapping Results of Alternative Hardware Topologies           | 239         |

|         | 5.5.5    | Summary                                                      | 243         |

| 5.6     | High-I   | Level Simulation of the Neural Data Transport                | 243         |

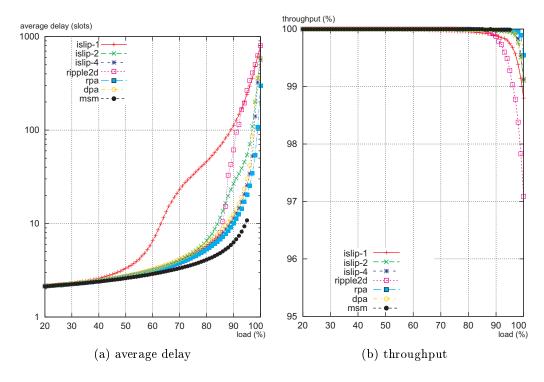

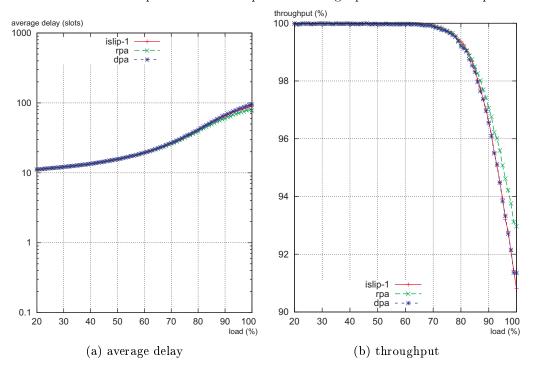

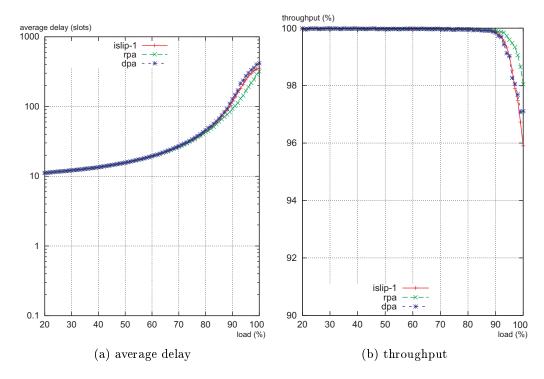

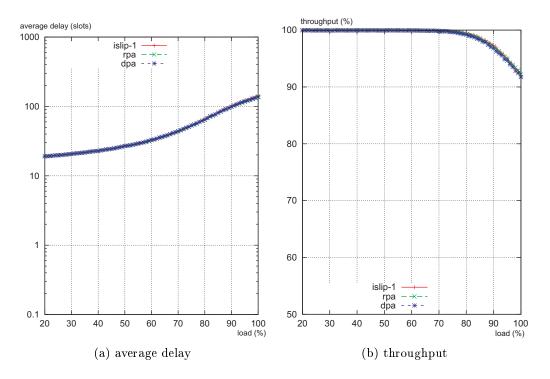

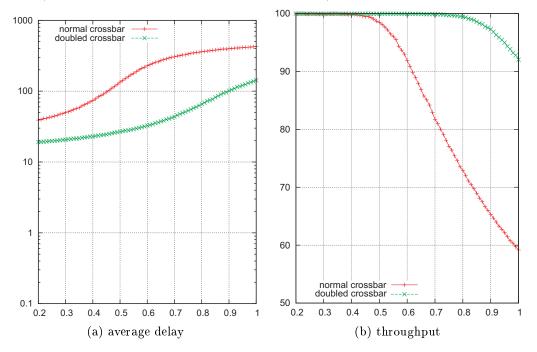

| 5.7     | Perfor   | mance of the Best-Effort Schedulers                          | 246         |

| 5.8     | Summ     | ary                                                          | 250         |

| Conclu  | ision a  | nd Outlook                                                   | <b>25</b> 3 |

| List of | Acron    | ivms                                                         | 259         |

| CONTENTS | V |  |

|----------|---|--|

| List of Symbols                                          | 263 |

|----------------------------------------------------------|-----|

| List of Figures                                          | 267 |

| List of Tables                                           | 270 |

| Appendix 1 - Resource Consumption of FPGA Implementation | 271 |

| Bibliography                                             | 284 |

VI CONTENTS

## Introduction

The human brain is one of the most complex and powerful information processing systems. It is able to solve computational tasks that are far beyond the possibilities of artificial computational systems and still consumes only about 20 Watts of power. Better understanding of this highly efficient system has been a research goal since ancient times. Although the basic principles of its functionality are being researched intensively, a comprehensive understanding of its operation is still not existent. Moreover, no artificial system built by humans has ever reached a level of complexity that is comparable to that of the human brain.

The study of the brain has been an inspiration for the development of computational neuron models and artificial neural networks (ANNs). A first important but rather simple model that uses a threshold function over the sum of binary input values has been developed in 1943 by W. McCulloch and W. Pitts [83]. An important step forward has been made by Rosenblatt in 1958 [119], who introduced the perceptron network that consists of neurons that use continuous input and output values and a continuous transfer function. Both models are rather abstract and computational than a correct image of a biological neural network. One of the most important progresses has been made in 1952 by A. L. Hodgkin and A. F. Huxley, who developed a neuron model closer to biology [52]. It is oriented along the physiological processes within the cells and includes the generation and propagation of action potentials, or spikes between the neurons. The model of Hodgkin and Huxley formulates the influence of voltage-gated ion channels, leak channels and ion pumps through the cell membrane on the electric potential with differential equations.

To get a better understanding of neural information processing, it is required to combine a larger number of neurons to an ANN. Doing so, the computing time to solve the differential equations becomes the limiting factor for the size of the modeled networks. Especially if plasticity, diversity and temporal development are part of the model, the available computing power will be quickly insufficient to explore the timescales involved [124]. In contrast to the human nervous system, where 100 billions of neurons and about 10<sup>16</sup> synapses operate in parallel in continuous time, a software simulation reaches complexities in the order of 10<sup>3</sup> neurons in real-time with a simple Hodgkin-Huxley-based integrate-and-fire model on the fastest available microprocessors [97]. One solution to overcome this issue is to use a powerful parallel computer [80].

Progress in microelectronics makes it possible to implement physical neuron models using very large scale integration (VLSI) circuits with complementary metal oxide semiconductor (CMOS) technology to exploit the parallel nature of a neural network. In a physical model, important physiological quantities like the membrane potential

2 INTRODUCTION

are assigned an equivalent physical quantity. The variables of the differential equations of the neuron models are represented by electrical counterparts like voltages, currents and capacitances. The implementation of spiking neuron models in VLSI hardware has been done by several scientific groups. The work in [34] implemented Hodgkin-Huxley neurons in hardware. The group in [50] implemented spiking neurons with a time-dependent learning rule. Both designs are limited to a small number of neurons per chip due to the complexity of the model.

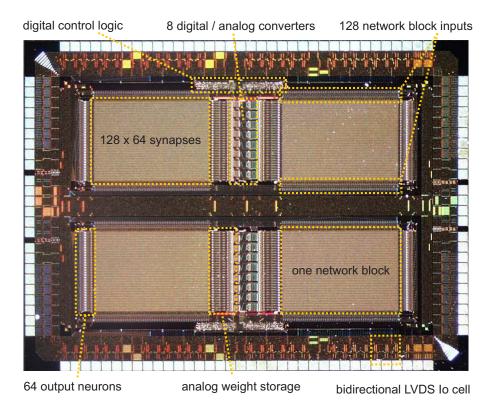

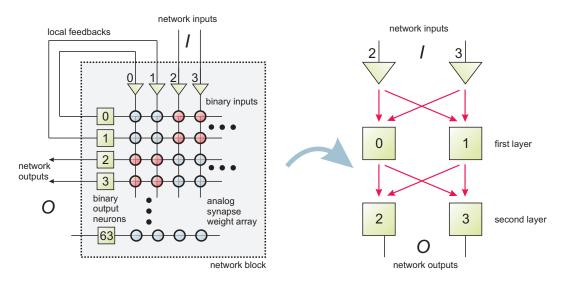

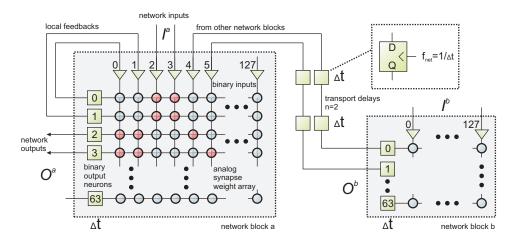

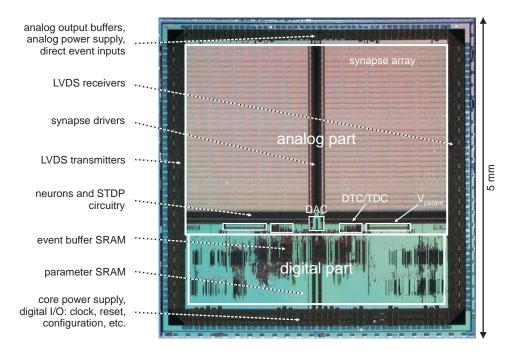

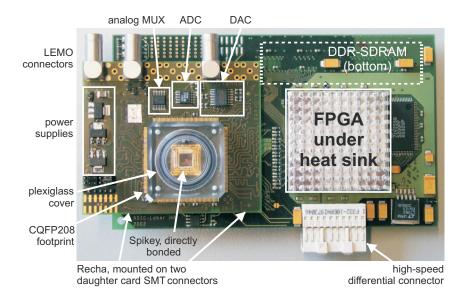

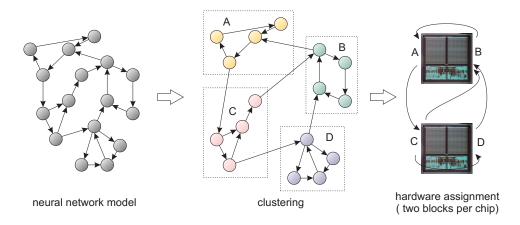

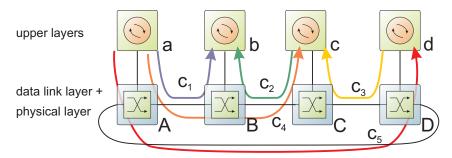

A different approach has been taken by the Electronic Vision(s) research group in Heidelberg in the course of the European projects SenseMaker [128] and its successor FACETS [89]. Two chips have been developed, whose VLSI designs use a less complex neuron model, with the benefit of several hundreds of artificial neurons per chip in a power-efficient design. The chip HAGEN [123] provides 256 perceptronbased neurons and the more recent chip Spikey [124, 122, 47] comprises 384 leaky integrate-and-fire neurons at an average acceleration factor of about 10<sup>4</sup> compared to biology. The synaptic interconnections of the neurons are established on-chip within configurable matrices, allowing a wide range of network topologies to be investigated on a single device. The Spikey chip provides plasticity as spike time dependent plasticity (STDP) within each individual synapse. Although both chips use different neuron models, they follow the same key idea: combining the advantages of analog VLSI techniques for the implementation of the neural circuits with the advantages of digital communication between the chips. The HAGEN chip has been used for a wide range of experiments including pattern recognition [39, 38], classification experiments based on evolutionary algorithms [55, 54, 53, 125] and the adaptation of liquid computing [127].

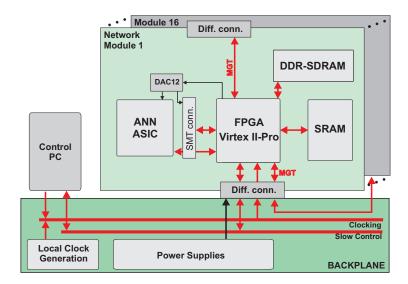

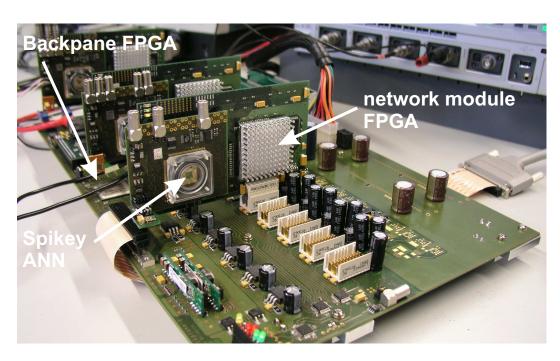

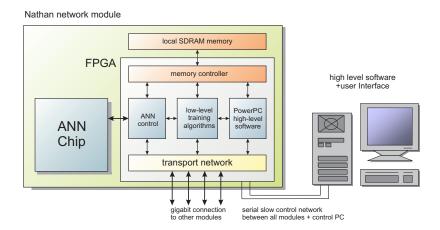

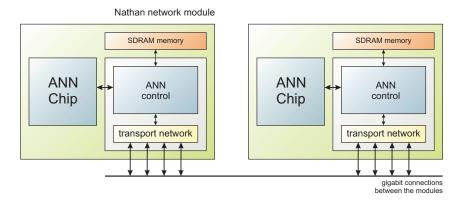

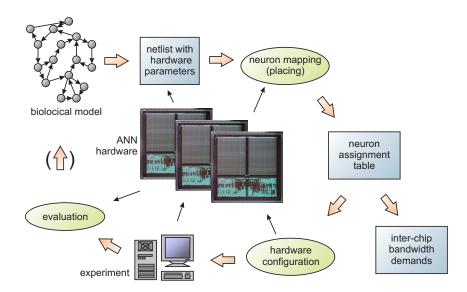

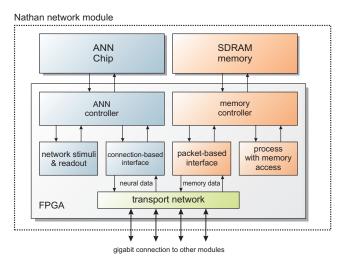

The pure digital interface of the developed chips makes it possible to extend the implemented networks beyond chip boundaries. Multiple chips can be interconnected to large-scale neural networks with several thousands of neurons. Connections between neurons on different chips then correspond to axonal connections of biological neurons. The physical infrastructure for this setup is provided by Stage 1 of the FACETS project, which consists of backplanes equipped with network modules each hosting an ANN chip [46, 39]. The framework requires a transport network to establish the neural interconnects, for which it provides programmable logic. Since the data to be transferred is digital, the transport network may use techniques and protocols of existing computer networks to perform this task.

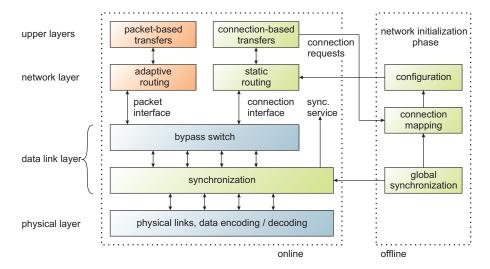

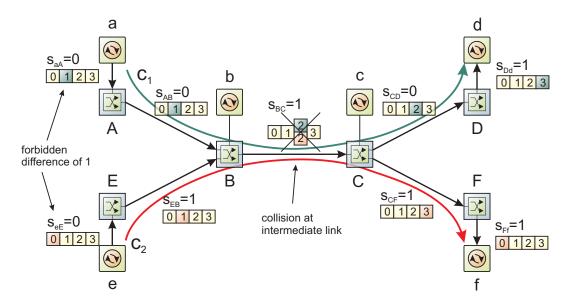

The challenge in designing the transport network is not only a required low online complexity, but also the large number of inter-neuron connections with strict service requirements on the timing and on the throughput of the transmitted neural data. Or to keep to the terms of computer networks: A large-scale ANN requires certain guarantees of quality of service (QoS). In particular, the operation of the chips relies on isochronous connections with a low and nearly constant connection delay and a guaranteed throughput due to the biological nature of the connections.

Besides the pure neural data, the experiments to be carried out require additional on-demand transfers for configuration data like synapse parameters, neuron parameters or the transport of network stimuli and monitored neural behavior. These data cannot be transferred within isochronous connections due to the latency and the complexity of their setup. Since a pre-reservation of permanent connections would lead to a bandwidth waste, a packet-based approach is more suitable.

INTRODUCTION 3

Although a wide range of network architectures have been published, only few of them provide isochronous connections combined with best-effort packet transfers and have only low online complexity. Well-established network architectures like asynchronous transfer mode (ATM) [143] are far too complex to be implemented within the limited space of the programmable logic of the framework. Packet switching approaches seem to be more suitable, but there is currently no switch design or scheduler design that provides a small enough end-to-end delay and jitter for a neural network application combined with low online complexity. Isochronous network architectures have been proposed [159, 40], but do not guarantee the throughput of the reserved bandwidth in all cases. Combined architectures using slotted timing have been presented for networks-on-chips (NoCs) in [35, 117], but the first design is based on asynchronous logic and does not scale, whereas the latter does not provide the required synchronization and slot allocation algorithms for a distributed setup like the Stage 1 framework.

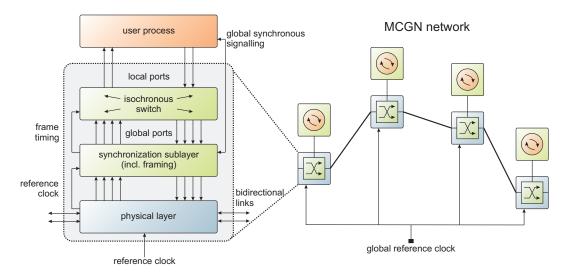

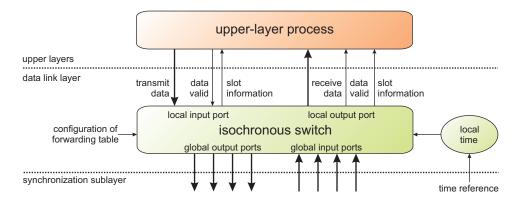

This thesis proposes a network architecture that combines techniques of circuit switching and packet switching to fulfill these requirements. A reference implementation of the architecture operates as the transport network of the FACETS Stage 1 framework for research into large-scale ANNs. Moreover, the network architecture is scalable to be used in the succeeding Stage 2 hardware of the FACETS project [121] for wafer-scale integration of hardware neural networks. Finally, the application of the network architecture is not limited to hardware neural networks, but is a general solution for all environments with demands for isochronous connections and packet-based transfers for which a compact implementation in programmable logic is needed.

### Thesis Overview

The thesis is organized as follows: The first chapter gives a brief survey of the basic principles of computer networks with focus on the provision of end-to-end QoS in packet switching networks. The second chapter presents the Stage 1 framework of the Electronic Vision(s) research group in Heidelberg. It concludes with a list of service requirements on the transport network according to the ANN application. Chapter three introduces the novel network architecture multi-class gigabit network (MCGN) and describes the framing strategy, the synchronization concept, the resource reservation algorithm as well as the traffic class multiplexing in detail. Chapter four describes the implementation of the transport network within the Stage 1 framework, which uses the reference implementation of MCGN for its lower network layers. Chapter five covers the evaluation and the verification of the implemented services by means of simulations and measurements. It is further discussed how the properties of different neural network topologies influence the possible average spike frequencies of the artificial neurons according to the bandwidth provided.

4 INTRODUCTION

## Chapter 1

## Computer Networks

The network architecture presented in this thesis has been developed to operate within a distributed setup of hardware neural networks in an embedded environment. However, its design techniques are borrowed from computer networks. This chapter introduces the basic terms, concepts and protocols of computer networks. The description starts with network topologies and reference models and introduces the concept of network layers. The switching techniques circuit switching and packet switching are described. Since the transport of neural network data requires guaranteed throughput and a low and constant transmission delay, the chapter continues with the description of QoS. The provision of QoS is described with focus on the design of packet switches and scheduling policies. The limited size of the thesis does not allow a detailed discussion of the complex matter. The descriptions are therefore given briefly and the interested reader may refer to [143, 110].

### 1.1 Network Topologies

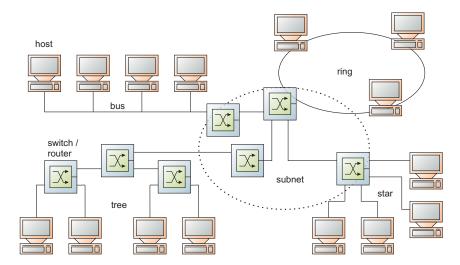

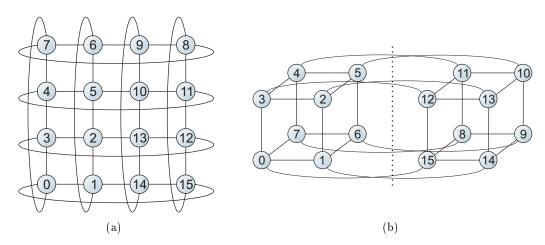

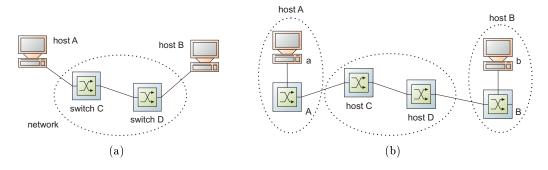

The nodes of a network can be divided into end-nodes and interconnecting nodes. The end-nodes are called hosts, whereas the interconnected nodes are called routers or switches (see below). Each node of a network is individually addressable via its dedicated network address. The network to be considered can be divided into several subnets. Subnets that contain multiple hosts are called local area networks (LANs). The LANs can be of a different network type and may have their own addressing format for the hosts. Figure 1.1 shows a network of 16 hosts, which are interconnected via a single subnet.

Different network topologies are conceivable: ring, bus, star, cubic, tree, mesh etc. The particular topologies require different methods for the access of the medium

Figure 1.1: Example network of 16 hosts organized in 4 local area networks of different topology. The hosts are interconnected via switches and routers.

and have different trade-offs for the access latency, the throughput per host or the medium costs.

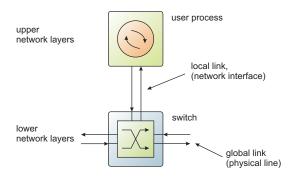

### 1.2 Reference Models

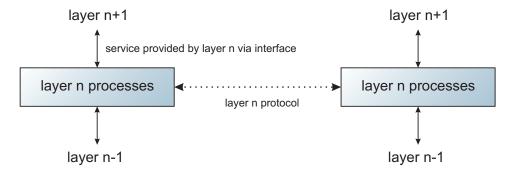

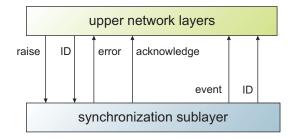

network layers and nomenclature The different functionalities of networks are usually organized into several network layers to reduce the design complexity. The layers are ordered by abstraction. The lowest network layer performs the access to the physical transmission medium. Each network layer contains a certain set of processes, which provide a set of services to the layer above and use the services from the layer below. The services define the functionalities the network layer provides and not how they are implemented. The communication between two stacked layers is performed via the corresponding interface between it. The interface defines the the basic operations to use the provided services. The communication between processes at different locations on the same layer is called a protocol. The entities at the different locations that communicate via a protocol are called peers. Figure 1.2 shows a schematic of a network layer protocol.

Figure 1.2: A network layer protocol provides a service to its layer above.

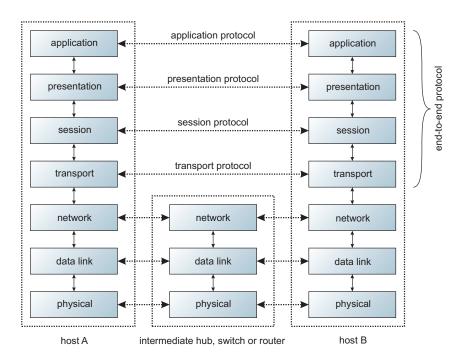

Figure 1.3: The seven-layer OSI reference model

Different reference models exist that define the purpose of the protocols and their basic functionalities within the layers. However, the implementation of certain functionalities is often not strictly limited to a particular layer. As an example, the tasks flow control, error detection or encryption are useful within both lower and higher network layers.

#### 1.2.1 The OSI Reference Model

An important and general model to be discussed is the open systems interconnection (OSI) reference model [163], which is shown in figure 1.3. It consists of seven layers with the physical layer being the lowest layer and the application layer on top.

### The Physical Layer

The physical layer accesses the physical medium to perform the transmissions between adjacent network nodes. The physical medium is conceptually located below the physical layer. The physical layer therefore defines mechanical and electrical standards, e.g. how the bits of the data streams are encoded, the pinouts of connectors, the voltage levels of electrical signals or the used transmission frequencies. Example processes of the physical layer are the data encoding and the data decoding.

Repeaters or hubs can be used to extent the size of a physical medium. Both devices operate basically within the physical layer. Repeaters refresh incoming signals on their way to the destination to enhance the transmission distance, whereas hubs are basically multi-port repeaters and reflect the frames between all ports to interconnect multiple nodes.

electrical and mechanical definitions

network extensions

### The Data Link Layer

node-to-node frame delivery The purpose of the data link layer is to ensure a reliable communication between adjacent network nodes within the local subnet. For this reason, the data link layer groups the bits that are transmitted via the physical layer to *frames*. The data link layer ensures that the particular frames are unambiguously detectable within the physical bit stream and adds functionalities for the error detection or also error correction. The provided service of the data link layer therefore is to transmit or to receive single frames to adjacent network nodes. Furthermore, the data link layer ensures that a fast node is not flooding a slow node with data. This is called *flow control*.

$media\ access$  control

Another important task is the arbitration of the access to the physical medium in the case that it is shared with other network nodes e.g. via a single cable, a ring or simply the radio frequencies in the case of wireless networks. This task is located within the media access control (MAC) sublayer, which is part of the data link layer. Example MAC sublayer protocols are Ethernet [92] or Token Ring [145].

$frame \\ forwarding, \\ switching$

The interconnection of subnets on the data link layer is done with bridges that also convert the frame formats. Network nodes that interconnect multiple other nodes or subnets are called *switches*. Switches have a larger number of physical ports and forward the frames between the ports according to their data link layer address. The main tasks of switches are multiplexing, queuing and scheduling. The design of packet switches is discussed in more detail in section 1.5.

#### The Network Layer

network-wide packet delivery The network layer provides a topology-independent view of the network to the layers above. It provides a network-wide communication between network nodes that are not necessarily directly connected and may even be located in interconnected subnets of different types. The data formats of the network layer are called *packets*. Packets contain network layer addresses.

routing of packets

The most important task of the network layer is the *routing*, which is to determine a path (or route) of consecutive adjacent network nodes from the source of a packet to its destination. One issue of this is to avoid live-locks and dead-locks, which means that packets are ensured to reach their destinations without circling or being blocked. The network nodes that perform this task are called *routers*. Routers operate with network layer addresses and are aware of (at least parts of) the network topology. This is in contrast to switches, which perform rather the forwarding of frames between adjacent nodes according to local addresses.

processes of the network layer

Besides the routing, further processes of the network layer are the fragmentation of packets into smaller ones to keep to the maximum packet size of the several subnets, as well as the re-assembly of the fragments to packets. An example network layer protocol is the internet protocol (IP) protocol [114] of the internet. Another task is the conversion between the network address and the data link layer addresses of the local subnets. An example protocol is the address resolution protocol (ARP) protocol [112], which is mostly used to translate addresses between IP and Ethernet.

9

### The Transport Layer

The transport layer provides multiple and independent end-to-end communication channels to the layers above. This end-to-communication can be either packets (now called *datagrams*) or *connections*. The mostly used transport layer protocols of the internet are user datagram protocol (UDP) [113] for datagrams and transmission control protocol/internet protocol (TCP/IP) [11] for connections.

end-to-end communication

Concerning TCP/IP connections, the protocol hides the packet-based nature of the network layer to the layers above and provides reliable connections. The main tasks are the fragmentation of the data streams to packets and its reassembly at the destinations. Furthermore, the transport layer re-requests erroneous packets or lost packets and also ensures the correct packet order in the case that packets get out-of order due to different routes. The connections of TCP/IP have a client-server architecture. One process (the server) is awaiting connections on a dedicated port and another process (the client) may initiate a connection to that port. Usually, connections require a setup-phase and a take-down phase. This is handled by an internal state-machine which can be of significant complexity.

TCP/IP connections

Another important task is to control the amount of packets sent into the network to avoid an overload of its resources (congestion control). This can be detected by the occurrence of packet drops even if the two peers of a connection feature sufficient resources. The transport layer protocol reduces the packet rates in that case.

### The Session Layer

The purpose of the session layer is to manage and coordinate multiple connections between different users or applications. The appearance of the session layer depends on the application, it can even be nonexistent. Its tasks are authentication (password checks), synchronization (e.g. the synchronization of audio streams and video steams within a video conference) or token management (preventing two users of using the same critical resource), but also the checkpointing and the restoration of data streams to resume a session after a crash.

coordination of multiple connections

### The Presentation Layer

The presentation layer defines the semantics and the syntax of the data formates to be exchanged. This is useful to allow machines with different encoding techniques to communicate via a common protocol. The services of the presentation layer perform the conversion of data formats and structures on a higher abstract level and define the bit-patterns that are send via the lower layers. Other presentation layer issues are the encryption or the compression of the transmitted data.

definition of transmitted data formats

### The Application Layer

The application layer finally contains the application-specific protocols and data formats. Examples for a application-layer protocols are hypertext transfer protocol (HTTP) to fetch web-sides or post office protocol version 3 (POP3) to get emails from the servers.

user defined

#### 1.2.2 Alternative Models

The described OSI reference model is not the only existing model. As an advantage, it is well suited to understand the basic principles of networking. The model has been deviced before the corresponding protocols have been invented [143].

TCP/IP reference model

In fact, the TCP/IP reference model of [11] describes the requirements for internet hosts and its protocols are widely used. The protocol is not formally defined in any publication, but its layered architecture can be extracted from [11]. The TCP/IP model groups the lower layers in a single general network access layer and the upper three layers in a general application layer. The intermediate network and the transport layer use the protocols IP respectively UDP and TCP/IP.

model used for the thesis

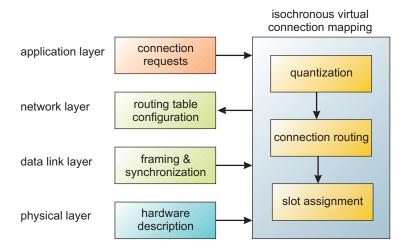

For the remainder of this theses, the discussion of the network functionality keeps to the layered organization of networks and to the concept of interfaces, services and protocols. The discussion does not use a strict model, but follows the presentation in [143] and uses a hybrid model of the described two for simplicity. It uses the lower levels of the OSI model to describe the physical transmissions and the switching technology in conjunction with the simplifications of the TCP/IP model to group the top three layers to a single abstract application layer. This used hybrid model is illustrated in figure 1.4.

Figure 1.4: The hybrid network model used throughout this thesis.

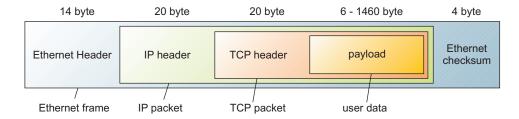

#### 1.2.3 Encapsulation of Data Formats

headers and trailers

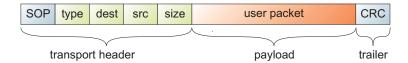

Most protocols require to transmit a certain amount of data together with the user data from the layer above. This data is added as a header or a trailer to the user data at the source node and is removed at the destination. The user data from the layers above is called the *payload* for the lower layer protocol. This results in the fact that the data from the lower layer protocols is placed at the beginning and at the end of the frame, whereas the user data is enclosed by its lower layer protocols "within". Figure 1.5 illustrates a typical example of a data frame on an Ethernet LAN that belongs to TCP/IP session.

$transparent \\ transportation \\ process$

The encapsulation of the protocols is an important aspect since it makes the implementation of the lower layer transport processes completely transparent to the layers above. As an example, a transport layer protocol that communicates via datagrams does not have to care about *how* exactly the datagrams arrive at the destination. A switching architecture that provides general packet transports can therefore be used by all higher-layer protocols that require this kind of service. Nevertheless, the way packet transports are implemented clearly determines the service

Figure 1.5: Example of an Ethernet data frame that contains a TCP/IP packet.

guarantees that are mad by the lower layers for the transportation process. This is investigated in the succeeding sections.

### 1.3 Circuit Switching and Packet Switching

Most computer networks are not fully connected, but the hosts are interconnected via intermediate switches using a switching technology. Switching reduces the number of physical lines and simplifies the interfacing of single hosts to the network. A fundamental design aspect of each network architecture is the question whether the network provides connection-oriented transport services or connection-less transport services to the layers above. The basic two alternatives are called circuit switching and packet switching.

### Circuit Switching Networks

In circuit switching networks, the communication is performed along dedicated paths (or circuits) between the source node and the destination node of a connection. The circuit uses exclusively reserved resources and features a certain guaranteed throughput (or bit rate). A once established circuit remains active for the duration of its connection. The circuits have to be set up in a signaling phase or call setup before a communication can take place and have to be taken down after the communication completes. The forwarding decision for the data is easy, since the routing decisions have already been made during the signaling phase. This reduces the required amount of buffering within the routers and switches. Examples for circuit switched networks are the old-style telephone networks with the protocol integrated services digital network (ISDN) [9].

The advantages of circuit switching is that it allows to reserve network bandwidth to the communicating hosts and that it reduces the complexity of the forwarding task of the data to be transmitted. The reservation of resources further results in a low overall end-to-end delay for the transmitted data. The drawbacks are that the required signaling phase is of high complexity and results in a latency before the transmissions of data starts. Furthermore, reserved but unused bandwidth is wasted, which makes circuit switching more useful in the case that the required bandwidth can be estimated. Circuit switching networks are also less robust, since a failure of a router results in a failure of all of its managed circuits.

$\begin{array}{c} functional \\ description \end{array}$

properties

### Packet Switching Networks

$\begin{array}{c} functional \\ description \end{array}$

In packet switching networks, the data to be transported is split into flows of multiple packets, which are transported independently. The path or route of the packets is not pre-determined, so its up to each packet to find its way through the network. Packed switching networks therefore require a routing decision to be made for each packet at each intermediate network node. For this reason, each packet contains an additional header with the destinations address and usually further administrative information. Since the bandwidth of the packets is not pre-reserved, the network may be required to buffer the packets at the routers and switches before the output lines became free (store-and-forward packet switching). An example for a packet switching network is an IP network that connects multiple Ethernet LANs.

properties

The advantage of packet switching networks is that they require less administrative overhead by the network, since no connections between end-nodes have to be set up or taken down. Furthermore, packet switching networks feature increased robustness, since the packets can be routed around a failed router along different routes and are also better designed to handle unpredictable traffic. The drawback of packet switching networks is that the packet headers can lead to a waste of bandwidth especially for small payloads. Furthermore, they require a higher administrative overhead by the end-nodes, e.g. for the re-ordering of packets that arrive out-of-order due to different routes. As another drawback, the non-deterministic forwarding of packets in packet switching networks makes it harder to provide deterministic service guarantees.

### Combined Switching Techniques

$\begin{array}{c} transparent\ to\\ user \end{array}$

The terms circuit switching and packet switching concern the operations within the lower network layers. The layered protocol stack makes the switching architecture of the network transparent to the user and allows to provide both, connections-oriented services as well as connection-less (datagram) services to upper network layers. Packet flows that belong to higher-layer connections can be transported via both switching techniques. As an example, an ATM [143] network uses fixed-sized packets (or cells) that are transmitted along virtual circuits (VCs) to provide both, connection-oriented services and also datagram services. Another example is the transport of IP packets over the telephone system or making telephone calls over the internet.

### 1.4 Quality of Service

definition

The term QoSs denotes the provision of traffic characteristics or priorities by the network for different levels of performance to the transported data flows. The provided services are usually guaranteed according to a request by the application and thus differ from the general methods to improve the network performance such as flow control or congestion control. Example requirements are:

- A guaranteed reliability of the transmitted data.

- A guaranteed throughput or more specifically, a bit rate.

- Guaranteed bounds for the transmission delay.

- Guaranteed bounds for the delay variation (the *jitter*).

- A guaranteed maximum cell loss ratio.

QoS requests from applications may vary in a wide range. For some applications, a low latency of the traffic is more important than the data reliability. For others, the data reliability is essential and a high throughput is desired etc. Table 1.1 shows an example list of applications and its requirements of QoS [143].

| application       | reliability | delay  | jitter | bandwidth               |

|-------------------|-------------|--------|--------|-------------------------|

| email             | high        | low    | low    | low                     |

| file transfer     | high        | low    | low    | $\operatorname{medium}$ |

| web access        | high        | medium | low    | medium                  |

| remote login      | high        | medium | medium | low                     |

| audio on demand   | low         | low    | high   | $\operatorname{medium}$ |

| video on demand   | low         | low    | high   | high                    |

| ${ m telephony}$  | low         | high   | high   | low                     |

| videoconferencing | low         | high   | high   | high                    |

Table 1.1: Example applications and how stringent its QoS requirements are [143].

### 1.4.1 Services Guaranteed by the Network

A network does usually not support detailed and fine-grained requests for all combinations of the above variables. In most cases, the network provides a set of traffic classes or service classes to the application. Some networks provide hard guarantees to certain parameters and others provide only soft QoS services. Example end-to-end QoS service classes are:

• Guaranteed services, also known as hard QoS. This can be guaranteed bandwidth or guaranteed end-to-end delay or jitter. The network guarantees these services to particular flows independent on the behavior of other flows. This usually requires the absolute reservation of network resources. Examples for guaranteed services are:

$\begin{array}{c} guarantees\\ services \end{array}$

- A guaranteed throughput. This can be achieved using a WFQ scheduling algorithm within the switches (see below).

- A constant bit rate (CBR) service. This is required e.g. for telephony, audio, video or other real-time applications, where not the absolute bandwidth, but the smoothness of the traffic is important to avoid gaps. It is e.g. provided by ATM networks [143].

- Isochronous connections. The term isochronous refers to a constant delay between the transmission of the data at the sender and its reception at the receiver. A constant delay ideally equals no jitter. In fact, isochronous

connections are practically achieved with CBR services and the isochronicity of the connections depends on the remaining jitter. Isochronous connections are useful for real-time applications. Example networks that provide isochronous connections are [137, 40].

$best\mbox{-}effort \\ services$

• Best-effort services. No QoS is guaranteed and the packets of a best-effort flow simply use the remaining resources not reserved or not used by other traffic classes. This is best characterized by first-in first-out (FIFO) queues, which have no differentiation between flows. The network usually tries to schedule best-effort traffic in a fair way, such that no flow is starved out completely by other best-effort flows.

$\begin{array}{c} integrated \\ services \end{array}$

• Integrated services is a technique to provide fine-grained QoS on IP networks. The QoS guarantees are made per flow. The management of the several flows is done by the network with the resource reservation protocol (RSVP) protocol [12, 151]. The applications have to describe the requested flow with a set of given QoS parameters. A request may be accepted or rejected. The drawbacks are that the complex RSVP protocol has to be implemented within each router of the network, and the required setup phase for each flow.

$differentiated \\ services$

• Differentiated services is a technique to provide coarse-grained QoS on IP networks [101, 7]. The QoS guarantees are class-based with pre-defined classes by the network. The guarantees are made statistically and no hard guarantees are made for individual flows. As an advantages to integrated services, this greatly simplifies the network organization and does not require a flow setup phase. Example traffic classes are expedited forwarding [27] for prioritized, low-loss or low-latency traffic, assured forwarding [51] with 12 sub-classes of different priority and discard probability, and best-effort traffic.

It is an important design factor whether the network itself defines the available QoS features or the application may demand a fine-grained QoS with a complex parameter set. Furthermore, the number of service classes is important since it may require the routers and switches of the network to manage multiple queues. A simple implementation to provide QoS is the definition of few priority classes which are served in ascending order.

### 1.4.2 Techniques to Provide QoS

The different traffic classes for QoS are provided with different techniques. Practical solutions often combining several of them:

error handling

• The data reliability is guaranteed by error detection and/or error correction mechanisms. Often used methods are checksums, e.g. the cyclic redundancy check (CRC), which are used in a wide range of protocols on nearly all network layers. Packets (or data in general) that arrive with wrong checksums are simply dropped and re-transmitted. The detection of lost packets and the re-transmissions are usually implemented within the data link layer or the transport layer. Other mechanisms are the usage of redundant data in the case that re-transmissions are too costly.

• A simple possibility to meet throughput requests is the overprovisioning of bandwidth and buffer space. In many cases, its more easy to buy additional capacities than to change an existing network architecture to increase the performance. As an example, the telephone system is overprovisioned, since a phone call is rarely rejected. As another example, the development of the dense wavelength division multiplexing (DWDM) technique leads to enormous capacities in fiber-optics communication [110] for wide area networks (WANs).

overprovisioning

• To reduce the jitter of a packet flow, its is possible to buffer the data streams. This can be done either at the receiver of a flow (by using a jitter or playback buffer), at the sender or at intermediate nodes (then called traffic shaping). Techniques for traffic shaping are e.g. the leaky bucket algorithm or the token bucket algorithm [143]. A traffic shaping algorithm controls the average rate of a data stream. It has the advantage that it reduces the burstiness of the traffic, which results in smaller buffer requirements and reduced congestion and packet drop probability at intermediate nodes.

buffering

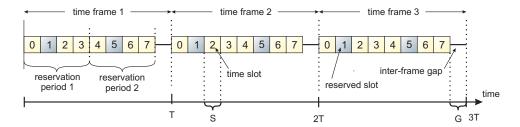

• In the case that a strict guaranteed QoS is required for a particular flow, the network has to use resource reservation. The resources like bandwidth, buffer space or central processing unit (CPU) cycles are exclusively reserved for the requesting flow and can be provided independently of the network traffic of other resources. Resource reservation can be achieved more easily in circuit switching networks, simply by establishing a circuit between the end-points of the flow with the guaranteed properties. The exclusive reservation of bandwidth can be achieved by a time division multiplexing (TDM) technique, which is a periodic division of the time into time slots. The reservation of time slots further requires a certain synchronization to keep to the correct slot position when passing data from one link to the next. Other possible reservation techniques are the assignment of wavelengths in optical networks or radio frequencies in wireless networks.

$resource \\ reservation$

• In packet switching networks, each packet is assigned to a certain flow, which is denoted within the packet header. The flow delimiters are respected by the intermediate packet switches of the network. Incoming packets are stored within the queues of the switches. The switches contain packet schedulers, which calculate the queues to be served next according to the flows the packets belong to. This is useful to implement different priorities or to balance the forwarding process of unreserved flows. Packet switches and scheduling algorithms are discussed in more detail in sections 1.5 and 1.6, respectively.

packet scheduling

• A network that provides QoS in any case must be able to decide whether it can accept a new request for a QoS flow according to its available resources. This process is called *admission control*. The network has to take care to only accept new flows such that the currently accepted flows remain unaffected. For that reason, a request for a new flow has to be specified by the calling process in a *flow specification*. An example flow specification is used with RSVP [12, 151] and contains the token bucket rate, the token bucket size, the peak data rate and the minimum and the maximum packet size [143]. The

$admission\ control$

maximum packet size may be limited for particular network protocols. As an example, an Ethernet frame is limited to 1500 byte payload.

The next sections considers a more practical view of how QoS can be implemented within the network.

### 1.5 Packet Switching Architectures

In circuit switching networks, the information of how to forward incoming data has been pre-determined during the signaling phase of the circuits and is available at the switches at the time the data arrives. Clearly, QoS can easily by provided in circuit switching networks by using the pre-reserved resources for bandwidth or buffering space. In contrast to that, the provision of QoS in packet switching networks is more complicated. This section describes the basic design principles of packet switches in packet switching networks.

The purpose of the switches is to forward the incoming packets to their destinations, which can be determined out of the destination address of the packets. The problem is that the switches may have no information in advance about the arriving packets, neither of their destination nor of their number. Besides the pure packet forwarding, a switch design has to respect the following aspects:

- The main goal is to achieve 100 % throughput. That is, no packet should be dropped due to overcrowded queues or contenting ports.

- The packet average delay, i.e. the average time the packet stays within the switch, should be minimized.

- No packet flow should be starved out. This has to be independent of the behavior of other flows.

- The design should be scalable in terms of area and line speed.

- The switch may provide to multicast packets from a single input to multiple outputs.

- The switch may provide deterministic QoS. As stated in section 1.4, QoS guarantees can be provided in terms of guaranteed bounds for the packet delay and throughput, but also by the provision of different service classes such that the packet flows are forwarded with different traffic characteristics (e.g. at different priorities).

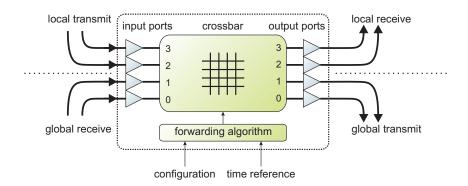

### 1.5.1 General Architecture of a Packet Switch

$basic\ operation$

The following discussion considers switches with the same number N of input and output ports, for simplicity. During the operation of the network, packets arrive sequentially at the input ports and leave the switch sequentially at its output ports. The purpose of the switch is to forward the incoming packets internally from the inputs to the outputs. To handle the packet flows, switches usually consist of the following components:

purpose

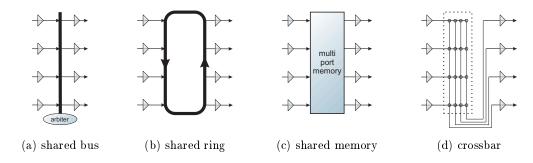

- A multiplexer functionality. Possible architectures are a central bus, a central ring, a shared memory or a crossbar with  $N^2$  crosspoints [148]. Multiple stages are possible.

- A set of buffers (or queues) to store the packets that cannot immediately be forwarded. One possibility is the usage of FIFO queues.

- A scheduling algorithm that decides the time each packet is served. This can be implemented with a centralized scheduler and also with multiple independent schedulers at each port.

Figure 1.6 illustrates basic switch architectures. The control of switches that use shared resources like a shared bus (a), a shared ring (b) or a shared memory (c) is less complex then switches that use crossbars (d) [148]. The drawback of the shared architectures is that the bandwidth of the shared medium has to be higher than the bandwidth of the external line. As an example, the central memory of a shared memory switch requires 2N times the bandwidth of the external line rate. Furthermore, the memory requires 2N independent ports, which increases its complexity. At higher port numbers and higher line rates, shared architectures have only limited scalability. The following discussion therefore focuses on crossbar switches only.

limited scalability

of shared

architectures

Figure 1.6: Schematic overview of basic switch architectures. The input ports are shown on the left, the output ports on the right.

The fully-connected crossbar is non-blocking and buffer-less and transfers multiple packets in parallel while still operating at the external line rate. The crossbar and the queues may operate at higher rates than the external line rate for increased performance. This is denoted as an internal  $speedup\ s>1$ . Different switch architectures of crossbar switches exist, which are mainly distinguished according to the locations of their queuing stages and the scheduling algorithm used.

$\begin{array}{c} crossbar \\ architecture \end{array}$

Crossbar switches have to solve the problem of *contention*. That is, each input port can forward data only to a single output port at a time and also each output port can take data only from up to a single input port. The switches have to solve this problem by using queuing stages at the input or output ports or by using a speedup to avoid data losses.

contention

### 1.5.2 Output-Queued Crossbar Switches

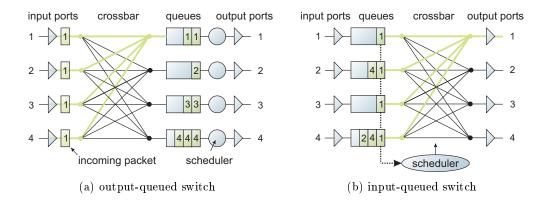

Figure 1.7(a) shows the basic design of an output-queued crossbar switch. At this basic architecture

type of switch, incoming packets are directly forwarded to the crossbar and stored in the queues, which are located in front of the output ports. The queuing stage at each output can be a single FIFO queue or also multiple queues to sort the packet flows. It is also easy to implement multicasts by simply copying the incoming packets.

limited scalability

Output queued switches have been investigated in the earlier times due to its conceptual simplicity. Several scheduling algorithms can be used to provide QoS in such a switch (for an overview see e.g. [161]). The main drawback of output-queued switches is the required speedup of N to handle contention at the output ports in the case that multiple packets that arrive at the same time at the input ports have to be forwarded to the same output port. Output-queues switches are therefore not scalable to higher line rates and larger port numbers.

Figure 1.7: Simplified schematic of an input-queued and an output-queued switch. (a) Output-queued switches require N times the memory bandwidth at the queues to handle worst-case packet arrivals. (b) Input-queued switches require a centralized scheduler for an optimal usage of the crossbar.

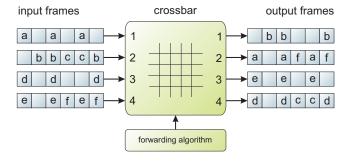

### 1.5.3 Input-Queued Crossbar Switches

$basic\ architecture$

Figure 1.7(b) shows the basic design of an input-queued packet switch. Incoming packets are immediately stored within the queues and thus a speedup is not necessarily required. Since the queues of a single input may have packets for different outputs, contention occurs at both, the input ports and the output ports. Without an internal speedup, each output port can take data from only a single input at a time. For that reason, a separate and independent scheduler at each output port is not possible, since multiple output schedulers could select the same input. The operation of the crossbar is therefore controlled by a single scheduler. This is usually achieved with a slotted time and by the use of fixed sized packets (e.g. ATM cells). The crossbar then multiplexes up to N packets in parallel from the input ports to the output ports within a single time slot. However, a stable scheduling of variable sized packets can achieved by modifying existing cell-based algorithms [81, 42].

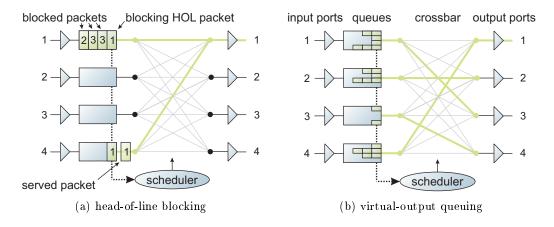

HOL blocking problem

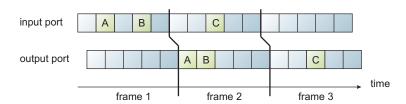

The problem of input-queued switches is that the architecture suffers from the head-of-line (HOL) blocking effect in the case that simple FIFO queues are used for the packet storage. The HOL effect is illustrated in figure 1.8(a). The effect occurs in the case that a single packet at the head of a FIFO queue cannot be forwarded to

its dedicated output due to other packets that are taken for this output, first. Due to the FIFO queuing policy, the packet at the head of the queue blocks the other packets even if packets behind the head could be transferred to other, currently unused, outputs. The work in [69] showed that this effect limits the throughput of such a switch to  $2 - \sqrt{2} = 58.6 \%$  for incoming uniform independent, identically distributed (i.i.d.) Bernoulli arrival patterns <sup>1</sup>.

Figure 1.8: Illustration of the head-of-line locking problem.

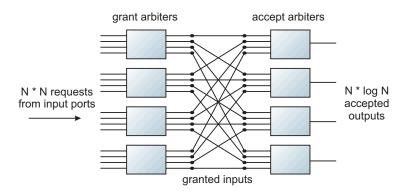

One opportunity to solve the problem of HOL blocking is to use virtual output queues (VOQs), which contain a separate FIFO queue for each output at each input. The work in [142] presents different architectures for statically and dynamically allocated queues. The queues can have a single write port for incoming packets and a single read port to the crossbar and implement the multiple queues internally. The usage of VOQs requires incoming packets to be pre-routed at the time of their arrival to determine their output port and thus their corresponding VOQ. Since each internal queue can be scheduled individually, the HOL blocking problematic has been removed (cf. figure 1.8(b)).

As a drawback, this technique significantly complicates the central scheduler, which now has to calculate a scheduling out of  $N \times N$  requests from the queues for the N output ports. In particular, it is difficult to implement guaranteed services for an input-queued switch. This shows that it has to be made a trade-off between scalability and the provision of QoS. The output queued switch can provide QoS, but is not scalable. The input-queued switch architecture is scalable, but the provision of QoS is difficult. Example schedulers for input-queued switches with VOQs are described below in section 1.6.2.

complex scheduler, QoS difficult

virtual-output queuing

### 1.5.4 Combined Input-Output Queued Switches

Switches with queues at both, the input ports and the outputs are called combined input-output queuing (CIOQ) switches. They combine the effects of the two previous

OQ emulation with speedup of

<sup>&</sup>lt;sup>1</sup>Uniform i.i.d. Bernoulli traffic comprises an arrival pattern such that in any given time slot, the probability that a packet arrives at a particular input is p. Each packet has the equal probability of 1/N of being addressed to any given output, and successive packets are independent.

architectures by accepting an increased amount of queuing space and an increased complexity of the scheduler. It has been shown in [25, 138] that a CIOQ switch with a speedup of two can emulate the behavior of an output-queued switch and thus provide guaranteed QoS.

#### 1.5.5 Further Switch Architectures

There are many variations besides the described switch architectures. Variants feature additional buffers, multiple stages or distributed schedulers in contrast to centralized ones. Newer approaches for designs for high-speed switches are:

load-balanced

• Load-balanced switches use an additional, unbuffered load-balancing stage with an additional crossbar before the switching stage [20, 21, 72]. The load-balancing stage distributes incoming traffic periodically over the central buffers. This results in a uniform arrival pattern at the second stage. For uniform arrivals, the second stage can be scheduled in a periodic manner of O(1) complexity and results in 100% throughput, which effectively removes the need of a scheduler. As a drawback, this type of switche suffers from packet disordering [74, 22, 160] and requires an increased space for the second stage. This promising switch type is discussed further below.

parallel switches

• A parallel packet switch also uses multiple stages, but placed in parallel such that each packet experiences only a single stage of buffering. It consists of multiple packet switches in parallel that operate independently and at a lower rate compared to the external line rate [64]. It can be shown that such a switch can achieve 100 % throughput and can emulate an output queued switch with FCFS scheduling (see below), but it is difficult to implement QoS.

The above sections gave an intention of how the multiplexers and the queues are arranged in different switch architectures. Most of the architectures require a queuing scheduler to decide which packet to be served next. The next sections discusses how this scheduling task can be implemented.

### 1.6 Queuing Schedulers

scheduling of queued packets

requirements

The purpose of the queuing schedulers is to decide at which time the packets that are stored in the various queues are forwarded to the output ports of the switch for transmission. Concerning packet switches, the scheduling task can be discussed either with reference to the single queues or also with reference to the various packet flows that are stored within the queues. In general, the scheduler gets repeatedly requests from the queues (or the packet flows) and selects one of them. The general requirements for a queuing scheduler are (see e.g. [4]):

- To maximize the throughput.

- To minimize the average delay (the queuing wait time) of the packets.

- To feature fairness and protection. This means that all queues should be served fair under equal traffic conditions and also that no service for a queue should be influenced or even starved out by others.

• To be of limited complexity, i.e. to be simple and fast for an implementation in hardware at high line rates.

Further requirements concern requests to guaranteed services depending on the switch type or application and may include:

- The provision of guaranteed, deterministic QoS.

- A simple admission control to request the guaranteed services.

- To still maintain the fairness for non-prioritized flows.

A wide range of queuing schedulers exist for different switch architectures and also purposes. The next sections give a brief overview of schedulers often used and discuss their advantages and disadvantages.

### 1.6.1 Schedulers to Access a Single Resource

Schedulers for an arbitration of a single resource can be used in output-queued switches, where the packets are stored in queues directly at the outputs after having already been transferred over the crossbar. The schedulers can therefore be implemented separately and independently at each queue. The purpose of this type of scheduler is to repeatedly select a single queue or packet flow out of N requesting queues (i.e. non-empty queues) to transmit a packet. Two simple scheduling policies are:

select 1 out of N

• One of the simplest schedulers uses the first-come first-served (FCFS) scheduling policy. All packet flows are stored within a single queue and are served within the order in which they arrived. It is simple to implement.

first-come first-serve

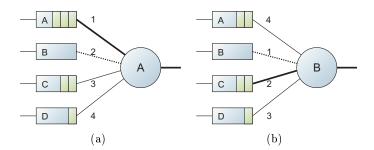

• A commonly used scheduler is a round-robin scheduler (cf. figure 1.9). For each selection, all queues have different priorities in a cyclic order. The queue to be served next is selected out of the non-empties according to the current priorities. The priorities are then rotated such that the selected queue gets the least priority next. Round-robin is fair since no queue has to wait longer than N-1 selections and can be starved out by other queues. It performs well for comparable service requests from all queues.

round-robin

A drawback of the above schedulers is that no service guarantees are made for particular queues (or packet flows). In contrast to that, the following schedulers can be used to provide guaranteed services. Most of them provide guaranteed rates [161, 4].

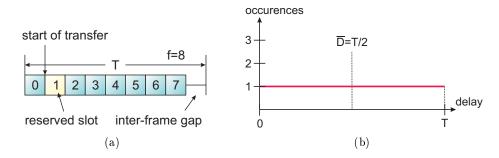

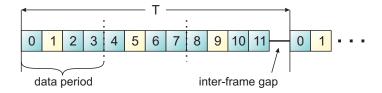

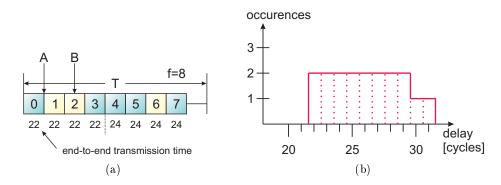

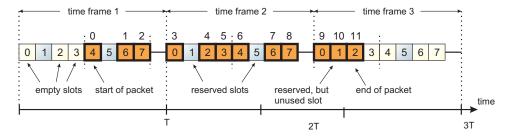

• The simplest way to guarantee the service for a particular queue is using a static priority, which serves each queue with a different priority. A particular queue is served only if all higher-priority queues are empty. The unfairness is obvious since only the top-priority queue receives a guaranteed service and packets in lower-prioritized queues can encounter significant delays.