## RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

Martin Albrecht Trefzer

Evolution of Transistor Circuits

Dissertation

HD-KIP 06-29

KIRCHHOFF-INSTITUT FÜR PHYSIK

## DISSERTATION

submitted to the Combined Faculties for the Natural Sciences and for Mathematics

of the Ruperto-Carola-University of Heidelberg, Germany

for the degree of Doctor of Natural Sciences

presented by Dipl.-Phys. Martin Albrecht Trefzer born in Lörrach, Germany

Date of oral examination: 13.12.2006

# **Evolution of Transistor Circuits**

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Fred A. Hamprecht

#### **Evolution von Transistor Schaltungen**

Der Entwurf von analogen Schaltungen ist ein Bereich der Elektronikentwicklung, der dem Entwickler ein hohes Maß an Wissen und Kreativität beim Lösen von Problemen abverlangt. Bis heute gibt es nur rudimentäre analytische Lösungen um die Bauteile von Schaltungen zu dimensionieren. Motiviert durch diese Herausforderungen, konzentriert sich diese Arbeit auf die automatische Synthese analoger Schaltungen mit Hilfe von Evolutionären Algorithmen. Als analoges Substrat wird ein field programmable transistor array (FPTA) benutzt, das ein Feld von konfigurierbaren Transistoren zur Verfügung stellt. Der Einsatz von echter Hardware bietet zwei Vorteile: erstens können entstehende Schaltungen schneller getestet werden als mit einem Simulator und zweitens funktionieren die gefundenen Schaltungen garantiert auf einem echten Chip. Softwareseitig eignen sich Evolutionäre Algorithmen besonders gut für die Synthese analoger Schaltungen, da sie keinerlei Vorwissen über das Optimierungsproblem benötigen. In dieser Arbeit werden neue genetische Operatoren entwickelt, die das Verständnis von auf dem FPTA evolutionierten Schaltungen erleichtern und außerdem Lösungen finden sollen, die auch außerhalb des Substrates funktionieren. Dies ist mit der Hoffnung verbunden, möglicherweise neue und ungewöhnliche Schaltungsprinzipien zu entdecken. Weiterhin wird ein mehrzieliger Optimierungsalgorithmus implementiert und verfeinert, um die Vielzahl von Variablen berücksichtigen zu können, die für die gleichzeitige Optimierung von Topologie und Bauteiledimensionierung notwendig sind. Die vorgeschlagenen genetischen Operatoren, sowie die mehrzielige Optimierung werden für die Evolution von logischen Gattern, Komparatoren, Oszillatoren und Operationsverstärkern eingesetzt. Der Ressourcenverbrauch der durch Evolution gefundenen Schaltungen wird damit vermindert und es ist möglich in einigen Fällen einen übersichtlichen Schaltplan zu erstellen. Ein modulares System für die Evolution von Schaltungen auf konfigurierbaren Substraten wurde entwickelt. Es wird gezeigt, dass mit diesem System FPTA-Architekturen modelliert und direkt für Evolutionsexperimente verwendet werden können.

#### **Evolution of Transistor Circuits**

Analog circuit design is a discipline of electronic design, that demands a lot of knowledge and experience as well as a considerable amount of creativity in solving diverse problems from the designer and there are to date only rudimentary analytical solutions for parameterizing circuit topologies. Motivated by the latter challenges, this thesis focuses on the analog design automation for FPTA architectures by means of evolutionary algorithms (EAs). The advantages of using real hardware for circuit evolution are the significantly faster evaluation of candidate solutions compared to a simulator and the fact that found solutions are guaranteed to work on a real-world substrate. On the software side EAs are particularly well suited for analog circuit synthesis since they do not require prior knowledge of the optimization problem. New genetic operators are developed within this thesis aiming to facilitate the understanding of evolved FPTA circuits and to find solutions that can be transfered to other technologies. A great hope is thereby to possibly discover unusual, new design principles. Furthermore, a multi-objective algorithm is implemented and refined, in order to allow for taking the numerous variables into account, that are required for optimizing the topology and the dimensioning of transistor circuits. The proposed genetic operators and the multiobjective approach are successfully applied to the evolution of logic gates, comparators, oscillators and operational amplifiers. It is achieved to reduce the resource consumption of evolved circuits and in some cases it is possible to generate clear schematics of good solutions. A modular framework for the evolution of circuits on configurable substrates has been developed, which is used to perform the experiments and is further demonstrated to be useful for modeling FPTA architectures and subsequently using them in evolution experiments.

# Contents

| In | Introduction 1 |                                        |                                                 |    |

|----|----------------|----------------------------------------|-------------------------------------------------|----|

| I  | Fou            | ndatio                                 | ns                                              | 5  |

| 1  | CM             | OS Ana                                 | alog Circuit Design                             | 7  |

|    | 1.1            | Physic                                 | cal Representation of the CMOS Transistor       | 8  |

|    |                | 1.1.1                                  | Operation Regions                               | 11 |

|    |                | 1.1.2                                  | Parasitic Capacitances                          | 12 |

|    |                | 1.1.3                                  | Large Signal and Small Signal Model             | 13 |

|    |                | 1.1.4                                  | Possible Configurations                         | 14 |

|    | 1.2            | Realiz                                 | ting Switches with Transmission Gates           | 15 |

|    |                | 1.2.1                                  | Parasitics of Transmission Gates                | 15 |

|    | 1.3            | CMOS                                   | S Transistor Modeling                           | 16 |

|    |                | 1.3.1                                  | SPICE LEVEL3 Simulation Model                   | 17 |

|    |                | 1.3.2                                  | BSIM3v3 Simulation Model                        | 17 |

|    | 1.4            | CMOS                                   | S Design Flow                                   | 18 |

| 2  | Evo            | lutional                               | ry Algorithms                                   | 21 |

|    | 2.1            | Inspira                                | ation from Natural Evolution                    | 22 |

|    |                | 2.1.1                                  | Darwinian Evolution                             | 22 |

|    |                | 2.1.2                                  | The Genetic Level                               | 23 |

|    |                | 2.1.3                                  | From Genotype to Phenotype                      | 25 |

|    | 2.2            | Buildi                                 | ng Evolutionary Algorithms on Nature's Concepts | 25 |

|    |                | 2.2.1                                  | Historical Roots and Current Subareas           | 26 |

|    |                | 2.2.2                                  | Modules of Evolutionary Algorithms              | 27 |

|    |                | 2.2.3                                  | Extensions to Evolutionary Algorithms           | 29 |

|    |                | cterization of Evolutionary Algorithms | 29                                              |    |

|    |                | 2.3.1                                  | Features for Global Optimization                | 30 |

|    |                | 2.3.2                                  | Is Any Convergence Guaranteed?                  | 30 |

|    |                | 2.3.3                                  | Model-Free Heuristics                           | 31 |

|    |                | 2.3.4                                  | No Free Lunch Theorem                           | 32 |

|    |                | 2.3.5                                  | Feasible and Infeasible Solutions               | 32 |

| II | An  | nalog Circuits Evolution Framework                                       | 35 |

|----|-----|--------------------------------------------------------------------------|----|

| 3  | The | FPTA: an Analog Evolvable Hardware Substrate                             | 37 |

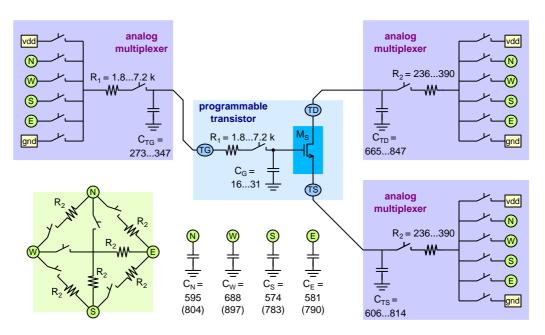

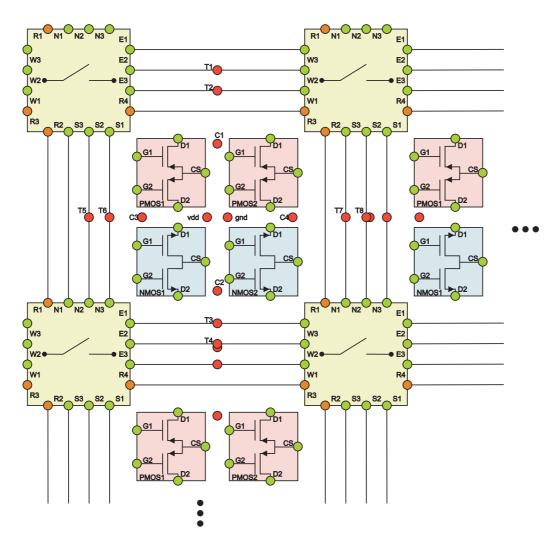

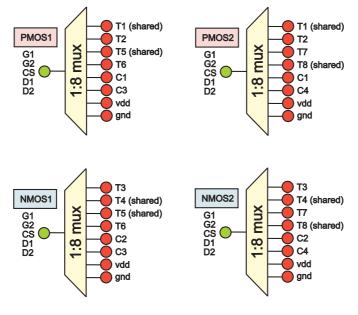

|    | 3.1 | The FPTA's Architecture                                                  | 39 |

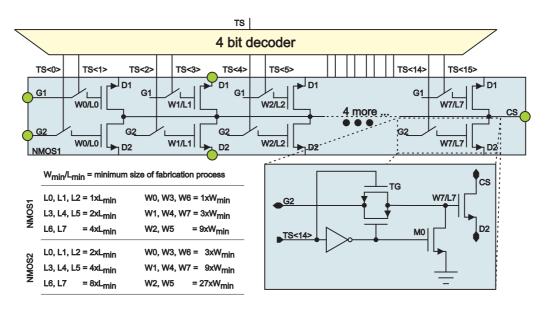

|    |     | 3.1.1 Configurable Transistor Cell                                       | 39 |

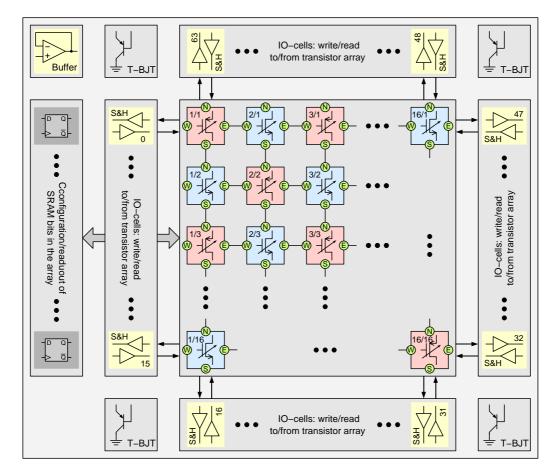

|    |     | 3.1.2 Transistor Cell Array                                              | 40 |

|    |     | 3.1.3 Comparison with the JPL FPTA                                       | 42 |

|    |     | 3.1.4 An Overview of FPAAs from Industry                                 | 43 |

|    | 3.2 | The Hardware Evolution Setup                                             | 44 |

|    |     | 3.2.1 The Controller: a Standard PC Hosting a FPGA-Based PCI Card .      | 44 |

|    | 3.3 | Characteristics of the FPTA and the Hardware Environment                 | 45 |

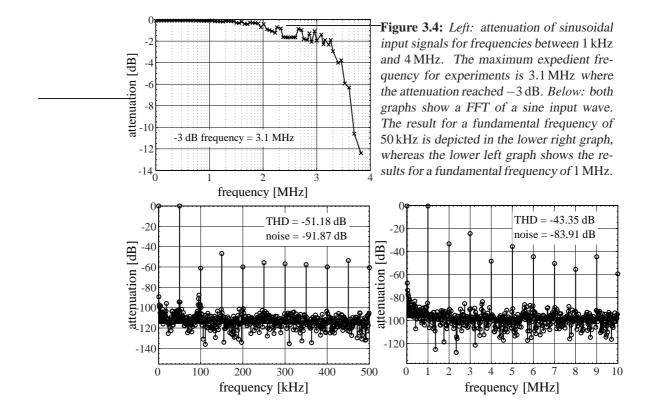

|    |     | 3.3.1 Bandwidth                                                          | 45 |

|    |     | 3.3.2 Noise, Distortion and Accuracy                                     | 46 |

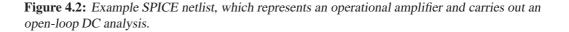

|    |     | 3.3.3 Influence of Configuration Circuitry                               | 47 |

|    | 3.4 | Why Hardware in the Loop for Circuit Evolution?                          | 49 |

| 4  | Ana | log Circuit Simulator                                                    | 51 |

|    | 4.1 | Introduction to Circuit Simulators                                       | 51 |

|    | 4.2 | Operation Principle of Analog Circuit Simulators                         | 52 |

|    |     | 4.2.1 CMOS Device Modeling                                               | 52 |

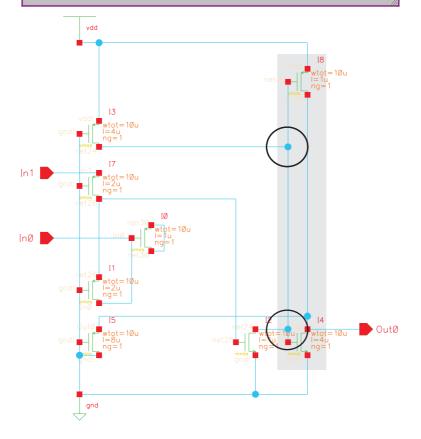

|    |     | 4.2.2 The SPICE Netlist: Circuit Description and Simulation              | 53 |

|    |     | 4.2.3 Floating Nodes and Initial Conditions                              | 55 |

|    | 4.3 | Simulator in the Loop: Berkeley SPICE3f5, NGSPICE                        | 56 |

|    | 4.4 | Extracting Netlists from FPTA Results                                    | 57 |

|    |     | 4.4.1 Level 1: Simulation with Plain Transistors                         | 58 |

|    |     | 4.4.2 Level 2: Simulation Including Resistances of Switches              | 58 |

|    |     | 4.4.3 Level 3: Simulation Including the Whole Configuration Circuitry    | 58 |

|    | 4.5 | Cadence Design Framework                                                 | 59 |

|    |     | 4.5.1 Circuit Simulation in Cadence                                      | 59 |

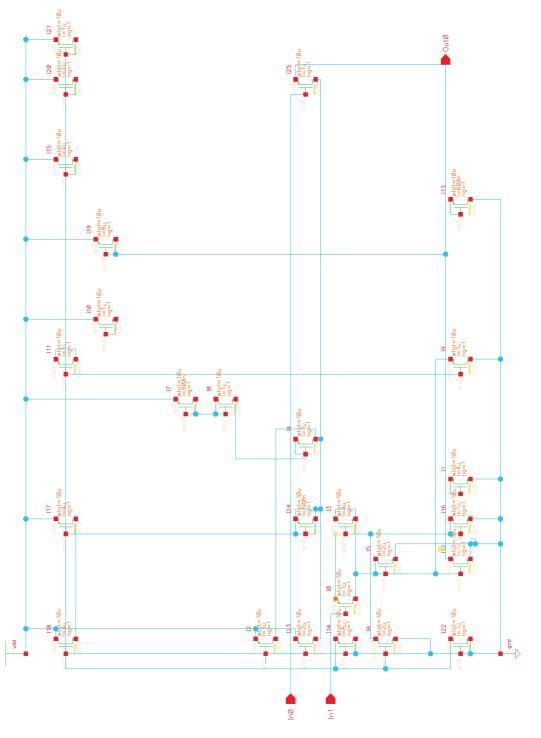

|    |     | 4.5.2 Automatic Schematic Generation Using SKILL                         | 60 |

| 5  | Evo | lution Software Environment                                              | 65 |

|    | 5.1 | Operation Principle of the Modular Evolution Software Framework          | 66 |

|    | 5.2 | The Algorithmic Side of the Evolution Software                           | 66 |

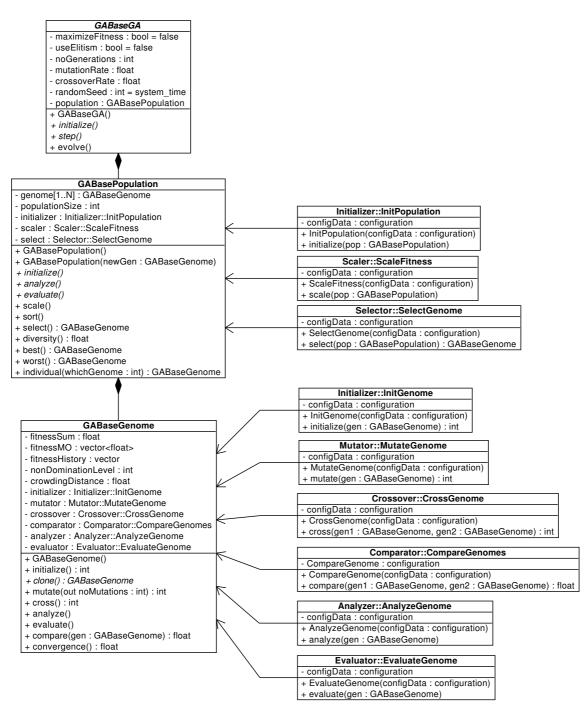

|    |     | 5.2.1 Class Structure of the Evolutionary Algorithm                      | 68 |

|    |     | 5.2.2 Derivation of Custom Evolutionary Algorithms                       | 68 |

|    |     | 5.2.3 Implementation of Modular Genetic Operators                        | 69 |

|    | 5.3 | Analysis and Evaluation of the Genomes                                   | 70 |

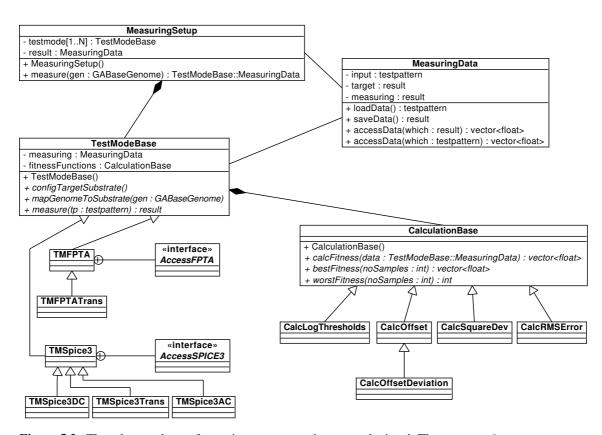

|    |     | 5.3.1 Class Structure of the Testmode-Based Experimental Setup           | 70 |

|    |     | 5.3.2 Targeting Different Evolution Substrates                           | 71 |

|    |     | 5.3.3 Implementation of Fitness Functions and Fitness Calculation        | 72 |

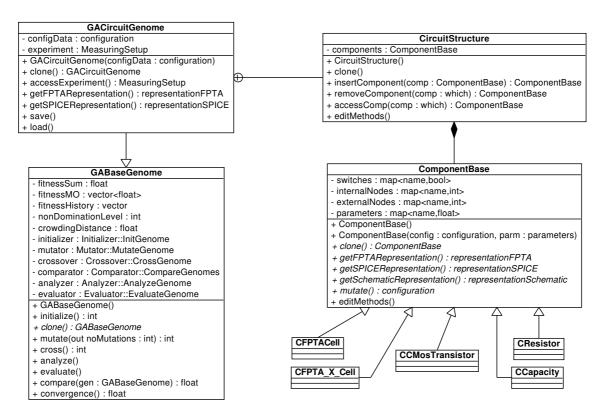

|    | 5.4 | Implementation and Customization of the Genotype                         | 72 |

|    |     | 5.4.1 Class Structure of the Genetic Representation of Analog Circuits . | 72 |

|    |     | 5.4.2 Derivation of Custom Circuit Components                            | 73 |

|    |     | 5.4.3 Modular Genetic Representation of Custom FPTA Architectures .      | 74 |

|    |     | 5.4.4 The Genetic Representation of the Current FPTA                     | 74 |

Contents

|     | 5.5  | Contro   | I Software and User Interface for the Evolution Software          | 74  |

|-----|------|----------|-------------------------------------------------------------------|-----|

| III | [ Ex | xperim   | ents and Results                                                  | 77  |

| 6   | Evol | ution of | f Transferable Circuits on the FPTA                               | 79  |

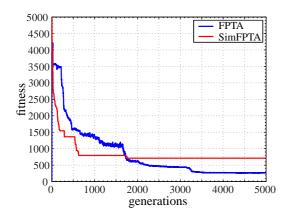

|     | 6.1  | Develo   | ppment of the Evolutionary Algorithm                              | 80  |

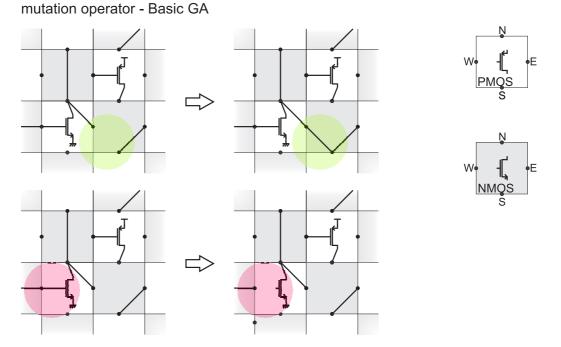

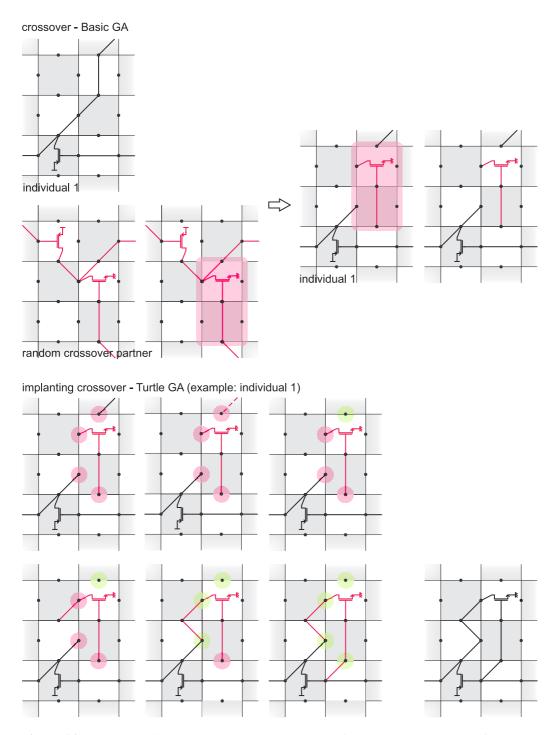

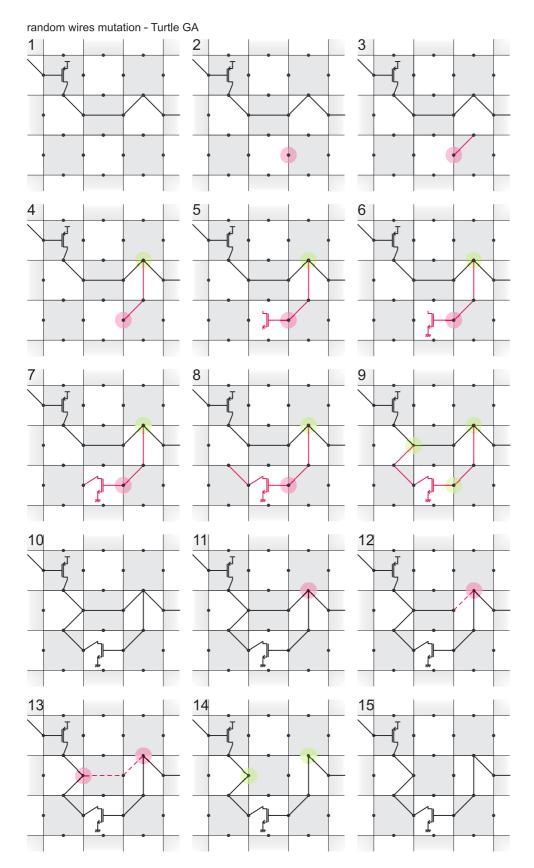

|     |      | 6.1.1    | The Basic GA                                                      | 80  |

|     |      | 6.1.2    | The Turtle GA                                                     | 82  |

|     |      | 6.1.3    | Shortcomings of the Basic GA                                      | 86  |

|     |      | 6.1.4    | Improvements of the Turtle GA Compared with the Basic GA          | 86  |

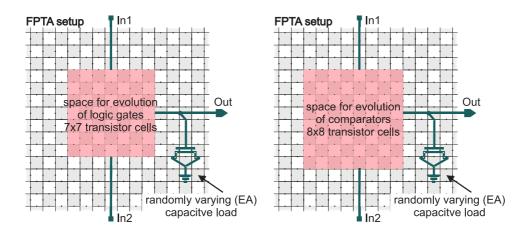

|     | 6.2  |          | mental Setup                                                      | 86  |

|     |      | 6.2.1    | Test Modes for the Logic Gates                                    | 87  |

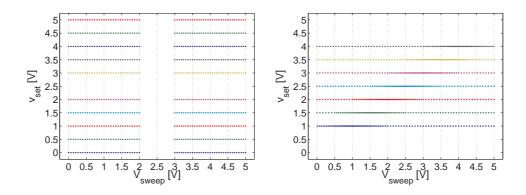

|     |      | 6.2.2    | Test Modes for the Comparators                                    | 88  |

|     |      | 6.2.3    | Simulator Setup                                                   | 89  |

|     |      | 6.2.4    | Fitness Measure                                                   | 89  |

|     |      | 6.2.5    | Estimation and Setup of the EA Parameters                         | 90  |

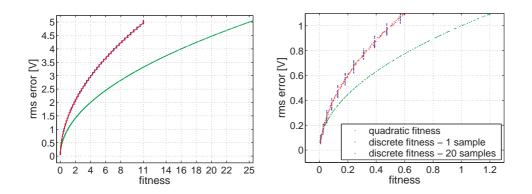

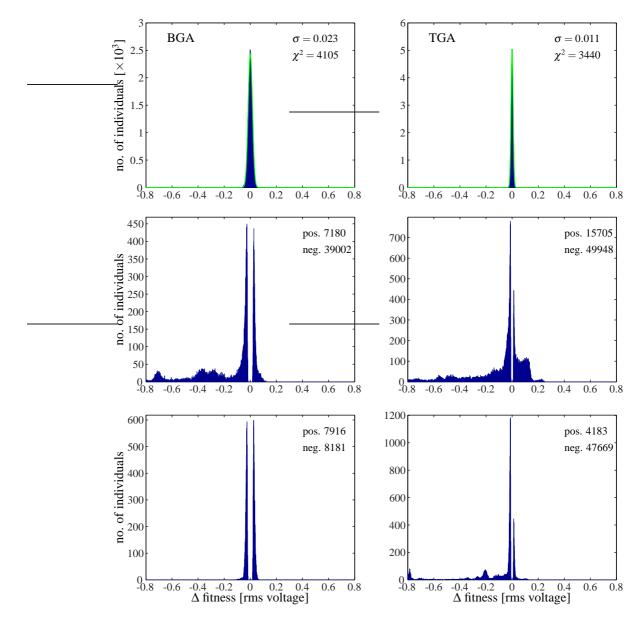

|     | 6.3  |          | ring the Performance of the Variation Operators of Both GAs       | 93  |

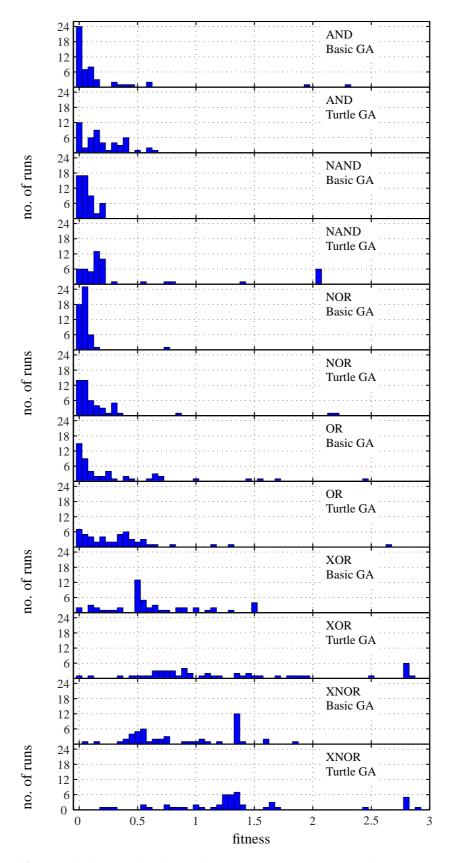

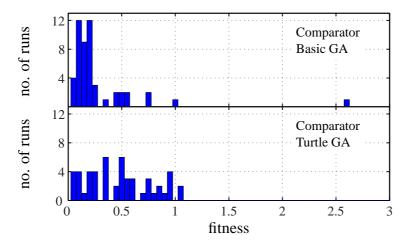

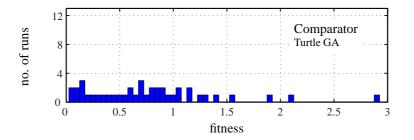

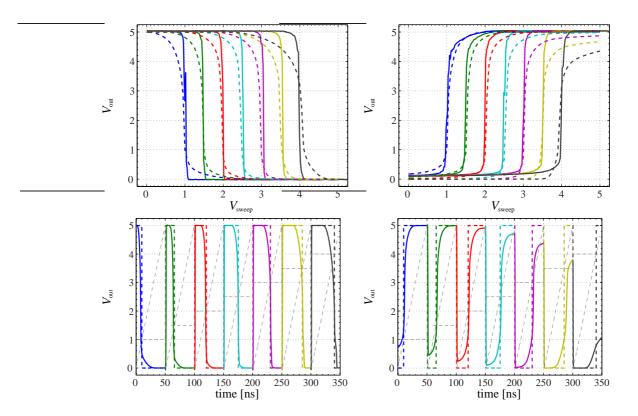

|     | 6.4  |          | s for the Evolution of Logic Gates and Comparators Using Both EAs |     |

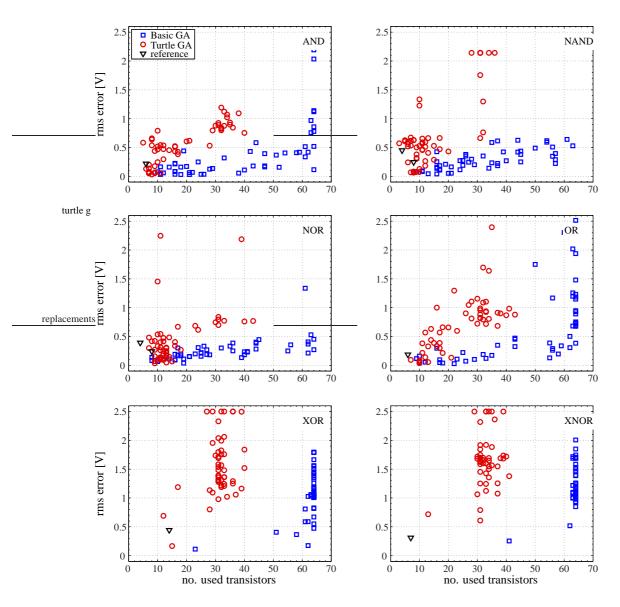

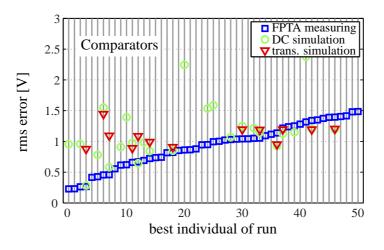

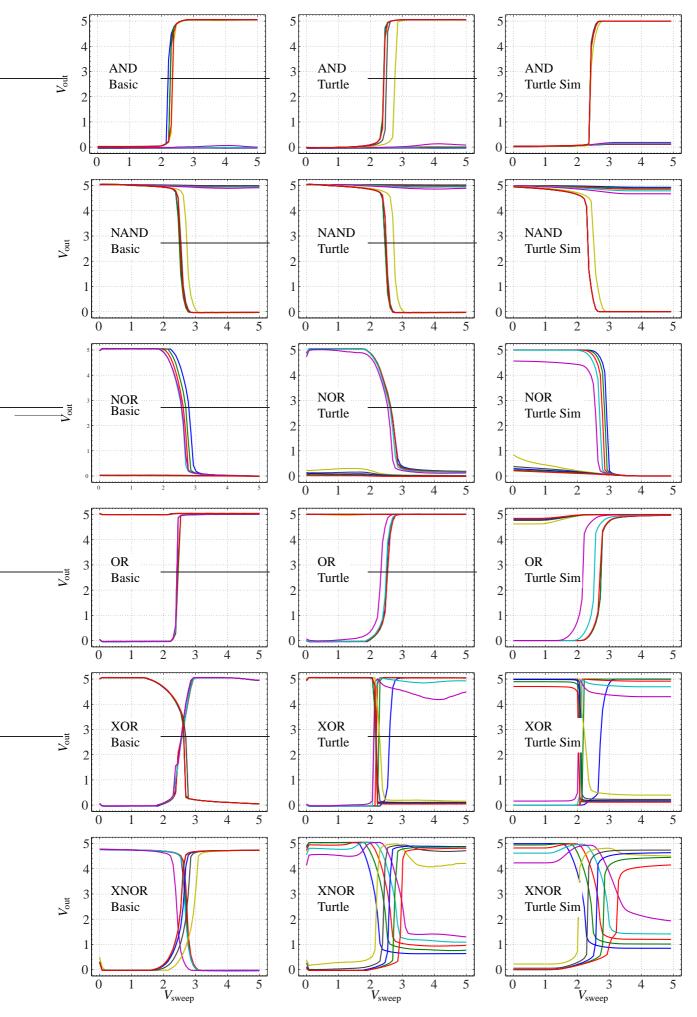

|     |      | 6.4.1    | Comparison of the Results of Both Algorithms                      | 96  |

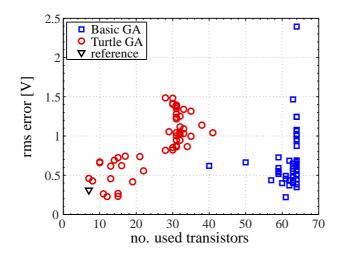

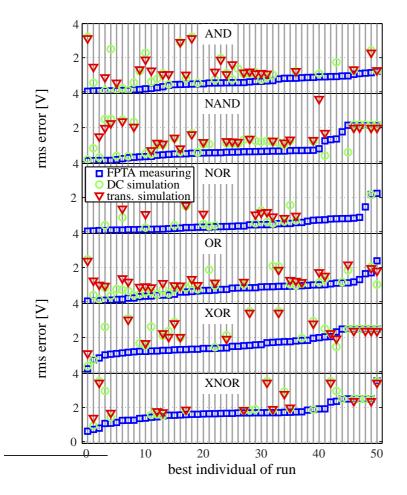

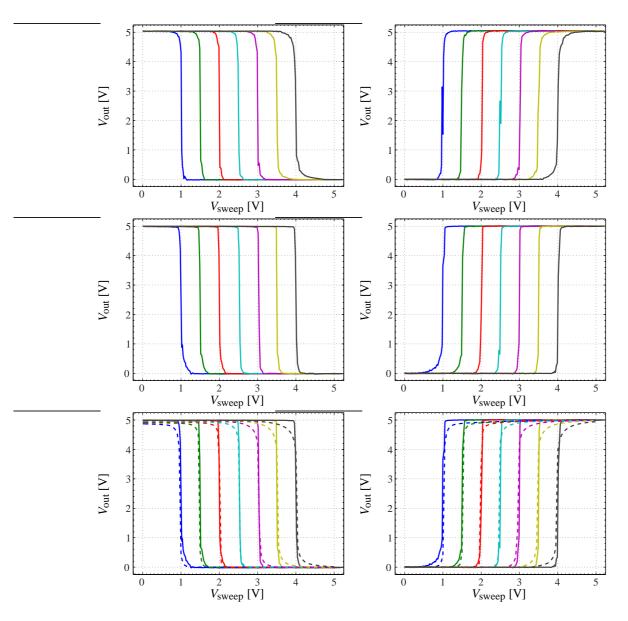

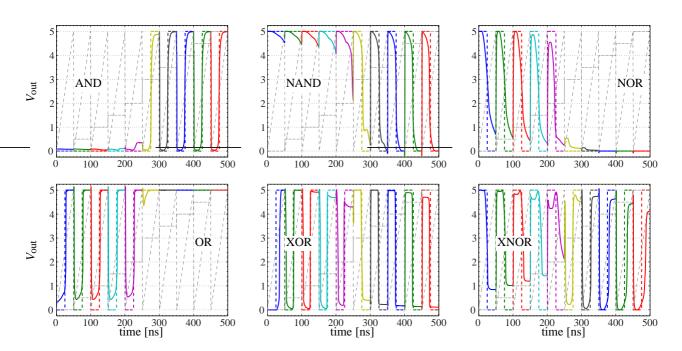

|     |      | 6.4.2    | Verifying the Evolved Circuits in Simulation                      |     |

|     |      | 6.4.3    | Performance of the Evolved Circuits on Different FPTAs            |     |

|     |      | 6.4.4    | How the Algorithm Does FPTA Tricks                                |     |

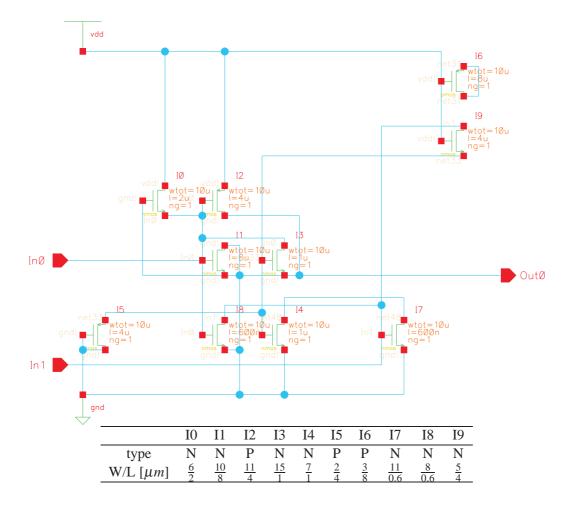

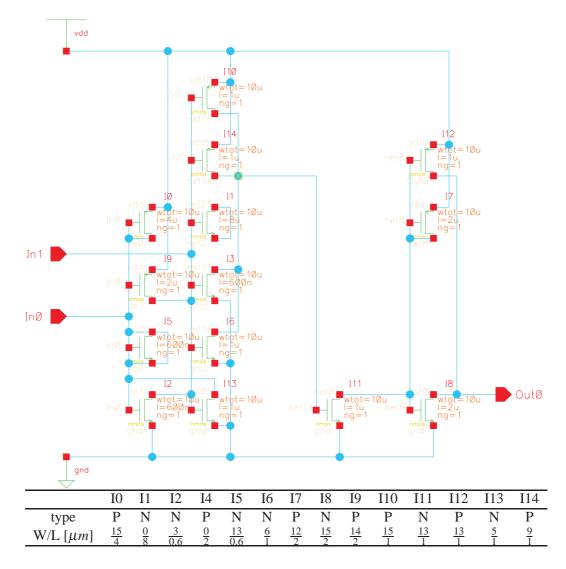

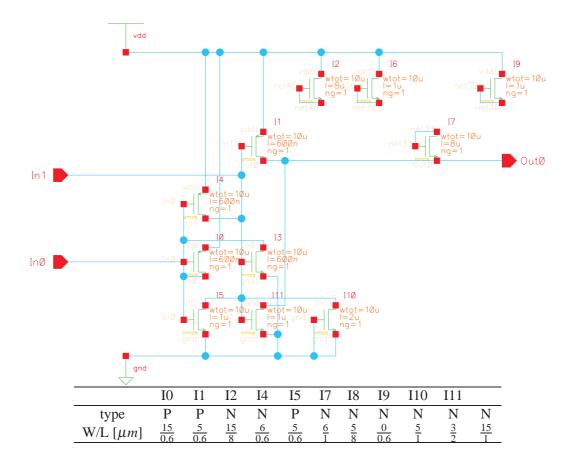

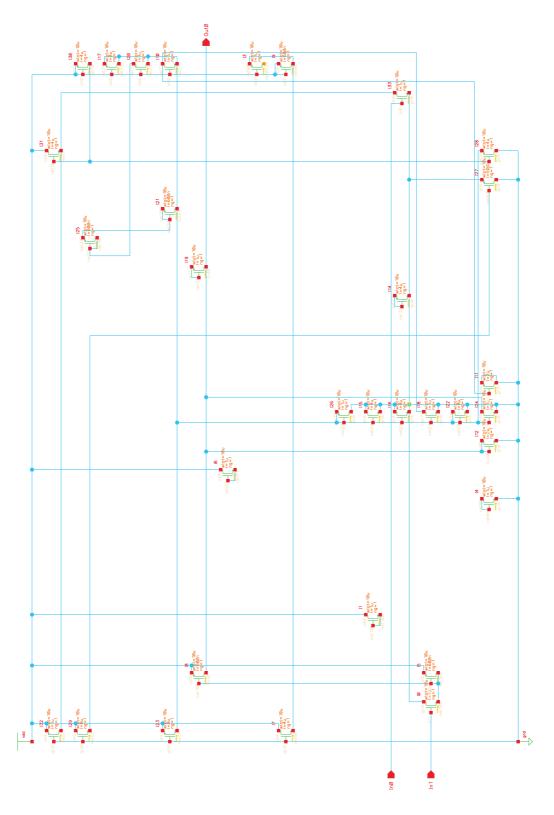

|     |      | 6.4.5    | Understanding Schematics of the Evolved Circuits                  |     |

|     | 6.5  | Conclu   | Iding Remarks                                                     | 112 |

| 7   | Mul  | ti-Obje  | ctive Optimization of the Transistor Circuits                     | 115 |

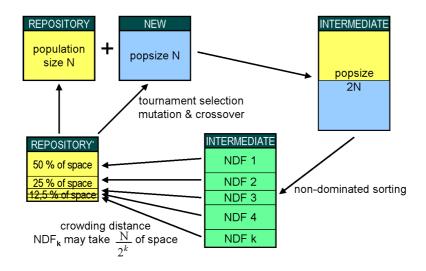

|     | 7.1  | The M    | ulti-Objective Evolutionary Algorithm                             | 116 |

|     |      | 7.1.1    | Variation Operators of the MO-Turtle GA                           | 116 |

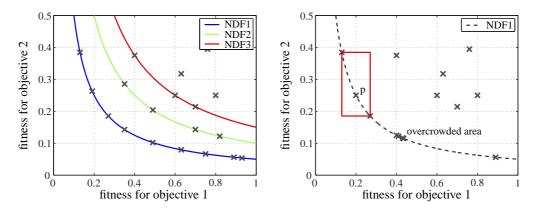

|     |      | 7.1.2    | Non-Dominated Sorting and Crowding Distance                       | 117 |

|     |      | 7.1.3    | Selection Scheme                                                  | 121 |

|     |      | 7.1.4    | The Evolutionary Step                                             | 121 |

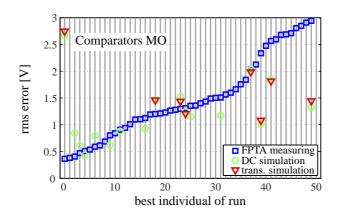

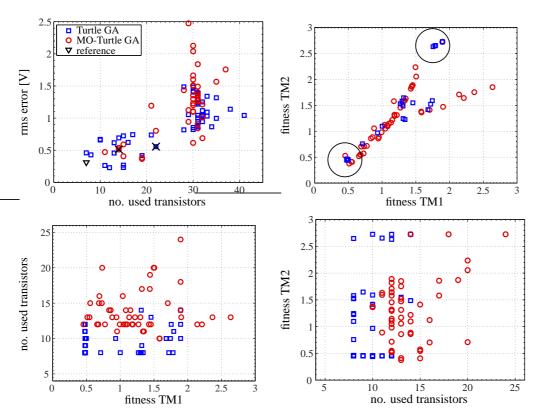

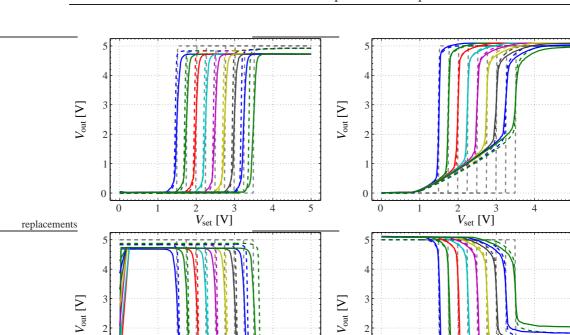

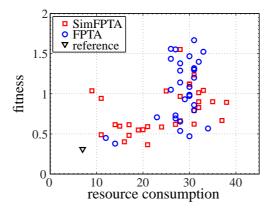

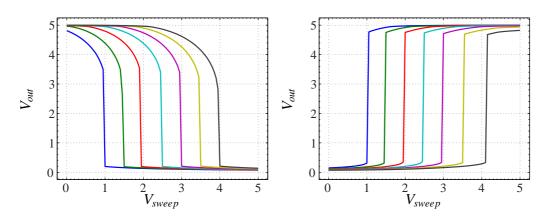

|     | 7.2  | A First  | Benchmark: the Comparators                                        | 122 |

|     |      | 7.2.1    | Experimental Setup                                                | 122 |

|     |      | 7.2.2    | Results and Conclusions                                           | 123 |

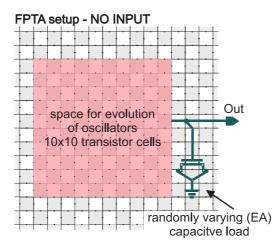

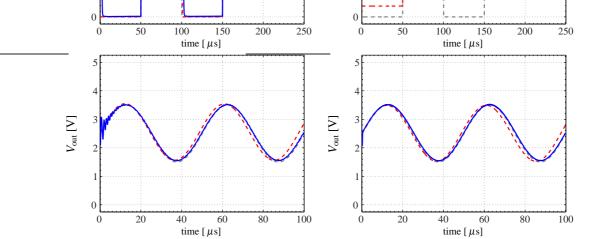

|     | 7.3  | A Trul   | y Multi-Objective Result: Oscillators from Scratch                | 126 |

|     |      | 7.3.1    | Experimental Setup                                                | 126 |

|     |      | 7.3.2    | Test Modes and Fitness Calculation                                | 127 |

|     |      | 7.3.3    | Implications of Multi-Objective Optimization                      | 127 |

|     |      | 7.3.4    | Results and Conclusion                                            | 128 |

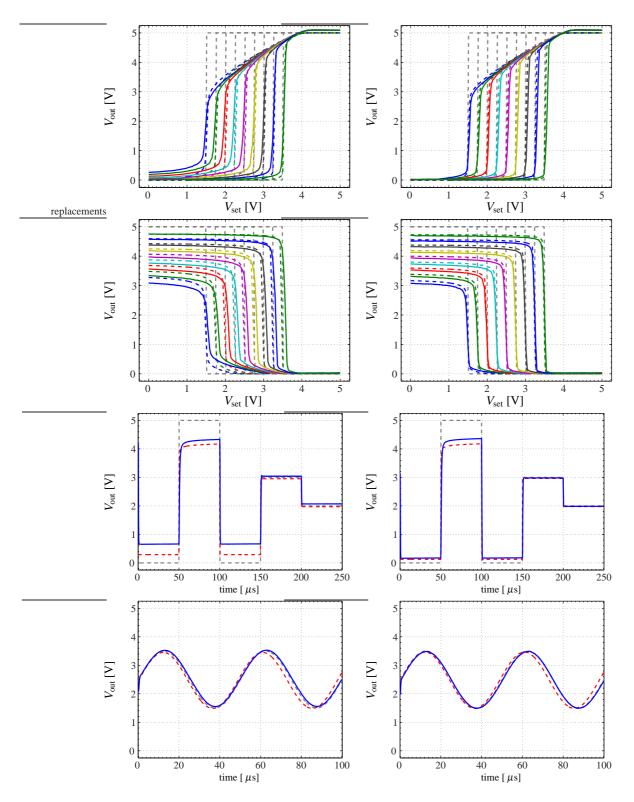

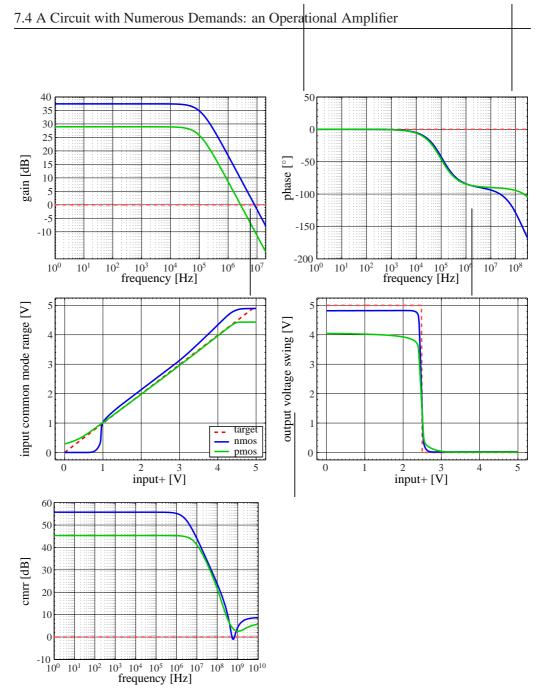

|     | 7.4  | A Circ   | uit with Numerous Demands: an Operational Amplifier               | 132 |

|     |      | 7.4.1    | Setup and On-chip Test Bench                                      | 132 |

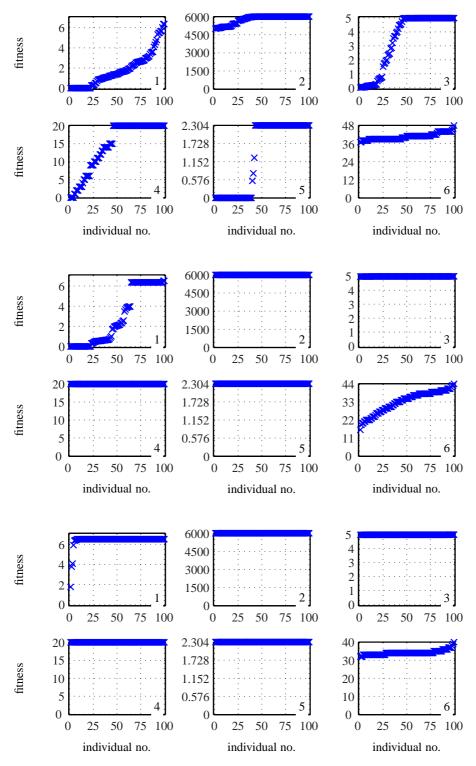

|     |      | 7.4.2    | Test Modes for the Measurements on the FPTA                       | 133 |

|     |      | 7.4.3    | Performance of the Multi-Objective Approach                       | 135 |

|     |      | 7.4.4    | Solutions for the Operational Amplifier                           | 140 |

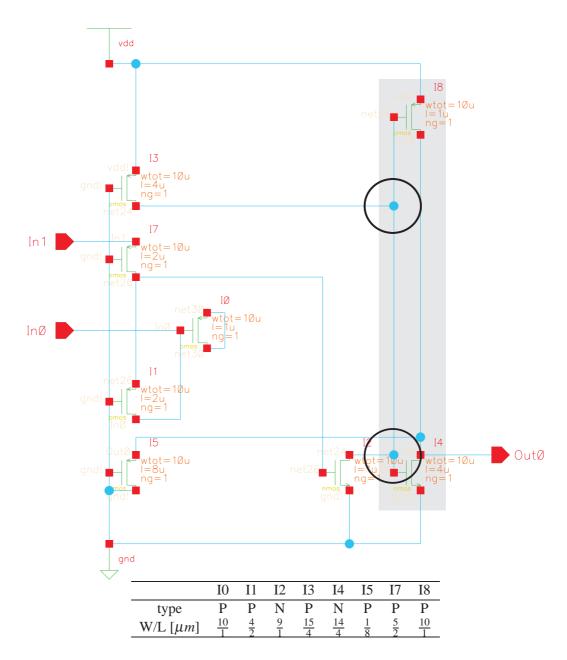

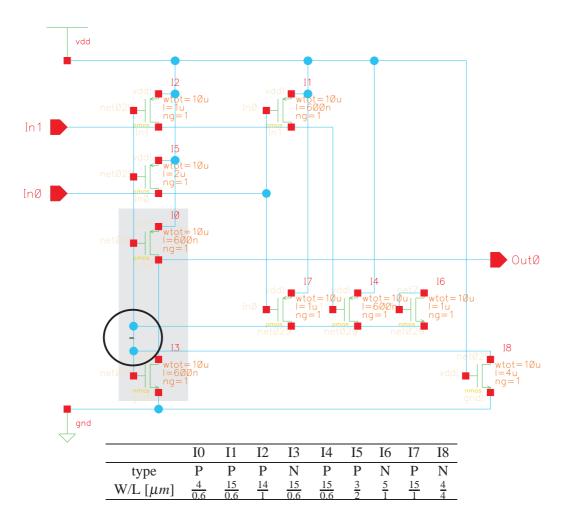

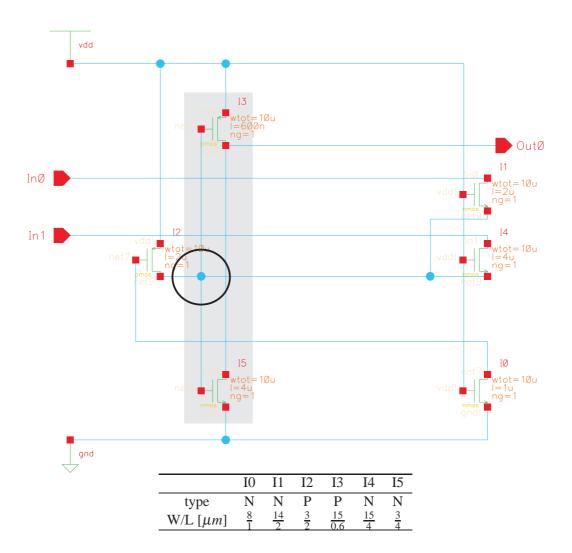

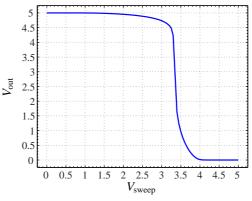

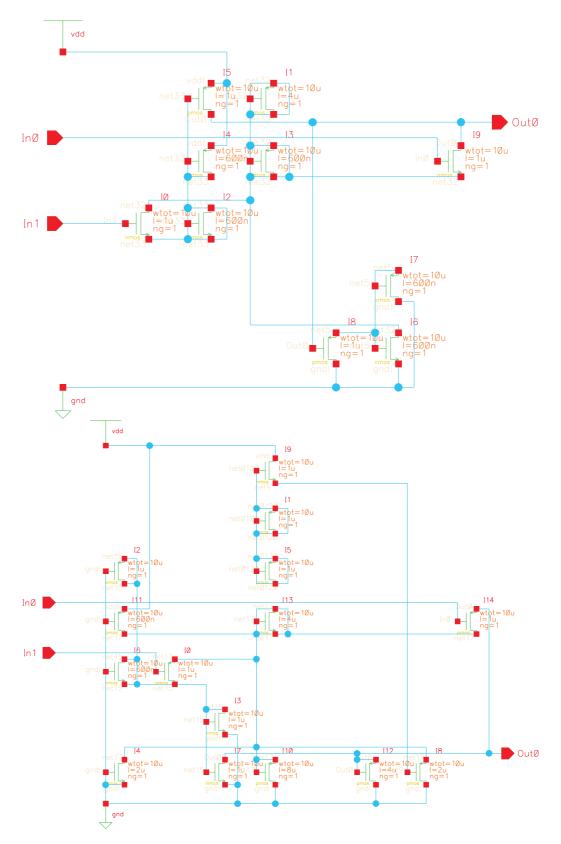

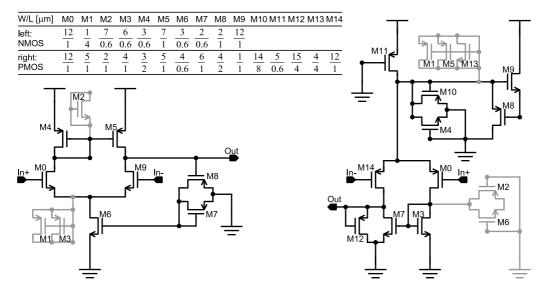

|    |                                    | 7.4.5                            | Schematic Extraction of Good Solutions: Deriving New Design<br>Principles?                                                                                                                                                                                                                 | . 147                   |  |

|----|------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

|    |                                    | 7.4.6                            | Concluding Remarks                                                                                                                                                                                                                                                                         |                         |  |

| 8  | <b>Mod</b><br>8.1<br>8.2           | A Sim<br>8.1.1<br>8.1.2<br>8.1.3 | <b>PTA Architectures</b> ulation Model of the Current FPTA         Performing Experiments with the Simulation Model         Time Consumption for Different Evolution Experiments         Influence of the Parasitic Effects and its Consequences         uents on the Current Architecture | . 152<br>. 153<br>. 154 |  |

|    |                                    | 8.2.1<br>8.2.2                   | Advantages                                                                                                                                                                                                                                                                                 |                         |  |

|    | 8.3                                |                                  | posal for Improvements                                                                                                                                                                                                                                                                     | . 156<br>. 156          |  |

| Su | mma                                | ry and                           | Outlook                                                                                                                                                                                                                                                                                    | 163                     |  |

| Ac | rony                               | ms                               |                                                                                                                                                                                                                                                                                            | i                       |  |

| AĮ | openo                              | dix                              |                                                                                                                                                                                                                                                                                            | iii                     |  |

| Α  | A.1                                |                                  | on Operators                                                                                                                                                                                                                                                                               |                         |  |

| В  | Add                                | itional                          | Schematics of Evolved Circuits                                                                                                                                                                                                                                                             | xii                     |  |

|    | B.1<br>B.2<br>B.3                  | Compa                            | Gates                                                                                                                                                                                                                                                                                      | . xii                   |  |

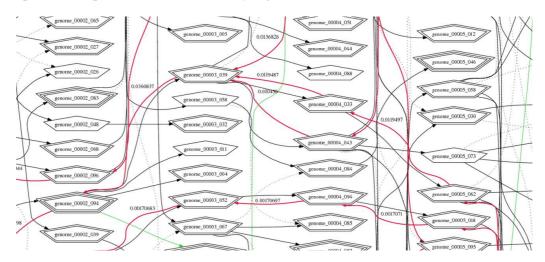

| С  | Trac                               | king th                          | e Course of Evolution: a Side-Result                                                                                                                                                                                                                                                       | xxii                    |  |

| D  | <b>Algo</b><br>D.1<br>D.2          | Logic                            | c Take-Outs<br>Crossover Operator                                                                                                                                                                                                                                                          |                         |  |

| Bi | bliogı                             | aphy                             | •<br>•                                                                                                                                                                                                                                                                                     | XXV                     |  |

|    | Danksagung (Acknowledgements) xxxv |                                  |                                                                                                                                                                                                                                                                                            |                         |  |

# Introduction

Analog circuits are the basis for any electronic device and have thereby tremendously influenced our lives during the last decades. Electronic equipment like satellites, mobile phones or digital cameras would simply not exist, if the technology for integrating hundreds of millions of transistors, which represent the building blocks of analog circuits, was not available. The success story of the transistor began with its invention in 1947 by William Shockley, John Bardeen and Walter Brattain and with its successful integration into a receiver circuit in 1958 [98]. Only the advent of the field effect transistor in 1971 has been the final breakthrough, due to this technology rendered the first microprocessor possible, namely the Intel 4004, which was built of 2.300 transistors. According to Moore's Law [61], the transistor count has exponentially grown during the last 35 years and this lead, for instance, to the Itanium 2 processor [38], which consists of the impressive number of more than half a billion transistors.

An inevitable consequence of the rapidly increasing density of transistors is the development of concepts and tools to effectively and efficiently organize such a great number of components. As a consequence, large circuit designs are usually divided into smaller subcircuits, which can be independently developed and facilitate the description of entire systems. Furthermore, an important low level solution to the problem is to introduce logic circuits as an abstraction layer over the transistors, which, on the one hand, greatly facilitates the design of digital circuits and, on the other hand, makes it possible to describe digital circuits independent from the technology. However, in practice, the underlying analog circuits define the specifications of the digital layer, e.g. speed, input voltage range and noise. According to the differentiation between analog and digital design, both approaches aim for different applications. Analog circuits are needed for any interaction with the real world, e.g. controlling valves or a motor, creating sounds or measuring physical quantities like light intensity, whereas almost every signal processing task can be more easily carried out with digital hardware.

As the need for fast, customizeable signal and data processing units further increased, field programmable gate arrays (FPGAs) emerged, which are meanwhile widely used in various applications. FPGAs are providing a huge number of various building blocks for logic circuits on a single substrate, which can be interconnected with a complex configurable routing scheme, in order to build large digital circuits. The design software, that comes along with those chips, indeed unfolds their real power as it is possible to describe a logic circuit with a hardware description language (HDL) on an abstract level and subsequently the FPGA can be configured in a way that it becomes a physical representation of this circuit. Additionally, it is possible to reconfigure the device an indefinite number of times, which offers the possibility to develop highly customizeable hardware. Once

a circuit is described in a HDL, it will immediately benefit from improvements of new technologies, if an appropriate new FPGA is available.

Driven by the intention of further automating the circuit design process, yet aiming for reducing it to merely a specification of the desired task alongside with a suitable heuristic, which is able to develop a solution circuit, field programmable transistor arrays (FPTAs) entered the discipline of evolvable hardware in the 1990s. The algorithms, that are applied for problem solving in the field of evolutionary computation (EC), derive their operation principles from natural evolution and are widely used as model-free heuristics for solving complex optimization tasks. Thus, they are denoted as EAs. In the case of evolvable electronics, the candidate solutions will be either represented by a configuration bit string, if real configurable hardware is targeted (*intrinsic evolution*), or by a netlist, if a simulator is used (*extrinsic evolution*). Moreover, the model-free nature of EAs is an advantageous property, since this makes it possible to apply them to a great variety of problems without including prior knowledge about possible solutions into the algorithm. As Higuchi stated in 1992 [34], the combination of configurable hardware and evolutionary algorithms suggests itself, as EAs rely on a great number of evaluations of candidate solutions, which can be performed at high speed with a hardware evolution system. Although a real chip is inherently limited by its fixed constraints, it offers considerable advantages: first, evaluation speed is significantly faster than in simulation and, second, it ensures an intrinsic realism of the found solutions, which are bound to work at least on their particular evolution platform. It shall be thereby mentioned that the field of evolutionary hardware is not restricted to electronics, but also exhibits examples of the successful evolution of e.g. antennas [7, 57, 58], that are put on a space mission, wing shapes for supersonic aircrafts [63,66] and orbit trajectories with minimal coverage blackout for telecommunication satellites [99].

Eventually, the initial spark, that set especially the community of evolutionary electronics on fire, has been ignited by Thompson in 1999 [84–86], who not only achieved to successfully evolve a tone discriminator on a Xilinx FPGA, but happened to find a circuit with astonishing properties. For one thing the circuit operated without a clock signal, which is quite unusual from a human designer's point of view, and for another thing evolution seemed to exploit parasitic effects of the substrate in order to get the circuit working. Thompson found unconnected subcircuits which were nevertheless essential for proper operation. Inspired and encouraged by this work, researchers developed various ideas for using configurable architectures as evolution platforms for electronic circuits, e.g. certainly all sorts of field programmable analog arrays (FPAAs) (Anadigm, Cypress, Zetex and [52, 53, 76, 79, 107]) and even a liquid crystal display in the sense of a programmable matter array [30, 31, 60]. Additionally, EAs offered new possibilities for researching fault tolerance, build-in self test (BIST), self-recovery and adaptability [10, 29, 43, 44, 88, 104] to the field of evolutionary electronics.

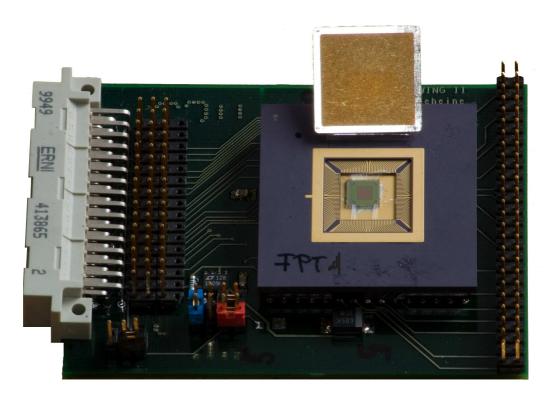

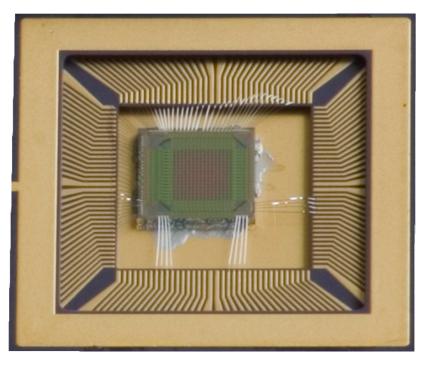

The aforementioned efforts and results within this research field motivate the implementation of FPTAs as the analog counterparts to the already well-elaborated FPGAs and finally lead to the conception and design of the Heidelberg FPTA in 2001 [50–52], which represents the analog configurable evolution substrate for the experiments in this thesis. It is manufactured in a 0.6  $\mu$ m complementary metal oxide semiconductor (CMOS) process and provides 256 configurable transistor cells, which can be variously interconnected and by this means it is possible to realize a great variety of transistor circuits on the Heidelberg FPTA. Aside from application specific FPAAs, where the behavior can be tweaked, but the topology is fixed and an FPTA from the NASA Jet Propulsion Laboratory (JPL) [76,79,107], which already consists of high-level building blocks (configurable amplifier architecture), the Heidelberg FPTA is the only fine-grained substrate in the sense of configurable on the transistor level—in the world. The philosophy behind preferring one of those architectures differs: the use of comparably complex cells aims to quickly find robust solutions for problems that fit the predefined structures, but those solutions are always bound to the constraints of the topology. Contrary to that, the single transistor cells provide a higher degree of freedom to the evolving circuits and therefore offer the possibility to discover new or unusual circuit topologies. However, it has to be kept in mind that finer-grained substrates suffer from increasing parasitic effects although this is not necessarily a shortcoming, as Thompson's results suggest.

Analog circuit design is a discipline of electronic design, that demands a lot of knowledge and experience as well as a considerable amount of creativity in solving diverse problems from the designer. Motivated by the latter challenges, new genetic operators are developed within this thesis aiming to facilitate the understanding of evolved transistor circuits and to make it possible to transfer them to other technologies, that is to verify them in simulation. Thereby, a great hope is to possibly discover any kind of new or innovative design principle. Furthermore, a multi-objective approach is adapted and refined, in order to allow for taking the numerous variables into account, that are required for optimizing the topology and the dimensioning of CMOS transistor circuits. It is shown that the proposed genetic operators and the multi-objective approach can be successfully applied to the evolution of logic gates, comparators, oscillators and operational amplifiers. It is achieved to significantly reduce the resource consumption of evolved circuits and in some cases it is indeed possible to generate a clear schematic of good solutions. Within this thesis, a modular framework for the evolution of circuits on configurable substrates has been developed, which is used to perform the various experiments and is further demonstrated to be useful for modeling FPTA architectures and subsequently assessing their evolvability.

The thesis is organized as follows: part I introduces the principles of CMOS design and modeling (chapter 1) and provides the ideas behind evolutionary algorithms while emphasizing the topics, that are relevant to this thesis (chapter 2). All components of the setup are described in part II: first, the architecture and the properties of the Heidelberg FPTA are shown in chapter 3. Second, chapter 4 provides an introduction to the simulation environment, which is used for off-chip verification of the found solutions. Third, the modular evolution software framework is presented in chapter 5 alongside with a description of how to customize it. Finally, the conducted experiments and the results are discussed in part III. Following the course of research, the new genetic operators are introduced in chapter 6 and their performance in evolving logic gates and comparators is compared to a straight forward implementation of the EA. Owing to the increasing complexity of the tackled problems, i.e. the evolution of oscillators and operational amplifiers, a multi-objective algorithm has been developed and is discussed in chapter 7. To conclude, the algorithm is applied to extrinsic evolution of comparators with a simplified simulation model of the real hardware in chapter 8. Based on these results and the experience gained during this thesis a proposal for an improved FPTA architecture is presented.

# Part I Foundations

# Chapter 1 CMOS Analog Circuit Design

This chapter introduces the basic concepts of CMOS analog circuit design, which are relevant to this thesis. The focus is set on metal oxide semiconductor (MOS) transistors and transmission gates, since those are the basic building blocks of the field programmable transistor array (FPTA), namely the Heidelberg FPTA, which is extensively used for the experiments in this thesis and is described in chapter 3. Characteristics and parasitic effects of the latter devices are discussed, due to mainly the transmission gates (switches) significantly influence the circuits that are realized on the FPTA. Moreover, it is shown how MOS transistors can be used—to a certain extent—as capacitances and resistors, hence, can replace passive components. The reason for this is that no such components are directly provided by the configurable transistor array. An additional aim of this thesis is to verify FPTA circuits in simulation. Thus, CMOS transistor models, which are used by simulators for calculating the behavior of analog circuits are described. Thereby, in analog circuit design, since the aim is to reliably fabricate a fully operational chip, it is crucial to use a suitable and sufficiently accurate model of the respective process for simulation. Lastly, an overview of the CMOS design flow is given, since this work aims at automating several design steps by means of evolutionary algorithms.

During the last two decades, CMOS processes gained importance in the field of very large scale of integration (VLSI) technology, due to some great advantages: on the one hand, the structures in CMOS processes are steadily shrinking and therefore the density of transistors increases. Current technology makes it possible to integrate millions of transistors on one single die (chip). On the other hand, field effect transistors feature a zero current gate, thus, can be successfully applied as well for highly intergrated digital designs. The latter feature has become crucial for implementing systems on a chip, which consist of both, analog and digital circuits on the same substrate. Such systems are denoted as *mixed-signal systems*. The information presented in this chapter is mainly based on the foundations from [4, 81, 82].

## 1.1 Physical Representation of the CMOS Transistor

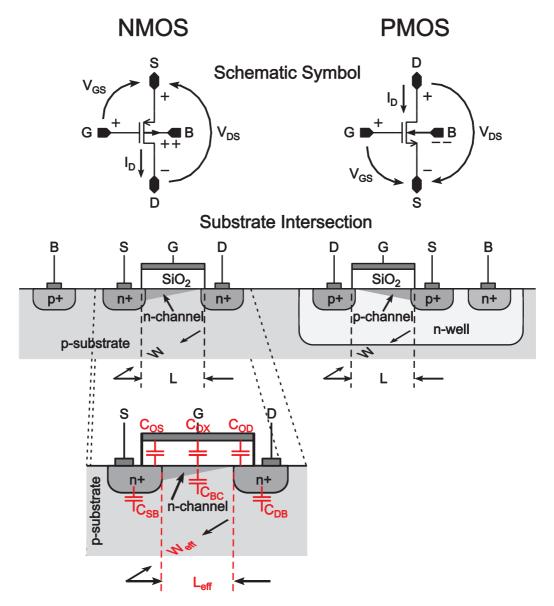

MOS transistors are four terminal electrical devices, which are either used as voltage controlled resistors or current sources in analog circuits and can be realized either as n-channel or p-channel devices in CMOS technology. A lightly doped  $p^-$  substrate is used in CMOS technology, thus, the n-channel transistor can be directly formed with two heavily doped  $n^+$  regions, as can be seen from figure 1.1. In the case of the p-channel transistor, which is realized with two heavily doped  $p^+$  regions, an additional lightly

**Figure 1.1:** *Top:* the symbolic view of a PMOS and an NMOS transistor. *Middle:* a substrate cross section through a PMOS and an NMOS transistor. *Bottom:* the parasitic device capacitances are shown, using the NMOS transistor as an example. Parts of the illustration are taken from [49].

p-channel or n-channel devices

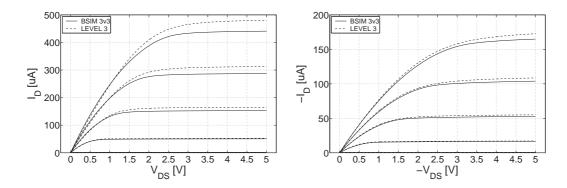

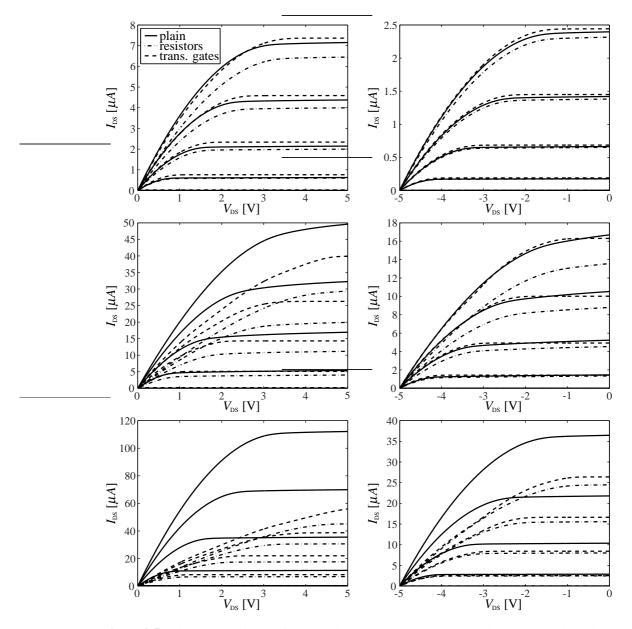

**Figure 1.2:** Example output characteristics of a PMOS (*left*) and an NMOS transistor (*right*) with  $W = L = 2 \,\mu\text{m}$  are graphed for  $V_{GS} = 1, 2, 3, 4, 5 \,\text{V}$ . Thereby, the source voltage of the NMOS was gnd and the source of the PMOS was tied to vdd. Furthermore, the  $i_D - v_{DS}$  characteristics for two simulation models, namely the SPICE level 3 model and the industrial standard BSIM3v3, are compared.

doped  $n^-$  well is necessary. The heavily doped regions are named source (S) and drain (D), while the substrate resp. the n-well is named bulk (B). At the surface, a gate electrode (G), which is separated from the substrate by a dielectric material (silicon dioxide) lies between source and drain.

Considering the n-channel transistor with all four terminals connected to ground, at equilibrium, the source and drain are separated by the depletion regions of the two back-to-back pn junctions. Hence, the resistance between source and drain is very high (>  $10^{12} \Omega$ ). Thereby, the gate and the substrate form a capacitor ( $C_{OX}$ ), enclosing the silicon dioxide as dielectric. If a positive potential  $V_{GS}$  is applied between gate and source, holes will be pushed away from the Si – SiO<sub>2</sub> interface, thereby forming an additional depletion region, that is inverse to those from the pn-junctions. Considering the one-dimensional case, the charge density  $\rho$  of the latter depletion region is given by

$$\rho = q(-N_A),\tag{1.1}$$

with the carrier charge q and the doping strength  $N_A$ . The resulting electric field can be electric field obtained by applying Gausses law and determining the integration constant C by evaluating E(x) at the boundaries of the depletion region (x = 0 at Si – SiO<sub>2</sub> and  $x = x_d$  at the depth of the depletion region in the bulk).

$$E(x) = \int_0^x \frac{\rho}{\varepsilon} dx = \int_0^x \frac{-qN_A}{\varepsilon_{\rm Si}} dx = \frac{-qN_A}{\varepsilon_{\rm Si}} x + C \tag{1.2}$$

with

$$C = \frac{-qN_A}{\varepsilon_{\rm Si}} x_d$$

(1.3)

$$E(x) = \frac{qN_A}{\varepsilon_{\rm Si}}(x_d - x) \tag{1.4}$$

Relating the electrical field to the Fermi potential  $(\Phi_F)$  and the surface potential  $(\Phi_S)$  yields

$$-\int_0^{x_d} E(x)dx = \int_{\Phi_S}^{\Phi_F} d\Phi = -\frac{qN_A x_d^2}{2\varepsilon_{\rm Si}} = \Phi_F - \Phi_S, \qquad (1.5)$$

field effect transistor with isolated gate

back-to-back pn junctions thereby, the Fermi potentials of the semiconductor are given as

p-type:

$$\Phi_F = -V_t \ln\left(\frac{N_A}{n_i}\right)$$

(1.6)

n-type:

$$\Phi_F = V_t \ln\left(\frac{N_A}{n_i}\right)$$

. (1.7)

Further, assuming  $|\Phi_S - \Phi_F \ge 0|$ ,  $x_d$  can be calculated from equation 1.5.

$$x_d = \sqrt{\frac{3\varepsilon_{\rm Si}|\Phi_S - \Phi_F|}{qN_A}} \tag{1.8}$$

The charge underneath the gate can be calculated by inserting the immobile charge of the acceptor ions

$$Q = -qN_A x_d = -\sqrt{2qN_A \varepsilon_{\rm Si} |\Phi_S - \Phi_F|}$$

(1.9)

If a threshold voltage  $V_{\text{TS}}$  is applied to the gate, the substrate between source and drain will become inverted, hence, a n-type channel exists, that allows carriers to flow. This condition is referred to as *strong inversion*. In order to achieve this, the surface potential must become at least  $\Phi_S = -\Phi_F$ . Thus, if  $v_{\text{GS}} = V_T$ ,  $Q_{b0}$  will be

$$Q_{\rm b0} = -\sqrt{2qN_A\varepsilon_{\rm Si}|-2\Phi_F|} \tag{1.10}$$

and in case of a reverse biased pn junction with an according  $v_{SB}$ , this becomes

$$Q_{\rm b} = -\sqrt{2qN_A\varepsilon_{\rm Si}|-2\Phi_F + \nu_{\rm SB}|} \tag{1.11}$$

threshold voltage

strong inversion

Finally, an expression for the threshold voltage can be given by taking the components of  $V_{\text{GS}}$  into account that are necessary to achieve inversion: first, the difference in the work functions between the gate material (polysilicon) and the bulk silicon, denoted as  $\Phi_{\text{POLY}}$ . Second, the gate voltage of  $-2\Phi_{\text{F}} - \frac{Q_b}{C_{\text{OX}}}$ , which is necessary to change the depletion-layer charge. Third, there is an additional voltage  $-\frac{Q_{\text{SS}}}{C_{\text{OX}}}$ , taking the additional  $V_{\text{GS}}$  into account that is caused by material impurities. Thus, using equations 1.10 and 1.11,  $V_T$  can be expressed as

$$V_T = V_{\rm T0} + \gamma \left( \sqrt{|-2\Phi_F + \nu_{\rm SB}|} - \sqrt{|-2\Phi_F|} \right)$$

(1.12)

with

$$V_{\rm T0} = \Phi_{\rm POLY} + -2\Phi_F - \frac{Q_{\rm b0}}{C_{\rm OX}} - \frac{Q_{\rm impurities}}{C_{\rm OX}}$$

(1.13)

and

$$\gamma = \frac{\sqrt{2q\epsilon_{\rm Si}N_A}}{C_{\rm OX}},$$

(1.14)

which is defined as the body-effect coefficient or the bulk-threshold parameter.

Consequently, if inversion is achieved and a voltage  $v_{DS}$  is applied between drain and source, a current  $i_D$  will be able to flow across the channel. Example I-V characteristics are depicted in figure 1.2. It is now assumed that the channel has the width W and  $v_{DS}$  is small. The charge per unit area dl of the channel length can then be expressed by

$$Q_{i}y = C_{\rm OX} \left( v_{\rm GS} - v(y) - V_T \right)$$

(1.15)

inversion of the substrate type

and therefore, the voltage drop along the channel length is

$$dv(y) = i_D dR = \frac{i_D dy}{\mu_n Q_i(y)W}.$$

(1.16)

Thereby,  $\mu_n$  is the average carrier mobility in the channel. Solving the latter equation and integrating along the channel from 0 to L, resp. 0 to  $v_{DS}$ , results in

$$i_D = \frac{\mu_n C_{\rm OX} W}{L} \left[ (v_{\rm GS} - V_T) v_{\rm DS} - \frac{v_{\rm DS}^2}{2} \right], \qquad (1.17)$$

which is called the Sah equation and has been developed by Shichman and Hodges [81] as a model for computer simulation. Note that equation 1.17 is only valid when  $v_{\text{GS}} \ge V_T$  and  $v_{\text{DS}} \le (v_{\text{GS}} - V_T)$ . Thereby, the factor  $\mu_n C_{\text{OX}}$  is defined as the device-transconductance parameter, given as

$$K' = \mu_n C_{\text{OX}} = \frac{\mu_n \varepsilon_{\text{OX}}}{t_{\text{OX}}}.$$

(1.18)

For a detailed description of the physical CMOS model, especially consequences of latch-up, temperature and noise, the reader is referred to [4, 81, 82]. Note, that the n-channel devices are generally denoted as NMOS transistors, whereas the p-channel devices are denoted as PMOS transistors.

#### **1.1.1 Operation Regions**

Furthermore, the relation between  $v_{GS}^{1}$  and  $v_{DS}$  defines the operation region of the transistor. Note that the conditions for  $v_{GS}$  and  $v_{DS}$  in the following are valid for an NMOS transistor, thus, in the case of a PMOS transistor, the relational symbols have to be inverted. A number of 4 operation regions are distinguished: first, the *cutoff* region, where  $v_{GS} = 0$  V and the channel resistance is greater than  $10^{12} \Omega$ . Hence, there is no inversion at all and  $i_{DS} = 0$  A. Second, the *weak inversion* region, for which  $0 < v_{GS} < V_T + nV_{th}^2$ , thus, the absolute drain currents are relatively low and they are exponentially depending on the gate source voltage. Third, for  $v_{GS} \ge V_T + nV_{th}$ , the substrate is actually inverted and the transistor is in the *strong inversion* state, which features a parabolic characteristic for  $v_{DS} \le v_{GS} - V_T$ . This operation region is also called *linear* or *ohmic* region, since the drain source current is almost linear for small  $v_{DS}$ . As the term *ohmic* already suggests, the transistor can be used as voltage controlled active resistor in this operation mode. Fourth, if  $v_{DS} \ge v_{GS} - V_T > 0$ ,  $i_{DS}$  will not further increase and the transistor is in *saturation*. In this case, the transistor resembles a voltage controlled current source.

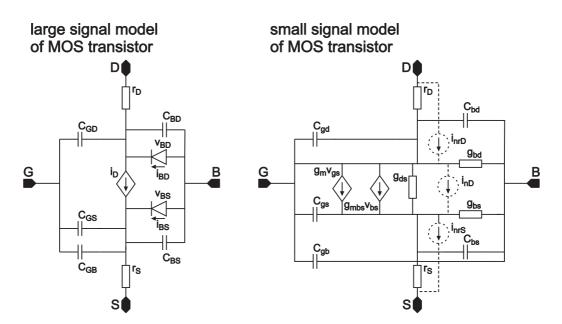

The influence of the different operation regions is not limited to the so-called large signal model presented above. Higher order effects, dynamic behavior and the various intrinsic device capacitances are also depending on the operation mode of the transistor. Some important small signal parameters, e.g. the channel transconductances  $g_m = \partial i_D / \partial v_{GS}$  and  $g_{ds} = \partial i_D / \partial v_{DS}$  strongly depend on the transistor's operation mode. Further, even

the Sah equation, drain current

NMOS and PMOS transistors

cutoff

weak inversion and strong inversion

saturation

<sup>&</sup>lt;sup>1</sup> A lower case letter indicates that the quantity is variable, whereas an upper case letter stands for a constant value.

<sup>&</sup>lt;sup>2</sup> n is the so-called subthreshold slope parameter. It is process specific and it is needed for modeling the exponential behavior of the I-V characteristic in *weak inversion*.

**Figure 1.3:** *Left:* the large signal model of a transistor, which is used to find the DC operating point. *Right:* a linearized small signal model, on which the equations for computer simulations are based. Note that the small signal model equations are depending on the DC operating point.

device mismatch on the silicon die<sup>3</sup> causes threshold voltage variations, that may lead to infeasible strong sensitivity to small variations of  $v_{GS}$ .

#### 1.1.2 Parasitic Capacitances

large signal model

The presented large signal model includes several characteristics of the MOS transistor, such as parasitic capacitances of boundaries, channel resistance and noise. A complete large-signal model is depicted in figure 1.3. Thereby, the diodes are used for modeling the leakage currents and must always be reverse-biased for proper transistor operation. The leakage currents are given by

$$\dot{u}_{\rm BD,BS} = I_s \left[ \exp\left(\frac{qv_{\rm BD,BS}}{kT}\right) - 1 \right]$$

(1.19)

where  $I_s$  is the saturation current of a pn junction, q is the charge of an electron, k is the Boltzmann constant and T is temperature in Kelvin units.

The resistors  $r_D$  and  $r_S$  correspond to the ohmic resistance of source and drain and are only important for high drain currents. Typically, their resistances are in the order of 10  $\Omega$ . The capacitors, formed by the several interfaces, are depicted in figure 1.1 and in figure 1.3. There are three types of such capacitances: first,  $C_{BD}$  and  $C_{BS}$ , which are formed by the depletion regions of the reverse-biased pn junctions of source and

capacitance of the depletion region

<sup>&</sup>lt;sup>3</sup> A 'die' is a small piece of silicon, on which the fabricated circuit is located and which is cut out of the wafer. The dye has to be put in a package and to be connected to its pins, in order to operate it. The wafer, in turn, is a slice of an artificially grown silicon mono-crystal, on which the circuit is built by means of photo lithography and chemical deposition of the different layers (metal, polysilicon, silicon-oxide).

drain respectively. Those capacitances are a function of the reverse-bias voltage and are additionally influenced by their side boundaries to the depletion region, which is denoted as *sidewall effect*, and can be described with

$$C_{\rm BD,BS} = \frac{WL_{\rm diff}}{(1 + V_{\rm D,S}/\Phi_b)^{MJ}} \cdot CJ + \frac{2(W + L_{\rm diff})}{(1 + V_{\rm D,S}/\Phi_b)^{MJSW}} \cdot CJSW,$$

(1.20)

where, W and  $L_{eff}$  define the geometry of the terminal diffusion and  $V_{D,S}$  denotes the terminal potential. The parameters MJ, MJSW, CJ, CJSW, CGXO<sup>4</sup> and  $C_{OX}$  are process dependant constants and  $\Phi_b$  is the working potential of the bulk. The first addend of 1.20 accounts for the area junction at the surface of the terminal diffusion, while the second addend represents the sidewall effects.

Second, the capacitors related to the gate, which are dependent on the operating region parasitic gate of the transistor, namely  $C_{GD}$ ,  $C_{GS}$  and  $C_{GB}$ . Those capacitances, in turn, can be calculated capacitances from  $C_{OS}$ ,  $C_{OX}$  and  $C_{OD}$  according to

$$C_{\rm GB} = \begin{cases} C_{\rm OX} W_{\rm eff} L_{\rm eff} + C_{\rm GS} + C_{\rm GD} = C_{\rm OX} W_{\rm eff} L_{\rm eff} + L_{\rm eff} CGBO & \text{off} \\ C_{\rm GS} + C_{\rm GD} = L_{\rm eff} CGBO & \text{saturation} & (1.21) \\ C_{\rm GS} + C_{\rm GD} = L_{\rm eff} CGBO & \text{nonsaturated} \\ \end{cases}$$

$$C_{\rm GS} = \begin{cases} C_{\rm OS} W_{\rm eff} L_{\rm eff} = W_{\rm eff} CGSO & \text{off} \\ C_{\rm OS} W_{\rm eff} L_{\rm eff} + \frac{2}{3}C_{\rm OX} W_{\rm eff} L_{\rm eff} = W_{\rm eff} CGSO + \frac{2}{3}C_{\rm OX} W_{\rm eff} L_{\rm eff} & \text{saturation} (1.22) \\ C_{\rm OS} W_{\rm eff} L_{\rm eff} + \frac{1}{2}C_{\rm OX} W_{\rm eff} L_{\rm eff} = W_{\rm eff} (CGSO + \frac{1}{2}C_{\rm OX} U_{\rm eff}) & \text{nonsaturation} \\ \end{cases}$$

$$C_{\rm GD} = \begin{cases} C_{\rm OD} W_{\rm eff} L_{\rm eff} = W_{\rm eff} CGDO & \text{off} \\ C_{\rm OD} W_{\rm eff} L_{\rm eff} = W_{\rm eff} CGDO & \text{off} \\ C_{\rm OD} W_{\rm eff} L_{\rm eff} + \frac{2}{3}C_{\rm OX} W_{\rm eff} L_{\rm eff} = W_{\rm eff} CGDO + \frac{2}{3}C_{\rm OX} W_{\rm eff} L_{\rm eff} & \text{saturation} (1.23) \\ C_{\rm OD} W_{\rm eff} L_{\rm eff} + \frac{1}{2}C_{\rm OX} W_{\rm eff} L_{\rm eff} = W_{\rm eff} (CGDO + \frac{1}{2}C_{\rm OX} L_{\rm eff}) & \text{nonsaturation} \end{cases}$$

$$(1.24)$$

and account for the gate-source and gate-drain overlap as well as for the gate-bulk capacitor. Again, the values CGSO, CGDO, CGBO and  $C_{OX}$  are process dependent parameters with the unit  $\frac{F}{m}$ . Thereby,  $C_{OX}$  represents the third type of capacitance, which is depending on the device geometry—the polysilicon of the gate and the bulk silicon form a plate capacitance, with the *SiO*<sub>2</sub> as dielectric—, but not on the operation mode.

gate-source and gate-drain overlap

linearized model

#### **1.1.3 Large Signal and Small Signal Model.**

As yet, the large signal model of MOS transistors is considered, which is used for finding the DC conditions, hence, the DC operating point of the device. Additionally, a linearized small-signal model, graphed in figure 1.3 is available, in order to simplify calculations after the DC operating point is found. The parameters of both models are closely related albeit the small-signal model is only valid for small changes in the vicinity of a given operating point. Consequently, the values of the small-signal parameters strongly depend on the given DC operating point and can take on several alternate forms. Note that the

<sup>&</sup>lt;sup>4</sup> MJ=bulk-source/drain grading coefficient, MJSW=MJ for sidewalls, CJ=zero bias, bulk-source/drain capacitance and CJSW=CJ for sidewalls.

corresponding large-signal subscripts will be lowercase in the small-signal case. Thus, the small signal channel transconductances are given as

$$g_{\rm m} = \begin{cases} \cong \sqrt{2K' I_D \frac{W}{L}} & \text{DC current} \\ - & \text{DC current and voltage} \\ \cong \frac{K' W}{L} (V_{\rm GS} - V_T) & \text{DC voltage} \end{cases}$$

(1.25)

$$g_{\rm mbs} = \begin{cases} - & \text{DC current} \\ \frac{\gamma \sqrt{2I_D \beta}}{2\sqrt{2|\Phi_F| + |V_{\rm SB}|}} & \text{DC current and voltage} \\ \frac{\gamma \sqrt{\beta(V_{\rm GS} - V_T)}}{2\sqrt{2|\Phi_F| + |V_{\rm SB}|}} & \text{DC voltage} \end{cases}$$

(1.26)

$$g_{\rm ds} = \begin{cases} \cong \lambda I_D. & \text{DC current} \\ - & \text{DC current and voltage} \\ - & \text{DC voltage} \end{cases}$$

(1.27)

$$- & \text{DC voltage} \end{cases}$$

(1.28)

Thereby,  $K' = \mu C_{OX}$  is the transconductance,  $\gamma$  is the bulk threshold,  $2|\Phi_F|$  is the strong inversion surface potential,  $\lambda$  is the channel length modulation and *n* is the subthreshold slope process parameter. In practice, process parameters are obtained from measuring the properties of the target technology and fitting the numerical model. The process parameters will be provided by the chip manufacturers, if a chip is fabricated with one of their processes.

#### 1.1.4 Possible Configurations

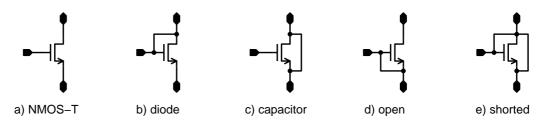

**Figure 1.4:** As can be seen from the figure, a CMOS transistor can be configured as diode, capacitor or as pass transistor (switch, open/closed).

In practice, the bulk of a transistor is connected to vdd (PMOS) or to gnd (NMOS), whereas the three remaining terminals source, drain and gate are used for assembling transistors to circuits. Possible configurations of the MOS transistor are depicted in figure 1.4. Transistors can be configured as diodes or capacitors, although those components could also be fabricated without using a transistor structure. Examples for the different configurations are depicted in figure 1.4. Contrary to that, it is not possible to integrate resistors with a sufficiently high resistance on the dye, due to the fact that the sheet resistance of polysilicon is very low in standard CMOS processes. If resistances greater than a few k $\Omega$  are desired, either a specialized process will have to be chosen, that features an

diodes, capacitors and active resistors

additional layer of high-resistive polysilicon, or transistors will have to be used as active resistors, as described in section 1.1.1. Thereby, the transistor has to be operated in the linear region, in order to achieve the desired I-V characteristic. Furthermore, it is possible to realize resistors as switched capacitors, which provide a high degree of linearity, although such circuits require nonoverlapping clock signals with a much higher frequency than the voltage variations. Switched capacitors are mostly used in telecommunication applications.

### **1.2 Realizing Switches with Transmission Gates**

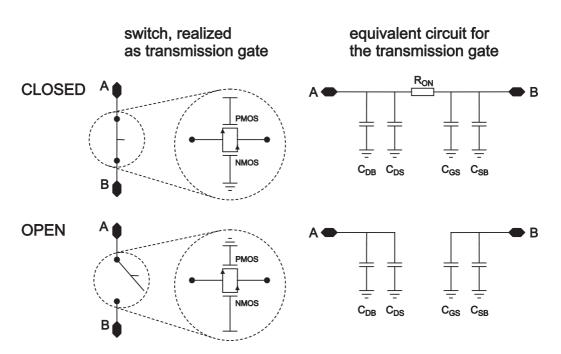

Transmission gates are one of the most important circuits of the FPTA chip, which is used for the experiments in this thesis and is introduced in chapter 3. The reason for this is that the manifold configuration options of the transistor array are provided by a large number of switches, hence, transmission gates. Thus, it is possible to realize a great number of almost freely scalable circuits on the FPTA simply by opening or closing the according switches. One pass transistor, which is closed by applying vdd/gnd (NMOS/PMOS) and opened by applying gnd/vdd to the gate (NMOS/PMOS), as depicted in figure 1.4, is the most simple realization of a switch. A major drawback of the latter approach is the limited input voltage range, due to the constraint  $V_{GS} > V_T$  (NMOS) or  $V_{GS} < V_T$  (PMOS). This can be overcome by combining both, NMOS and PMOS, in order to compensate the limited  $V_{GS}$  of the respective other transistor. Consequently, as can be seen from figure 1.5, transmission gates consist of a PMOS and an NMOS transistor in parallel, which are opened and closed with gate voltages of opposite polarity respectively.

#### 1.2.1 Parasitics of Transmission Gates

As can be seen from the small signal model of transmission gates in figure 1.5, these switches possesses several parasitic capacitances and, in the on state, a finite parasitic resistance. Since, in the case of a transmission gate, the gate voltages are either vdd or gnd, the transistors can be considered to be either in the cutoff or in the linear operation mode. The on-resistance of a transmission gate can be obtained from equation 1.17:

$$r_{\rm on} = r_{\rm DS} = \left(\frac{\partial i_D}{\partial v_{\rm DS}}\right)^{-1} = \left(K'\frac{W}{L}(vdd - v_S - V_T - v_{\rm DS})\right)^{-1}.$$

(1.29)

Thereby, the channel length modulation  $\lambda$  is omitted. The total parasitic capacitance is obtained by simply adding the according parasitic capacitances from section 1.1.2.

The parasitics of transmission gates are of great importance to this thesis, due to the fact that they are extensively used as switches for realizing the configuration options of the FPTA, which is used for the presented experiments and is introduced in chapter 3. The on-resistance is considered to greatly influence the circuits, that are configured on the transistor array, since the mean on-resistance of the switches is about  $330 \,\Omega^5$ . Due to this fact, the latter resistances have to be considered for testing FPTA circuits in SPICE simulations, in order to obtain the correct behavior. The SPICE simulations are described

realizing the configurability of the FPTA

on-resistance

<sup>&</sup>lt;sup>5</sup> The mean on-resistance of the gate switches is  $2310 \Omega$ . However, the influence of the gate resistance is not as significant as the source and drain resistances.

**Figure 1.5:** The realization of an open and a closed CMOS switch as transmission gates is depicted. Additionally, small signal models of an open and a closed switch are provided respectively, in order to illustrate the parasitic capacitances and resistances of such switches.

parasitic capacitances

in chapter 4, section 4.4. Contrary to that, it is assumed that the parasitic capacitances are negligible, since their signal bandwith is estimated to be  $f_{-3 \text{ dB}} = 66.7 \text{ MHz}$  (see [49], chapter 1), while the configured circuits are operated at a maximum speed of 4 MHz.

### **1.3 CMOS Transistor Modeling**

The large-signal model of the MOS transistor, which is previously described in section 1.1, is useful for getting an insight into the operation principles of those devices and for hand calculations, although important second-order effects are not covered. Thus, more accurate simulation models are required for successfully fabricating application specific integrated circuits (ASICs). Consequently, the fabrication facilities provide according simulation parameters for their target processes to the designer. As yet, SPICE simulators support more than 60 different models, which cover different technologies and complexity levels. Each model consists of parameterized mathematical equations and according target technology dependent parameters, that are extracted by researchers at the respective fabs. While the mathematical model is included in the SPICE simulator and is most often public domain, the parameters themselves are company property.

The main shortcoming of the large-signal model from section 1.1 is the fact that it is no longer valid for small device sizes down to  $0.8 \,\mu\text{m}$  and moreover does not include effects like velocity saturation and intrinsic parasitic resistances. Consequently, more complex models have been developed, which provide the possibility to accurately describe the behavior of devices with sizes down to  $0.1 \,\mu\text{m}$ . Thereby, important models are: first,

simulation models with increasing complexity and accuracy the SPICE level 3 model, which covers the range down to about  $0.8 \,\mu\text{m}$ . Second, the BSIM3v3 model, which covers the range down to  $0.25 \,\mu\text{m}$  and, finally, the BSIM4v4 model, which is valid for device sizes down to about  $0.1 \,\mu\text{m}$ . Two models are briefly introduced in the following, namely the SPICE level 3 model, which is already quite accurate and is not yet too complex, and the BSIM3v3 model, which is used for the process, with which the FPTA of chapter 3 is fabricated. The BSIM model is not presented in detail, due to the volume of complex equations, that are necessary to describe it. A more detailed description of the BSIM equations can be found in [9, 24].

#### 1.3.1 SPICE LEVEL3 Simulation Model

Contrary to the basic large-signal model of the MOS device, narrow and short channel effects (<  $3 \mu$ m) as well as temperature effects are considered in the SPICE level 3 model. Therefore, numerous additional parameters have to be taken into account for the calculations and also the equations have to be accordingly modified. The main parameters and considerations of the level 3 model are shown in table 1.1. Despite the fact that the level 3 model already includes numerous process parameters, like substrate properties and operating conditions, e.g. temperature and saturation, it is only valid for structures not smaller than 0.8  $\mu$ m. Consequently, as structures of up-to-date processes are shrinking down to 60 nm and also the FPTA chip, which is used for the experiments in this thesis, is fabricated with a smaller 0.6  $\mu$ m process, the BSIM3v3 model is briefly introduced in the next section.

valid down to 0.8 µm

#### 1.3.2 BSIM3v3 Simulation Model

The equations of the BSIM3v3 model are far more complex, due to the fact that all relevant parasitic effects down to structures of  $0.25 \,\mu$ m are included. As a consequence of this, 93 parameters are necessary to describe a PMOS or NMOS transistor with the BSIM3v3 model. In addition to the device parameters, capacitances and resistances of metal lines are also taken into account for the parasitic extraction of circuits. Moreover, the BSIM3v3 model can be successfully applied for simulating both analog and digital circuits and therefore has become the industry standard MOS transistor model. The most important deep-submicron effects, that are included in the BSIM model are listed in the following:

valid down to  $0.25\,\mu m$

- threshold voltage reduction

- mobility degradation due to a vertical field

- carrier velocity saturation effects

- drain-induced barrier lowering

- channel length modulation

- subthreshold (weak inversion) conduction

- parasitic resistance of source and drain

- hot-electron effects on output resistance

| characteristic             | considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| drain current              | W/L is replaced with the effective size of the device,<br>by subtracting the gate overlap regions. For the cal-<br>culation of the effective drain-source voltage ( $v_{DS}^{eff}$ ),<br>the narrow-width threshold adjustment factor for the<br>channel, the substrate doping concentration and the<br>actual extent of the diffusion and metallurgical junc-<br>tion is taken into account.                                                                                                               |

| threshold voltage          | In addition to the geometrical implications, which are<br>described for the drain current calculation, the intrin-<br>sic threshold, based on the work function of the sub-<br>strate and the static feedback threshold adjustment is<br>considered.                                                                                                                                                                                                                                                        |

| effective carrier mobility | Depending on $v_{DS}^{eff}$ , the mobility of the minority<br>charge carriers degrades. Thus, it is accounted by an<br>effective carrier mobility. Moreover, the carrier mo-<br>bility is temperature dependend, which is considered<br>by a temperature coefficient.                                                                                                                                                                                                                                       |

| saturation voltage         | Again, the implications of $v_{DS}^{eff}$ are presumed. Additionally, the reduced charge carrier mobility is considered for the calculation of the saturation voltage.                                                                                                                                                                                                                                                                                                                                      |

| channel length modulation  | The channel length variation depends on the differ-<br>ence between $v_{DS}^{eff}$ and $v_{DS}^{saturation}$ and therefore a satu-<br>ration field factor is included in the model.                                                                                                                                                                                                                                                                                                                         |

| weak inversion             | The transition between the <i>cutoff</i> and the <i>strong in-</i><br><i>version</i> region of a transistor, namely the <i>weak in-</i><br><i>version</i> is also included in the level 3 model. This<br>is achieved by providing additional equations and a<br>subthreshold slope factor, which are used to model<br>the exponential behavior of $i_D$ in the <i>weak inversion</i><br>region. Thereby, <i>weak inversion</i> will be reached, if<br>$v_{GS}$ is close to the threshold voltage ( $V_T$ ). |

**Table 1.1:** The main parameters and considerations of the level 3 model are shown. Although, the level 3 model already considers numerous process parameters, it is only valid for processes above  $0.8 \,\mu$ m.

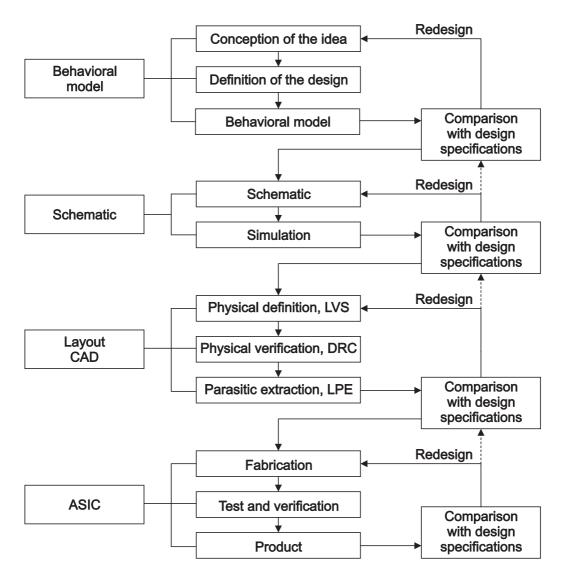

## 1.4 CMOS Design Flow

behavioral model

schematic

Nowadays, there are actually four independent 'realities' in which a circuit exists: a behavioral model, the schematic, the layout and the final ASIC. First, the behavioral model describes the desired properties of the circuit in an abstract modeling language. Second, the schematic is a symbolic sketch of interconnected components. It contains the information about the circuit architecture, the type of the components and their basic component parameters, e.g. the W/L ratio of transistors and the values for capacitors and resistors.

**Figure 1.6:** The design flow for an ASIC is shown. The first step represents the conceptional stage, where the desired behavior of the chip is described. The necessary types of circuits are designed and are divided and structured in hierarchical schematics in the second step. First simulations can be performed with both the behavioral model and the schematics, hence, with the first two design loops it is achieved to remove conceptional faults. Subsequently, an according layout of the circuit has to be drawn, in order to define the physical representation of the ASIC and to be able to extract the whole parasitic information from it. Thereby, the third design loop will be closed, if all specifications are met. Finally, after the manufacturing facilities have fabricated the real chip, it can be tested in the real world and shipped, once the fourth design loop of testing is completed.

At this level, it is already possible to predict the behavior of the drawn circuit by using the equations from section 1.1, although the circuit is not yet specified for all physical properties of a target technology in the real world. Third, the layout of a circuit is a floorplan of the different layers of metal, silicon-oxide, polysilicon and diffusion, that shall be

layout

piled up on a silicon substrate (wafer), in order to fabricate the fourth representation of the circuit, namely the actual ASIC. For a successfull transfer of a circuit from the schematic to an operational chip, powerfull design tools are available, in order to deal with thestill increasing—high complexity of current systems, for which millions of transistors are intergrated on one single die. Those tools consist of editors for creating schematics, CAD tools for drawing the layout and comprehensive simulation environments, which allow for creating various test benches and for considering all significant parasitic effects. In order to achieve this, numerous steps are necessary: first, a validity check of the schematic and a design rule check (DRC) have to be successfully performed. Second, the components of the schematic have to be identified in the layout. This process is denoted as layout versus schematic (LVS). Subsequently, all device parasitics can be extracted from the layout with the layout parameter extraction (LPE). If the LVS and the LPE are done, simulations of back-annotated layouts<sup>6</sup> can be carried out and therefore crosstalk, parasitic layer and wire capacities as well as device mismatching are included in the simulation. Those extensive simulation and verification methods provide an elaborate design flow, graphed in figure 1.6, that reliably yields fully operational ASICs.

real world chip

<sup>&</sup>lt;sup>6</sup> The term 'back-annotated layout' denotes a layout in which, on the one hand, each component is identified with its respective representation in the schematic and, on the other hand, all parasitic effects, which are extracted from the layout, are provided for simulation.

## Chapter 2

# **Evolutionary Algorithms**

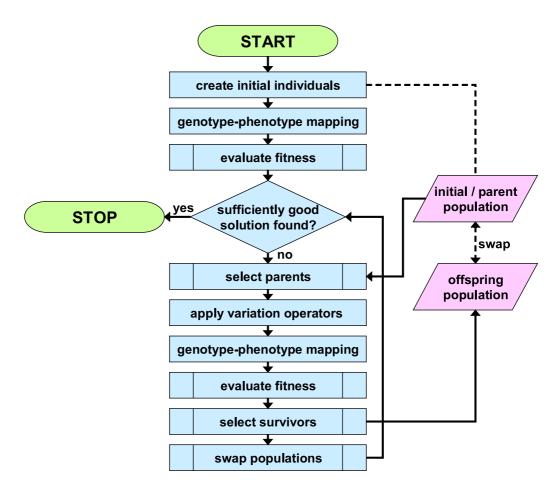

The operation of an EA is inspired by the principles of natural evolution. This chapter introduces these principles on the macroscopic level, where organisms have to cope with the challenges of their environment, and on the microscopic level, which provides and develops the construction plans for building those organisms. Furthermore, it is shown how the ideas, which are drawn from the mechanisms of natural evolution, can be formulated as an evolutionary algorithm. The main constituents of such an algorithm are described and some extensions to the basic principle are presented. Theoretical considerations of desireable properties of an evolutionary approach are made, in order to substantiate their suitability for a great variety of tasks. The performance of evolutionary approaches as global optimizers and their properties as model-free heuristics are discussed. Moreover, the consequences of feasible and infeasible solutions are described and it is shown how infeasible solutions can be handled. A solution, of which not all properties can be tested in a given environment, is thereby denoted as infeasible solution. The focus is set on analog circuit evolution whenever examples are given in this chapter.

Evolutionary algorithms became very popular during the last 20 years, due to their reputation for being general purpose automated problem solvers. The advent of genetic programming (GP) [47] even lead to the opinion that EAs can be used as sources of invention. Indeed, EAs have been successfully applied to a great variety of optimization problems as, for instance, search, engineering design, scheduling and neural network training. The most intriguing advantage of using EAs is their generality, i.e. good solutions can be found without prior knowledge about the tackled problem. The latter generality will be an important property, if either the problem is too complex to be able to develop a simple solution, or it is desired to find unconventional or alternate designs.

## 2.1 Inspiration from Natural Evolution

The manifold algorithmic approaches within the field of EC are inspired from natural evolution mechanisms. Hence, the vocabulary is also borrowed from natural genetics. Natural evolution achieved to produce an enormous variety of species, which are perfectly matched to their ecological niches. It is noticeable that about 2 million different species are currently living on earth and it is estimated that, including those which already again vanished, there existed in the order of a billion more. Natural evolution has obviously been able to develop these species in a manner that they are able to coexist by fitting into different ecological niches. However, there is interference and concurrence between different species. Moreover, the environment is steadily changing and therefore, each species has to be continuously adapted, in order to be able to survive. Looking at nature's achievements from an algorithmic point of view, evolution found solutions, represented by the individuals of the different species, to a given problem specification, namely to survive in a present environment. Thus, it is an interesting idea to see natural evolution as a general optimization algorithm. The question is now, on the one hand, how the natural concepts can be implemented in an algorithm and, on the other hand, if such an evolutionary algorithm will be suitable for solving problems. First of all, it is necessary to take a more detailed look at how natural evolution actually works and to derive its main principles.

#### 2.1.1 Darwinian Evolution

Charles Darwin proposed his theory "On the Origin of Species" in 1859 which is, alongside with the insights of molecular genetics, the foundation of evolutionary biology. An essential statement of Darwin's model of natural evolution is the survival of the fittest, i.e. those individuals, which are best adapted to their environment will more likely reproduce and survive. This phenomenon is denoted as natural selection and will necessarily occur, if a population of individuals has to compete for a limited amount of ressoures and has to escape from the same predators. Thereby, the basic driving forces of reproduction and the will to survive is presumed to exist—at least to a certain extent—in all individuals.

Furthermore, if there was always only the same pool of individuals producing offspring, the individuals would, on the one hand, be able to specialize to their ecological niche but, on the other hand, the population would not be able to develop truly new features in order to adapt to a changing environment, since no really new genetic information would arise within the individual's genomes. Nevertheless, species are able to adapt to changing or different environments, due to a second important phenomenon, that actually introduces random changes to the individuals, namely mutation. The latter effect takes place with a certain probability during reproduction and results in a variation of traits in the offspring generation. As a consequence of iterated reproduction, mutation and natural selection, the traits of the individuals of the current generation, which produce offspring, are preserved. Thus, their traits are newly combined and slightly modified present in the next generation. The various individuals of the new generation then have to face the challenges of their environment, hence, solely the advantageous traits of those, which survive long enough to again produce offspring, are preserved, while other features are discarded.

All higher life-forms reproduce by sexual mating. Thus, all individuals, which are

natural evolution as a general optimizer

the variety of species

natural selection: survival of the fittest

variation through mutation

able to produce offspring with each other belong to the same species. Consequently, it will be principally possible that new species arise, if the diversion of subpopulations of one species reaches a point where sexual reproduction between those subpopulations is no longer possible. Geographical separation can be a reason for the latter effect. It is believed that fundamental diversification of the species has already taken place at a vary early stage of life and once there were no free ecological niches left, there was no room for new species. Therefore, nowadays it has become unlikely albeit not impossible that entirely new species evolve.

Concluding, a species evolves by means of reproduction, random variations and natural selection. Thereby, natural selection affects the individuals, while the population as a whole is evolved. The three stated mechanisms of evolution are already featuring algorithmic characteristics, due to the presence of an iterated evolution loop, modification and selection operations. The individuals can be considered as candidate solutions to a given problem, although the suitable data structure can only be delivered by looking at the construction plan of the individuals themselves that is their genome.

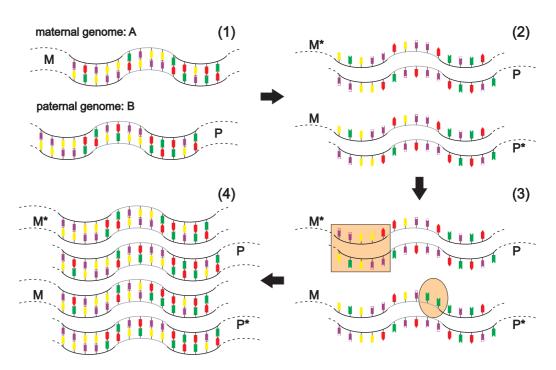

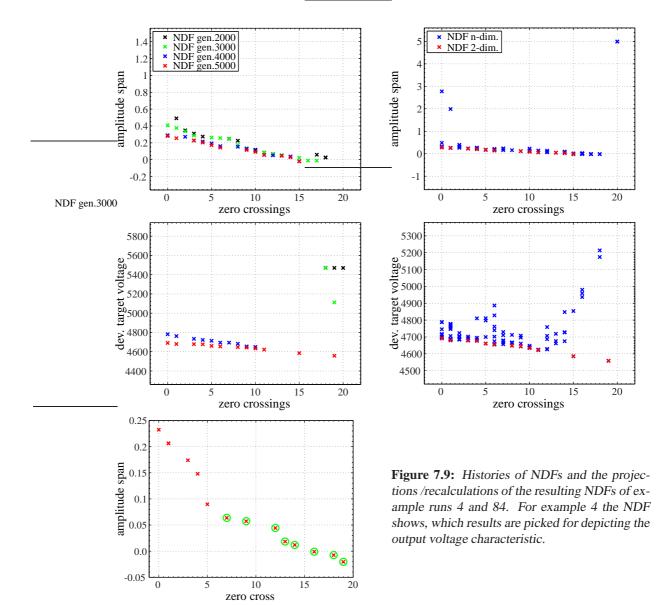

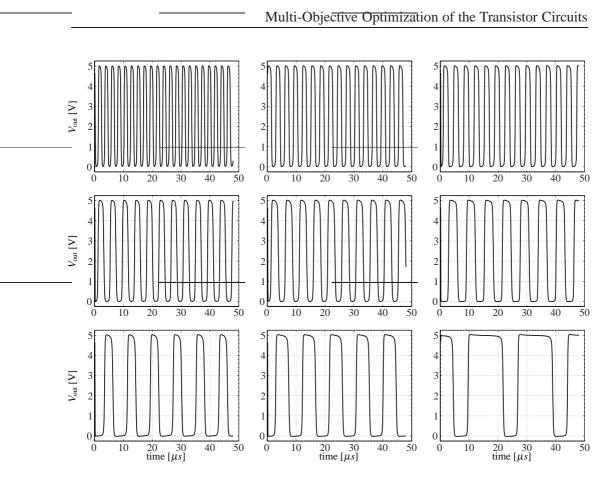

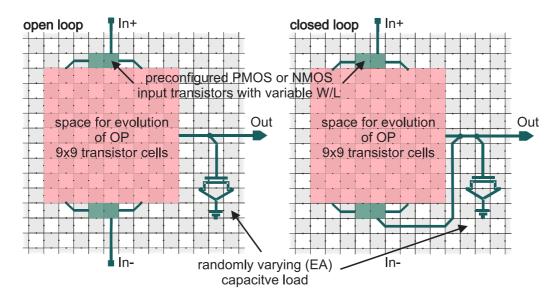

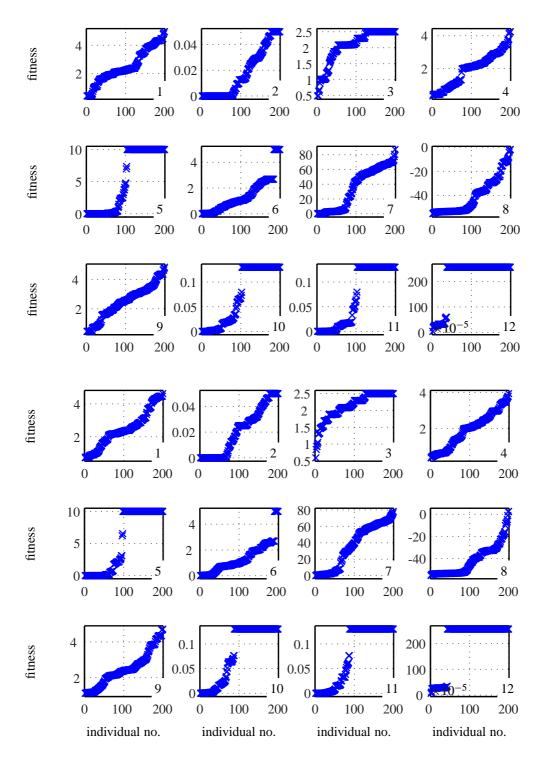

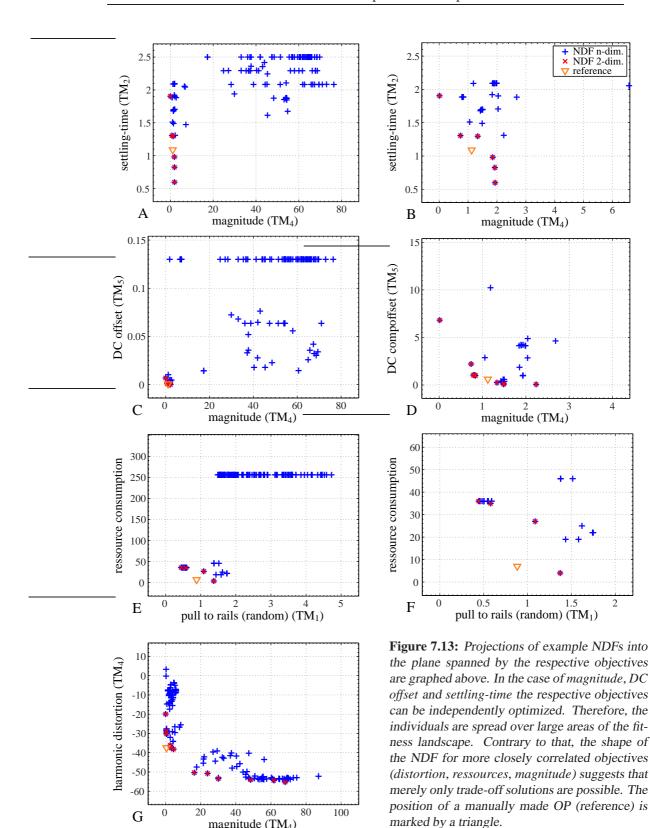

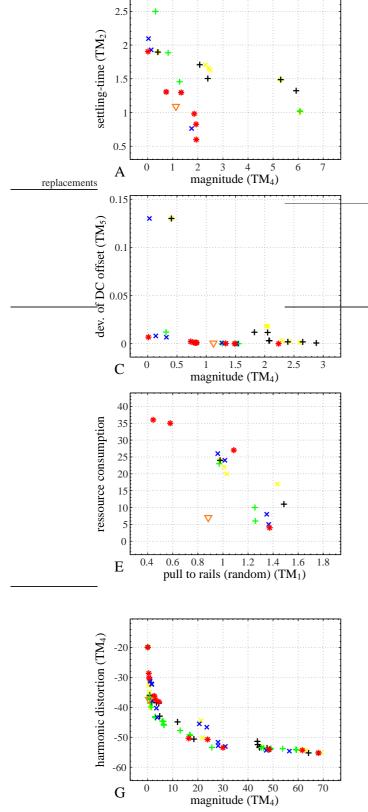

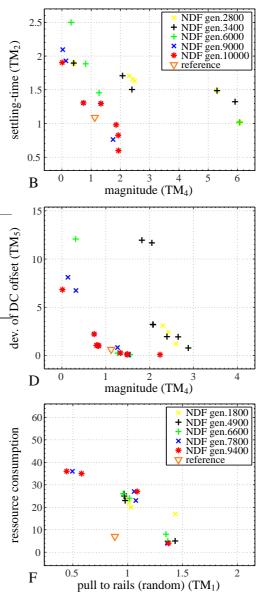

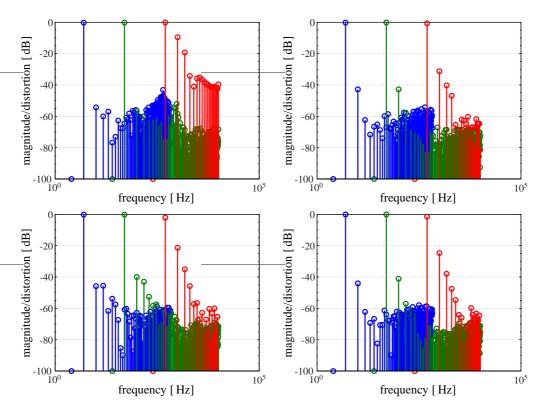

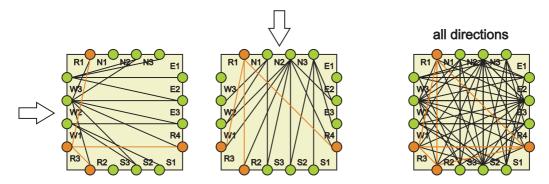

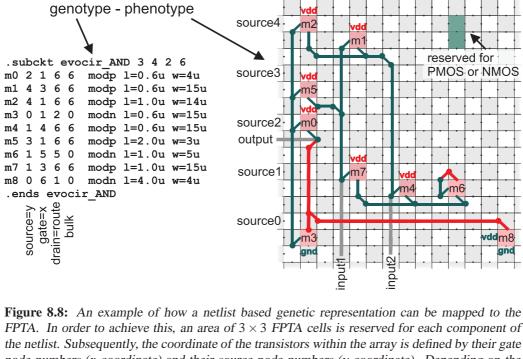

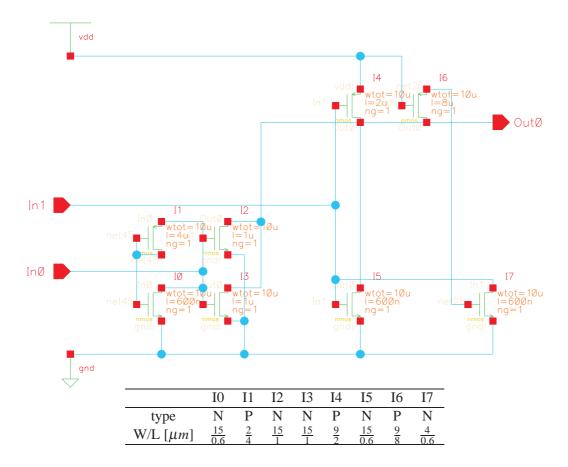

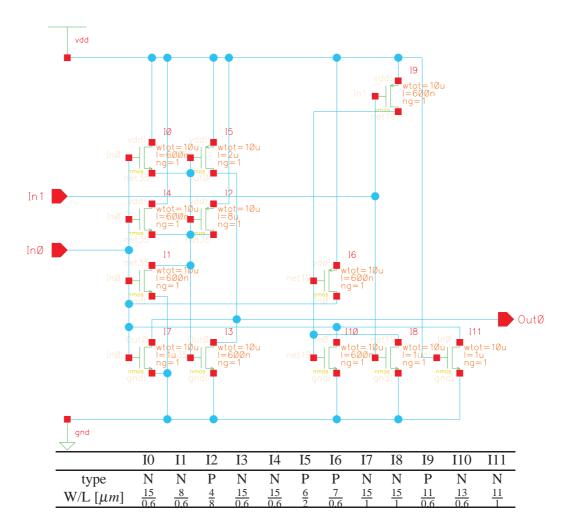

#### 2.1.2 The Genetic Level