KIRCHHOFF-INSTITUT FÜR PHYSIK

# RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

## DISSERTATION

submitted to the Combined Faculties for the Natural Sciences and for Mathematics

> of the Rupertus Carola University of Heidelberg, Germany

> > for the degree of Doctor of Natural Sciences

presented by Diplom-Physicist: Jörg Langeheine born in: Essen

Heidelberg, July 6, 2005

# Intrinsic Hardware Evolution on the Transistor Level

Gutachter: Prof. Dr. Karlheinz Meier Prof. Dr. Norbert Herrmann

# Zusammenfassung

#### Intrinsische Hardware-Evolution von Transistorschaltungen -

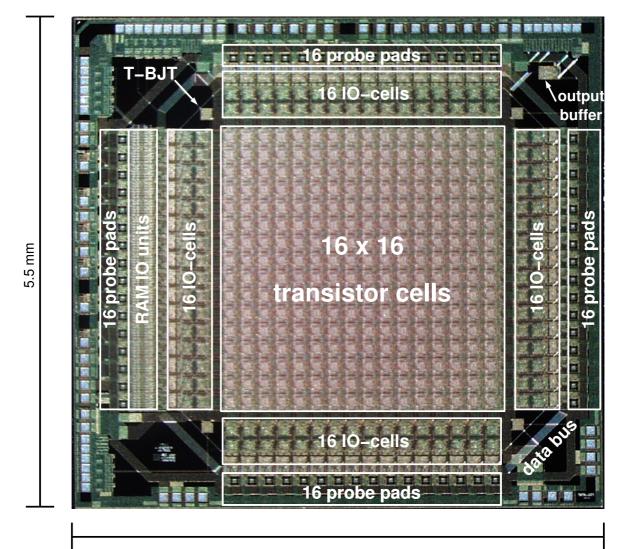

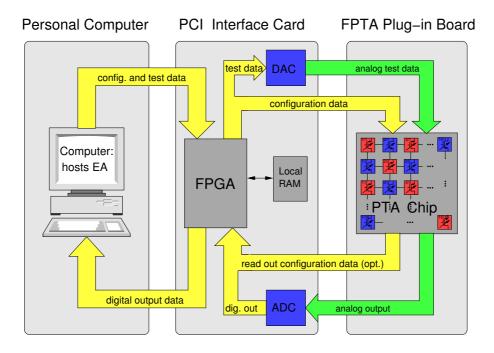

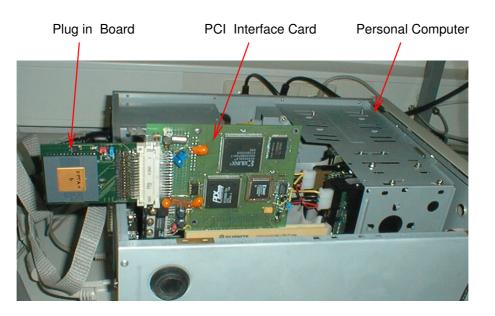

Diese Arbeit stellt einen neuartigen Ansatz zur automatisierten Synthese analoger Schaltungen vor. Evolutionäre Algorithmen werden dazu benutzt, analoge Schaltungen zu generieren, die auf einem eigens dafür entworfenem Mikrochip, der als analoges Substrat fungiert, getestet werden. Die Tatsache, dass die Güte der von dem evolutionären Algorithmus generierten Schaltungen durch einen Test auf dem oben genannten Mikrochip erfolgt, hat zwei Vorteile. Einerseits kann es den künstlichen Evolutionsprozeß beschleunigen, da der Test einer Schaltung oft schneller erfolgen kann als seine Simulation. Andererseits garantiert diese Vorgehensweise, dass die evolutionierten Schaltungen tatsächlich auf einem echten Chip funktionieren. Die oben beschriebene Methode wird durch ein Hardware-Evolutionssystem realisiert, das aus den folgenden Komponenten besteht: Einem IBM kompatiblen Computer, auf dem der evolutionäre Algorithmus abläuft, einer FPGA basierten gemischt analogen-digitalen Messkarte und dem analogen Substrat. Dieses ist durch ein Field Programmable Transistor Array (FPTA) realisiert, dessen programmierbare Transistorzellen fast beliebig miteinander verschaltet werden können. Die Abmessungen des Transistorkanals können in jeder Transistorzelle aus 75 verschiedenen Kombinationen ausgewählt werden. Der Mikrochip ist in einem 0.6µm CMOS Prozeß hergestellt worden und stellt vielfältige Möglichkeiten analoge Signale anzulegen und auszulesen zur Verfügung. Die Konfiguration des FPTA wird in SRAM Zellen gespeichert, die in die programmierbaren Transistorzellen eingebettet sind. In dieser Arbeit wird das Hardware-Evolutionssystem für die künstliche Evolution einer Vielzahl verschiedener Schaltungstypen verwendet. Die Zielschaltungen sind: Logische Gatter, Schaltkreise mit einer Gauß'schen Ausgangscharakteristik, D/A Wandler, Tief- und Hochpaßfilter, Tondiskriminatoren und Komparatoren. Die Ergebnisse der Experimente werden gründlich analysiert und mit anderen publizierten Arbeiten verglichen.

# Abstract

#### Intrinsic Hardware Evolution on the Transistor Level -

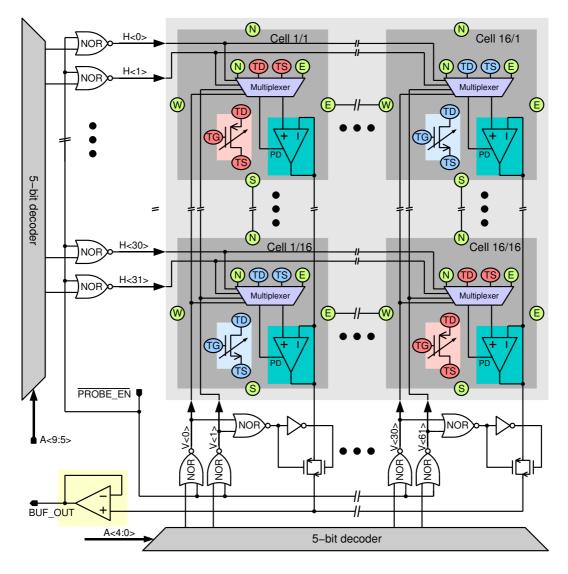

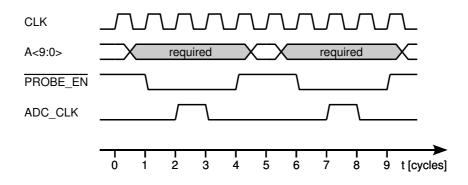

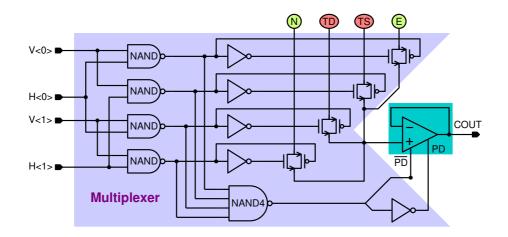

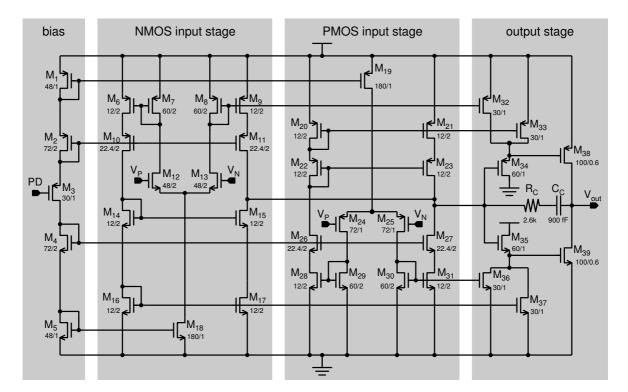

This thesis presents a novel approach to the automated synthesis of analog circuits. Evolutionary algorithms are used in conjunction with a fitness evaluation on a dedicated ASIC that serves as the analog substrate for the newly bred candidate solutions. The advantage of evaluating the candidate circuits directly in hardware is twofold. First, it may speed up the evolutionary algorithms, because hardware tests can usually be performed faster than simulations. Second, the evolved circuits are guaranteed to work on a real piece of silicon. The proposed approach is realized as a hardware evolution system consisting of an IBM compatible general purpose computer that hosts the evolutionary algorithm, an FPGA-based mixed signal test board, and the analog substrate. The latter one is designed as a Field Programmable Transistor Array (FPTA) whose programmable transistor cells can be almost freely connected. The transistor cells can be configured to adopt one out of 75 different channel geometries. The chip was produced in a 0.6 µm CMOS process and provides ample means for the input and output of analog signals. The configuration is stored in SRAM cells embedded in the programmable transistor cells. The hardware evolution system is used for numerous evolution experiments targeted at a wide variety of different circuit functionalities. These comprise logic gates, Gaussian function circuits, D/A converters, low- and highpass filters, tone discriminators, and comparators. The experimental results are thoroughly analyzed and discussed with respect to related work.

# Contents

| In | trodu | ction                                                           | 1  |

|----|-------|-----------------------------------------------------------------|----|

| Ι  | Fou   | ndations                                                        | 7  |

| 1  | CM    | OS Analog Circuit Design                                        | 9  |

|    | 1.1   | CMOS Transistors                                                | 10 |

|    |       | 1.1.1 Physical Definition                                       | 10 |

|    |       | 1.1.2 Simple Low Frequency Transistor Model                     | 11 |

|    |       | 1.1.3 Capacitances of CMOS Transistors                          | 14 |

|    | 1.2   | Linear Devices in CMOS Technology                               | 16 |

|    |       | 1.2.1 Resistors in CMOS technology                              | 16 |

|    |       | 1.2.2 Capacitors in CMOS                                        | 17 |

|    | 1.3   | CMOS Switches                                                   | 18 |

|    |       | 1.3.1 Switch Parasitics                                         | 18 |

|    |       | 1.3.2 Dynamic Operation: Sample and Hold Circuits               | 19 |

|    | 1.4   | Simulation and Verification                                     | 21 |

|    |       | 1.4.1 MOSFET Modeling                                           | 22 |

|    |       | 1.4.2 Analysis Types                                            | 22 |

|    |       | 1.4.3 Influence of Temperature and Device Mismatch              | 23 |

|    |       | 1.4.4 Comment on Circuit Simulations in Evolutionary Algorithms | 24 |

|    | 1.5   | Design Flow                                                     | 24 |

| 2  | Evol  | utionary Algorithms in a Nutshell                               | 27 |

|    | 2.1   | Biological Inspiration                                          | 28 |

|    |       | 2.1.1 Darwinian Evolution                                       | 28 |

|    |       | 2.1.2 Genetic Principles                                        | 29 |

|    |       | 2.1.3 Ontogenesis                                               | 31 |

|    | 2.2   | Overview of Evolutionary Algorithms                             | 31 |

|    |       | 2.2.1 Operation Principle                                       | 32 |

|    |       | 2.2.2 Components of an Evolutionary Algorithm                   | 32 |

|    |       | 2.2.3 Selection Schemes                                         | 36 |

|    | 2.3   | Dialects of Evolutionary Algorithms                             | 39 |

|    |       | 2.3.1 Genetic Algorithms                                        | 39 |

|    |       | 2.3.2 Evolution Strategies                                      | 40 |

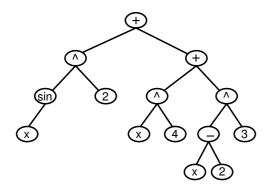

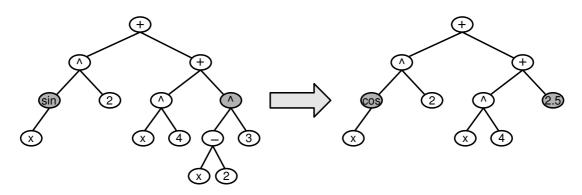

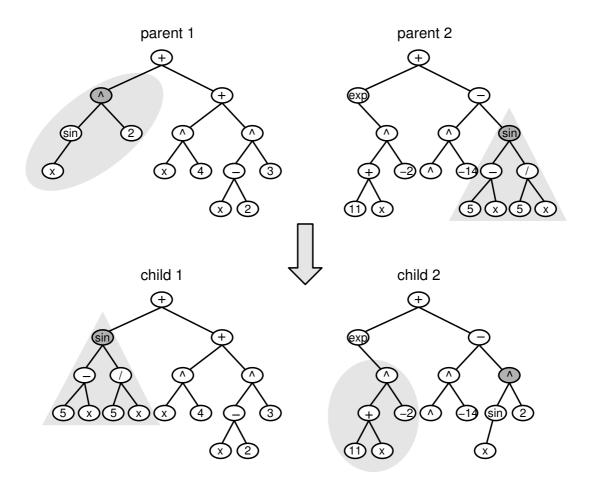

|    |       | 2.3.3 Genetic Programming                                       | 41 |

|    |       | 2.3.4 A Note on EA Parameters                                   | 43 |

|    | 2.4   | Evolutionary Algorithms as Global Optimizers                    | 45 |

|   |      | 2.4.1            | Global Optimization                                                 |  |

|---|------|------------------|---------------------------------------------------------------------|--|

|   |      | 2.4.2            | Model-Free Heuristics    46                                         |  |

|   |      | 2.4.3            | No Free Lunch Theorem                                               |  |

|   |      | 2.4.4            | Implications of the Stochastic Nature of Evolutionary Algorithms 47 |  |

|   | 2.5  | Extensio         | ons and Refinements                                                 |  |

|   |      | 2.5.1            | Distributed Populations                                             |  |

|   |      | 2.5.2            | Multi Objective Evolution                                           |  |

|   |      |                  |                                                                     |  |

|   |      |                  |                                                                     |  |

| Π | Evo  | olution <b>S</b> | System 49                                                           |  |

| 3 | Impl | ementat          | ion of the FPTA 51                                                  |  |

|   | 3.1  | Rational         | e                                                                   |  |

|   |      | 3.1.1            | The Very Idea of the Programmable Transistor Array                  |  |

|   |      |                  | Target Specifications                                               |  |

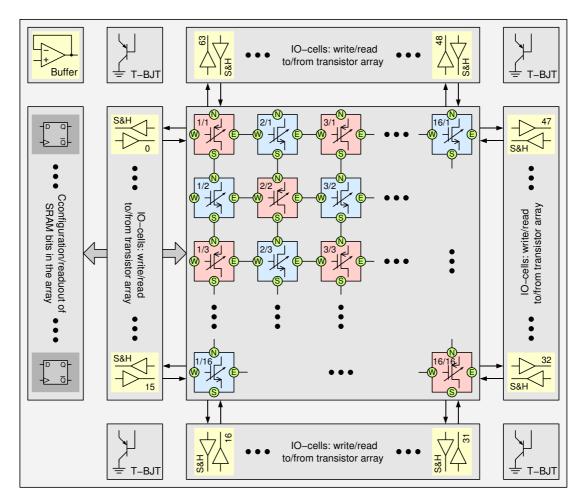

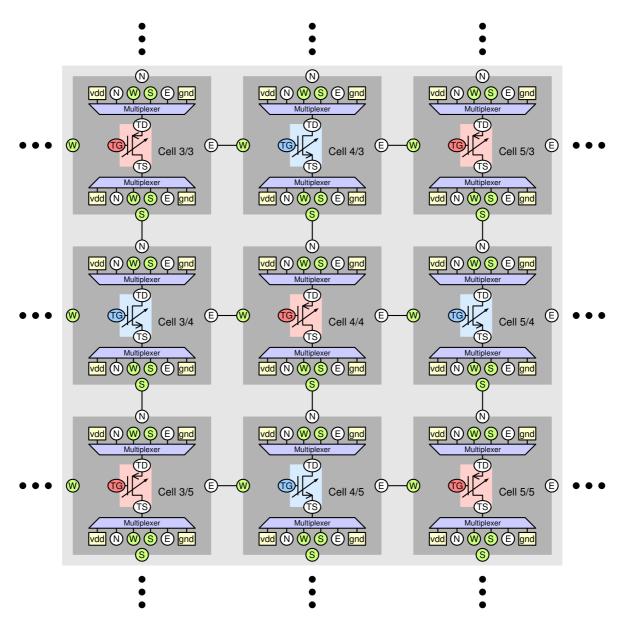

|   | 3.2  |                  | ture of the FPTA                                                    |  |

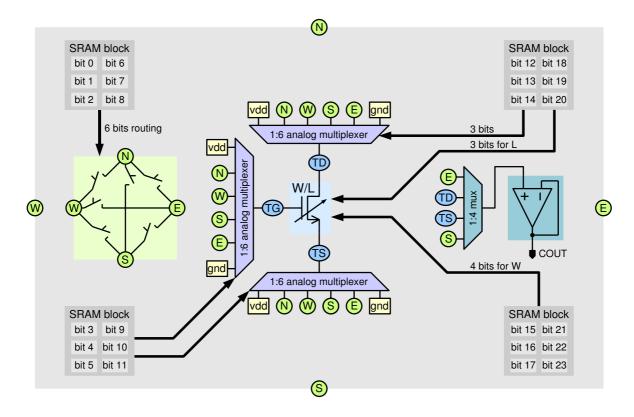

|   | 3.3  |                  | mable Transistor Cell Array                                         |  |

|   | 0.0  |                  | Transistor Cell Architecture                                        |  |

|   |      |                  | Routing Concept                                                     |  |

|   |      |                  | Programmable Transistor                                             |  |

|   |      |                  | Switch Dimensions                                                   |  |

|   |      |                  | Parasitic Devices                                                   |  |

|   |      |                  | Layout of the Programmable Transistor Cell       67                 |  |

|   | 3.4  |                  | Tor Configuration Storage   70                                      |  |

|   | 5.4  |                  |                                                                     |  |

|   |      |                  |                                                                     |  |

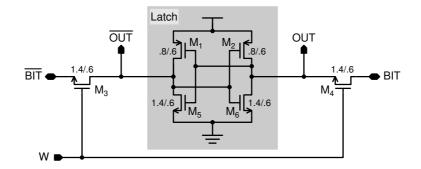

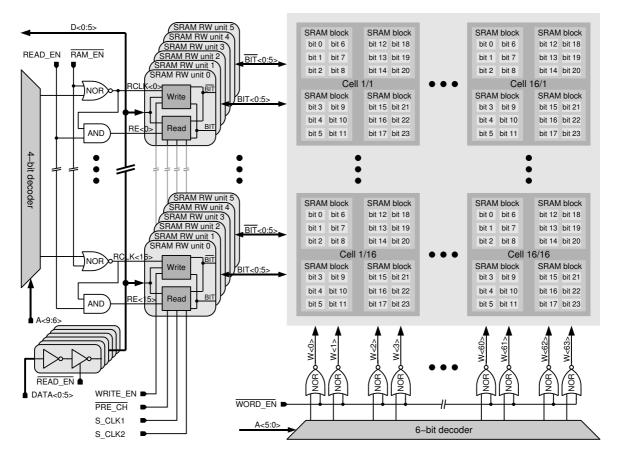

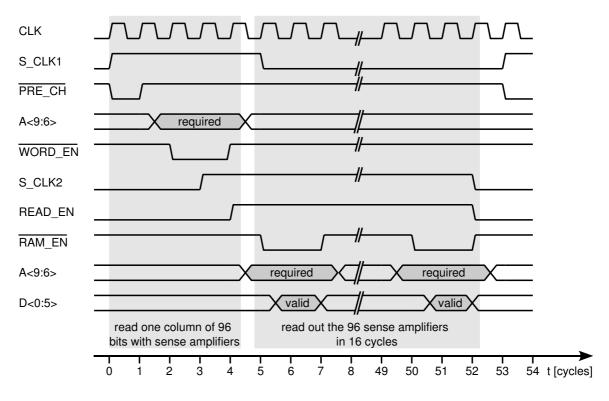

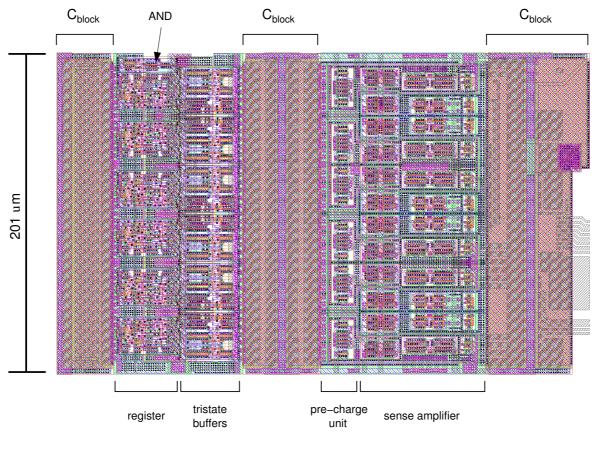

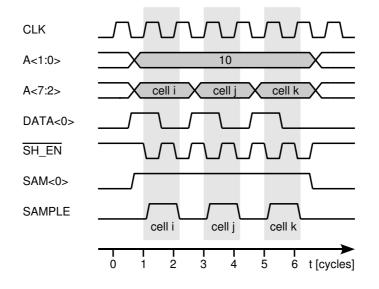

|   |      |                  | SRAM Architecture                                                   |  |

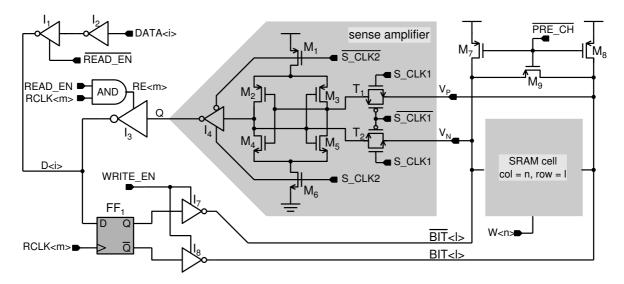

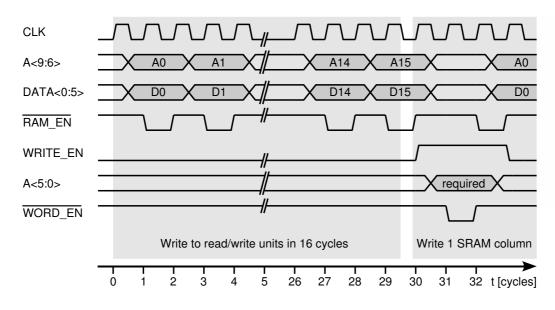

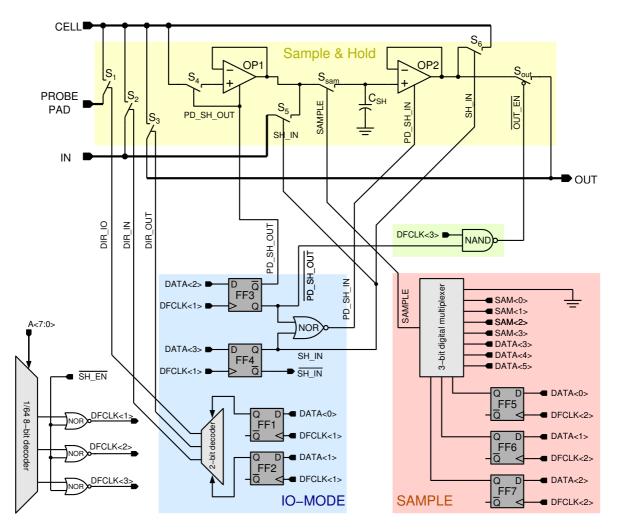

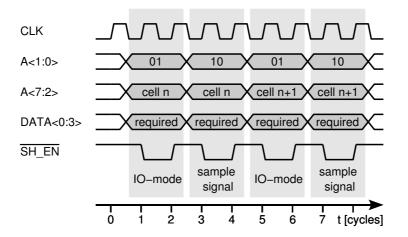

|   |      |                  | SRAM: IO-Circuitry                                                  |  |

|   | 2.5  |                  | SRAM: Concluding Remarks                                            |  |

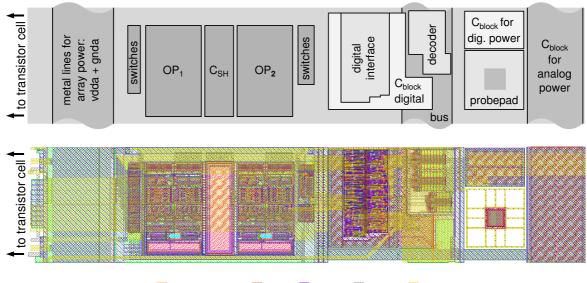

|   | 3.5  |                  | 78                                                                  |  |

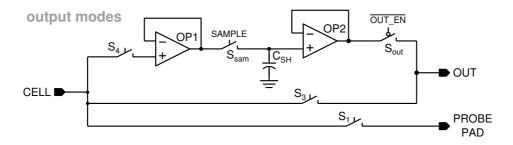

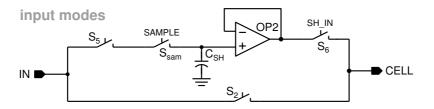

|   |      |                  | Functionality of the IO-cells                                       |  |

|   |      |                  | Architecture of the IO-Cells                                        |  |

|   |      | 3.5.3            | Configuration of the IO-cells                                       |  |

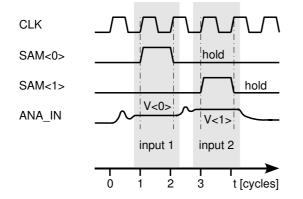

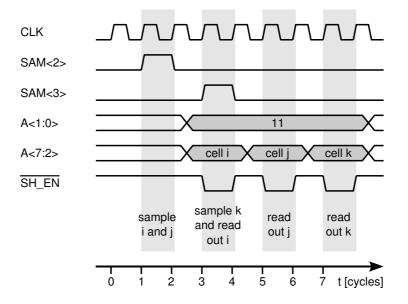

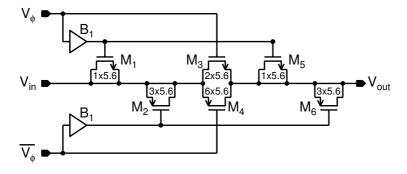

|   |      |                  | Sample and Hold Units: The Analog Perspective                       |  |

|   |      |                  | Layout of an IO-Cell                                                |  |

|   | 3.6  |                  | ell Signal Probing                                                  |  |

|   |      |                  | Inner-Cell Probing Concept    88                                    |  |

|   |      | 3.6.2            | Implementation of the Inner-cell Probing         88                 |  |

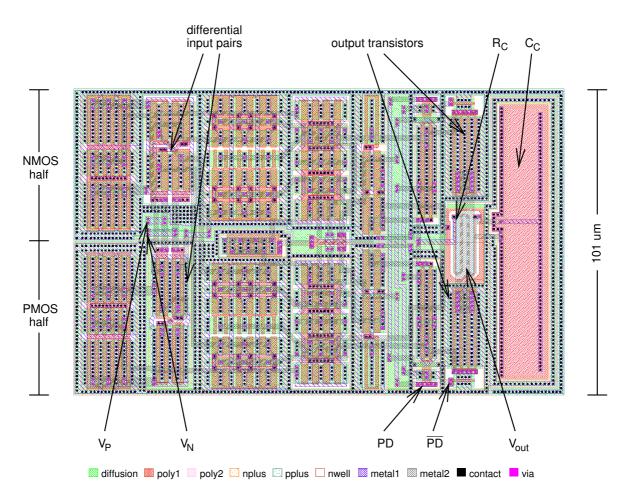

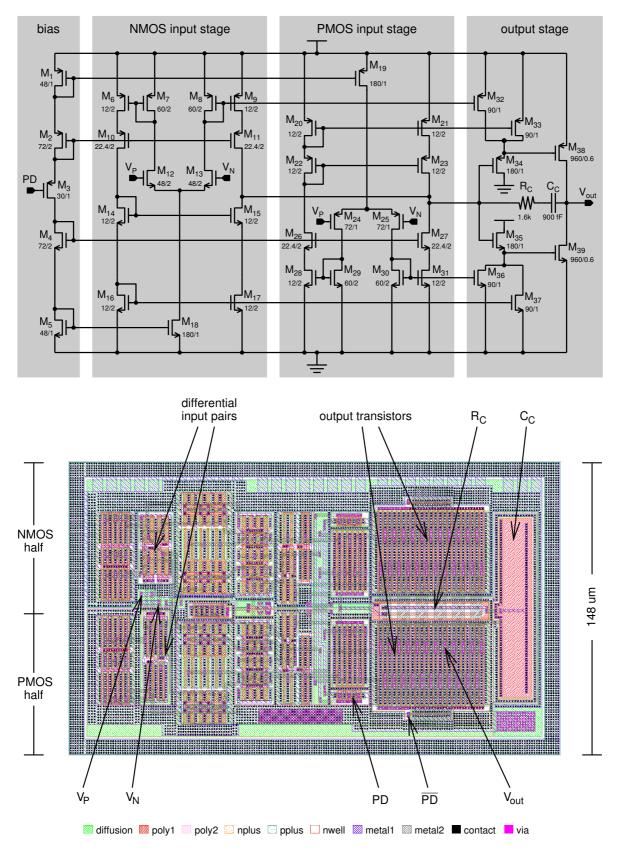

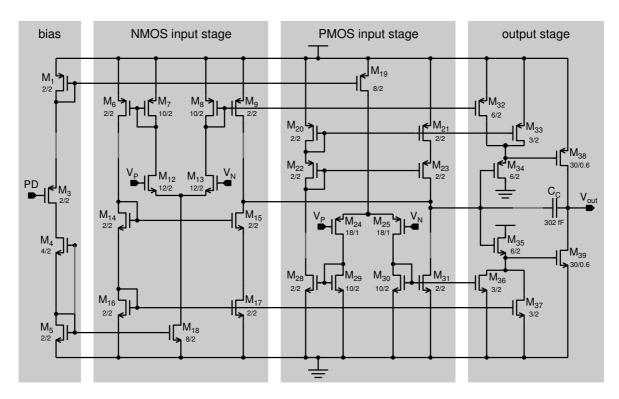

|   | 3.7  | -                | of Rail-to-Rail Operational Amplifiers                              |  |

|   |      |                  | IO-cell Buffer                                                      |  |

|   |      | 3.7.2            | Global Output Buffer                                                |  |

|   |      | 3.7.3            | Cell Buffer                                                         |  |

|   |      | 3.7.4            | Summary of Simulated Performance                                    |  |

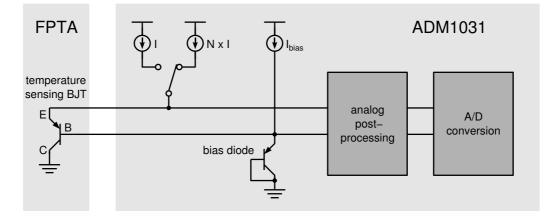

|   | 3.8  | Measure          | ement of Die Temperature                                            |  |

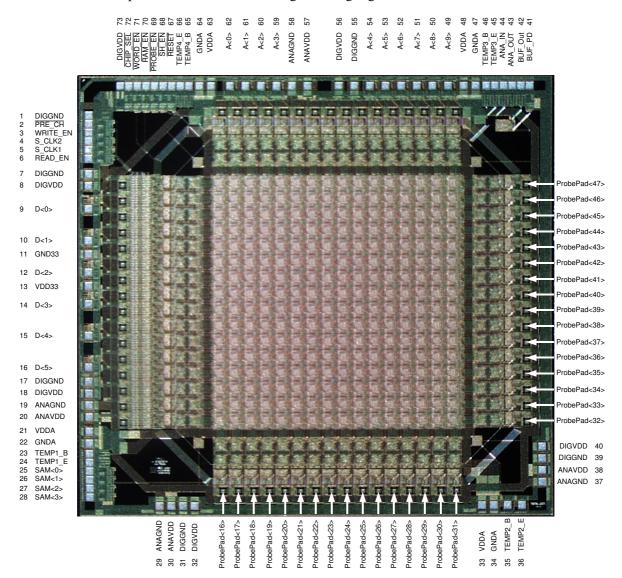

|   | 3.9  | Layout           | of the Complete Chip                                                |  |

|   | 3.10 | Yield A          | nalysis                                                             |  |

|   | 3.11 | Compar           | ison of the Heidelberg and JPL FPTA Chips                           |  |

|   |      |                  |                                                                     |  |

| 4 | Evol | ution System 105                                   |

|---|------|----------------------------------------------------|

|   | 4.1  | Overview of the Evolution System                   |

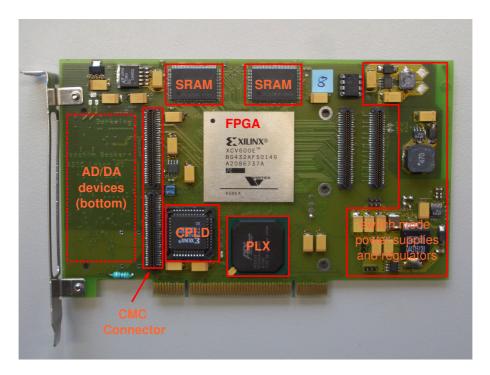

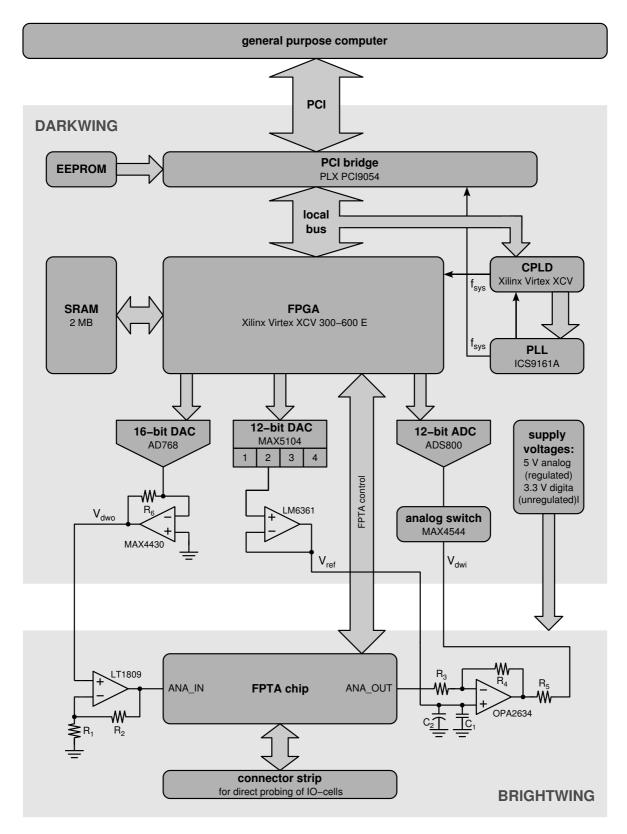

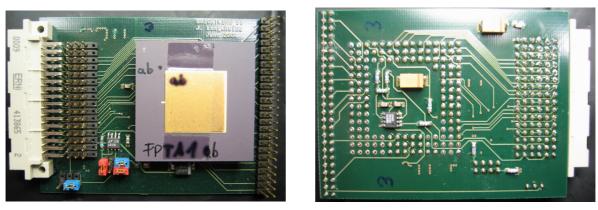

|   | 4.2  | Mixed-Signal Test Environment                      |

|   |      | 4.2.1 Electrical Test System: Background           |

|   |      | 4.2.2 Test Environment: Digital Part               |

|   |      | 4.2.3 Analog Signal Path                           |

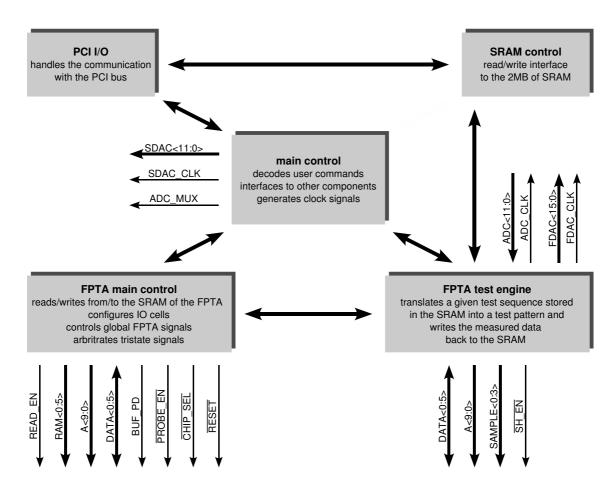

|   | 4.3  | Hardware Control Software                          |

|   |      | 4.3.1 Overview                                     |

|   |      | 4.3.2 Analog Test Engine                           |

|   | 4.4  | DarkGAQT Software Package                          |

|   |      | 4.4.1 Overview                                     |

|   |      | 4.4.2 Multithreading Architecture                  |

|   |      | 4.4.3 Implementation of the Evolutionary Algorithm |

|   |      |                                                    |

|   |      |                                                    |

### **III** Experiments and Results

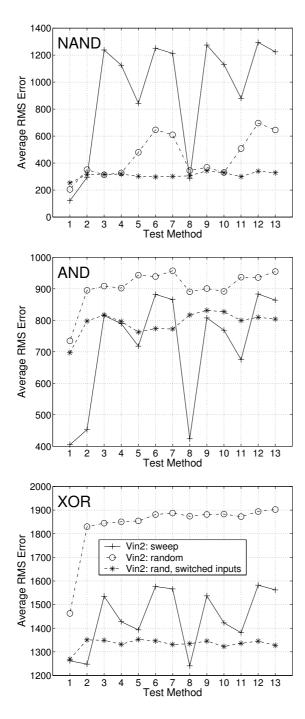

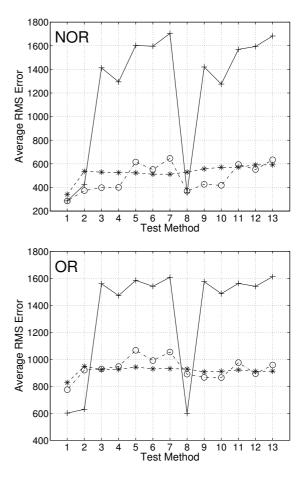

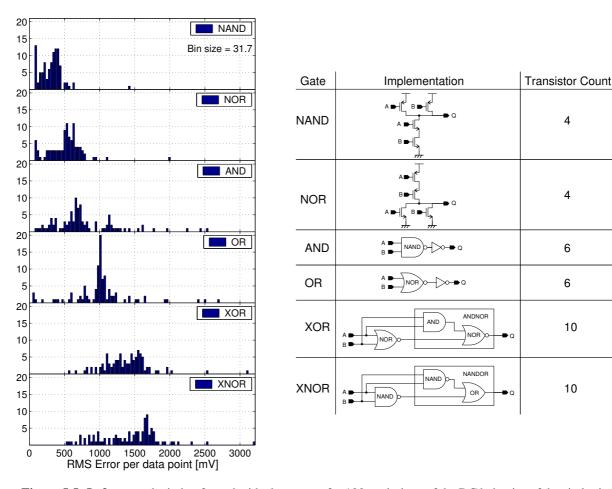

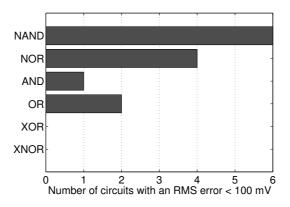

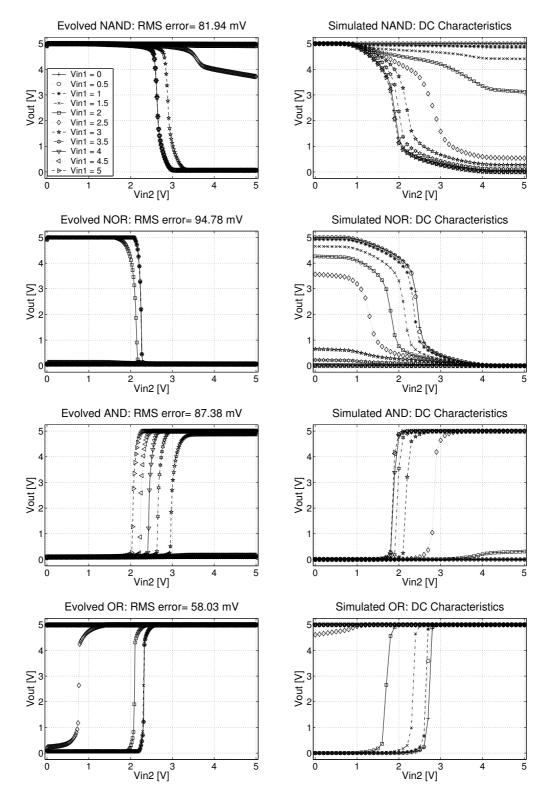

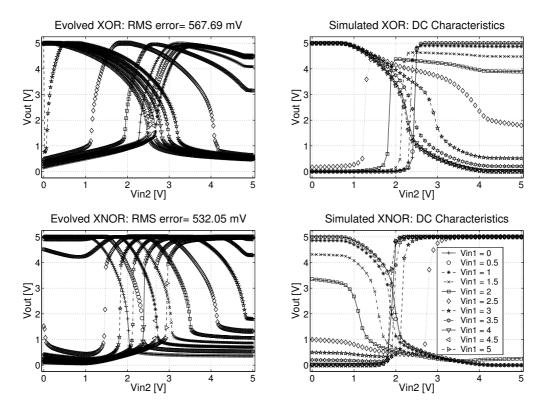

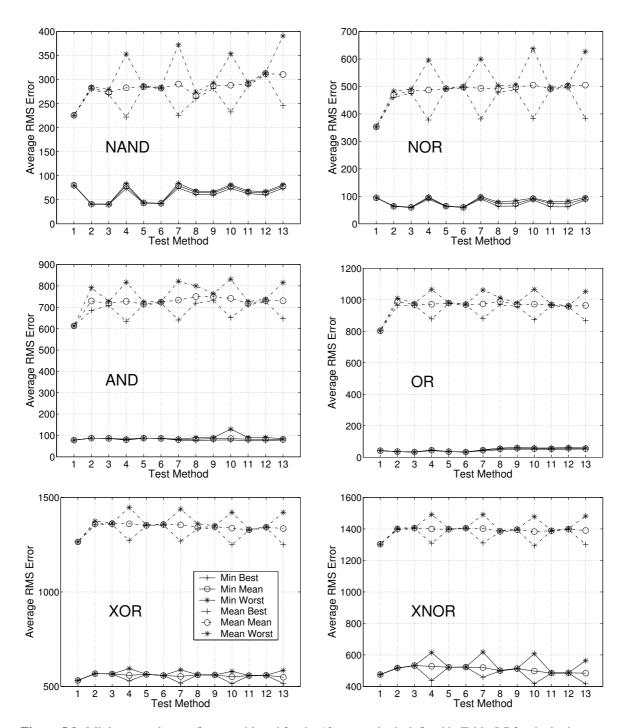

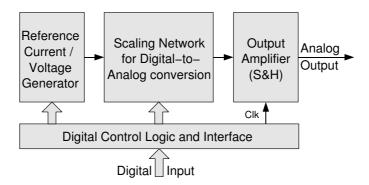

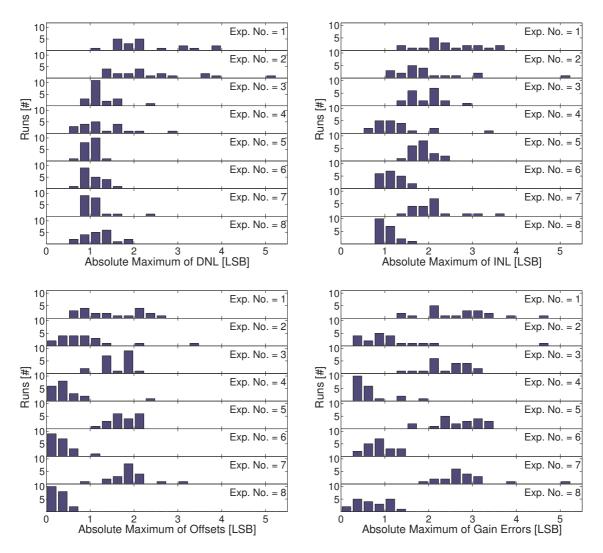

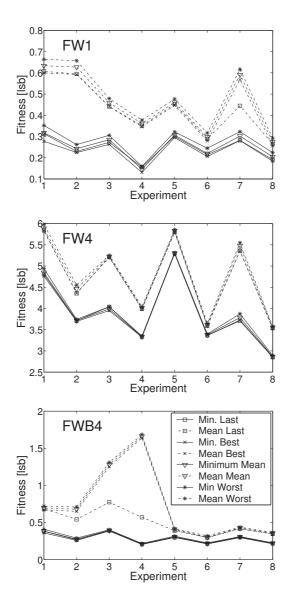

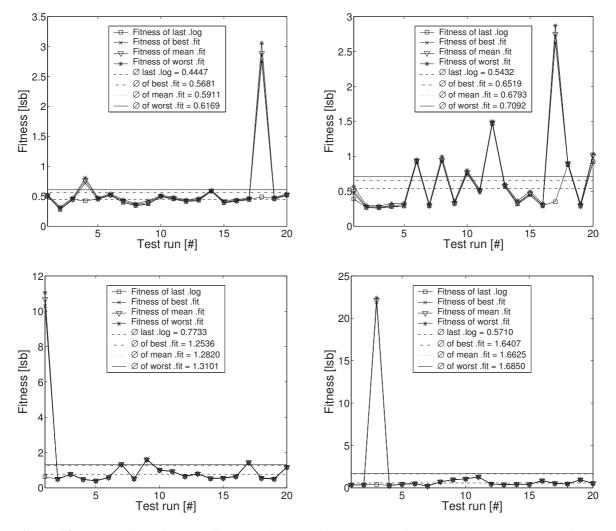

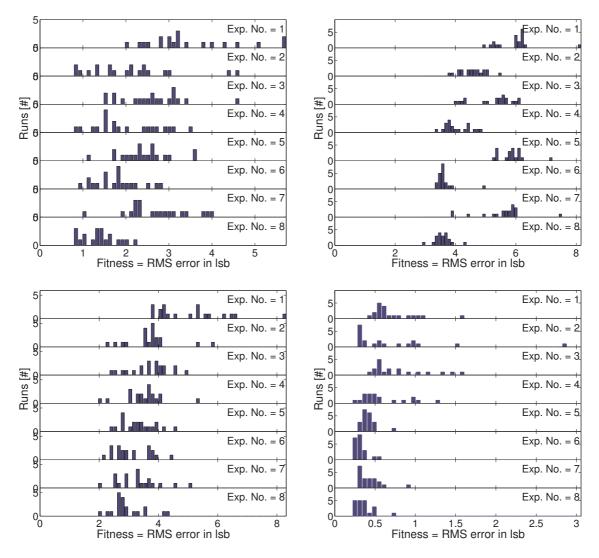

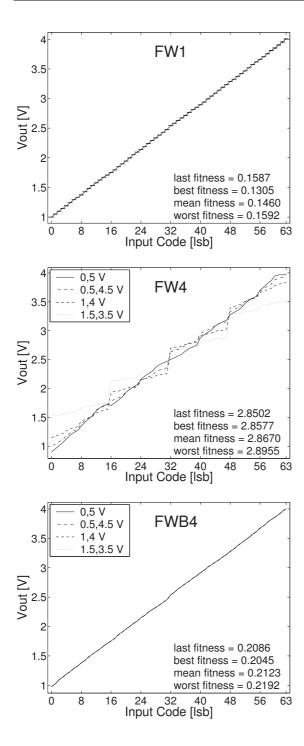

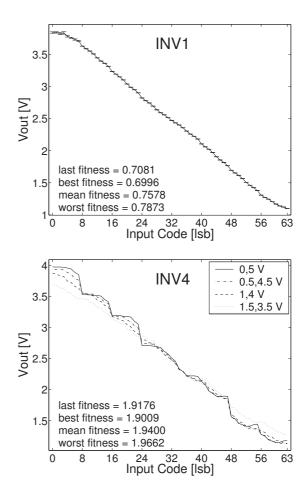

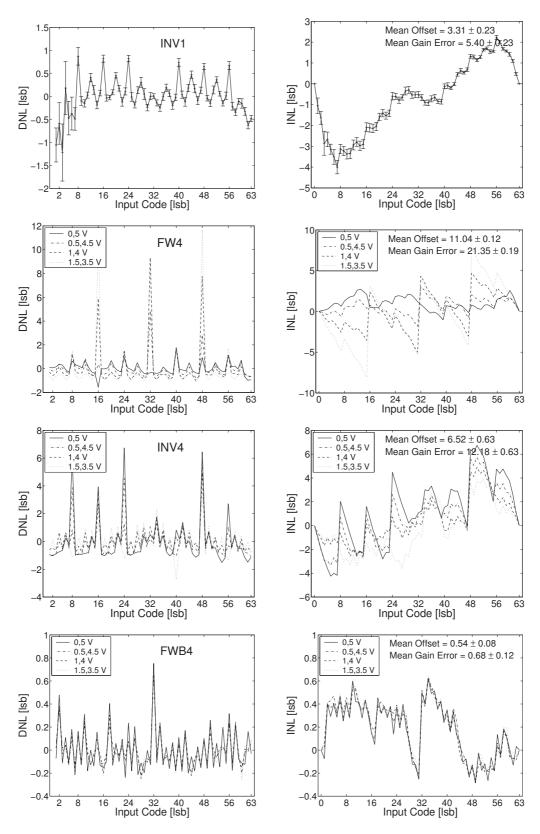

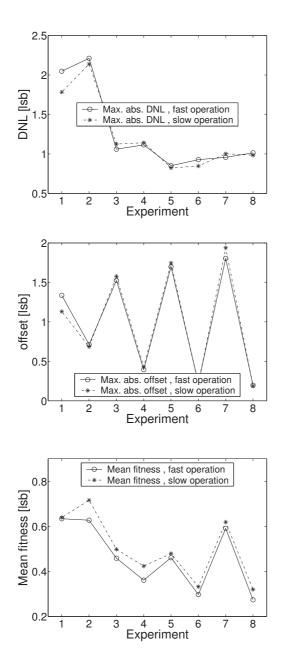

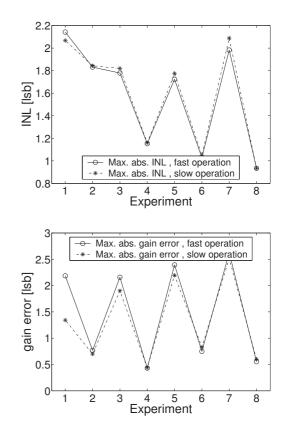

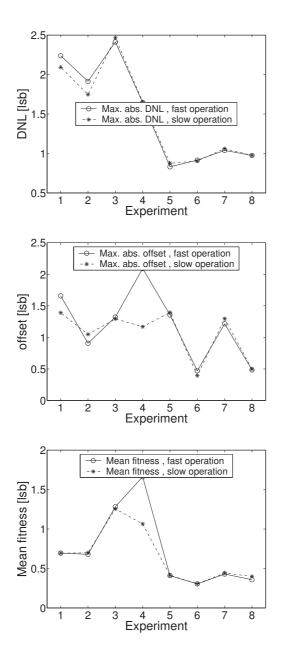

**Evolution of Quasi-DC Solutions** 133 5 5.1 133 5.1.1 133 5.1.2 134 5.2 136 5.2.1 Problem Definition 136 5.2.2 Geometrical Setup 139 5.2.3 Overview of the Experiments 139 5.2.4 141 5.2.5 Verification Tests 141 5.3 Results: Evolution of Logic Gates I 141 5.4 144 5.4.1144 5.4.2 146 5.4.3 Performance Comparison for Different Tests 148 5.5 150 5.5.1 150 5.5.2 Output Characteristic of the Best Evolved Circuits 150 5.5.3 Verification Measurements 153 153 5.6 6 **Evolution of Digital-to-analog Converters** 155 156 6.1 6.1.1 Problem Definition 156 Overview of the Experiments 6.1.2 157 6.1.3 Fitness Function 158 6.1.4 Test Patterns 159 6.1.5 GA Parameters 160 6.2 160 6.2.1 Root Mean Square Error 161 Nonlinearity, Offset and Gain Error 6.2.2 161

131

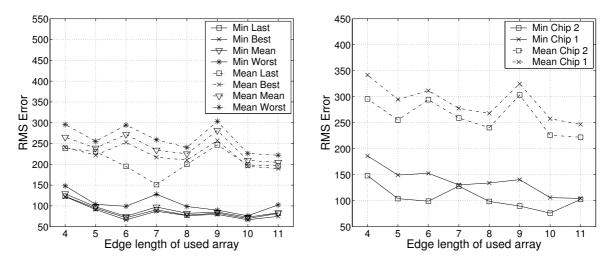

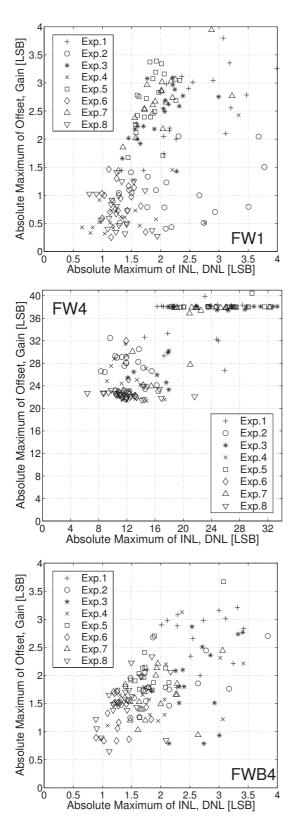

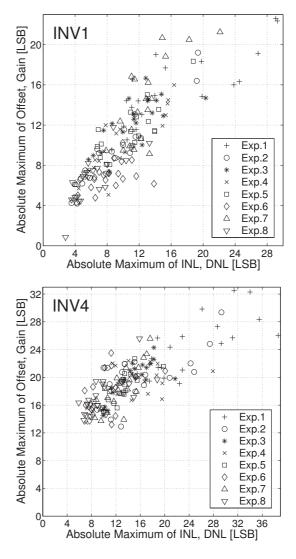

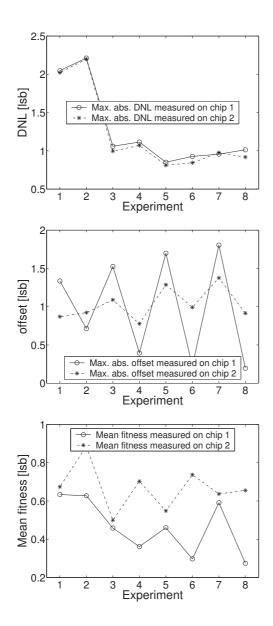

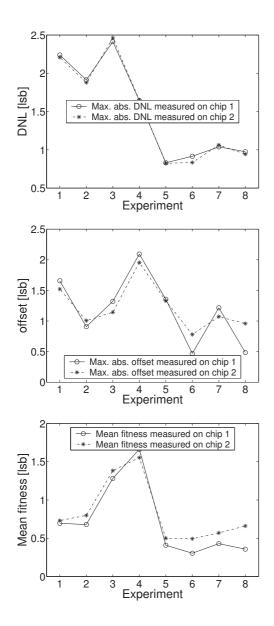

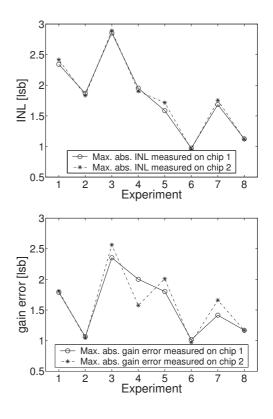

|   | 6.3   | Compar    | ison of the Five Different Series of Experiments                | . 164 |

|---|-------|-----------|-----------------------------------------------------------------|-------|

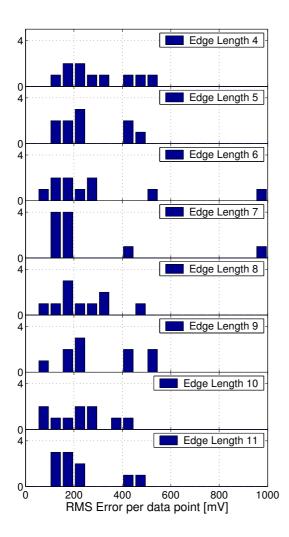

|   |       | 6.3.1     | Root Mean Square Error                                          | . 164 |

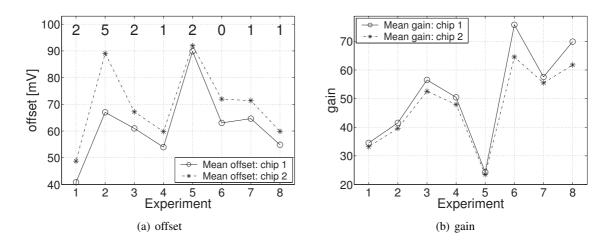

|   |       | 6.3.2     | Offset, Gain and Nonlinearities                                 | . 167 |

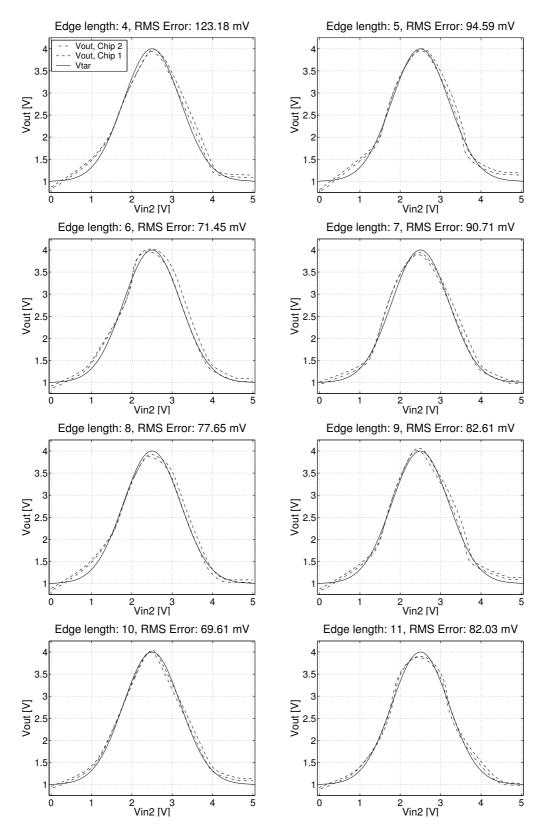

|   |       | 6.3.3     | Best per Series Results                                         | . 170 |

|   | 6.4   | General   | izability of the Results of Series FW1 and FWB4                 | . 173 |

|   |       | 6.4.1     | Verification at a Second Time Scale                             | . 173 |

|   |       | 6.4.2     | Performance on a Second Chip                                    | . 174 |

|   | 6.5   | Discussi  | ion                                                             | . 177 |

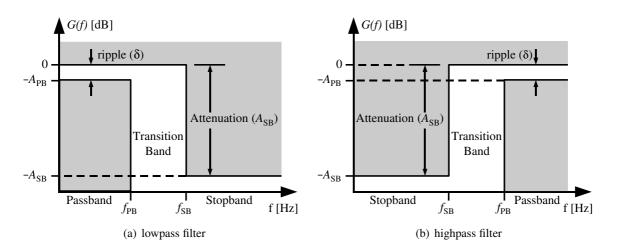

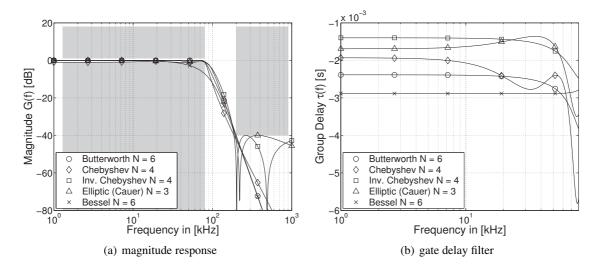

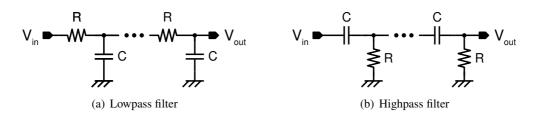

| 7 | Evo   | lution of | Filters                                                         | 181   |

|   | 7.1   |           | tion                                                            |       |

|   | / • 1 |           | Conventional Design of Analog VLSI Filters in a Nutshell        |       |

|   |       |           | Related Work                                                    |       |

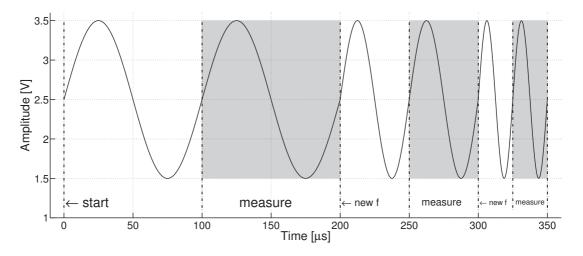

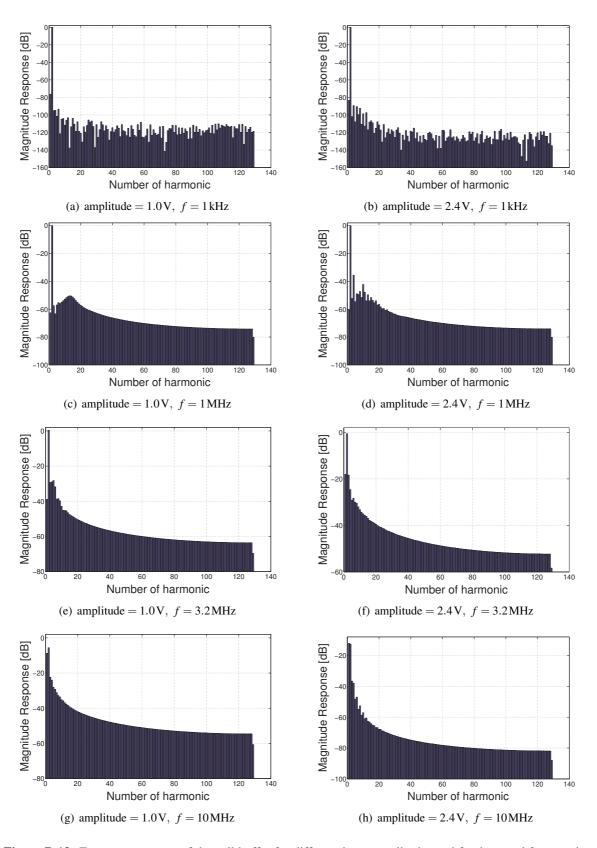

|   | 7.2   |           | ion of the Magnitude Response                                   |       |

|   | 1.2   |           | M1: Transfer Function from the Step Response                    |       |

|   |       |           | M2: Magnitude Response from the Mean Signal Power               |       |

|   |       |           | M3: Magnitude Response from Fourier Analyzed Sinusoidal Stimuli |       |

|   |       |           | Noise Floor                                                     |       |

|   |       |           | List of All Test Modes                                          |       |

|   |       |           | Randomization for Time-Dependent Experiments                    |       |

|   | 7.3   |           | g Low Pass Filters                                              |       |

|   | 1.5   |           | Experimental Setup                                              |       |

|   |       |           |                                                                 |       |

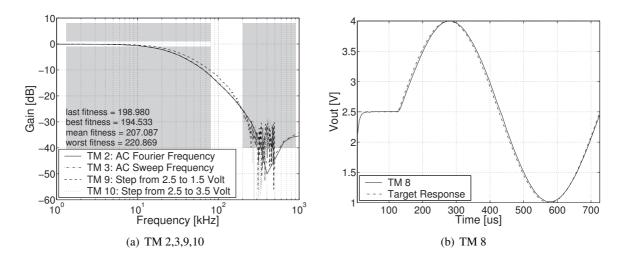

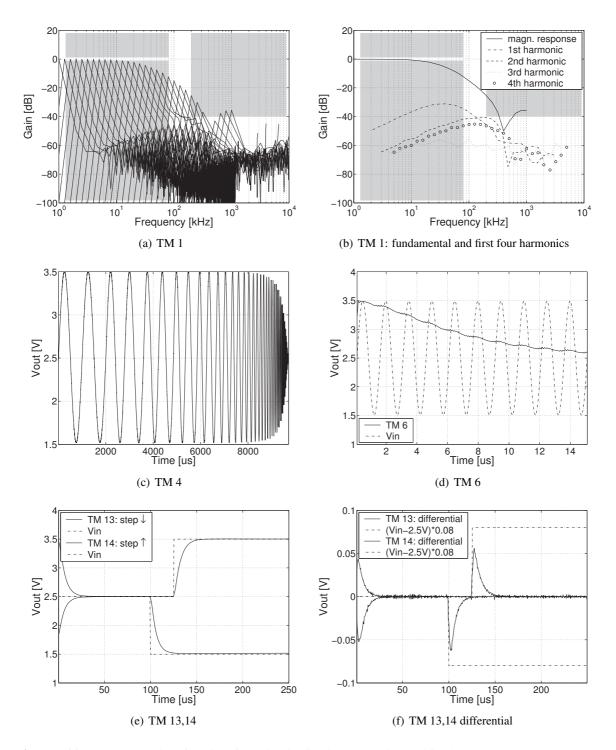

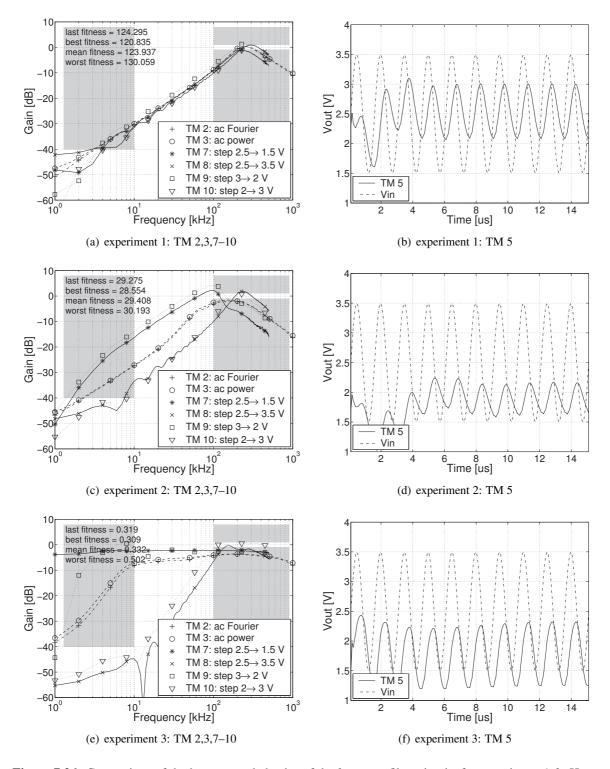

|   |       |           | Illustration and Discussion of the Different Test Modes         |       |

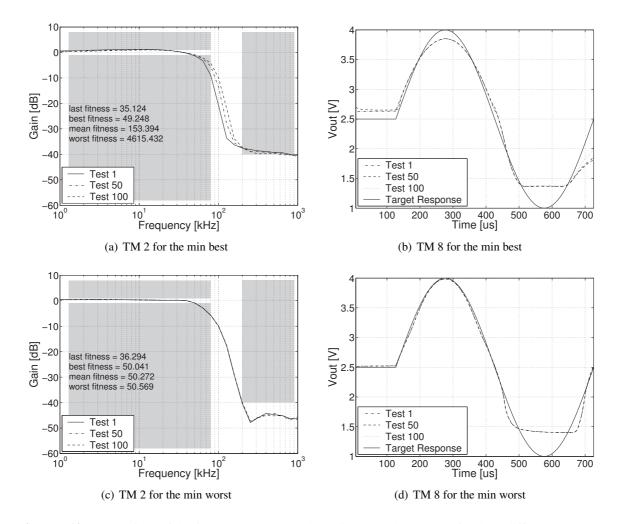

|   |       |           | Reproducibility                                                 |       |

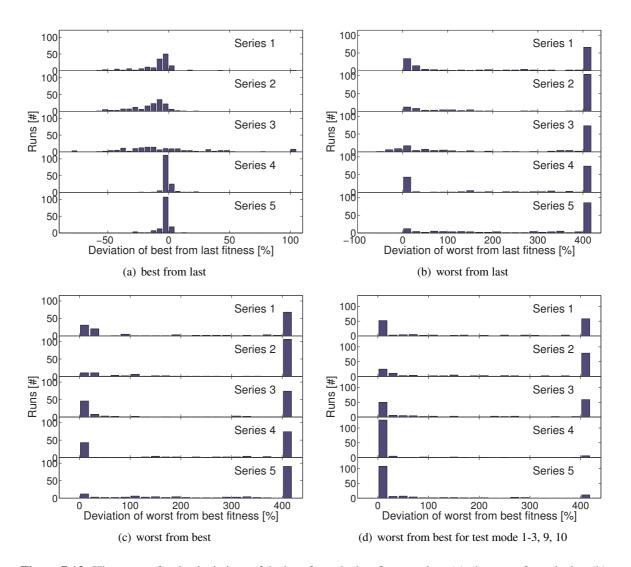

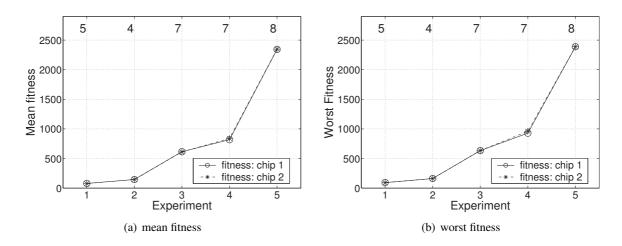

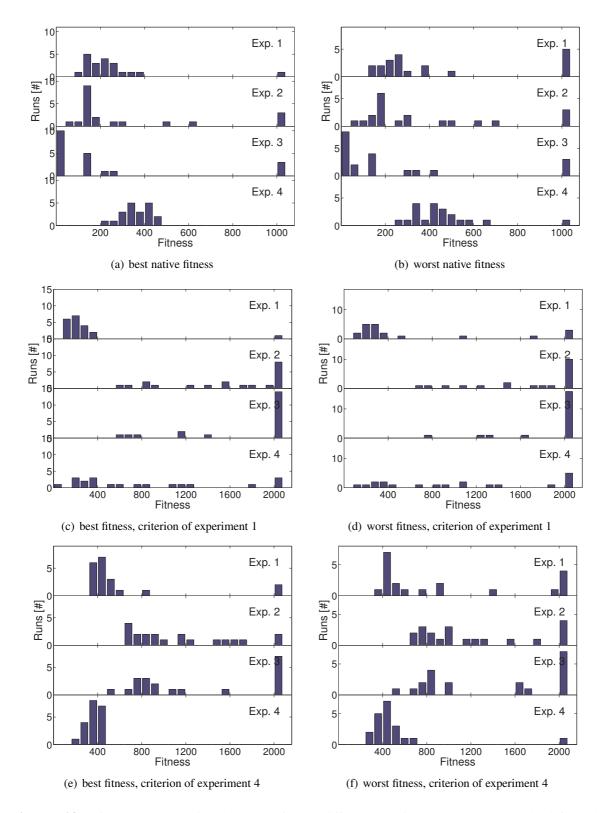

|   |       |           | Comparison of Different Experiments                             |       |

|   |       |           | Comparison of Different Series of Experiments                   |       |

|   |       |           | Migration to a Second Chip                                      |       |

|   | 7.4   |           | g LPFs on Different Frequency Scales                            |       |

|   |       |           | Experimental Setup                                              |       |

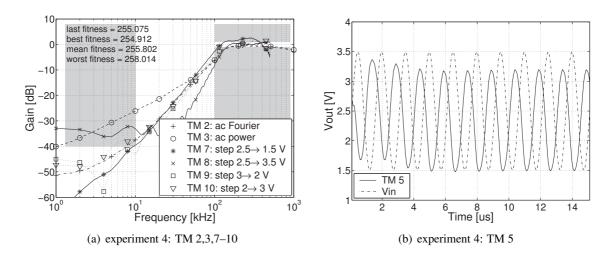

|   |       |           | Output Behavior for the Best-Of-Experiment Circuits             |       |

|   |       |           | Statistical Analysis                                            |       |

|   |       |           | Migration to a Second Chip                                      |       |

|   | 7.5   |           | ss Filter                                                       |       |

|   |       |           | Experimental Setup                                              |       |

|   |       | 7.5.2     | Output Behavior for the Best-Of-Experiment Circuits             | . 235 |

|   |       |           | Statistical Analysis                                            |       |

|   |       | 7.5.4     | Reproducibility                                                 | . 239 |

|   |       | 7.5.5     | Migration to a Second Chip                                      | . 240 |

|   | 7.6   |           | ry and Discussion                                               |       |

|   |       | 7.6.1     | Lessons Learned                                                 | . 241 |

|   |       | 7.6.2     | Comparison with Related Work                                    | . 243 |

| 8 | Evo   | lution Us | ing Human Made Building Blocks                                  | 245   |

|   | 8.1   |           | ology                                                           |       |

|   |       |           | Rationale                                                       |       |

|   |       |           | Related Work                                                    |       |

|   |       |           | Building Block Concept                                          |       |

|   |       |           |                                                                 |       |

|   |       |           | <b>1 1 1 1 1 1 1 1 1 1</b>                                      | =.5   |

| imental Setup for Case Studies I and II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

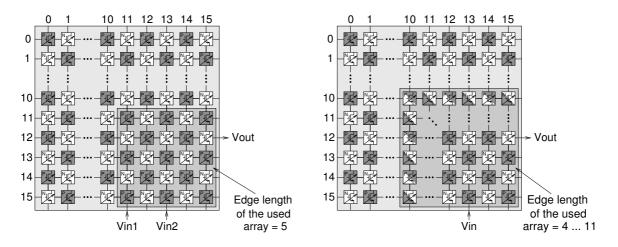

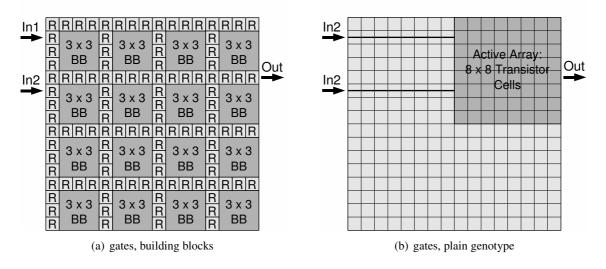

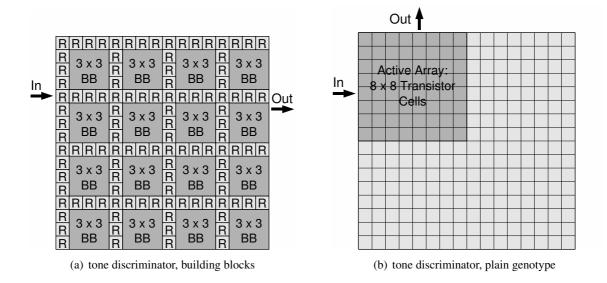

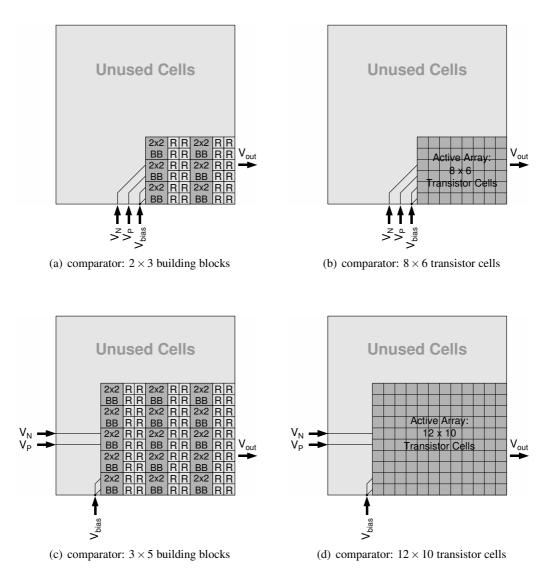

| Geometrical Setup for Case Studies I,II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                    |

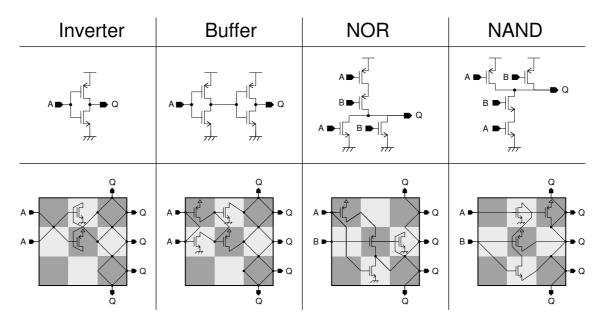

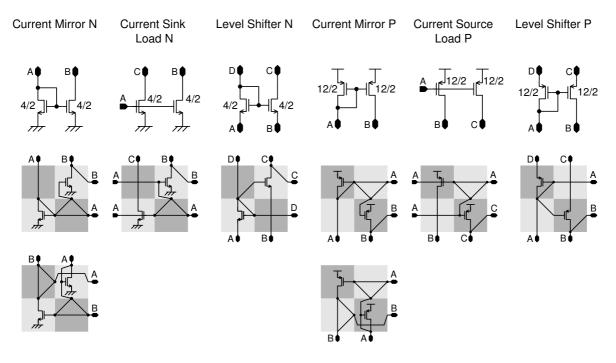

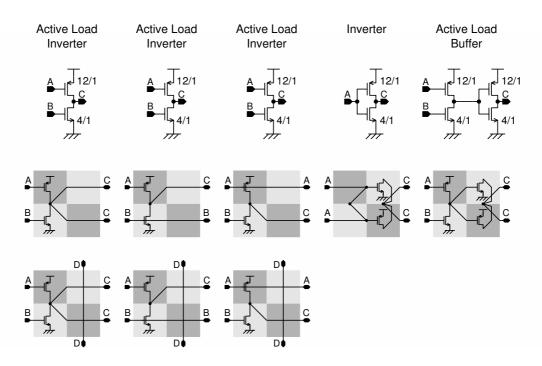

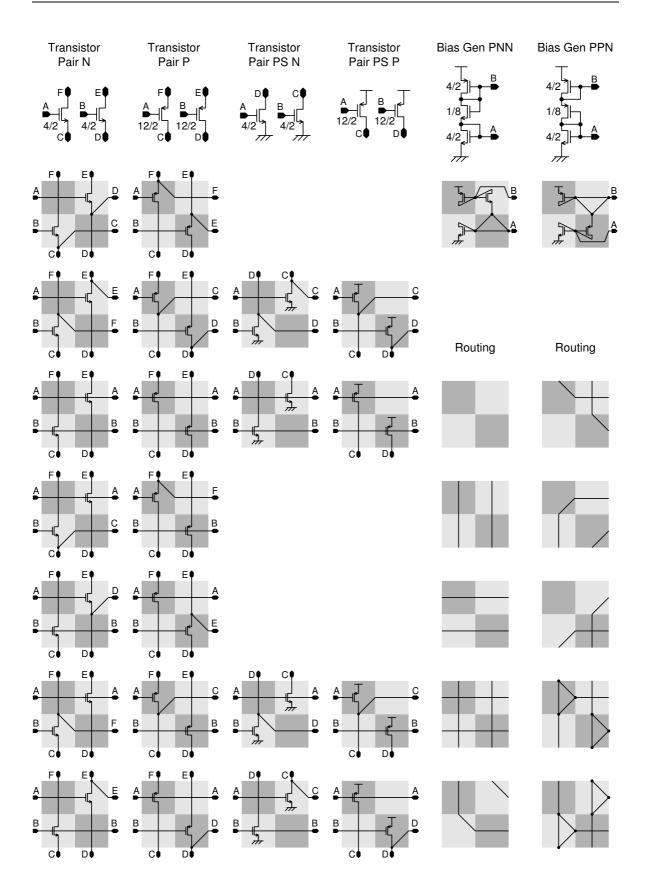

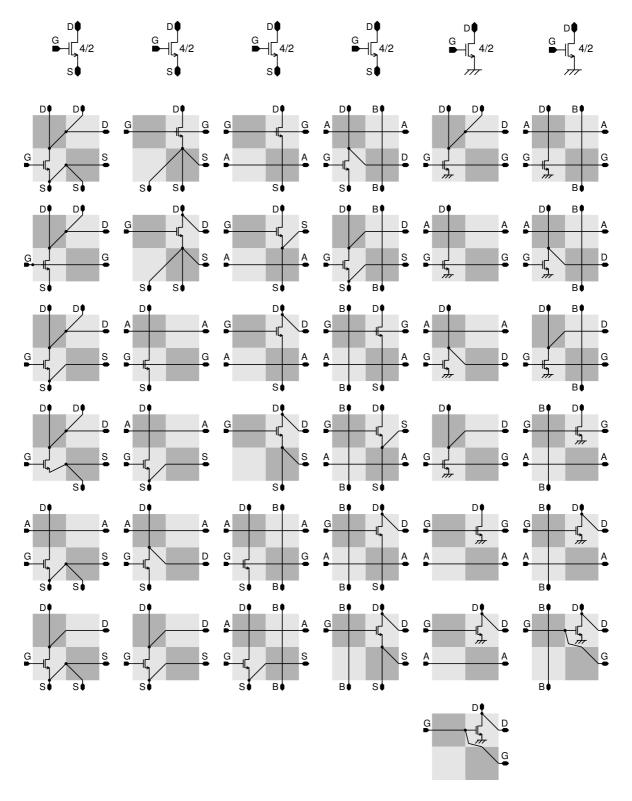

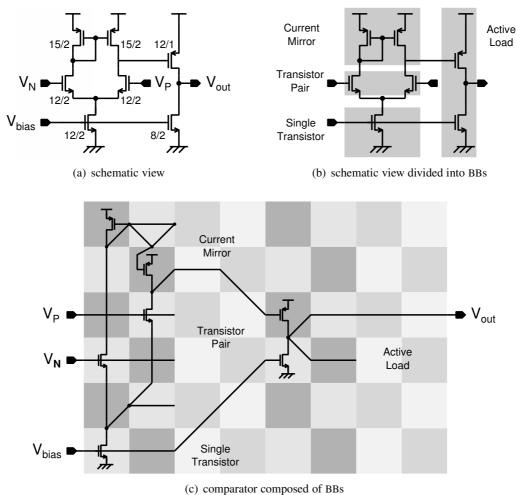

| Building Block Library for Case Studies I,II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                    |

| Evolutionary Algorithm for Case Studies I,II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                                                                                                                                                                                                                                                                                    |

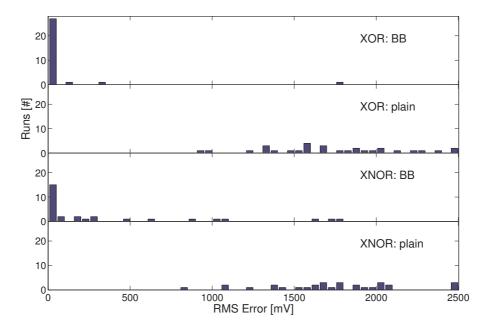

| Study I: XOR/XNOR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                    |

| Problem definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                    |

| Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

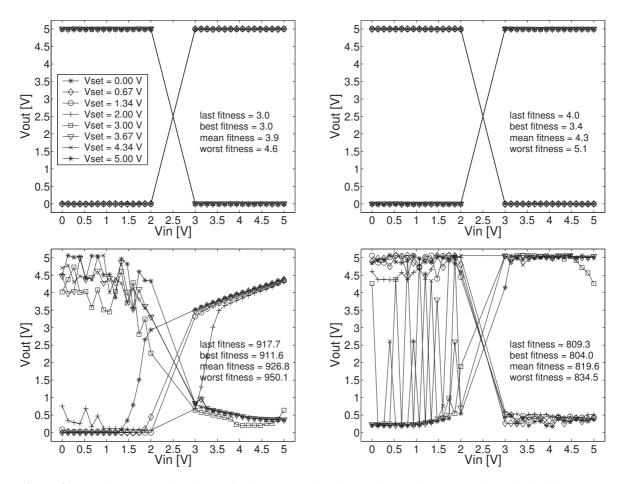

| Problem Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                       |

| Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ç .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                       |

| ÷ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                     |

| 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                       |

| o: Configuration Details and Pad and Signal Description 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | )5                                                                                                                                                                                                                                                                                                                                                                                                    |

| b: Configuration Details and Pad and Signal Description       30         guration Bit Assignment       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                       |

| с с <u>с</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )5                                                                                                                                                                                                                                                                                                                                                                                                    |

| guration Bit Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )5<br>)7                                                                                                                                                                                                                                                                                                                                                                                              |

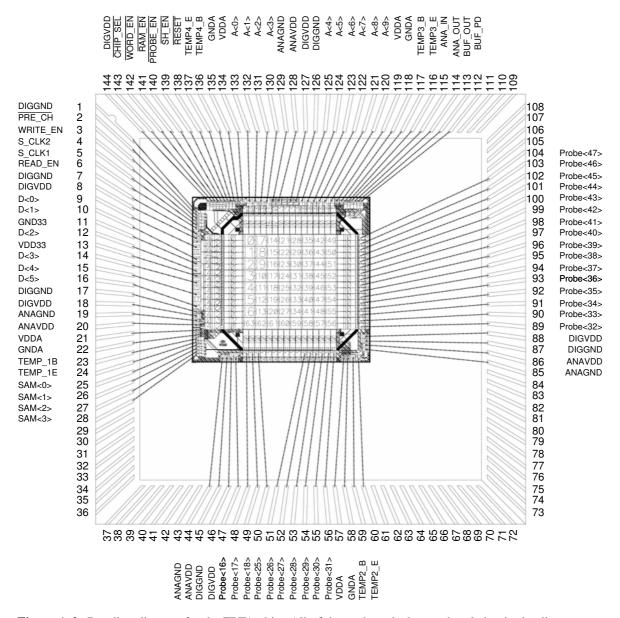

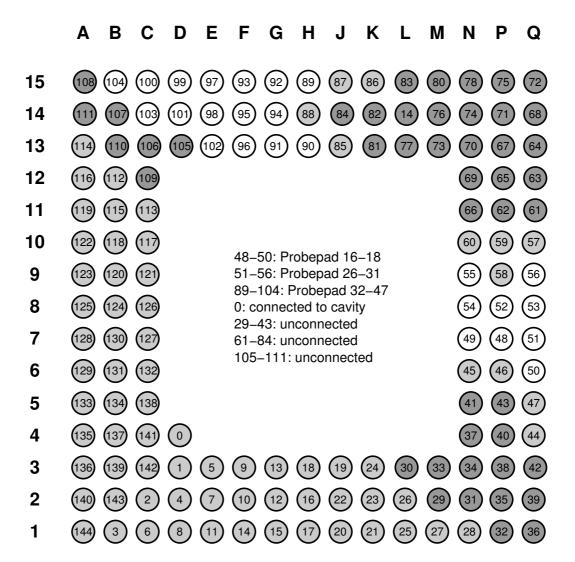

| guration Bit Assignment30Pads of the FPTA30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | )5<br>)7<br>)8                                                                                                                                                                                                                                                                                                                                                                                        |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )5<br>)7<br>)8<br>)9                                                                                                                                                                                                                                                                                                                                                                                  |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )5<br>)7<br>)8<br>)9                                                                                                                                                                                                                                                                                                                                                                                  |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins301 Description31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )5<br>)7<br>)8<br>)9<br>10                                                                                                                                                                                                                                                                                                                                                                            |

| guration Bit Assignment       30         Pads of the FPTA       30         ng Diagram       30         Carrier Pins       30         I Description       31         I – Bond Pad – Carrier Pin Assignment       31         I Operational Amplifier: Simulation Results       31                                                                                                                                                                                                                                                                                                             | )5<br>)7<br>)8<br>)9<br>10<br>13                                                                                                                                                                                                                                                                                                                                                                      |

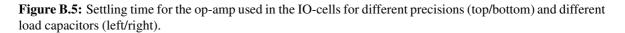

| guration Bit Assignment       30         Pads of the FPTA       30         ng Diagram       30         Carrier Pins       30         I Description       31         I – Bond Pad – Carrier Pin Assignment       31         I Operational Amplifier: Simulation Results       31         ation of the Rail-to-Rail IO-cell Buffer       31                                                                                                                                                                                                                                                   | )5<br>)7<br>)8<br>)9<br>10<br>13                                                                                                                                                                                                                                                                                                                                                                      |

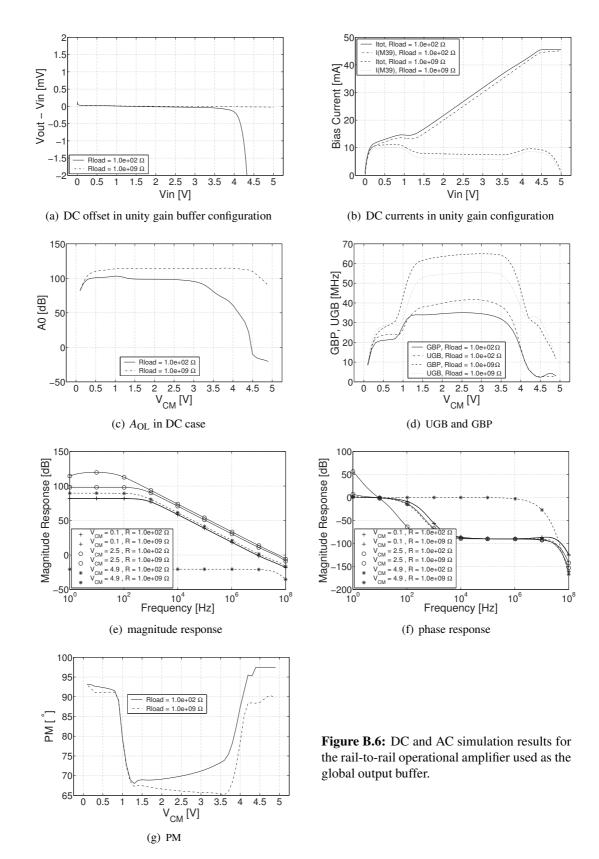

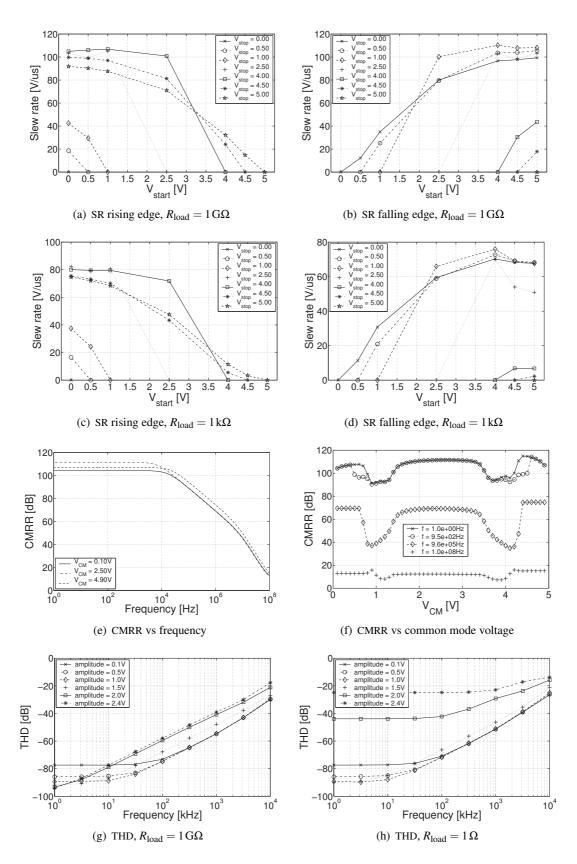

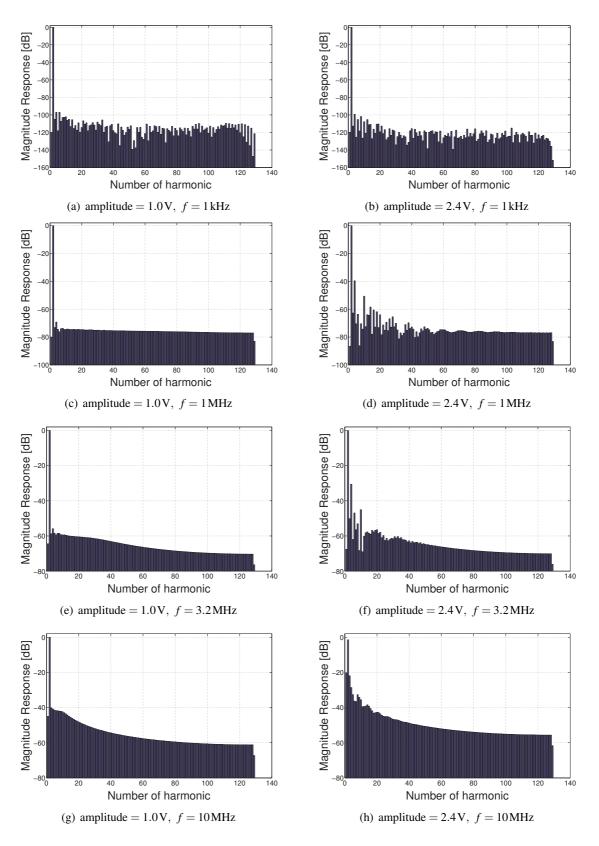

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32                                                                                                                                                                                                                                                                                                                                 | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23                                                                                                                                                                                                                                                                                                                                                    |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32                                                                                                                                                                                                                                                                            | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27                                                                                                                                                                                                                                                                                                                                              |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32                                                                                                                                                                                                                                                                                                                                 | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27                                                                                                                                                                                                                                                                                                                                              |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32                                                                                                                                                                                                                                                                            | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27<br><b>35</b>                                                                                                                                                                                                                                                                                                                                 |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer33                                                                                                                | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27<br><b>35</b><br><b>37</b>                                                                                                                                                                                                                                                                                                                    |

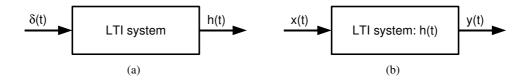

| guration Bit Assignment30Pads of the FPTA30ng Diagram30carrier Pins30Carrier Pins30l Description31l – Bond Pad – Carrier Pin Assignment31l Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer33l Systems Analysis33                                                                                                                                                                          | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27<br><b>35</b><br><b>37</b><br>37                                                                                                                                                                                                                                                                                                              |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer33I Systems Analysis33ete Fourier Transform33                                                                                                            | )5<br>)7<br>)8<br>)9<br>10<br>13<br>15<br>16<br>23<br>27<br><b>35</b><br><b>37</b><br>37                                                                                                                                                                                                                                                                                                              |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer33Parseval's Relation for the DFT33 | )5)7)8)9<br>10<br>13<br>15<br>16<br>23<br>27<br>35<br>37<br>37<br>38                                                                                                                                                                                                                                                                                                                                  |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I – Bond Pad – Carrier Pin Assignment31I Operational Amplifier: Simulation Results31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer33Parseval's Relation for the DFT33Parseval's Relation for the DFT33ystem Response to Sinusoidal Inputs33                                                                                       | 5)7<br>()7<br>()7<br>()7<br>()7<br>()7<br>()7<br>()7<br>()7<br>()7<br>(                                                                                                                                                                                                                                                                                                                               |

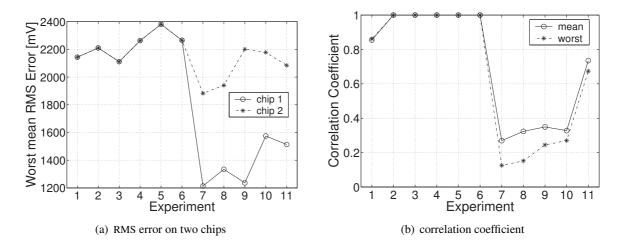

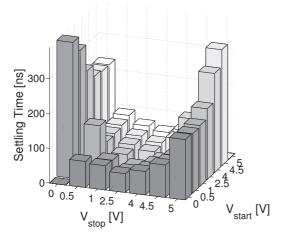

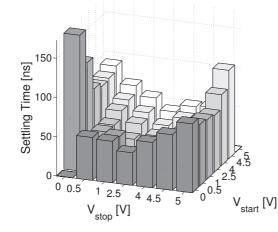

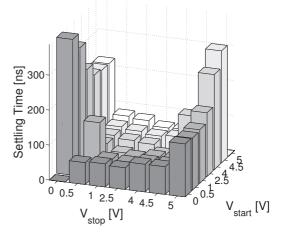

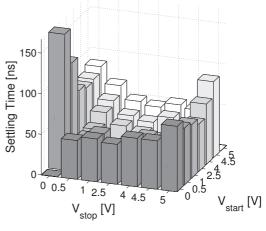

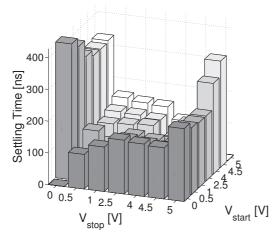

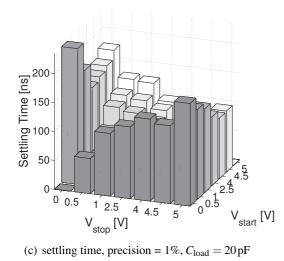

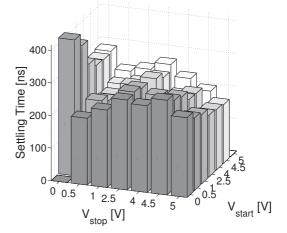

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I – Bond Pad – Carrier Pin Assignment31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer33Parseval's Relation for the DFT33Parseval's Relation for the DFT33ystem Response to Sinusoidal Inputs33Series of Comparator Experiments: Large Settling Time34                                                                             | )5)7)8)9<br>10)9<br>10]3<br>15<br>1623<br>27<br>35<br>37<br>38<br>37<br>38<br>39<br>41                                                                                                                                                                                                                                                                                                                |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I – Bond Pad – Carrier Pin Assignment31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer33Parseval's Relation for the DFT33Parseval's Relation for the DFT33ystem Response to Sinusoidal Inputs33Series of Comparator Experiments: Large Settling Time34arison of the Different Experiments: Histograms34                                          | )5)7)8)9<br>10)8)9<br>10<br>13<br>15<br>16<br>23<br>7<br>35<br>37<br>38<br>37<br>38<br>37<br>38<br>39<br>41                                                                                                                                                                                                                                                                                           |

| guration Bit Assignment30Pads of the FPTA30ng Diagram30Carrier Pins30Carrier Pins30I Description31I – Bond Pad – Carrier Pin Assignment31I – Bond Pad – Carrier Pin Assignment31ation of the Rail-to-Rail IO-cell Buffer31ation of the Rail-to-Rail Output Buffer32ation of the Rail-to-Rail Cell Buffer32ation of the Rail-to-Rail Cell Buffer33Parseval's Relation for the DFT33Parseval's Relation for the DFT33ystem Response to Sinusoidal Inputs33Series of Comparator Experiments: Large Settling Time34                                                                             | )5)5)7<br>(0)7<br>(0)8<br>(0)9<br>(1)3<br>(1)5<br>(1)5<br>(1)5<br>(1)5<br>(1)5<br>(1)5<br>(1)5<br>(1)5                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Evolutionary Algorithm for Case Studies I,II25Study I: XOR/XNOR Gate25Problem definition25Results25Study II: Tone Discrimination25Problem Definition25Results25Study III: Comparators25Geometrical Setup26Building Block Library27Overview of the Experiments28Test of the Hand-Designed Comparator28Summary of the Comparator Results28Summary of the Comparator Results29aimer and Acknowledgment29 |

| F | List | of Acronyms           |      |   |      |   |  |       |      |   |   |       |  |   | 347     |

|---|------|-----------------------|------|---|------|---|--|-------|------|---|---|-------|--|---|---------|

|   | E.5  | Test on a Second Chip | <br> | • | <br> | • |  | <br>• | <br> | • | • | <br>• |  | • | <br>346 |

# Introduction

I am turned into a sort of machine for observing facts and grinding out conclusions.

CHARLES DARWIN

The invention of the transistor in 1947 and the first successful integration of several transistors into one monolithic circuit in 1958 paved the way for a breathtaking development that has largely influenced and shaped today's life. Highly integrated microelectronic circuits are the cornerstone for the present era of information technology that brought radically new means of communications like cellular phones, e-mail or the internet. At the beginning of the third millennium, the aid of electronic devices like computers, microcontrollers or sensors seem to be indispensable for a vast variety of tasks ranging from office organization to space exploration as well as from medical applications to most of scientific research and design, control, and optimization in engineering.

As in recent years many signal processing tasks have been shifted from the analog to the digital domain, the aforementioned technological progress is often ascribed to the advances in digital circuit design. Yet, this is not the full truth: First, the nature of digital circuits is analog. On one hand, performance critical parts still require full custom design to push the technological limits. Second, prior to being used by digital synthesis tools, a library of logic primitives like gates, flipflops etc. must be generated so as to meet a set of analog specifications, as e.g. setup and hold times as well as acceptable input voltage ranges, noise immunities or gate delays. It is not until these devices are designed and verified that abstraction from their analog behavior can be achieved. Second, although nature exhibits quantized behavior according to last centuries ground breaking quantum theory, there is hardly any access thereof without analog electronics. In other words, even if most of the signal processing can indeed be done in digital hardware, any connection to the real word, be it to mass storage devices, be it wireless communication, a sound or graphics device, or the readout of a light intensity in an optical storage device, necessitates the conversion into an analog signal. Moreover, in a variety of consumer, engineering, and scientific products, sensors – in which a physical quantity is again first converted into an analog signal – play a crucial role. In summary, analog circuits will persist to be of great importance in future microelectronic systems.

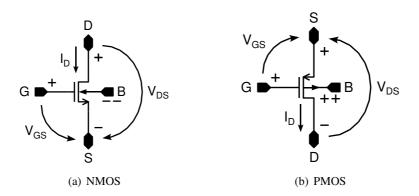

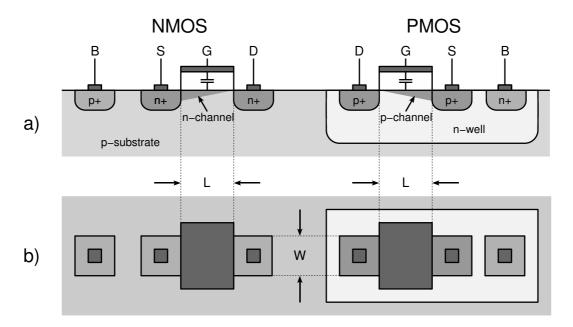

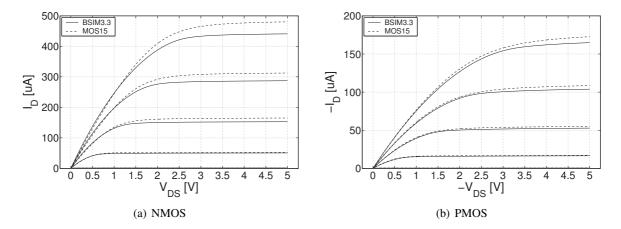

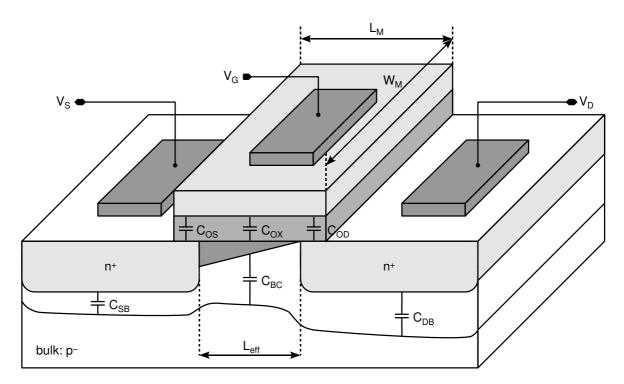

Although the first integrated circuits consisted of bipolar junction transistors (BJT), CMOS<sup>1</sup> has become the prevalent integrated circuit technology during the last two decades. Its high integration density paired with low static currents have proven to be most appropriate for digital circuit. In case of analog circuits, both, BJT and CMOS technology, as well as the combination thereof, that is BiCMOS<sup>2</sup> technology are used. Yet, most often CMOS is also the choice for analog circuits. For one, this allows to benefit from the rapid advances in process technology driven by the larger digital market. For the other, analog subsystems are nowadays frequently integrated together with digital systems to form a

<sup>&</sup>lt;sup>1</sup>Complementary Metal-Oxide Semiconductor

<sup>&</sup>lt;sup>2</sup>Bipolar Complementary Metal-Oxide Semiconductor

system on a chip (SoC). Here again the requirements of the digital part dictate the process technology to be CMOS.

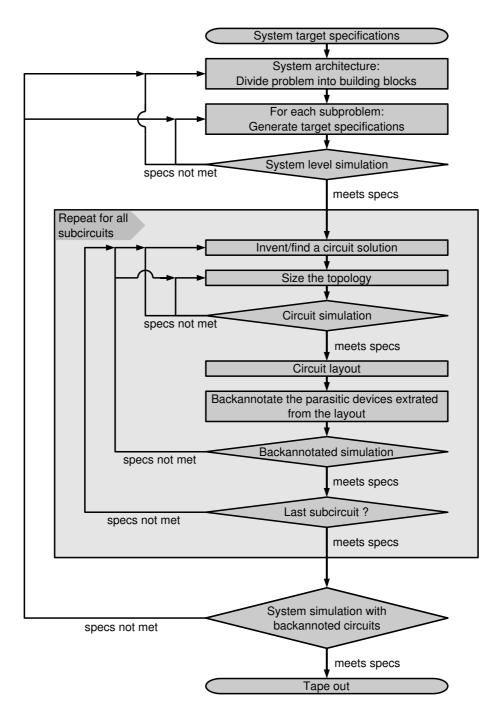

Unfortunately, the design of analog circuits is an intricate, tedious, time-consuming task, as it requires the designer to think about any single transistor. At first, a suited topology has to be found. In the next step the parameters of all the circuit components must be optimized, and finally, the resulting circuit has to be laid out. Even worse, because of parasitic resistors and capacitances introduced by the layout, it may be necessary to repeat the process of parameter optimization and layout several times. Furthermore, as the behavior of an analog circuit is inextricably connected to the device physics of the used circuit elements, great care must be taken to minimize an analog circuit's sensitivity to variances in the manufacturing process and its operating environment. Yet, even for a suited, fixed topology, a design of moderate size can comprise difficult relationships between some tens of design variables and a dozen performance goals.

# **Analog Design Automation**

The efforts to automate the digital design process have led to sophisticated tools that greatly leverage productivity. In the best case, the digital design can be defined in a hardware description language. This abstract description is then automatically translated into a suited netlist, which is eventually mapped onto the target technology at hand. Here, the success of digital synthesis tools is largely due to the high level of abstraction achieved for the utilized digital building blocks in that they can be characterized relatively uniformly by a few timing constants. In comparison to digital synthesis, the field of analog design automation is still in its infancy, which is not surprising given the tight linkage of analog circuit behavior and device physics mentioned above. In the context of SoC designs, the vast difference in the current productivity in analog and digital design, which leads to situations in which the analog part only occupies 10% of the whole chip, yet requires 90% of the design time, is sometimes referred to as *the analog dilemma* [Tou02]. Accordingly, improved design methodologies as well as advances in analog design automation are believed to be of utmost importance to eliminate this bottleneck encountered in SoC designs [Gie00], [Sha02], [Phe00a].

Analog design, and therefore analog synthesis comprises to steps: First, an electrical design – the schematic – of a circuit has to be generated. Second, this design has to be translated into an appropriate layout that it used for the production of the circuit (physical synthesis). Here, the first task, that is, finding an appropriate analog circuit for the problem at hand can be divided into four levels of difficulty [Lia01]:

- 1. Local parameter optimization: Fine-tune the device sizes of a given circuit topology, starting with a working set of circuit parameters.

- 2. Global parameter optimization: Find optimal circuit parameters for a given topology.

- 3. Topology selection: Choose the best out of a given set of predefined topologies and optimize its parameters.

- 4. Circuit design: Invent a circuit that meets the desired specifications from scratch.

The majority of attempts to automatic synthesis of analog circuits attack at the second level, that is they try to find the optimal design variables for a given topology. Thereby, the description of the optimization problem will embody some principles of conventional analog circuit design, as for instance, that matched transistor pairs ought to possess the same channel dimensions. The reported approaches to this kind of parameter optimization can be classified in three groups [dMH02a], namely, knowledge based, simulation based [Phe00a], [Alp03], and equation based methods [dMH01]. During the last couple of years, the latter two methods have been proven successful in optimizing high-performance analog cells, as e.g. operational amplifiers [Lia01], [Hen02], or an equalizer/filter block [Phe00b]. In case of the equation based method, even more complex problems have been tackled, for instance, the design of a pipeline analog-to-digital converter [dMH02a], or a phase locked loop [dMH02b]. Yet, it has only been very recently, that some of the attempts have matured into commercial products [Cad04b], [Syn05]. The same is true for one physical synthesis tool that allows the user to capture analog design constraints, which are then used to generate the layout [Cad04a].

## **Hardware Evolution**

Although the tools described above are certainly an important help for the analog designer, they nevertheless fall short of finding new, more efficient circuit topologies. Yet, the incorporation of topological synthesis adds two new opportunities to analog design automation: First, it can provide new circuit topologies for problems for which a satisfactory design solution has not yet been found. It should be noted that this situation can also arise when the migration to a new circuit technology renders formerly successful circuit topologies useless, e.g. due to a decrease in power supply voltage. Second, analog synthesis including topology search may be able to exploit the actual transistor physics more effectively than today's conventional circuit topologies, because they are not restricted to the human way of thinking about circuit design [Tho99]. Thus, the resulting circuits may yield better or equal performance whilst consuming equal or less power and area.

Although the automatic invention of analog circuits is an intriguing idea, one must not forget that the inclusion of topology selection in the synthesis process vastly increases the complexity of the problem. In fact, to date, no heuristic algorithm is known that could deterministically solve the problem of analog circuit invention, which is not surprising if one takes into account that it has only been recently that a heuristic could be developed for analog synthesis on the parameter optimization level [dMH01].

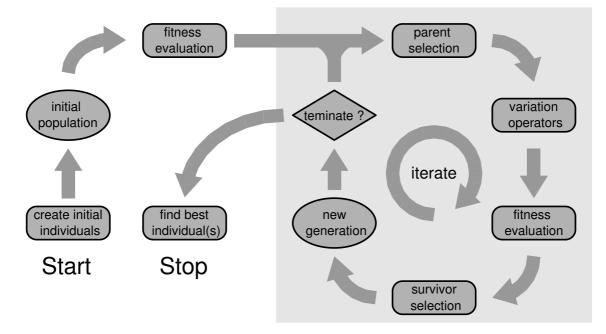

On the other hand, evolutionary algorithms, a class of model-free heuristics, are often successfully used to solve hard optimization problems that cannot be solved deterministically. In analogy to natural evolution, evolutionary algorithms process a whole population of feasible solutions. In the course of an artificial evolution experiment, the members of the population are varied by genetic operators like mutation and crossover. A selection mechanism ensures that the probability for a member of the population to propagate its genetic information to the next generation depends on their ability to solve the problem at hand. Hence, probabilistic sampling of the search space is combined with a selection pressure towards better solutions.

The application of evolutionary algorithms to engineering design problems is one, if not the main topic of a relatively young research field referred to as hardware evolution or evolvable hardware. Generally speaking, the field comprises a wide variety of approaches including evolutionary algorithms, modeling of ontogenetic processes, and the design of electronic systems that mimic the behavior of a biological immune system. However, in the context of this thesis, the first approach, namely that to use evolutionary algorithms to solve synthesis problems, is most relevant. In principle, the field of hardware evolution lends itself to the evolutionary development of any kind of hardware. Practically, the target systems are almost exclusively restricted to be realizable as digital or analog circuits. Depending on the implementation process, hardware evolution is either referred to as *extrinsic* or *intrinsic*. It is *extrinsic* if the behavior of the phenotype is simulated, and *intrinsic* if hardware is used in the evolutionary loop to evaluate the fitness of candidate solutions produced by the algorithm.

# Scope of this Thesis

On one hand, extrinsic, that is, simulation based hardware evolution may be more flexible, and its implementation requires less effort if existing circuit simulators can be used. On the other hand, intrinsic hardware evolution offers other beneficial properties. First, in case of intrinsic evolution experiments, the successfully evolved circuits are guaranteed to work at least on the particular substrate they are evolved on. In contrast, in extrinsic approaches, the evolutionary algorithm may not always find optimal circuit solutions but rather tend to exploit imperfections of the circuit simulator or the test setup used for the fitness evaluation. Second, hardware tests can speedup artificial evolution in that they are often faster than simulations. The potential speedup is most evident for time-consuming transient analyses of large designs, since simulation times scale with the size of the circuit, whereas a hardware test is independent of the circuit size for a given task. Moreover, intrinsic fitness evaluations inherently capture the real conditions the prospective circuits are to work in, as e.g. noise and the imperfections of the production process. The simulation of such effects dramatically increases the time necessary for a fitness evaluation. In fact, the verification of circuits invented by extrinsic hardware evolution will most probably have to be more elaborate than for circuits consisting of a well known topology whose design variables are optimized, as the sensitivity to variations of the circuit parameters or operating conditions are much more uncertain.

Yet, intrinsic hardware evolution also offers a completely new perspective conceivable as field evolvable hardware. During the last decade, the success of programmable logic arrays, as e.g. FPTAs<sup>3</sup>, has inspired similar developments for the analog domain. These FPAAs<sup>4</sup> are general purpose analog devices that offer a variety of different analog functions. Typically, they are composed of analog cells like operational amplifiers [Zet99] and are targeted at filtering and signal conditioning applications [Lat01], [AN203].

Although recent FPAAs usually can be conveniently configured through dedicated software tools, field evolvable hardware can be advantageous in the following regards: First, here too hardware evolution may simplify the design task at hand. Second, field evolvable hardware can adapt to electrical and environmental conditions that cannot be known a priori. Such situations may arise e.g. in DSL<sup>5</sup> applications, where the precise electrical properties of the copper telephone wire used for connecting the subscriber to a broadband network are unknown, the calibration of intermediate frequency filters necessitated by the fabrication tolerances [Mur03], or space missions, in which the electronic circuitry has to cope with temperature variations of several hundred Kelvin [Sto04], [Zeb04].