# RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

KIRCHHOFF-INSTITUT FÜR PHYSIK

## **DISSERTATION**

## submitted to

the

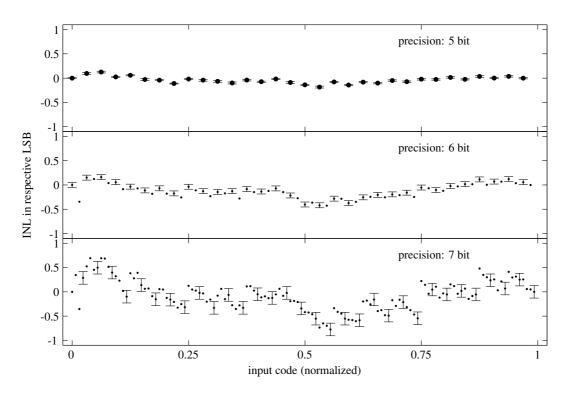

Joint Faculties for Natural Sciences and Mathematics

of the Ruprecht-Karls-Universität Heidelberg, Germany

for the degree of Doctor of Natural Sciences

presented by M.S. Felix Schürmann born in Kassel, Germany

Date of oral examination: 8.6.2005

Exploring Liquid Computing in a Hardware Adaptation:

Construction and Operation of a Neural Network Experiment

Referees: Prof. Dr. Karlheinz Meier

Prof. Dr. Norbert Herrmann

Erkundung von Liquid Computing in einer Hardwareadaptierung: Konstruktion und Betrieb eines neuronalen Netzwerkexperiments - Die zukünftige Steigerung von Rechenleistung basiert auf Miniaturisierung, hoher Integration und Parallelisierung. Allerdings entstehen bei der Annäherung an Nanometerstrukturen neue Herausforderungen bezüglich der Verläßlichkeit der Bauelemente, der Leistungsaufnahme und der Konnektivität. Diese Aspekte finden in den momentan vorherrschenden Mikroprozessorimplementierungen noch nicht genügend Berücksichtigung. Um so wichtiger ist es, die Erforschung alternativer Rechenarchitekturen und -strategien voranzutreiben, die große Anzahlen unzuverläßiger Bauelemente nutzen können und dennoch nur eine moderate Leistungsaufnahme haben. Diese Doktorarbeit beschreibt die Konstruktion eines Experiments, welches es ermöglicht, Adaptierungen von künstlichen neuronalen Netzwerkparadigmen in Silizium bezüglich ihrer Anwendbarkeit, effizienten Leistungsaufnahme und Fehlertoleranz zu untersuchen. Der hier vorgestellte Aufbau besteht aus peripherer Elektronik, programmierbarer Logik und Software, um einen gemischt digital-analogen CMOS Mikrochip zu betreiben, auf dem ein flexibeles Perceptron mit 256 McCulloch-Pitts Neuronen implementiert ist. Mit Hilfe dieses neuronalen Netzwerkexperiments wird eine kürzlich veröffentlichte Strategie untersucht, mittels derer rekurrente Netzwerktopologien nutzbar gemacht werden können. Die hier präsentierte erstmalige Adaptierung von Liquid Computing an ein neuronales Netwerk auf CMOS-Basis bestätigt dessen vermutete Eignung für eine Hardwareadaptierung. Dabei wird nicht nur die Machbarkeit demonstriert, sondern auch die Toleranz gegenüber Substratvariationen und die Robustheit gegenüber Fehlern, die während des Betriebs auftauchen.

Exploring Liquid Computing in a Hardware Adaptation: Construction and Operation of a **Neural Network Experiment** - Future increases in computing power strongly rely on miniaturization, large scale integration, and parallelization. Yet, approaching the nanometer realm poses new challenges in terms of device reliability, power dissipation, and connectivity—issues that have been of lesser concern in today's prevailing microprocessor implementations. It is therefore necessary to pursue the research on alternative computing architectures and strategies that can make use of large numbers of unreliable devices and only have a moderate power consumption. This thesis describes the construction of an experiment dedicated to exploring silicon adaptations of artificial neural network paradigms for their general applicability, power efficiency, and faulttolerance. The presented setup comprises peripheral electronics, programmable logic, and software to accommodate a mixed-signal CMOS microchip implementing a flexible perceptron with 256 McCulloch-Pitts neurons. This *neural network experiment* is used to explore a recent strategy that allows to access the power of recurrent network topologies. While it has been conjectured that this *liquid computing* is suited for hardware implementations, this first time adaptation to a CMOS neural network affirms this claim. Not only feasibility but also tolerance to substrate variations and robustness to faults during operation are demonstrated.

# **Contents**

| In | trodu                   | ction   |                                                       | 1  |

|----|-------------------------|---------|-------------------------------------------------------|----|

| 1  | Neural Network Concepts | 5       |                                                       |    |

|    | 1.1                     | Founda  | ations                                                | 5  |

|    |                         | 1.1.1   | Historical Origins of ANNs – A Hardware's Perspective | 5  |

|    |                         | 1.1.2   | VLSI Variety                                          | 7  |

|    |                         | 1.1.3   | Present Trends and Future                             | 9  |

|    | 1.2                     | Design  | n Considerations                                      | 10 |

|    |                         | 1.2.1   | General                                               | 10 |

|    |                         | 1.2.2   | Network Model Implications                            | 10 |

|    |                         | 1.2.3   | VLSI Implications                                     | 15 |

|    | 1.3                     | Realiza | •                                                     | 18 |

|    |                         | 1.3.1   | A Neural Network Experiment                           | 18 |

|    |                         | 1.3.2   | ANN ASICs                                             | 19 |

|    |                         | 1.3.3   | Experimental Framework                                | 20 |

|    |                         | 1.3.4   | Suitable Training Approaches                          | 21 |

| 2  | Con                     | puting  | without Stable States                                 | 23 |

|    | 2.1                     | Recurr  | rent Neural Networks                                  | 23 |

|    |                         | 2.1.1   | Finite Automata and Neural Networks                   | 23 |

|    |                         | 2.1.2   | The Liquid State Machine Approach                     | 24 |

|    | 2.2                     | Explor  | ring Liquid Computing in Hardware                     | 27 |

|    |                         | 2.2.1   | Motivation                                            | 27 |

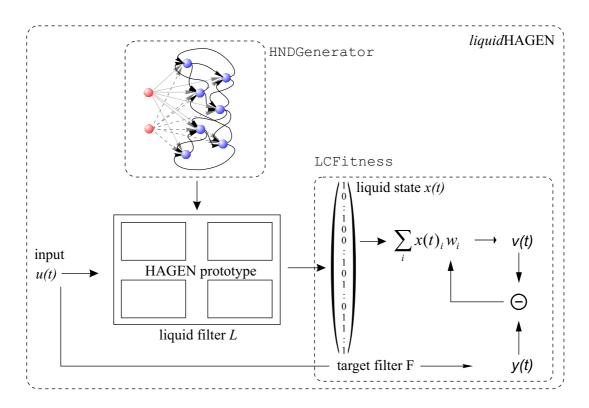

|    |                         | 2.2.2   | liquidHAGEN                                           | 28 |

|    | 2.3                     | Liquid  | Dynamics                                              | 31 |

|    |                         | 2.3.1   | Input Driven Networks                                 | 31 |

|    |                         | 2.3.2   | The Edge of Chaos                                     | 33 |

|    |                         | 2.3.3   | Performance Measures                                  | 35 |

| 3  | The                     | HAGE    | N Prototype Implementation                            | 39 |

|    | 3.1                     | Learnin | ng from the Predecessor ASIC                          | 39 |

|    | 3.2                     | HAGE    | N Overview                                            | 42 |

|    | 3.3                     | Netwo   | rk Block                                              | 47 |

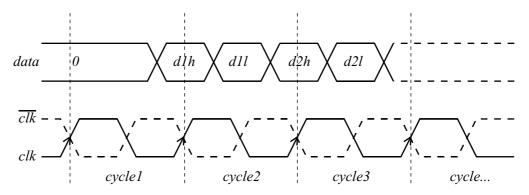

|    |                         | 3.3.1   | A Network Cycle                                       | 48 |

|    |                         | 3.3.2   | Elementary Synapse                                    | 49 |

|    |                         | 3.3.3   | Neuron                                                | 53 |

|    |                         | 3.3.4   | Weight Storage                                        | 58 |

|    | 3 4                     | Digital | 1-to-Analog Converters                                | 60 |

II CONTENTS

|     | 3.5    | Interface    |                                                  | 61  |

|-----|--------|--------------|--------------------------------------------------|-----|

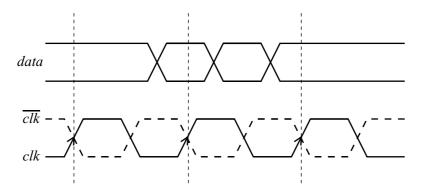

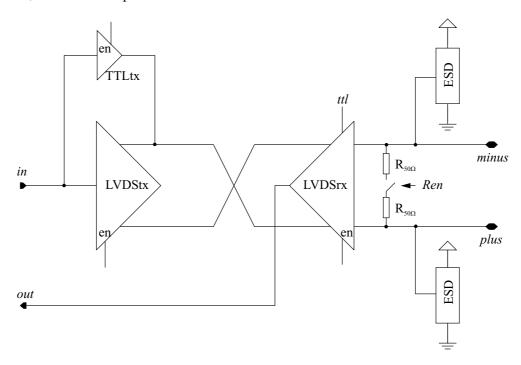

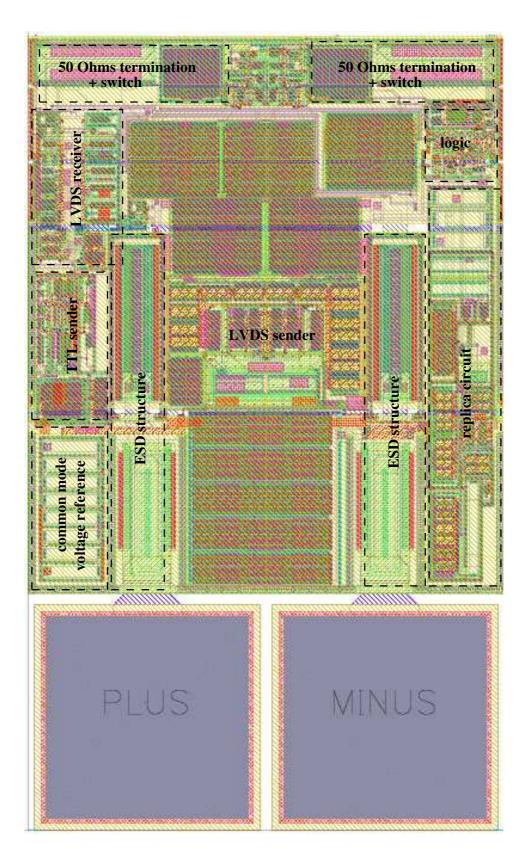

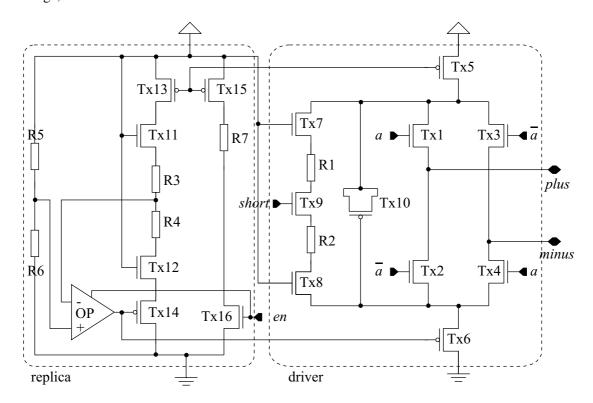

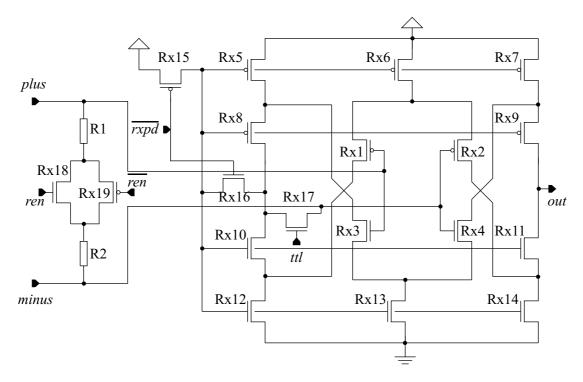

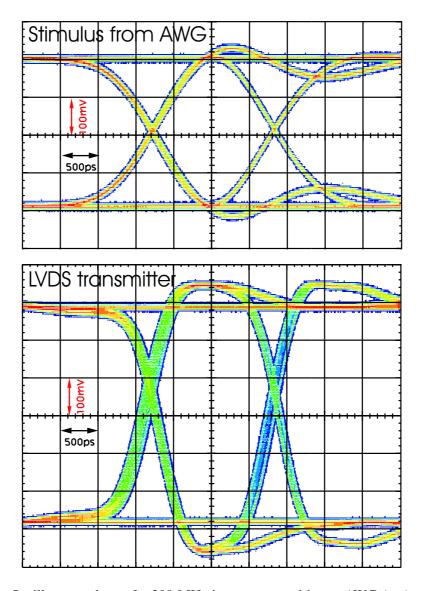

|     |        | 3.5.1 Phys   | sical Layer                                      | 62  |

|     |        | 3.5.2 Logi   | ical Layer                                       | 68  |

|     | 3.6    | Power Cons   | iderations                                       | 70  |

|     |        | 3.6.1 Pow    | ver Consumption of a Network Block               | 70  |

|     |        | 3.6.2 The    | HAGEN Prototype                                  | 71  |

|     | 3.7    |              | HAGEN Prototype                                  | 72  |

|     |        |              | or Modifications                                 | 73  |

|     |        |              | ing                                              | 73  |

|     |        |              | look                                             | 75  |

|     |        |              |                                                  |     |

| 4   | -      | erimental Fr |                                                  | 77  |

|     | 4.1    |              |                                                  | 77  |

|     |        |              | N ASICs                                          | 77  |

|     |        |              | icated Peripheral Electronics                    | 78  |

|     |        | 4.1.3 PCI-   | -based Mixed-Signal FPGA Adapter                 | 83  |

|     |        | 4.1.4 Gen    | eral Purpose Computer                            | 87  |

|     |        | 4.1.5 Adv    | ancing the Framework                             | 88  |

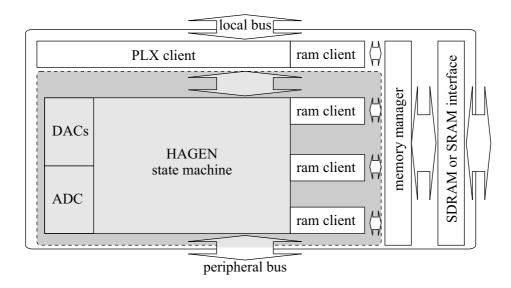

|     | 4.2    | Programmab   | ole Logic Design                                 | 91  |

|     |        | 4.2.1 Ove    | rview                                            | 91  |

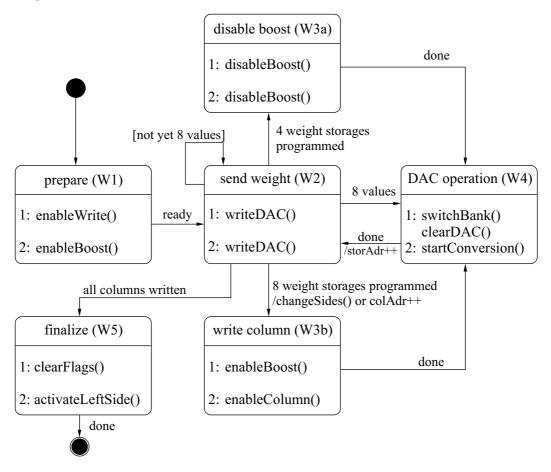

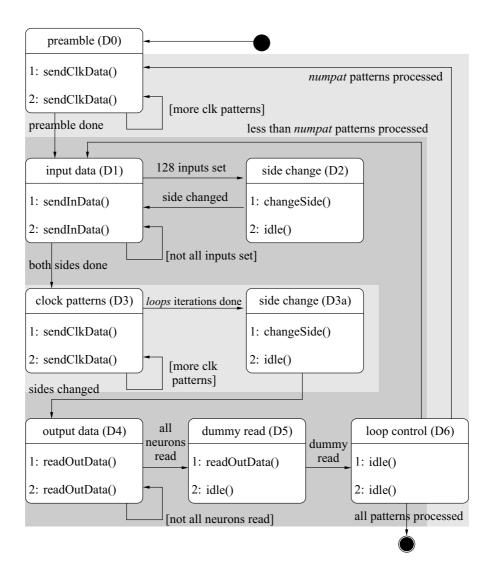

|     |        | 4.2.2 HAC    | GEN State Machine                                | 93  |

|     |        | 4.2.3 Exte   | ensions                                          | 94  |

|     | 4.3    |              | tware (HANNEE)                                   | 96  |

|     |        | 4.3.1 Ove    | rview                                            | 96  |

|     |        |              | dware Abstraction Layer                          | 98  |

|     |        |              | at/Output Pattern Management and Operation Modes | 99  |

|     | 4.4    | _            | S                                                | 102 |

|     |        |              | dware-in-the-loop                                | 102 |

|     |        |              | calculated Weights                               | 104 |

|     |        |              | aid Computing                                    | 106 |

|     |        |              |                                                  |     |

| 5   | -      | erimental Re |                                                  | 111 |

|     | 5.1    |              |                                                  | 111 |

|     | 5.2    |              | Hardware Liquid                                  | 111 |

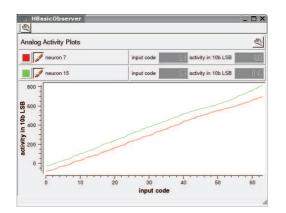

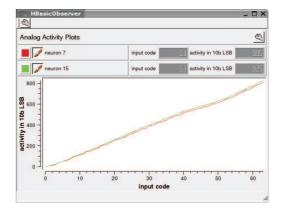

|     |        |              | al Experiments                                   | 111 |

|     |        | 5.2.2 Obse   | erving the Edge of Chaos                         | 115 |

|     |        | 5.2.3 Scal   | ing Behavior                                     | 121 |

|     | 5.3    | Fault-Tolera | nce                                              | 123 |

|     |        | 5.3.1 Rob    | ustness to Substrate Variations                  | 123 |

|     |        | 5.3.2 Grad   | ceful Degradation with Time                      | 125 |

|     |        | 5.3.3 Grad   | ceful Degradation with Individual Synapse Faults | 131 |

| Di  | scussi | on           |                                                  | 135 |

| -/1 | ussi   | V41          |                                                  | 133 |

| A   | -      | -            | ng Supplements                                   | i   |

|     |        | •            | ession Training                                  | i   |

|     | A.2    | Mean-Field   | Theory for Input Driven Networks                 | ii  |

CONTENTS

| B   | HAGEN Prototype Supplements |                                         |      |  |  |

|-----|-----------------------------|-----------------------------------------|------|--|--|

|     | B.1                         | Inter-Block Routing                     | vi   |  |  |

|     | B.2                         | Bonding Diagram                         | vii  |  |  |

|     | B.3                         | Interface                               | viii |  |  |

|     |                             | B.3.1 Command-Address Symbols           | viii |  |  |

|     |                             | B.3.2 Slow-Control Registers A and B    | ix   |  |  |

|     | B.4                         | Clock Pattern                           | X    |  |  |

|     |                             | B.4.1 Preamble-Pattern                  | X    |  |  |

|     |                             | B.4.2 A Loopable Clock Pattern          | X    |  |  |

|     | B.5                         | HAGEN Measurements                      | xii  |  |  |

| C   | Expe                        | erimental Framework Supplements         | xiii |  |  |

|     | <b>C</b> .1                 | Peripheral Electronics                  | xiv  |  |  |

|     | C.2                         | Pattern Handling                        | XV   |  |  |

| D   | Vari                        | able Network Resources                  | xix  |  |  |

| E   | Supp                        | plementary Liquid Computing Experiments | XXV  |  |  |

| Ac  | ronyr                       | ns x                                    | xxi  |  |  |

| Bil | oliogr                      | raphy xx                                | xiii |  |  |

IV CONTENTS

# Introduction

Unraveling the principles of biological nervous systems has shown to be a long lasting and enormously challenging endeavor. To date it seems that only a unified effort of disciplines ranging from biology to medicine and from physics to engineering will lead to a complete picture [53, 137].

While this laborious process may still need decades in order to converge, along the way many useful results and insights will be gained. It was over 60 years ago that McCulloch and Pitts [134] used a mathematical model to give an abstract description of neural activity. On the one hand, this formalism made it possible to assess the (computational) capabilities and limitations of networks of neurons and encouraged others to conceptualize the biological findings. On the other hand, the research on artificial neural networks (ANN) became a topic of its own 1. The most prominent example for the former is the strongly biologically motivated *perceptron* by Rosenblatt [173], later fully understood in its restrictions [140] and shown to have a *universal approximation property* if used in multiple layers [97]. An important achievement of the ANN research was the rediscovery 2 of the gradient-descent *back-propagation algorithm* [178] which opened the field for technical applications.

The history of hardware adaptations of neural networks reflects these different directions: Early implementations like the *SNARC* by Minsky [138] and the *MARK I Perceptron* by Rosenblatt [80] and more recently Mead [135] with his *silicon retina* aimed at mimicking biological systems. In parallel, a multitude of hardware implementations were dedicated to merely accelerate the training and operation of ANNs. Primarily, this was in reaction to the shortcomings of available computing power for adequate software simulations in the late eighties and early nineties. The approaches ranged from digital arithmetic accelerators to stand-alone analog implementations. The prevailing technology used is the *very large scale integration* (VLSI) of *complementary metal oxide semiconductor* (CMOS) devices, also the basis for modern digital microprocessors. An acceleration of the computation by dedicated ANN circuits therefore has to arise from architectural rather than from technological advantages. Yet, the designs of modern microprocessors incorporate instruction and data level parallelism as well as highly optimized non-standard logic that uses the analog properties of the substrate [43]. Due to the flexibility of software and the ease of porting it from one processor generation to the next, allowing immediate utilization of technological advances, present research activity is dominated by software implementations of ANNs.

However, architectural advantages that can be achieved with dedicated circuits are not limited to mere acceleration. Other performance aspects are of increasing importance: An unresolved and critical issue is the power dissipation of integrated circuits. The speed of modern microprocessors is already governed and limited by their thermal power management. Reducing the supply volt-

<sup>&</sup>lt;sup>1</sup>An elaborate selection of important publications can be found in the collection edited by Anderson and Rosenfeld [6].

<sup>&</sup>lt;sup>2</sup>The back-propagation algorithm was independently discovered several times: 1969 by Bryson and Ho [32], 1974 by Werbos [222], and 1985 by Parker [159] and LeCun [120], when it was finally widely spread in the neural network community.

2 INTRODUCTION

ages along with the shrinking of the feature size may increase the power efficiency of the active components, but the increased operation frequencies, larger off-currents, and higher component densities in effect worsen the power dissipation. The miniaturization of the structures, furthermore, is accompanied by the susceptibility to imperfections in the substrate and to variations in the manufacturing process which reduce the yield. Ultimately, manufacturing processes in the nanometer-realm will rely on principles such as self-assembly which is likely not only to produce unreliable devices but also to limit the interconnectivity and require some regularity. These challenges are anticipated by the semiconductor industry in their bi-annual semiconductor roadmap [104].

The future of semiconductors therefore relies on the research of alternative computing architectures that incorporate features such as sparseness of activity, reconfigurability, and fault-tolerance. From observations of biological nervous systems, one can conclude that it is indeed possible to realize these properties in a single system. The goal of contemporary research on hardware implementations of neural networks should therefore aim to answer the question of how these properties can be efficiently realized in an artificial system.

Part of the answer lies in the technical realization of the artificial system; and part in the learning strategy that actually configures the neural architecture. This thesis describes the construction and operation of a neural network experiment and is dedicated to start exploring both parts of the answer.

In the current setup, the experiment allows to assess a network paradigm based on a flexible perceptron with about 33,000 synapses and 256 McCulloch-Pitts neurons for its efficient realization in a standard CMOS technology. The appropriate concepts and implementations of the neural network model in mixed-signal VLSI have been developed in [187] and have received partial contributions by this thesis work. The ANN microchip is accommodated by a framework comprised of peripheral electronics, programmable logic, and software running on a microprocessor. This modularity is the key to do research on a wide variety of questions: those that deal with the feasibility of specific network paradigms, those that are concerned with the exploration of training strategies, and others that have a specific application in mind. The neural network experiment is a conjoint effort with several other researchers<sup>3</sup>.

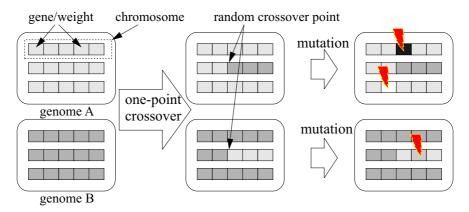

In [86] the neural network experiment has been used to extensively explore learning with evolutionary algorithms. The approach relies on iteratively testing weight configurations and—if appropriately adapted—it can profit from the parallelism inherent to the hardware and its fast reconfigurability and operation. Competitive results in commonly used pattern classification benchmark problems have been achieved. The hardware-in-the-loop operation, which tests the effect of a synaptic weight change on the actual ANN hardware, furthermore allows one to cope with variations of the substrate.

While those investigations use feed-forward topologies where the activity is propagated from input neurons to the dedicated output neurons in a pipelined fashion, biological nervous systems usually also have long or short-range *recurrent* connections. May the precise purpose be difficult to pinpoint, the overall effect is clear: Recurrent connections make the network response depend on its history, allowing perhaps regulatory cycles as well as short-term memories. Specifically, the essential difference is that feed-forward networks are static mappings from an input to an output, while recurrent networks are dynamical systems.

For the processing of time varying inputs, recurrent neural network are promising whereby configuring the weights appropriately proves to a difficult task [106]. In 2001, Maass et al. [131] and Jaeger [105] published independently a strategy that is fundamentally different to other learn-

<sup>&</sup>lt;sup>3</sup>This thesis concentrates on the electronics; for a software perspective see [86]. The programmable logic will be detailed in the Ph.D. thesis of T. Schmitz, yet to be published.

ing strategies for recurrent networks to date in that it does not change the synaptic weights of the recurrent neural network at all but rather draws them once randomly from a given distribution. Instead, only an observer is trained that continuously interprets the transient behavior of the recurrent neural network. Maass et al. and Jaeger showed that in many cases a linear readout suffices to predict outputs that are non-linear functions of the input.

Intuitively, this strategy may be viewed as an input constantly perturbing a dynamical system; the observable state of this system is then interpreted by the readout. The internal interactions within the dynamical system will evoke changing trajectories for different inputs and time courses. If the interactions in the system are appropriate, non-linear projections of the input are observable in the transient dynamics which are available for linear readout. According to the terminology of Maass et al. this strategy is called *liquid computing*.

Different types of recurrent neural networks have been proposed to be configurable as adequate<sup>4</sup> dynamical systems [131, 105, 21], yet all of them have been implemented in software. However, there are good reasons to adapt the strategy for a hardware implementation: First of all, a physically realized dynamical systems frees one from having to compute the non-linear projections and to handle the desired high-dimensionality explicitly. Furthermore, the published simulation experiments showed that essentially random synaptic weights can accommodate appropriate dynamics. This may be used to hide device variations of the substrate in the weight distribution or it may even enrich the dynamics of the system. Lastly, the robustness with which randomly generated recurrent neural networks yield adequate dynamics gives rise to the assumption that this property is not emerging from the individual synaptic connections or neurons but rather from the distributed interaction of several of them. This promises an inherent tolerance to faults throughout operation.

In this thesis the strategy of Bertschinger et al. [21] is adopted to realize a hardware adaptation of liquid computing—to the knowledge of the author this is the first reporting. This hardware implementation allows to test the propositions of robustness to substrate variations and the tolerance to faults in a physical experiment and to assess liquid computing with recurrent neural networks as a possible paradigm for future computing architectures.

The thesis is partitioned into five chapters: The first chapter will motivate the design of the neural network experiment while the second chapter introduces liquid computing and its implementation in detail. Chapters three and four describe the used ANN microchip and the experimental framework along with the contributions to both. Finally, chapter five will present the experimental data collected on liquid computing.

<sup>&</sup>lt;sup>4</sup>Other dynamical systems may similarly be considered as long as they provide certain properties; for details see Ch. 2 and [132].

# **Chapter 1**

# **Hardware Neural Network Concepts**

Since the early days of artificial neural networks, hardware implementations have accompanied the research. Recently, the ever increasing performance of general-purpose digital microcomputers and the ease of their programming challenge the enormous effort of dedicated hardware development. Yet, the ongoing miniaturization of computing substrates to the nanometer realm make it necessary to explore architectures that can cope with unreliable devices, interconnect limitations, and a moderate power dissipation. The inherent parallelism and robustness of neural networks in combination with hardware-friendly paradigms and adequate training strategies offer a promising approach. In this chapter a combined hardware-software approach is presented that allows to assess these propositions in a physical experiment.

#### 1.1 Foundations

#### 1.1.1 Historical Origins of ANNs – A Hardware's Perspective

While the *summing amplifier* by Swartzel [196] implementing an electrical threshold device preceded the seminal article of 1943 by McCulloch and Pitts [134] which presents neurons as binary decision units, the first dedicated neurocomputer was realized by Minsky and Edmonds in 1951 [138]: The *Stochastic Neural-Analog Reinforcement Calculator* (SNARC) was an electromechanical implementation of 40 cells that—with a certain probability—transmitted incoming electrical pulses. The individual transmission probabilities were realized by multivibrator circuits that could be adjusted by potentiometers. With the help of magnetic clutches these adjustments could be initiated by the network pulses themselves which allowed an ongoing reinforcement learning. SNARC was tested on a series of maze-running experiments, where at a number of vertices a 'direction-decision' had to be performed to ultimately arrive at the exit. Possible advantages of a dedicated parallel hardware implementation for the fault-tolerance have already been observed by Minsky (p. 4-39 in [138]):

"Perhaps most impressive was the fact that at any time during operation, the random net of Snarcs could be rearranged, wires pulled out, tubes removed, and even fuses blown, and yet, if not too many snarcs were inactivated, the machine would, again after a period of confusion, adapt to the new situation and find paths to the preferred vertices." [Marvin Minsky, 1954]

While this was the first hardware implementation of a pulse-based artificial neural network, it was primarily a toy demonstrator for Minsky's theoretical work on reinforcement learning.

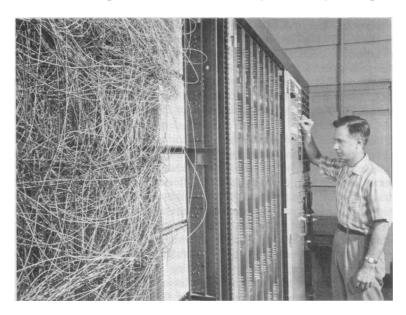

It was Rosenblatt in 1957 [173] who extended McCulloch-Pitts networks, which needed to be explicitly constructed for each problem, to networks with variable connection weights. The so-called *perceptron* could be trained with reinforcement learning to classify patterns and was even capable of generalizing on previously unseen patterns. In the following years Rosenblatt performed numerical simulations [174] on an IBM 704 mainframe computer [99] and in a parallel effort with co-workers he developed the *MARK I Perceptron* hardware with automatic learning [80]. Even though the actual MARK I hardware was not remarkably faster than the simulations [23], the first realization of a 'perceiving' machine and the ease of varying the stimuli, i.e., stimuli could be provided with overhead slides, attracted a lot of interest. Moreover, Rosenblatt anticipated a much higher performance gain of hardware implementations for larger network architectures where the parallelism would pay off [174]. Technically, the MARK I had a 20x20 grid of photo-receptors, each hand-wired to up to 40 of the 512 *associator units* which is shown in Fig. 1.1. These were responsible for thresholding their input signals, summing them and generating a weighted output signal via a dc-motor driven potentiometer which represented the synapses. The associator units then were connected to one of up to 8 threshold units (relays driven by dc amplifiers).

**Figure 1.1:** The MARK I Perceptron: in front the patch board for connecting the 400 photo-receptors with up to 40 of the 512 associator units each. Photograph taken from [82].

The success of the MARK I drew increasing interest to the field of neural network hardware, and in 1960 Widrow and Hoff published a supervised learning rule along with a hardware implementation of a threshold unit with 16 adjustable weights, the *adaptive linear* (ADALINE) [225]. The initial ADALINE element used multi-aperture magnetic cores [41, 27] for the weight storage and a human operator needed to manually adjust the gains according to a mechanized procedure (knobby ADALINE). Widrow demonstrated that it is possible to build networks from theses elements, the multiple ADALINE (MADALINE), and even commercialized improved versions with automatic electronic learning with his Memistor company [224]. The Widrow-Hoff learning

1.1. Foundations 7

procedure—being a local, error-correction strategy—is also known as the *least-mean-squares rule* or *delta-rule* and is the basis for the renowned *back-propagation algorithm*.

With the 1969 book by Minsky and Papert [140], a rigorous mathematical description of a perceptron's capabilities was given, and especially, its limits. While it was already known by Rosenblatt and co-workers that a perceptron is not able to correctly distinguish between linearly non-separable patterns, Minsky and Papert proved that this limitation is indeed a general inability to compute a certain set of logical functions<sup>1</sup>. In a generalization they showed that furthermore certain types of pattern distinctions cannot be made by realistic perceptrons, i.e., perceptrons that have a limited fan-in. Their (wrong) conjecture that these inabilities are fundamental even to more complex perceptron architectures (e.g. multi-layer perceptrons), further accelerated the renunciation of perceptrons, which had already started in the mid 60s [82]. For the following 15 years, research funding was directed from neural networks to areas like artificial intelligence, and even though theoretical progress was still made, hardware implementations were increasingly neglected.

The early 80s brought new innovations and approaches to the field of neural networks, e.g. 1982 *self-organizing maps* by Kohonen [114] or 1983 the *neocognitron* by Fukushima [64], and attracted a new group of researchers: physicists. Initially, Hopfield drew the connection between his proposed network model and the Ising model of spin-glass physics in 1982 [93]. He was followed by Kirkpatrick with the *Boltzmann machine* [110] and Geman with *simulated annealing* [68]. In 1984 Hopfield expanded his model and proposed an electrical circuit for its realization [94]. He was followed by researchers proposing an electro-optical [55] and electronic implementation based on MNOS/CCD [180]. Meanwhile, the availability of general purpose computers promoted software simulations, e.g., the *MARK I & II* packages by Hecht-Nielsen, but at the same time raised the desire for faster simulation speeds. This was the impetus for the development of general purpose digital neural network accelerators such as the *MARK III & IV* 1984-1986 [82].

Finally, the renaissance of the artificial neural network research began with the 1986 book edited by Rumelhart and McClelland [179]. The authors used the accumulated knowledge about neural processing to formulate a framework for a connection-based, distributed and highly-parallel approach to neural computing. With this book the back-propagation algorithm became widely known [178] and previously intractable problems suddenly became solvable. In 1989 Hornik, Stinchcombe and White even proved that multi-layer perceptrons are universal function approximators [97].

While previous hardware implementations experimented with all different kinds of substrates, the inherent parallelism of CMOS electronics in conjunction with ever advancing tools and fabrication let VLSI become the prevailing choice for the implementation of neural processing systems. In 1989 Mead [135] showed impressively that CMOS VLSI is not restricted to digital implementations but, rather, is well suited to directly model neural functionality by physical properties of the substrate (*silicon retina* [206], *electronic cochlea* [128]). Henceforth, the race was on between digital, analog and mixed-signal implementations.

#### 1.1.2 VLSI Variety

The late 1980s and the early 1990s brought a wave of new approaches to accelerate neural computing. On the one hand, many commercially available parallel computing platforms were evaluated for their suitability to accelerate neural networks, e.g., implementations on the Connection Machine 1990 by Singer [203], transputer based solutions by Vuurpijl 1992 [221], or a CRAY YM-P

<sup>&</sup>lt;sup>1</sup>And even worse: The percentage of Boolean functions  $f: \{0,1\}^n \to \{0,1\}$  that are linearly separable goes to 0 for  $n \to \infty$  [228, 1].

supercomputer adaptation 1993 by Leung and Setiono [123]. On the other hand, many semiconductor companies took on the developments of research groups for dedicated neural network chips to make neural computing available on a large scale—among them Intel, Siemens, IBM, Hitachi, Philips, and others. A concise overview can be found in [126]. A selection of neural network chips and systems built from it is given in Tab. 1.1.

Many more hardware implementations were and still are developed in university laboratories and are described in several overview articles [90, 100, 126, 83, 16, 34, 192, 20]. Digital implementations of neurocomputing hardware are described in [19, 191, 237]. Purely analog approaches are reviewed in [52, 214]. As shown in [170], fuzzy systems are very similar to neural networks which led to fuzzy hardware implementation be included in an overview [171].

In order to understand the diversity of approaches in hardware neural networks it is useful to categorize them. Several authors have proposed classification schemes which either can be applied to neural hardware or were explicitly postulated for it. An example of the former is the categorization of the computing architecture according to Flynn 1972 [60] in the instruction and data level parallelism, e.g., multiple-instruction multiple-data (MIMD). Nordström and Svensson, on the other hand, proposed to divide neural hardware by the degree of parallelism [156]. Other suggested to classify it by the biological evidence of the realization [72, 192] or by the training type [214].

A simple and coarse, yet useful, scheme was described by Heemskerk [83] in 1995 which goes back to Rückert [177]. Even though it does not factor in the purpose or biological relevance of the neural device, it clarifies major differences. As a major premise, he differentiates between *neurochips* and *neurocomputers*. This recognizes that reconfigurability, training, and interfacing are an integral part of a neurocomputer but need not necessarily be contained in a neurochip. A neurocomputer then can be comprised either of *standard chips* or dedicated *neurochips*. The category built from standard chips is divided into systems comprising a *single (sequential) processor* supported by a dedicated *accelerator* or systems comprised of *multiprocessors*. The category of dedicated neurochips is divided into *analog* and *digital* solutions or a combination of both (*hybrid* or *mixed-signal*).

It is understood that there are potential performance increases when going from the category of sequential processors with accelerator to the category of dedicated mixed-signal neurochips [72, 177, 83, 19]. Tab. 1.1 shows the classification scheme according to [83] which originates from Rückert [177] and lists prominent examples.

| neuro-    | standard<br>chips | seq. + accelerator<br>multiprocessor | ANZA plus (Motorola 68020, 68881) [82]<br>Mark IV (Motorola 68020) [82] |

|-----------|-------------------|--------------------------------------|-------------------------------------------------------------------------|

| computers | neuro<br>chips    | analog                               | Mod2 (Intel ETANN) [145, 91]                                            |

| Computers |                   | digital                              | Siemens SYNAPSE-1 (MA-16) [169]                                         |

|           |                   | mixed-signal                         | ANNA [25]                                                               |

Table 1.1: Classification of neurocomputers with prominent examples following Heemskerk [83].

It can be observed that the interest in building dedicated neurocomputers declined in the mid 90s. The reasons for this were manifold and still challenge todays neural hardware development:

First of all, in order to be efficient, neurocomputers need to be optimized for a certain neural network model. For a hardware implementation, the dedication to a model means a limited flexibility which in turn complicates or even prevents the exploration of new neural network paradigms [83]. As long as several paradigms are competing, investments to develop fullblown neurocomputers do not seem appealing. 1.1. Foundations

• A second, important reason is the steady growth of computing power in conventional computers and *digital signal processors* (DSPs) which is due to an ever higher device count (semiconductor roadmap 2003 [103]). That this indeed translates into an increased performance for simulated neural networks was shown in [8]. Architectural advancements in microprocessor design such as the integration of vector units [121] together with optimizing compilers let desktop computers become so powerful that they are well suited for simulating neural networks of limited size. This development is promoted by the observation that for a lot of research and applications the available software performance is already satisfactory. The expected advantage of a hardware solution by further exploiting parallelism therefore might not be needed [192] or not be relevant due to accompanying pre- and post-processing not making use of further parallelization (Amdahl's law [4]).

• Lastly, the possible performance gain of dedicated hardware solutions compared to software implementations comes along with a substantially increased design effort. For mixed-signal solutions, which are expected to have the highest performance potential, the effort is even higher because of the poorly automated design process of full-custom analog circuitry. The resulting longer time-to-market and higher financial investment at a reduced flexibility burden the development of dedicated neural hardware [171, 133].

#### 1.1.3 Present Trends and Future

It was however commercial interest, not research on hardware neural networks itself, which abruptly ended. A number of implementations of different paradigms is present in recent surveys [214, 20], special issues [37, 168, 125], as well as in conference proceedings, and journals [69, 164, 35]. Furthermore, the aspect of closely mimicking biological neural systems in CMOS as started by Mead [135] yields an increasing number of spiking neural network implementations, e.g. [230, 65, 73, 190, 185].

The competition with general purpose microprocessors and digital signal processors most affected the research on dedicated digital neural hardware [157]. This is because digital neural networks are considered to be essentially hardware accelerators [146], and therefore they are in direct competition. Nonetheless, dedicated digital implementations are still considered for applications due to a problem-specific performance advantage. For example, a new level-1 trigger based on neural networks for the H1 experiment at the HERA particle accelerator is proposed [44]. The currently observed renewed attention for digital implementations, especially those in programmable logic devices, is mainly caused by advances in the design tools and the so-called hardware/software co-design (HW/SW co-design) [229]. A prominent example are embedded systems where different types of resources are present (e.g. microprocessor cores, programmable logic, and signal processors) and an optimal apriori partitioning of the design becomes difficult. The idea of the HW/SW co-design is to allow the developer to easily assess the resulting performance with the help of a fully automated design environment. If applied to the development of neural hardware, the best use could be made of the parallel resources in the programmable logic and the flexibility of soft-programmable microprocessors while reducing the design effort [171, 237, 61]. Successful implementations are already reported [172, 160].

The automation of analog and mixed-signal integrated circuit design is unlike harder and a topic of research itself [71, 124, 117]. These types of designs therefore are quite costly in terms of design time and engineering expenses. According to [115] an analog solution therefore needs to provide an increase in efficiency (i.e. performance, size, or energy consumption) of at least an order of magnitude over digital ones as to become attractive for commercial use. Immediate applications arise for the realization of extremely low power consumption and robust devices, e.g.

implantable bio-medical devices [122, 199]. Others, such as nonlinear channel equalization in telecommunications, additionally demand extremely high speed and are shown to be realizable with neural networks [147, 161, 197, 54].

However, the main reasons for contemporary research on adapting neural architectures and principles for an efficient hardware implementation arise from the expected future of VLSI substrates: While the semiconductor roadmap [103] describes<sup>2</sup> in detail the expected steps of CMOS miniaturization, and in this regard predicts the increase of microprocessor performance, a whole chapter is dedicated to emergent devices and architectures [104] in order to take on the challenges concerning the power dissipation and unreliability of individual devices. The miniaturization towards the nanometer-realm furthermore will raise the problem of interconnecting the small structures. The construction of these shrunk structures will likely rely on self-assembling and will hence require some kind of regularity of the structures. The economical use of resources in terms of using as few devices as possible, on the other hand, will be less important due to the realizable integration. Consequently, computing architectures have to be developed that make use of the large scale of integration by sparsely using the individual devices simultaneously. Similarly, tolerance to faults will be required: those resulting from manufacturing as well as those exhibited throughout operation. Biological neural systems prove that these paradigms can be realized, thus the challenge is to find suitable adaptations for available and future hardware substrates.

## 1.2 Design Considerations

#### 1.2.1 General

The network model that is motivated and described in the following sections has been proposed in [186, 187]. It aims at an efficient implementation by a standard CMOS process and incorporates aspects of low power consumption, scalability, and flexibility.

#### 1.2.2 Network Model Implications

If one reverts to the analog nature of the elementary components present in the CMOS substrate, one can profit from a multitude of properties inherent to the transistor. Not only functions such as non-linear amplification, thresholding, and a multitude more when used in combination with other transistors [218, 67] but also the possibility of low power operation allow a dramatic increase in efficiency compared to using transistors merely as binary switches in digital circuits. Yet, an efficient mapping between the analog properties and the network model is crucial and not trivial. A key aspect is to choose a hardware-friendly network model [142], i.e., a model that explicitly allows an efficient representation by physical quantities [218, 20]. On the lowest level, efficient implementations of threshold devices have been developed, e.g. the *Neuron-MOS* transistor [201] suited for CMOS, and neural networks proposed to be implemented with single-electron transistors [74]; an overview can be found in [20]. Furthermore, efficient mappings of more complex properties and functions such as sigmoid transfer functions, normalization, multiplication have been realized [219].

The very feature of continuous quantities in analog VLSI comes at a cost: There are no discrete states the analog signals may be restored to, which consequently makes the design more susceptible to noise and offsets [181]. Binary logic in digital systems is the strict opposite and copes with much higher noise levels. Consequently, binary signals can be stored, buffered, distributed,

<sup>&</sup>lt;sup>2</sup>Indeed, the roadmap is a collaborate effort of the semiconductor industry and rather a detailed plan than a mere prognosis; it is thus often called self-fulfilling.

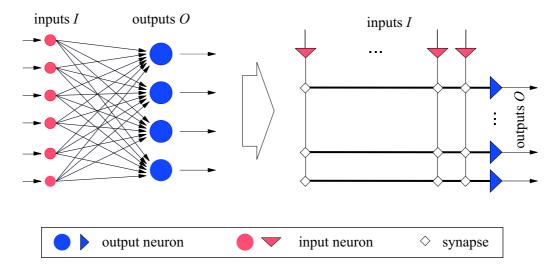

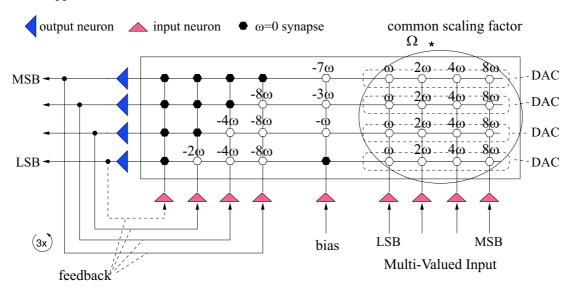

**Figure 1.2:** Fully-connected feed-forward perceptrons can be efficiently mapped to an array-based structure. Adapted from [184].

and transmitted much simpler than analog signals. Digital implementations therefore will be a good choice if high signal-to-noise ratios are required [219]; this will be important for long-range transportation of network activity.

One solution is to choose a low-connectivity network model, e.g. *cellular neural networks* [38, 176, 37], were connections only need to be made to nearest-neighbors. The more promising approach though is to combine analog and digital signal processing: The computationally intensive parts are to be implemented in analog VLSI, preferably in a regular, array-based structure [115]. Digital circuitry then will have to ensure a reliable and routable communication as to allow the scaling of the neural network.

A fan-in limited, analog, array processing with digital interface provides an efficient way for vector-matrix multiplication and is suited for many neural network paradigms, from feed-forward perceptrons ([25] or c.f. Fig. 1.2) to support vector machines [69]. Yet, the details of the elementary analog cells exhibit relevant differences. These will be especially important if the design is to be adapted to smaller feature size technologies. The ability to cope with imperfections and variations in gain and offset is a challenge for the analog circuits, the training, and ultimately the underlying network model. In contrast to off-chip learning, where the synaptic weights are calculated according to an idealized model of the neurons and weights, chip-in-the-loop approaches or on-chip training can deal with the actual characteristics and mismatches of the neural network substrate [142, 214].

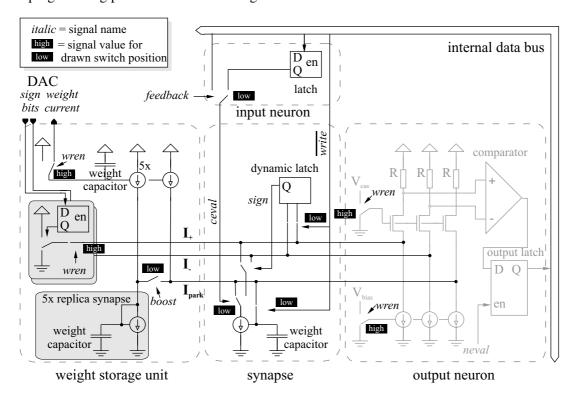

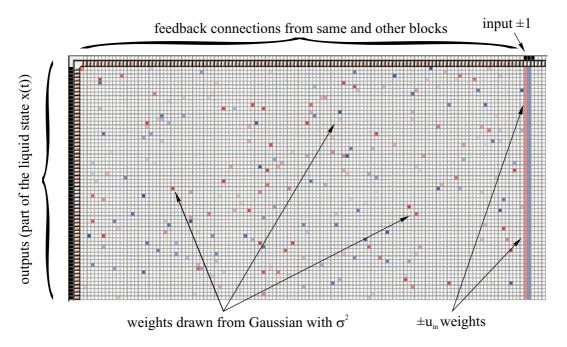

A Network of Network Blocks The model proposed in [186, 187] utilizes McCulloch-Pitts neurons and arranges them to a set of fully-connected, single-layer perceptrons in rectangular blocks with binary inputs as shown in Fig. 1.2. In the following, this is referred to as a *network block*. The network block's response is modeled by the standard perceptron formula, where I, O are the binary inputs and outputs,  $\omega$  the synaptic weights, and  $\Theta(x)$  is the Heaviside step function:

$$O_i = g(\sum_j \omega_{ij} I_j), \quad g(x) = \Theta(x), \ \omega \in [-1, 1] \ I, O \in \{0, 1\}.$$

(1.1)

In addition to the straight-forward rectangular structure, the choice of McCulloch-Pitts neurons yields a natural border between the analog and digital implementation: the synapse array and the

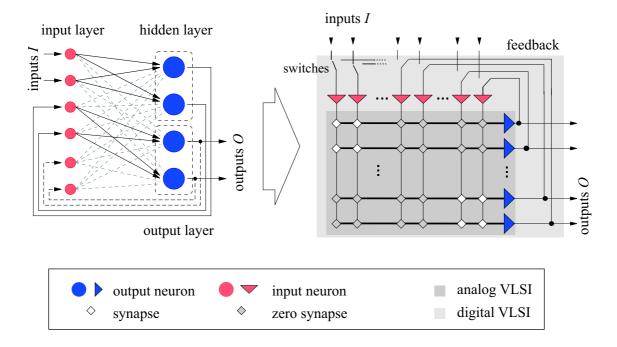

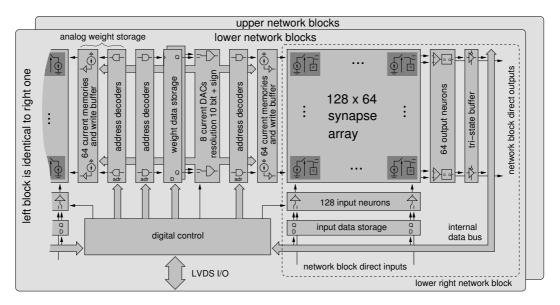

input stage of the output neurons can be implemented efficiently in analog VLSI; the input neurons are merely digital switches just as the outputs of the output neurons are digital signals. The right side of Fig. 1.3 illustrates this partitioning with dark gray (analog) and light gray shading (digital).

**Figure 1.3:** Multiple layers or even recurrent connections can be realized in the array structure if switchable connections allow to feed back the output to the input layer while setting appropriate synaptic weights to zero. Adapted from [184].

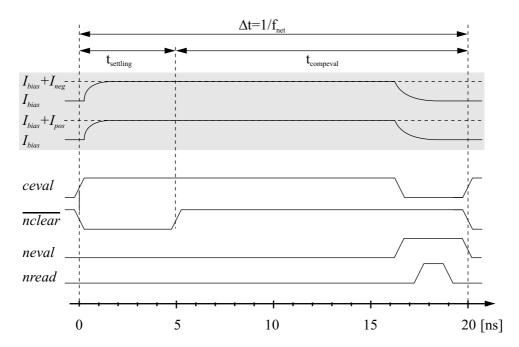

Having mentioned the inherent limit to linearly separable classification, a single-layer perceptron paradigm would restrict the neural network in its generality<sup>3</sup>. If extended by feedback connections, i.e., connections to transport the binary signals of the output neurons back to the input layer, the presented fully-connected single-layer perceptron can be configured to represent a multi-layer perceptron or recurrent network (this is illustrated by Fig. 1.3). To allow this behavior, it is necessary to configure the feedback connections and to set appropriate weights to zero in order to restrict the input signals to activate only synapses of certain output neurons. The necessary condition for this to work properly is the time-discretized operation of the network which allows to evaluate the various layers of a network in consecutive loops. One of these loops is called a *network cycle*. The evaluation of one layer consequently has to be assigned a time  $\Delta t$ ; the network then operates at a frequency of:

$$f_{\text{net}} = \frac{1}{\Lambda t}.\tag{1.2}$$

With this, the network response yields:

$$O(t + \Delta t)_i = \Theta(\sum_j \omega_{ij} I(t)_j + \sum_k \omega_{ik} O(t)_k). \tag{1.3}$$

<sup>&</sup>lt;sup>3</sup>Interestingly, many real-world benchmarks problems have a large proportion of linearly separable data which makes single-layer perceptrons applicable. Furthermore, experiments with the presented ANN ASIC show that a majority voting between independently trained single-layer perceptrons can improve classification performance beyond the limit given by the amount of linearly separable data [86].

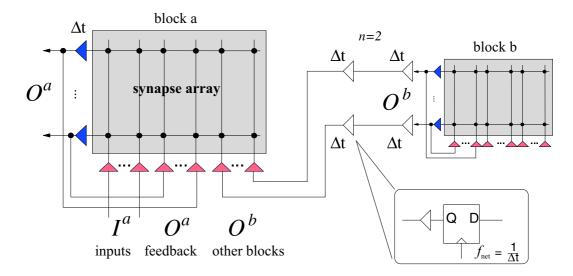

**Figure 1.4:** Multiple network blocks can be operated synchronously when the propagation delay is an integer multiple of the network frequency: The absolute delay may be large. Figure taken from [184].

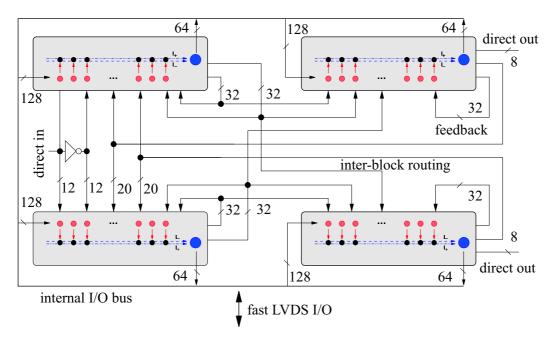

Of course, the inputs to one network block are not restricted to come from the same block only. They rather can be provided from other, similar network blocks as shown in Fig. 1.4. If those network blocks are operated at the same network frequency, the network response for one block (here, block *a*) can be consistently described by the following equation (the superscripts determine the block):

$$O(t + \Delta t)_i^a = \Theta\left(\sum_j \omega_{ij} I(t)_j^a + \sum_k \omega_{ik}' O(t)_k^a + \sum_l \omega_{il}'' O(t - n\Delta t)_l^b \dots\right). \tag{1.4}$$

The last term shows an exemplary connection from a second network block  $b(O_1^b)$ .

An intriguing feature is that—as long as the propagation delay from distant blocks is an integer multiple of the network frequency—the absolute delay is irrelevant for a synchronous operation. It is this property that allows the scaling to large networks.

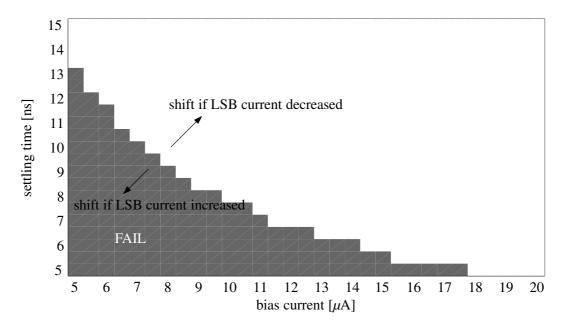

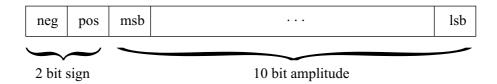

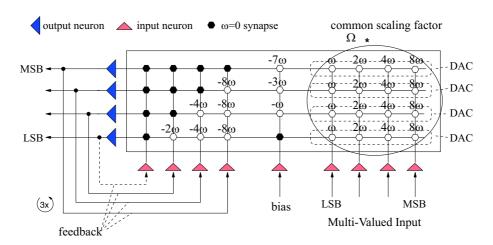

Variable Network Resources Since some perceptron training algorithms require continuous neuron activation functions (e.g., the prominent back-propagation algorithm [178]), many perceptron implementations do not restrict themselves to binary inputs/outputs. Unfortunately, the multiplier circuit then needs to be incorporated into each synapse if the full parallelism is to be exploited. Several examples with fully analog multipliers in the synapses are found in literature: ETANN [91], BELLCORE [3], and others [182, 144]. The largest problem of multiplier circuits is their susceptibility to fixed-pattern noise which results in offsets and gain errors. Another obvious disadvantage is the area penalty of synapses that need to accommodate the weight storage and the multiplier circuitry. Furthermore, it is difficult for analog multiplier circuits to achieve simultaneously low power consumption, high dynamic range, and a good noise resistance [78]. An alternative strategy is to use discretized multi-value inputs and have a simplified multiplier circuit in the synapse, e.g., a multiplying digital-to-analog converter (MDAC) in the AT&T ANNA [25] or weights stored in a binary weighted fashion [70] which releases the design from the need for data-rate analog-to-digital conversion (ADC).

Indeed, the latter concept can be successfully adopted for the binary inputs propagated here: A straightforward way to feed multi-valued signals is to consider *n* inputs as a group encoding

an *n* bit integer. The integer value then needs to be translated into an analog network activity according to the significance of the representing bits. The least significant bit (LSB) induces  $\omega$ , the next bits  $2\omega$ ,  $2^2\omega$  and so on. The most significant bit (MSB) induces  $2^{n-1}\omega$  into the network:

$$\omega_i = 2^i \omega \quad \text{for} \quad 0 \le i < n.$$

(1.5)

Essentially, this is a digital-to-analog conversion (DAC). Depending on the weight quanta  $\omega$  and the number of bits n, the maximum induced activity of a multi-valued input is  $(2^n - 1)\omega$ .

Similar to the pooling of binary inputs for multi-valued signals, it is possible to group McCulloch-Pitts output neurons to act as an m bit integer output in the range of  $[0, 2^m - 1]$ . The task to be performed by this group of neurons is to measure the analog network activity present at their inputs and represent this activity as an integer. Basically, they have to perform an analog-to-digital conversion. Although a single neuron only performs a threshold discrimination, it is possible to configure a recurrent topology with self-inhibiting feedback in order to operate similar to a successive approximation ADC [215].

**Figure 1.5:** Network configuration of a 4-bit input being connected to a 4-bit ADC by a 4-to-4-bit synapse of weight  $\Omega$ .

Fig. 1.5 depicts an exemplary configuration of a network that has a 4 bit multi-value input and extracts the activity by a 4 bit output neuron. It is to be noted that the activity induced to the pooled output neurons needs to be the same (for the same multi-value input) and has to stay constant over the course of the successive approximation.

In particular, the analog-to-digital conversion is achieved by the following procedure: One binary input is used as a bias (constantly activated) and adjusts the threshold values for the participating bits according to their significance, i.e., for the LSB 0, for the next bit  $\omega$  and for the MSB  $(2^m-1)\omega$ . After one network cycle, the MSB has reached its final state and subtracts  $2^m\omega$  from all other bit lines if active. After the second cycle, the second most significant bit is stable and will go on to adjust the lower significant bit lines and so on. This process is completed after m network cycles. The easiest way to ensure stability of the solution is to prohibit feedback connections of bits to themselves or higher significant bits, i.e., the upper left and the diagonal of the weight matrix need to be zero.

Even though the relative weights are fixed for the pool of synapses inducing a n bit input to the neurons performing the m bit successive approximation, it is possible to change their absolute

value by introducing a common scaling factor  $\Omega \in [-1,1]$ . Essentially, this pool of synapses then can be considered an n-to-m bit synapse of weight  $\Omega$ ; the case n=m=1 is the elementary synapse and  $\Omega = \omega$ .

If the number of bits for the inputs is chosen equal to the number of bits used in the output representation, the outputs can be directly fed to other inputs and arbitrary topologies of these so-called *variable network resources* can be realized in the network block architecture. On the other hand, the number of bits for the input and output do not have to be the same; a prominent case is  $n \neq 1$  and m = 1 where multi-bit inputs are fed to a single McCulloch-Pitts neuron. Yet, there is no restriction to the combination of multi-valued inputs of different bit resolution.

Binary inputs therefore are not a restriction for interfacing multi-valued inputs, quite to the contrary, they reduce synapse complexity which allows smaller synapse circuits. This is an important issue for the reconfigurability of the network topology; some implementations even limit the achievable network topologies as to minimize the amount of unused synapses, i.e. area consumption [182]. As it can be seen from Fig. 1.5, synapses indeed remain unused, i.e., are set to zero. Similarly, Fig. 1.3 illustrates that strictly layered feed-forward topologies as well leave parts of the synapse array unused. An immediate consequence is that it is desirable to have small individual synapses in terms of area coverage and, most importantly, that inactive synapses do not contribute to the power consumption.

Experimental results for variable network resources are shown in appendix D.

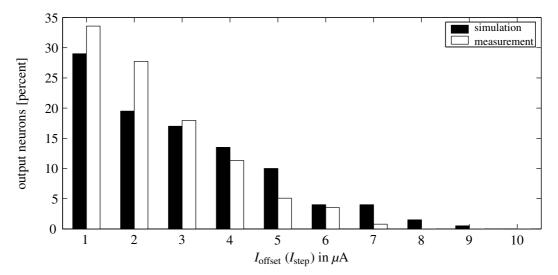

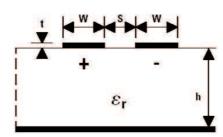

## 1.2.3 VLSI Implications

The most important implication of binary inputs is the major simplification they introduce to the VLSI design: in order to accumulate the postsynaptic activity only the sum of the active weights needs to be calculated, and not the sum of weights multiplied by the value of the respective inputs (multiply-accumulate). An analog summation, furthermore, has to deal only with additive offset mismatches, whereas an analog multiplication is affected by offsets in the inputs and additionally a mismatch in the gain [115]. A purely additive offset can easily be compensated for since it is constant, i.e., it is independent of the input data and the weight value. This is not true for the gain and offset errors in a multiplication which affects training performance even in on-chip setups [49, 142]. Circuit precautions may be introduced to compensate these effects, but those increase the circuit complexity [33, 9, 59].

The choice for McCulloch-Pitts neurons reduces the evaluation of the summed activity to a comparison task. If the activity is above a certain threshold, the neuron will fire, otherwise it remains silent. There are different ways to efficiently implement a summation, two possibilities are: First, if the weights are represented by charges, a capacitor can be used to accumulate them. Second, if currents are used to encode the weights, a property ensured by Kirchhoff's current law can be exploited: Currents that flow through the same node sum up. The thresholding, finally, is easily implemented by a voltage comparator.

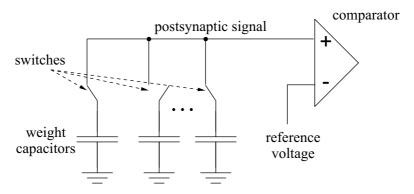

**Charge-Sharing Neuron** Implementing the network evaluation by the charge-sharing approach is straight forward and can be realized quite efficiently. Fig. 1.6 illustrates the schematic setup. First of all, a capacitor in each synapse is required to store its weight. It can be easily programmed by charging the capacitor to a certain potential. If several of these weight capacitors<sup>4</sup> are connected, charges will flow between them until a common potential is achieved, i.e., the weight

<sup>&</sup>lt;sup>4</sup>Since it is not desirable to recharge the weight capacitors after each leveling, one additional capacitor per synapse should be used.

averaging is performed. In order to have positive and negative weights, an intermediate potential is chosen to be zero.

Figure 1.6: Operation principle of a charge-sharing neuron.

If the same potential is used as the reference voltage at the voltage comparator in the neuron, the activity evaluation can be realized in two phases: First, the postsynaptic line gets precharged to the threshold voltage which essentially resets the neuron. In a second phase, the weight capacitors in the individual synapses are connected to the postsynaptic line in accordance to the input. In effect, the potential of the postsynaptic line will yield:

$$V_i^{\text{postsyn}} = \frac{\sum_{j=1}^N I_j Q_j}{\sum_{j=1}^N I_j C_j}, \quad I \in \{0, 1\},$$

(1.6)

where N is the number of inputs per neuron,  $C_i$  are the capacitances of the weight capacitors, and  $Q_i$  the amount of charge stored on each. Finally, if the postsynaptic voltage is higher than the reference voltage, the neuron fires.

In practice, Eq. 1.6 exhibits the drawback that the influence of one weight is dependent on the number of simultaneously activated synapses. While in the ideal case it can be shown that this does not cause a premature flip in sign, already the effect on the amplitude may lead to inaccurate fire decisions. In case there are precalculated weights to be used, e.g. for variable network resources, two neurons each are combined to alternately switch which keeps the total capacitance constant.

This neuron principle has been tested in an initial mixed-signal prototype ASIC [186]. It not only allowed to evaluate the performance of this neuron implementation but also made it possible to test the network block architecture. Details on the realization of this concept are given in Sec. 1.3.

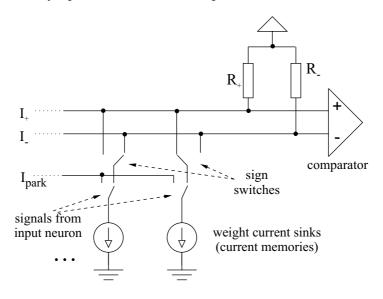

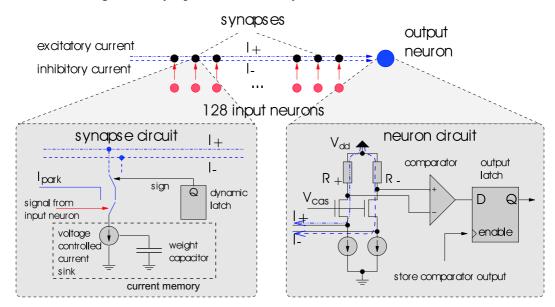

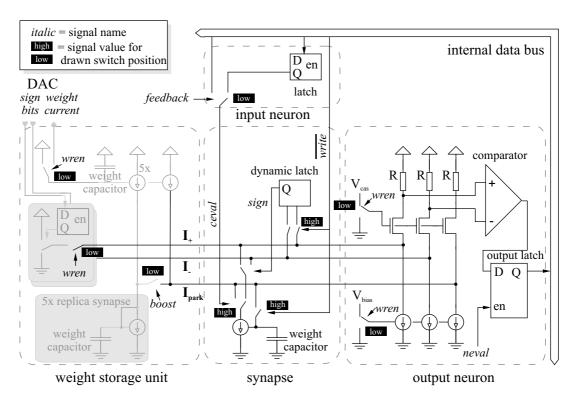

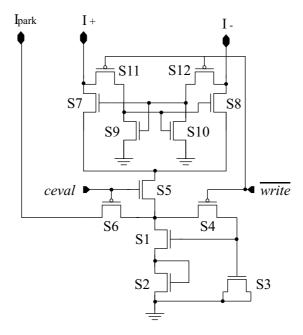

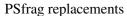

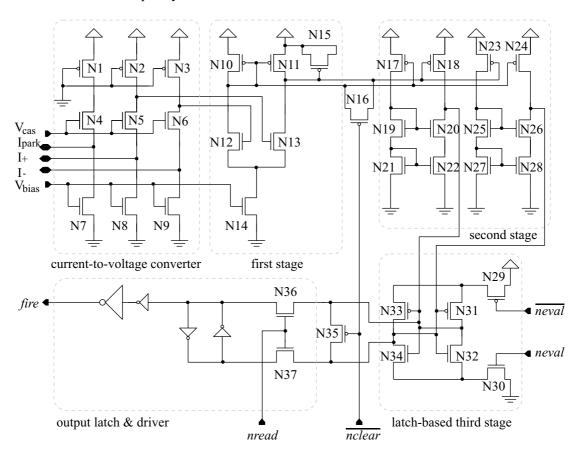

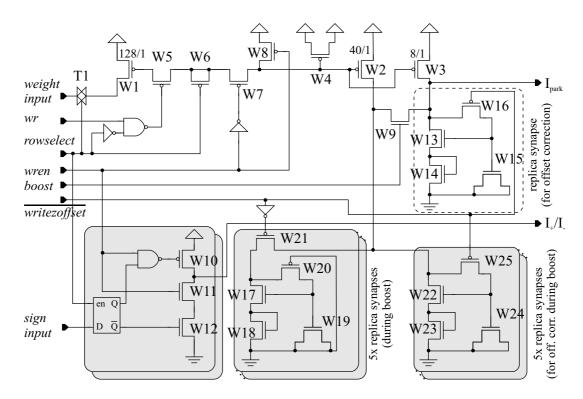

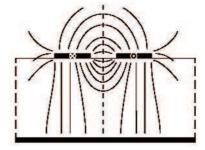

**Current-Sum Neuron** In contrast to the charge-sharing neuron, the current-summation can be easily combined with a differential approach, which makes the zero reference obsolete and eliminates one noise source. Fig. 1.7 shows a simplified visualization of the setup realized in a second mixed-signal ANN ASIC [187]; it is described in detail in Ch. 3. The amplitude of the weight is stored in an analog current memory and the sign is provided by a switch directing the current to one of the postsynaptic branches,  $I_+$  or  $I_-$ . The currents on the postsynaptic branches are the sum of the active (as determined by the on-signal from the input neuron) synapses of respective sign:

$$I_{\text{neg}} = \sum_{i}^{N} |\omega_i| I_{\text{syn}}^{\text{max}}, \quad \forall i \in \{j | -1 \le \omega_j < 0\},$$

$$\tag{1.7}$$

$$I_{\text{pos}} = \sum_{i=1}^{N} |\omega_{i}| I_{\text{syn}}^{\text{max}}, \quad \forall i \in \{j | 1 \ge \omega_{j} > 0\},$$

$$(1.8)$$

with  $I_{\text{syn}}^{\text{max}}$  being the maximum current sunk by a synapse. An inactive synapse, triggered by an inactive input neuron, gets connected to a third current line,  $I_{\text{park}}$ . This minimizes potential changes in the output node of a synapse and accelerates the operation.

Figure 1.7: Operation principle of a differential current-sum neuron.

Before the comparison in the output neuron is performed, the excitatory and inhibitory currents are converted to voltages by resistors  $(R_+ \text{ and } R_-)$  according to Ohm's law:

$$U_{\text{neg}} = V_{\text{dd}} - R \cdot I_{\text{neg}}, \tag{1.9}$$

$$U_{\text{pos}} = V_{\text{dd}} - R \cdot I_{\text{pos}}. \tag{1.10}$$

Weight Storage In order to perform a parallel evaluation of the postsynaptic activity, the weights need to be present in each synapse. And since the major feature of neural networks is their learning capability, the weight values need to be variable (during training) yet viable (during recall). Different approaches therefore have been utilized in earlier neurochips, such as classical EEPROM-based weight storage [91] or advanced versions that extend the underlying floating-gate principles to allow simultaneous weight update and read out in order to allow incremental online learning [47]. This way, the latter approach tries to account for longer programming times and higher programming voltages (above  $V_{\rm dd}$ ) by only doing small weight changes. Even though a successful adaptation to standard CMOS technology [48] has been shown, usually dedicated non-standard CMOS processes are required that accommodate the required voltages.

In a setup where the learning algorithm is not to be implemented on-chip and rapid weight changes may occur in training (e.g. evolutionary chip-in-the loop training), it seems more sensible to employ a split weight storage: In the synapses an easily changeable working copy of the weight is provided which allows a sufficiently long recall phase but eventually needs to be refreshed. The ANN ASIC based on the charge-sharing neuron showed that the leakage currents of the utilized CMOS process technology are such that capacitances in the 50-100 fF range, which can be efficiently realized by gate capacitances and allow small synapses, are viable enough to be trained and finally used during recall phase [186]. Nevertheless, after a certain time the weights need to be refreshed. This can be realized by introducing an digital weight storage as to provide a fast and long-lasting memory, and digital-to-analog converters can be used to accordingly load the weight capacitors in the synapses.

While in the ANN ASIC based on charge-sharing the long-term weight storage as well as the DA conversion was done off-chip, the on-die integration of the DACs has advantages: it reduces the interface of the overall chip to digital communication which allows a fast and noise-resistant operation. The current-sum prototype therefore integrates the DAC on-die, yet the digital long term storage there as well remains off-chip; this simplifies the exploration of different training strategies which can more easily be varied in software or programmable logic.

The reduced susceptibility to noise of the on-chip generation of the weights increases the analog representation of the weights. The reporting in literature on the minimal weight resolution requirements for training neural networks differs and ranges from 2 to 16 bits [142], whereby a 16 bit accuracy is only necessary for classical back-propagation training [11]. Especially, chip-in-the-loop strategies which only operate networks in forward propagation require much less accuracy and content themselves with as few as 2 to 3 bits [58, 56]. Compared to numerical tasks in computer algebra even the 16 bits for back-propagation are low requirements; according to Vittoz [218] perception-type tasks, which neural networks are dedicated for, seem to have an inherently lower requirement for precision than tasks aiming at the perfect restoration of information.

For some common benchmark problems theoretical worst-case limits for the minimal weight resolution have been calculated independently of the training strategy. These results show that they are problem-specific, yet well below 16 bits; using less rigid bounds the examination yields 8 to 12 required bits and less if a small percentage of misclassifications is allowed [7].

## 1.3 Realization

### 1.3.1 A Neural Network Experiment

The various hardware and software components presented in this thesis may be understood as parts of a *neural network experiment*, the main goal of which is the research on hardware adaptations of neural architectures by providing a framework that allows to readily exchange the substrate, the training and operation strategy, as well as the application.

This thesis will give a detailed description of the realization of the presented network paradigm and the experimental framework to assess its capabilities. Throughout the design and construction, a major emphasis has been put on interchangeability and reusability of its components. This modularity will allow the extension of the experiment to other network paradigms: A neurochip aiming at an efficient silicon adaptation of integrate and fire neurons [185] is currently under development and will initially be operated using the infrastructure presented here.

Design and construction of this neural network experiment are a collaborate effort with current and former researchers of the Electronic Vision(s) group contributing ASIC design, PCB development, logic programming, software engineering, and testing. The names of the contributing researchers are given where appropriate.

Within the scope of this thesis, hardware and software components have been developed which contribute to the experiment. This comprises the participation in the design of the ANN ASIC presented in Ch. 3, the development of peripheral electronics detailed in Ch. 4, and contributions to a modular software framework described in Sec. 4.3. Similarly, a substantial effort was dedicated to the testing of the individual components and their integration to an overall system in order to accomplish several operational platforms for different neural network experiments<sup>5</sup>.

<sup>&</sup>lt;sup>5</sup>Due to the modularity of the experimental framework it is even possible to use the infrastructure for other mixed-signal applications. Other projects of the Electronic Vision(s) group, such as research on evolvable hardware [117] or development of optical sensors with logarithmic response [28] employ some of the infrastructure.

1.3. Realization

Lastly, the experimental application pursued in this thesis adapts a recent strategy to operate recurrent neural networks to a hardware implementation. Since this paradigm does not rely on stable states, it promises some inherent robustness to substrate variations and faults throughout operation. It is explained in detail in Ch. 2 and experimental results are presented in Ch. 5.

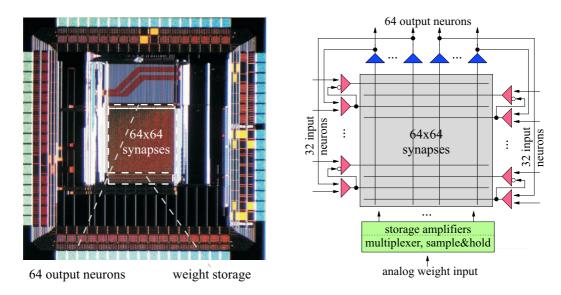

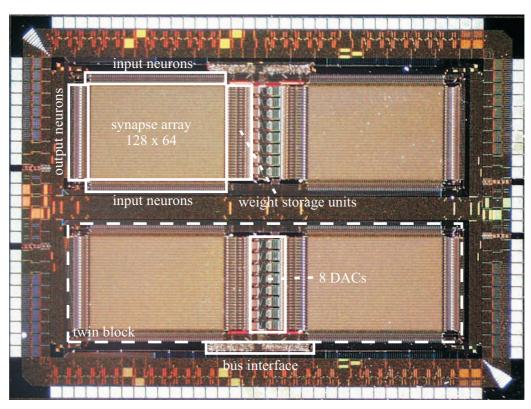

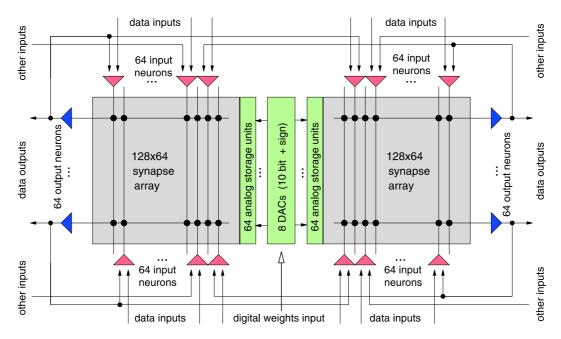

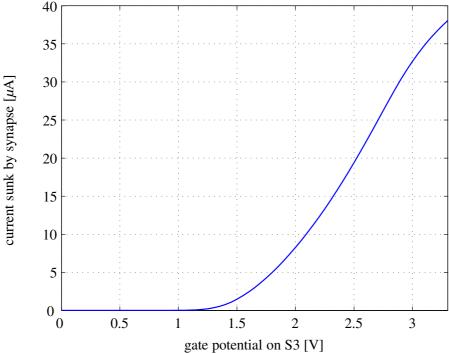

#### 1.3.2 ANN ASICs

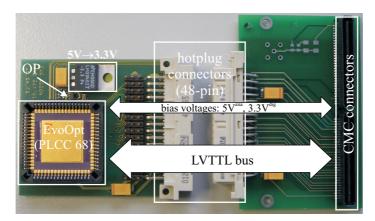

Central to the neural network experiment are the ANN ASICs. Currently, two different mixed-signal ANN ASICs can be accommodated: One that implements a single network block of charge-sharing neurons, the *EvoOpt*<sup>6</sup> chip [186]. And a second which implements four interconnected network blocks based on the current-summing neuron [187, 184]. The latter—the *HAGEN*<sup>7</sup> prototype—is explained in detail in Ch. 3. Tab. 1.2 lists the features of both ANN ASICs.

| Property                                            | EvoOpt Prototype                    | HAGEN Prototype                 |

|-----------------------------------------------------|-------------------------------------|---------------------------------|

| process features                                    | $0.35 \mu m$ , 1 poly, 3 metal      | $0.35 \mu m$ , 1 poly, 3 metal  |

| die/core size [mm <sup>2</sup> ]                    | $2.5\times2.5$ / $2\times2$         | $4.1 \times 3 / 3.6 \times 2.5$ |

| synapse array/network block size [mm <sup>2</sup> ] | $0.7{\times}0.7$ / $0.7{\times}0.9$ | $1.1 \times 0.8 / 1.5 \times 1$ |

| synapse size $[\mu m^2]$                            | $10\times10$                        | $8.7 \times 12$                 |

| blocks/output neurons/synapses                      | 1/64/4096                           | 4/256/32768                     |

| supply voltage                                      | 3.3 V                               | 3.3 V                           |

| max. network frequency $f_{net}$                    | 100 MHz                             | 50 MHz                          |

| CPS                                                 | 0.4 Teracps max.                    | 1.64 Teracps max.               |

| CUPS                                                | 16 Megaweigths/s max.               | 400 Megaweigths/s max.          |

| weight resolution                                   | up to 6 bit (measured)              | 10 bit (nominal) + sign         |

**Table 1.2:** Nominal specifications of the ANN ASIC prototypes.

Both ASICs are prototypes; the implementation therefore is primarily limited by the available silicon area. This area limit directly translates into a limitation in the number of available synapses. Nevertheless, the fundamental assumptions of the proposed network concept can be evaluated.

The EvoOpt prototype for example allowed to assess the following aspects:

- implementation of an efficient synapse for the use with charge-sharing neurons [186];

- trainability of multi-layer and/or recurrent topologies with chip-in-the-loop strategies in the presence of hardware non-idealities [88];

- variable network resources trained by an evolutionary algorithm [193].

Since both ASICs are designed in the same process technology, the feasibility of capacitive weight storage shown in the EvoOpt design allowed to optimize the synapses for the current-sum implementation.

A major goal of the current-sum approach, finally, was to realize a better accuracy while maintaining the successful concept of network blocks. With the HAGEN prototype therefore the following has been achieved in addition:

<sup>&</sup>lt;sup>6</sup>The name EvoOpt is derived from *Evolution* and *Optical*; it resembles the fact that indeed two designs were submitted on the same die: a neural network suited for the training by evolutionary algorithms and a optical sensor test design.

<sup>&</sup>lt;sup>7</sup>The acronym stands for Heidelberg Analog Evolvable Neural network; an obsolete internal name of the ASIC is *ANNA* (Analog Neural Network Array); yet it is reminiscent in some internal naming schemes.

- implementation of an efficient and accurate synapse for use with current-summing neurons [187];

- evaluation of the mixed-mode operation principle for a fast and accurate weight storage and activity evaluation by the neurons [187];

- demonstration of low power operation with a high-speed interface;

- evaluation of the mixed-signal approach for encapsulating the analog VLSI into blocks while only using digital signals for the communication with the outside [184];

- competitive trainability on standard classification benchmarks by specialized evolutionary algorithms [89, 87];

- feasibility of scalable networks by interconnecting several network blocks [87, 195, 57];

- variable network resources using precalculated weights [194].

### 1.3.3 Experimental Framework

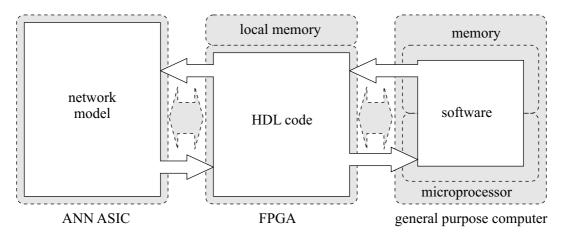

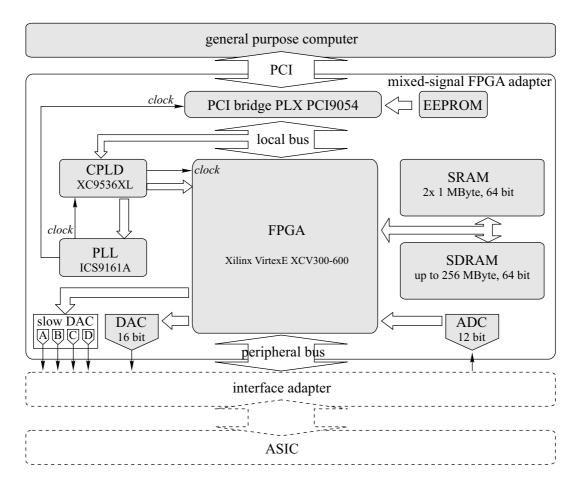

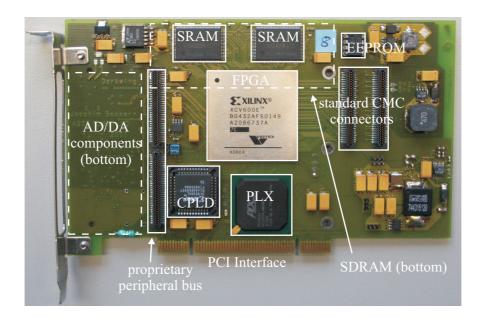

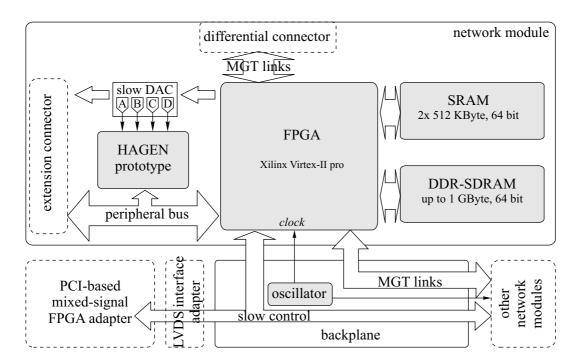

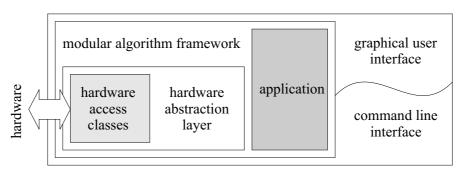

A first realization of the experimental framework is based on a custom-built PCI-based adapter that hosts a programmable logic in form of a *field programmable gate array* (FPGA), a local memory, and circuits for mixed-signal testing [18]. This adapter allows to interface various ANN ASICs and a general purpose computer (see Fig. 1.8); these components comprise the *substrate level*.

**Figure 1.8:** Components of the experimental framework and a possible realization. The actual implementation (gray boxes) and their physical interaction is mostly independent from the functionality (white boxes).

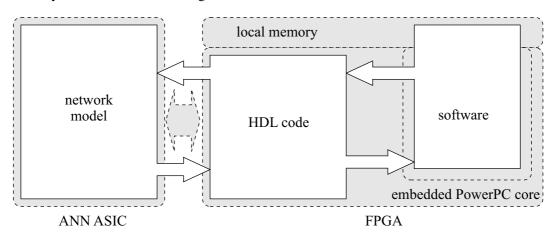

Not only on the substrate level but also on the *functional level*, a modular approach has been followed: The neural network has an abstract representation given by its modular network blocks, that allows the configuration, training, and operation the network independent of its actual hardware realization. This separation is realized in software as well as in the programming of the reconfigurable logic (as given by the code in a *hardware description language* (HDL)). In software, a *hardware abstraction layer* is responsible for accommodating the interaction with a hardware organized in the network block structure. Similarly, the HDL code is separated into an entity operating the respective ANN ASIC and other entities serving a general purpose such as interfacing

1.3. Realization 21

the software, operating a local memory, or logic supporting the algorithmics of the software. The realization of the substrates as well as details on the functional implementation are given in Ch. 4.

Due to its modular implementation, the experimental framework allows a rapid extension and migration of functionality between substrates. Examples for this are the following achievements:

- While the work on the experimental framework started with the development of the charge-sharing based ANN ASIC, the successor ASIC HAGEN was integrated by essentially only changing the chip-specific parts of the peripheral electronics, the interfacing by the programmable logic, and the low-level chip-representation in the software. The PCI-based FPGA adapter as well as major parts of the software, especially the training strategies, are reused. Details are described in Ch. 4. The integration of any future type of ANN ASIC which is organized in the same block structure will be similarly straight forward.

- Certain parts of an evolutionary training strategy have been migrated from the software to the HDL code to accelerate the training [189]. More details can be found in Sec. 4.2.3.

- A HDL entity that augments the network model implemented by the HAGEN prototype to emulate spike-based computing has been tested in software [31] before it was realized in the programmable logic. More details can be found in Sec. 4.2.3.

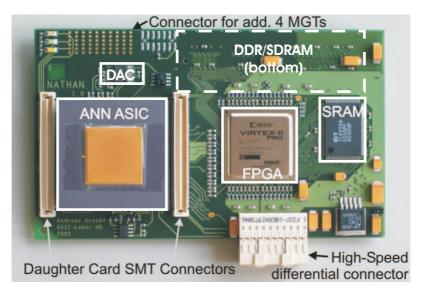

- A distributed system has been developed that integrates all substrates of the experimental

framework, i.e., the ANN ASIC, programmable logic, and a microprocessor, on a single

PCB [77]. Even though the electrical implementation changed, a new type of FPGA has

been used, and the general purpose Intel-based PC has been replaced by an embedded PowerPC core, most of the HDL code and the software is reused (c.f. Sec. 4.1.5). This advanced

implementation of the neural network experiment will be used to accommodate future ANN

ASICs, e.g. [185].

#### 1.3.4 Suitable Training Approaches

Essential to the operation of a neural network is the training: the functionality of a neural network is determined by adequately configured topologies and weights. Several lines of research are pursued that concern the feasibility of successful training in general, training strategies that are especially suited for the chosen network model, as well as training strategies that generate fault-tolerant architectures. To accommodate these different approaches, a modular software platform has been developed that allows a flexible yet efficient operation of the hardware and thus forms the basis for the operation of the neural network experiment. An introduction and description with emphasis on technical details is given in Sec. 4.3; a complementary description of other parts of the software can be found in [86].

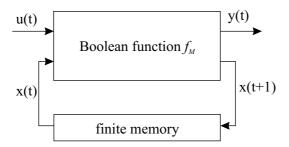

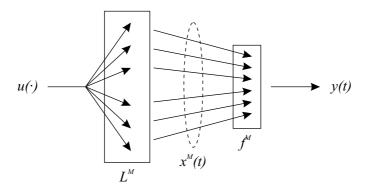

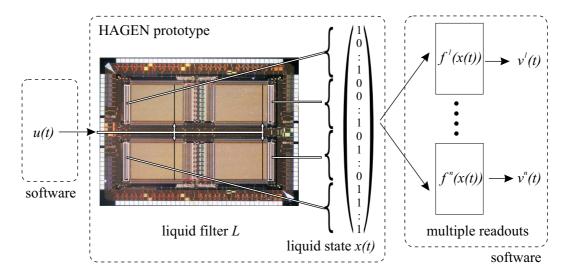

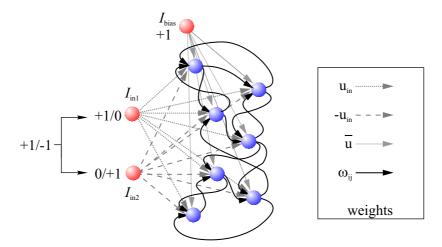

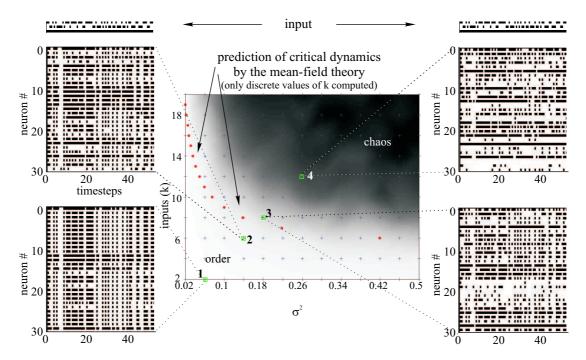

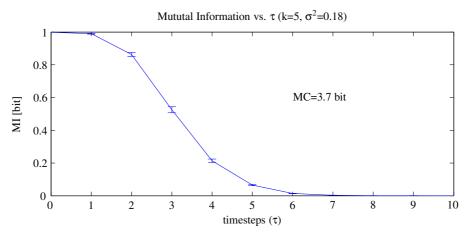

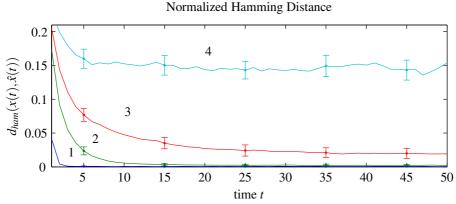

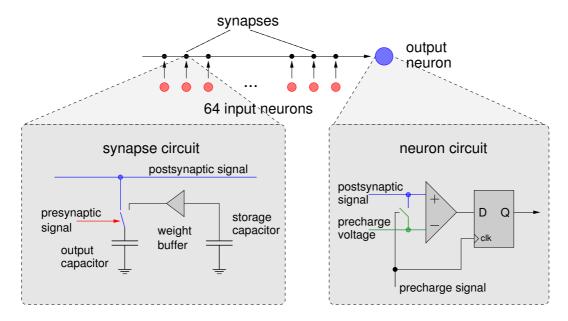

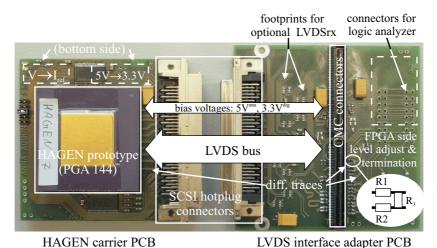

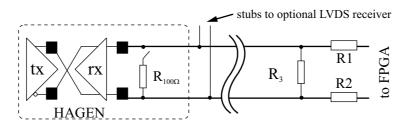

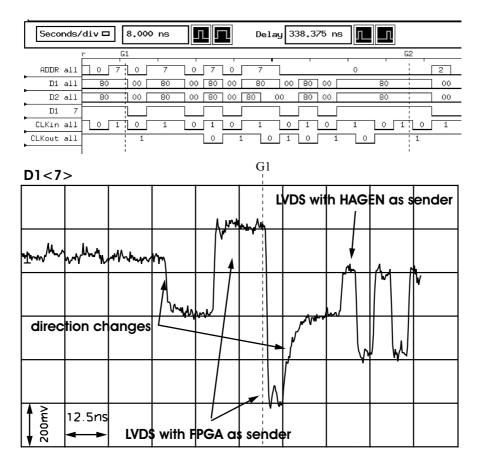

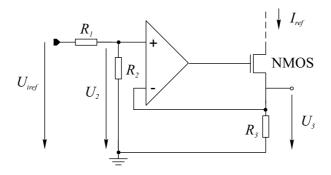

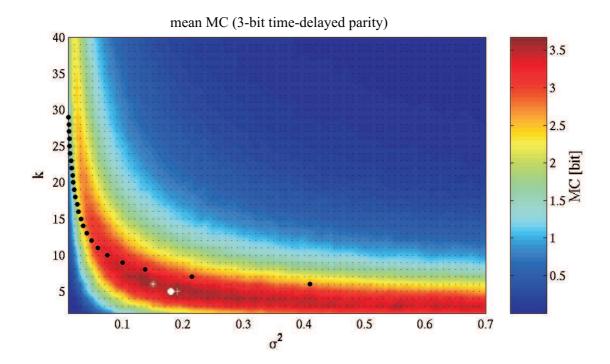

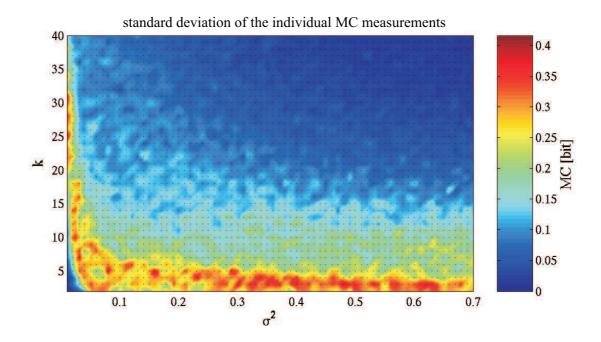

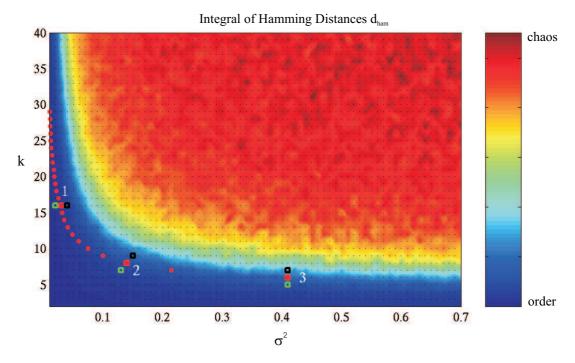

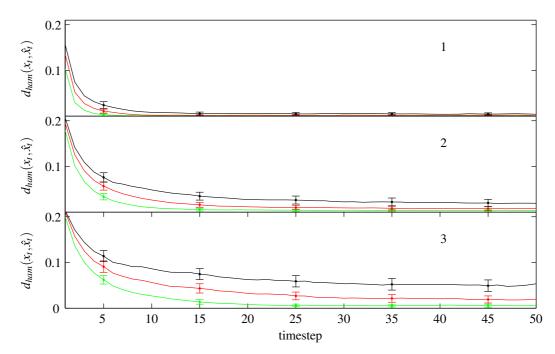

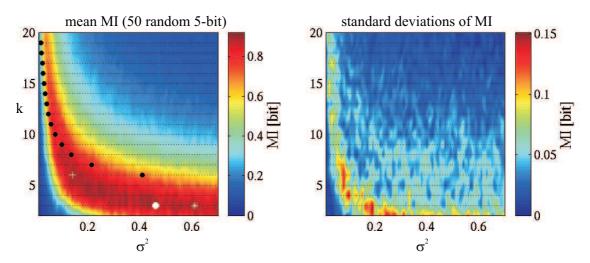

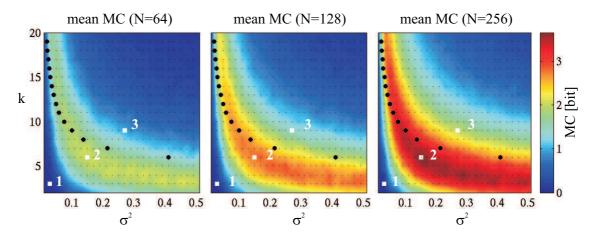

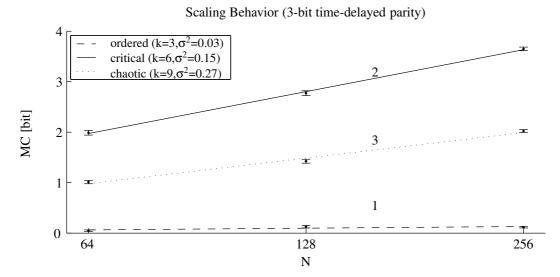

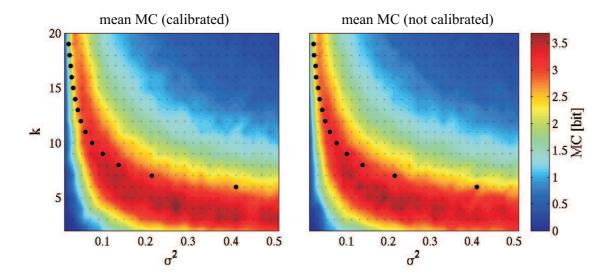

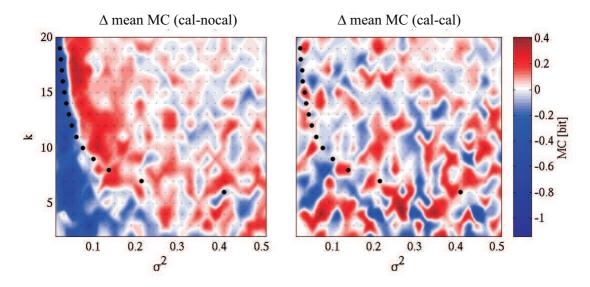

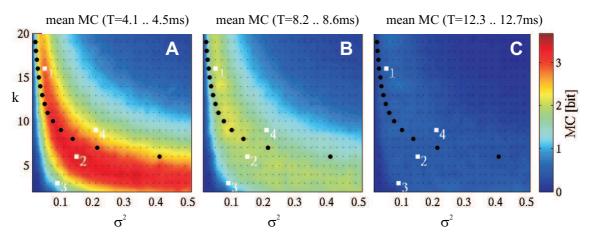

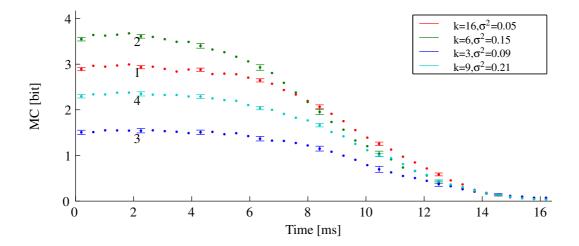

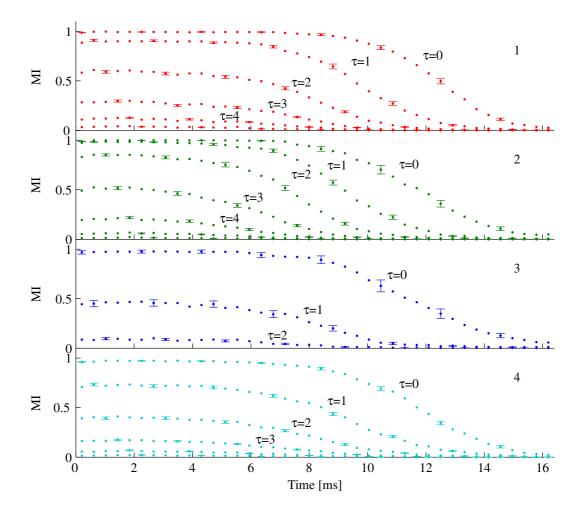

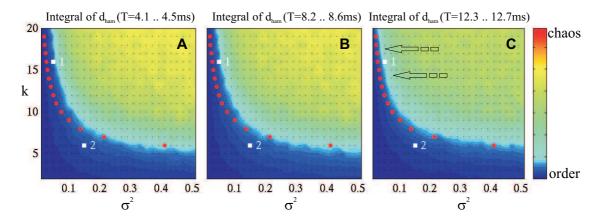

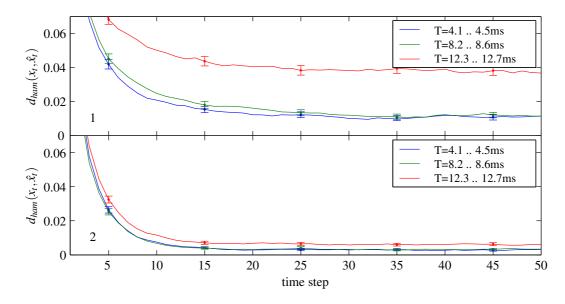

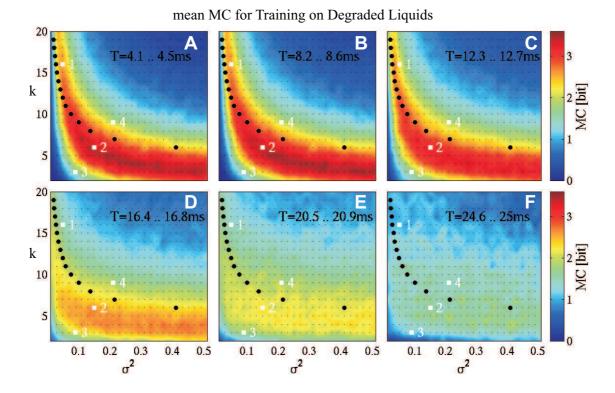

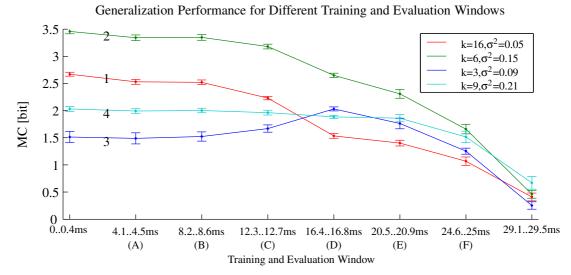

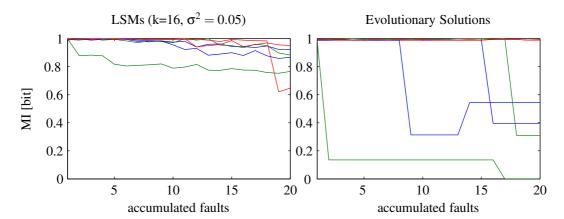

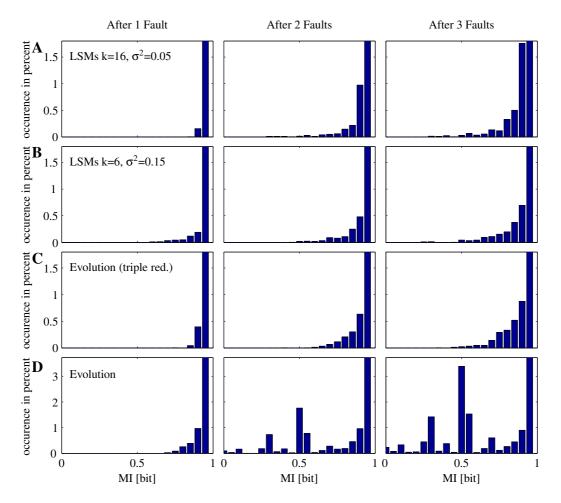

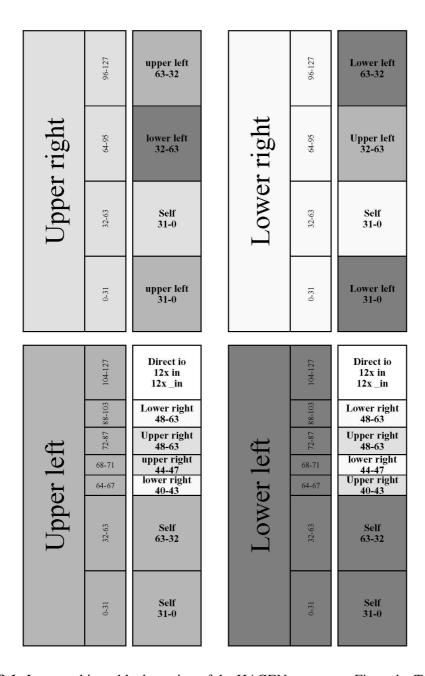

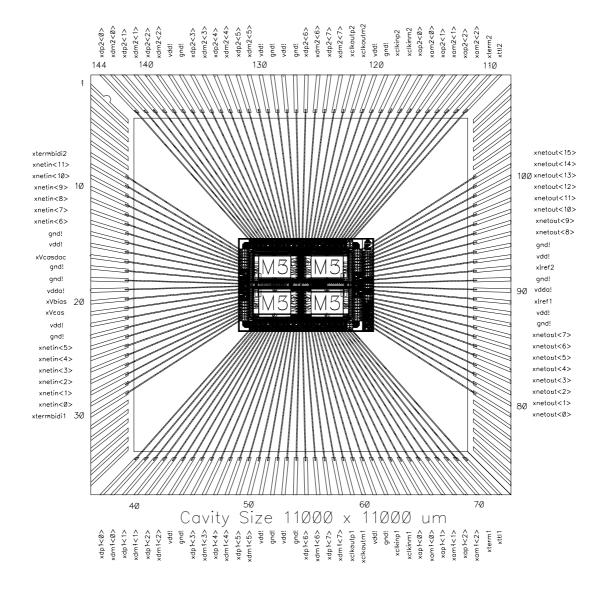

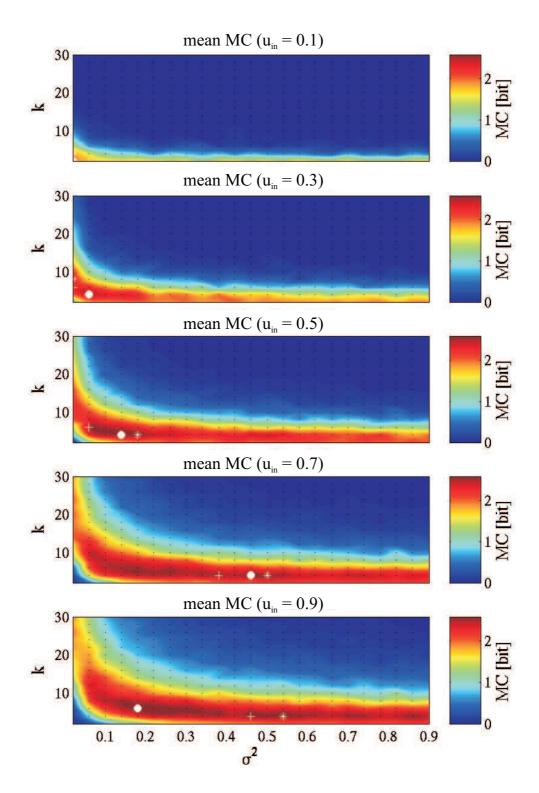

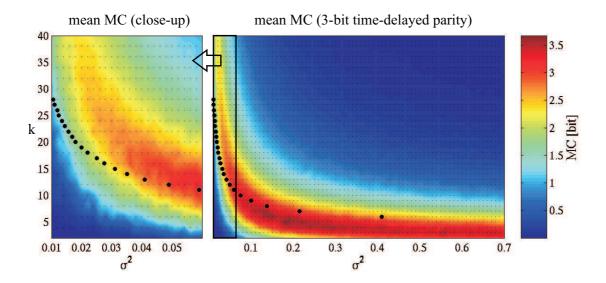

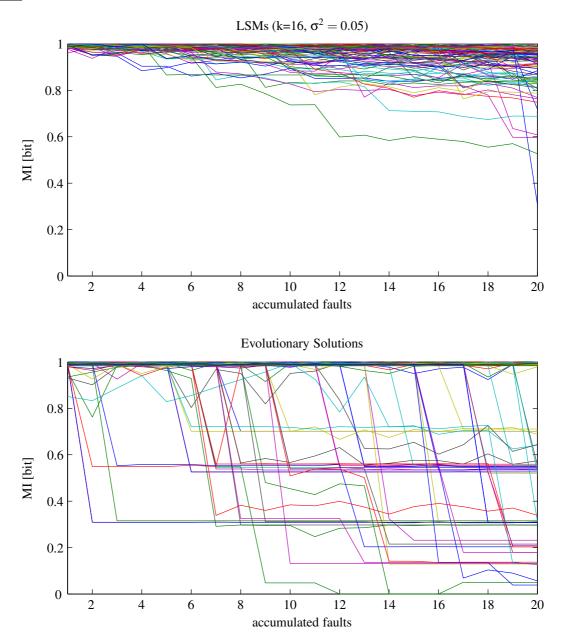

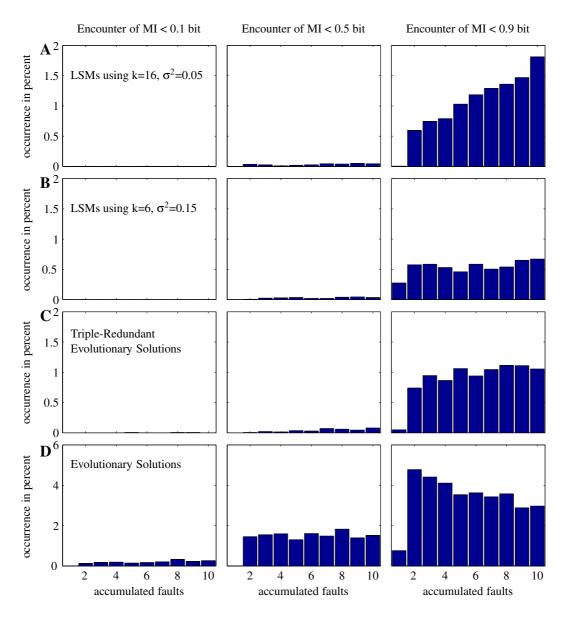

The lines of research that are currently pursued comprise the following: