## RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

KIRCHHOFF-INSTITUT FÜR PHYSIK

## Fakultät für Physik und Astronomie

Ruprecht-Karls-Universität Heidelberg

Diplomarbeit

im Studiengang Physik

vorgelegt von

Joachim Philipp Becker

aus Hanau/Main

2001

### Ein FPGA-basiertes Testsystem

für gemischt analog/digitale ASICs.

Die Diplomarbeit wurde von Joachim Philipp Becker ausgeführt

am Kirchhoff Institut für Physik

unter der Betreuung von

Herrn Prof. Dr. Karlheinz Meier

#### Ein FPGA-basiertes Testsystem für gemischt analog/digitale ASICs:

Der Test rekonfigurierbarer gemischt analog/digitaler ASICs erfordert neben der digitalen Konfiguration auch eine Evaluierung der analogen Fähigkeiten des Chips. Aufgabe eines Testsystems ist die Aufnahme des ASICs und Bereitstellung von Versorgungsspannungen, digitaler Kommunikation und analogen Testmustern. Außerdem müssen die analogen Ausgaben des ASICs gemessen und verarbeitet werden. Zur Ausnutzung der Geschwindigkeit des ASICs ist es notwendig, auch komplexe Testabfolgen wie genetische Algorithmen vollständig in Hardware zu implementieren, wozu eine ausreichend große programmierbare Logik bereitgestellt werden muss.

Die vorliegende Arbeit zeigt eine Spezifizierung der Anforderungen, die Entwicklung einer entsprechenden Schaltung und die Implementierung als Leiterplatte. Zur schnellen Rechneranbindung ist die Platine als PCI-Karte ausgeführt und beinhaltet als Kernstück einen FPGA. Im Rahmen dieser Arbeit wurde das Testsystem in Betrieb genommen und Teile der Programmierung erstellt.

#### An FPGA-based testbench for mixed-signal ASICs:

The test of reconfigurable mixed-signal ASICs demands digital configuration in addition to the evaluation of the analogue abilities of a chip. The task of the testsystem is to affiliate the ASIC and provide power, digital communication and analogue test patterns. Besides that, analogue outputs of the ASIC have to be measured and processed. In order to exploit the speed of the ASIC, it is necessary to completely implement complex testsequences like evolutionary algorithms in the hardware, for which a sufficiently large programmable logic has to be provided.

The present thesis describes the specifications demanded, the development of an appropriate circuit and implementation as printed circuit board. For fast communication with a computer, the hardware is designed as an PCI-board and contains an FPGA as its central unit. As a result of this work the board was commissioned and parts of the software were implemented.

# Inhaltsverzeichnis

| 1 | Mo                              | tivatio          | n                                        | 1  |  |  |

|---|---------------------------------|------------------|------------------------------------------|----|--|--|

| 2 | Übersicht über das Gesamtsystem |                  |                                          |    |  |  |

|   | 2.1                             | Hardw            | vare                                     | 5  |  |  |

|   | 2.2                             | Softwa           | are                                      | 7  |  |  |

|   |                                 | 2.2.1            | Hardwarebeschreibung                     | 7  |  |  |

|   |                                 | 2.2.2            | PC-Software                              | 8  |  |  |

| 3 | Har                             | dware            |                                          | 9  |  |  |

|   | 3.1                             | Mecha            | anische Spezifikationen der Karte        | 9  |  |  |

|   |                                 | 3.1.1            | Format der Platine                       | 9  |  |  |

|   |                                 | 3.1.2            | Anordnung der Bauteile                   | 9  |  |  |

|   |                                 | 3.1.3            | Lagenaufbau                              | 12 |  |  |

|   | 3.2                             | Baute            | il-Gruppen zur Initialisierung der Karte | 13 |  |  |

|   |                                 | 3.2.1            | Lokale Taktgenerierung (PLL)             | 13 |  |  |

|   |                                 | 3.2.2            | CPLD                                     | 13 |  |  |

|   |                                 | 3.2.3            | PLX                                      | 15 |  |  |

|   |                                 | 3.2.4            | EEPROM                                   | 16 |  |  |

|   | 3.3                             | FPGA             |                                          |    |  |  |

|   |                                 | 3.3.1            | IO-Aufteilung                            | 18 |  |  |

|   |                                 | 3.3.2            | FPGA-Taktung                             | 19 |  |  |

|   |                                 | 3.3.3            | LVDS/LVTTL-Bänke                         | 21 |  |  |

|   | 3.4                             | Lokaler Speicher |                                          |    |  |  |

|   |                                 | 3.4.1            | Statisches (S-) RAM                      | 26 |  |  |

|   |                                 | 3.4.2            | Synchron dynamisches (SD-) RAM           | 28 |  |  |

|   |                                 | 3.4.3            | Gemeinsame Benutzung der Busleitungen    | 29 |  |  |

|   |                                 | Stecker          | 30                                       |    |  |  |

|   |                                 | 3.5.1            | CMC-Standard konforme Stecker            | 31 |  |  |

|              |              | 3.5.2                                 | CMC-Stecker mit selbst definierter Belegung                        | 32  |  |  |

|--------------|--------------|---------------------------------------|--------------------------------------------------------------------|-----|--|--|

|              | 3.6          | 3.6 Bauteile zur analogen Ein/Ausgabe |                                                                    |     |  |  |

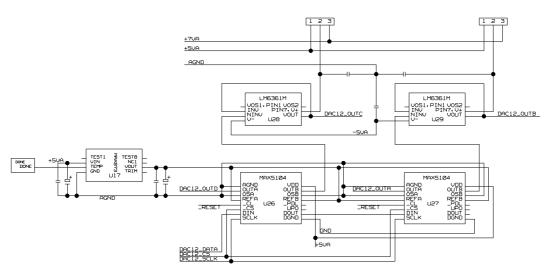

|              |              | 3.6.1                                 | 12 Bit-DACs                                                        | 33  |  |  |

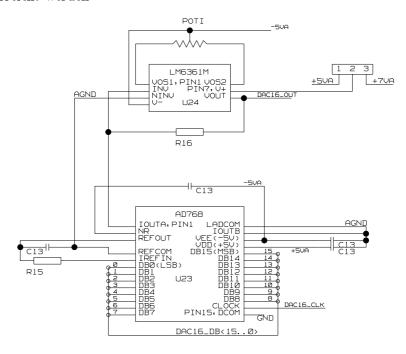

|              |              | 3.6.2                                 | 16 Bit-DAC                                                         | 35  |  |  |

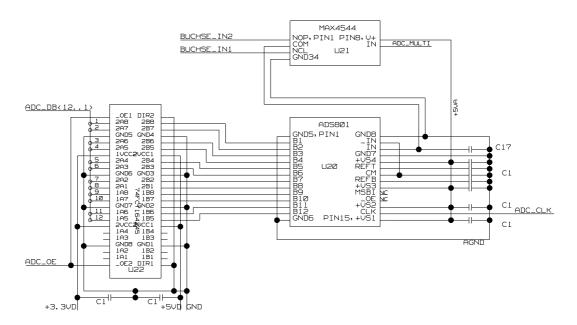

|              |              | 3.6.3                                 | ADC                                                                | 36  |  |  |

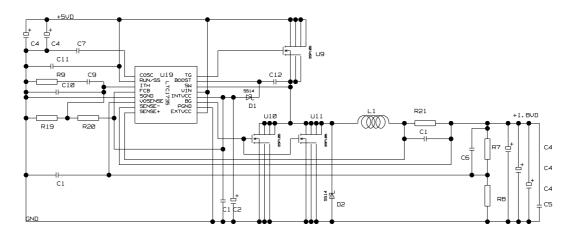

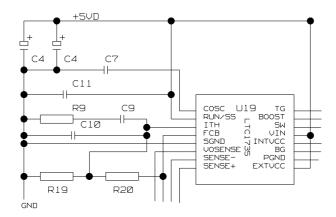

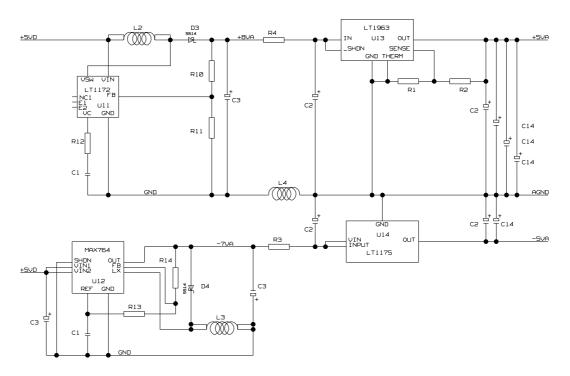

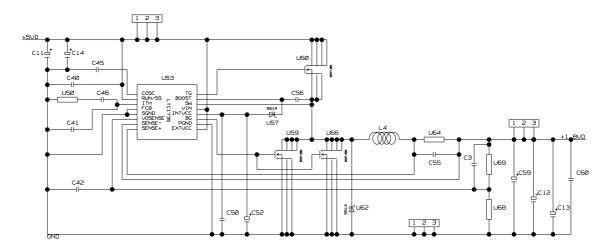

|              | 3.7          | Spann                                 | ungsversorgung                                                     | 38  |  |  |

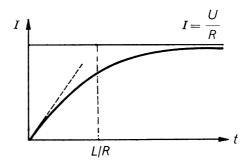

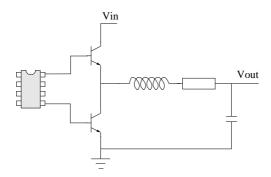

|              |              | 3.7.1                                 | Grundlagen                                                         | 38  |  |  |

|              |              | 3.7.2                                 | Spannungsversorgung der LVDS-Treiber des FPGAs $\ \ldots \ \ldots$ | 39  |  |  |

|              |              | 3.7.3                                 | Spannungsversorgung des FPGAs                                      | 39  |  |  |

|              |              | 3.7.4                                 | Filterung für den Analogteil                                       | 49  |  |  |

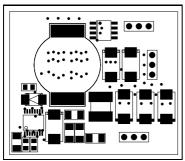

|              | 3.8          | Bestüc                                | ckung und Inbetriebnahme                                           | 52  |  |  |

|              |              | 3.8.1                                 | Reihenfolge der Bestückung                                         | 52  |  |  |

|              |              | 3.8.2                                 | Korrekturen                                                        | 52  |  |  |

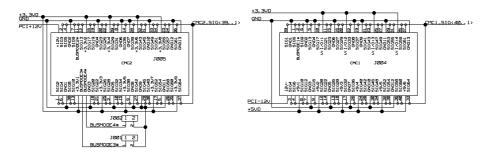

|              | 3.9          | Aufna                                 | hme der zu testenden ASICs                                         | 54  |  |  |

|              |              | 3.9.1                                 | Gosalyn                                                            | 54  |  |  |

| 4            | Messungen 56 |                                       |                                                                    |     |  |  |

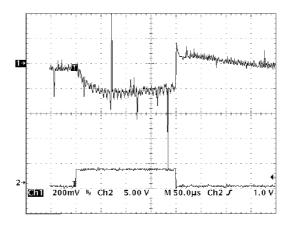

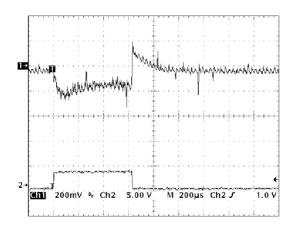

|              | 4.1          | Netzte                                | ile                                                                | 56  |  |  |

|              | 4.2          | Taktsi                                | gnal                                                               | 57  |  |  |

|              | 4.3          | LVDS                                  |                                                                    | 57  |  |  |

|              | 4.4          | 16 Bit-                               | DAC                                                                | 60  |  |  |

| 5            | Soft         | ware                                  |                                                                    | 62  |  |  |

|              | 5.1          | Allgen                                | neiner-FPGA Code für Darkwing                                      | 62  |  |  |

|              | 5.2          | FPGA                                  | -Code zur Ansteuerung des FPTAs                                    | 65  |  |  |

|              | 5.3          | Simula                                | ationsmodell für den FPTA                                          | 67  |  |  |

|              |              | 5.3.1                                 | Interne Signale und Speicher                                       | 68  |  |  |

|              |              | 5.3.2                                 | Grundfunktionen für die Kommunikation                              | 69  |  |  |

| 6            | Zus          | ammeı                                 | nfassung                                                           | 71  |  |  |

| A            | EEI          | PROM                                  | für PLX                                                            | i   |  |  |

| В            | VH           | DL Mo                                 | odell für den FPTA                                                 | ii  |  |  |

| $\mathbf{C}$ | Schaltplan   |                                       |                                                                    |     |  |  |

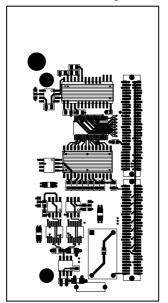

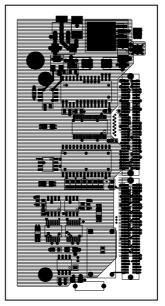

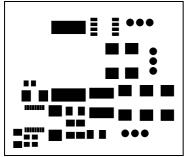

| D            | Bes          | tückun                                | ng                                                                 | xii |  |  |

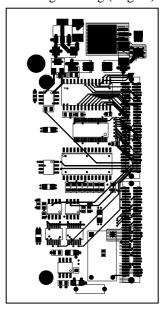

| $\mathbf{E}$ | Lagenpläne             | xix  |

|--------------|------------------------|------|

| $\mathbf{F}$ | Megavolt               | xxix |

| $\mathbf{G}$ | Tochterplatine Gosalyn | xxxi |

### Kapitel 1

## Motivation

Zur Bewältigung von Aufgaben der digitalen Signalverarbeitung geht die Lösungsstrategie in den meisten Fällen von einer möglichst allgemeinen, programmierbaren Hardware aus und reduziert das Problem auf die Definition und Optimierung eines geeigneten Lösungsalgorithmus in Software. Durch die immer weiter steigende Leistungsfähigkeit moderner Computer und die gute Beherrschbarkeit der digitalen Methoden ist auch die analoge Signalverarbeitung oft darauf reduziert, das analoge Signal möglichst bald zu digitalisieren, um es dann mit den Mitteln der digitalen Signalverarbeitung zu verarbeiten und gegebenenfalls wieder in ein analoges Ausgangssignal umzuwandeln. Dies gilt auch für die Simulation analoger Schaltkreise, wo auf die allgemeinen numerischen Methoden zurück gegriffen wird, um das Verhalten einer Schaltung zu berechnen.

Bei manchen Problemen verspricht man sich jedoch Geschwindigkeitsgewinne, falls es gelingt, möglichst viele Bestandteile des Lösungsansatzes direkt in Hardware zu implementieren. Dabei soll ein Lösungsalgorithmus nicht in Software geschrieben und dann auf einer allgemeinen Recheneinheit ausgeführt werden, sondern eine auf das Problem spezialisierte Hardware zum Einsatz kommen. Im digitalen Bereich gibt es einige Beispiele für dieses Vorgehen, wie mathematische Co-Prozessoren, Vektor-Recheneinheiten moderner Prozessoren oder spezialisierte Grafik-Chips für 3D-Effekte. Weil analoge Signale oft der digitalen Weiterverarbeitung zugeführt werden, gibt es aber kaum spezialisierte Hardware, die komplizierte analoge Signalverarbeitung leistet. Die Entwicklung analoger Bausteine für spezielle Anwendungen ist Objekt aktueller Forschung. Dabei erfolgt die Verwirklichung der Schaltung als Mikrochip, indem ASIC¹-Prototypen hergestellt werden.

Die Arbeitsgruppe electronic vision(s) am Kirchhoff Institut für Physik entwickelt konfigurierbare gemischt analog/digitale ASICs für Anwendungen in der Bildverarbeitung. Es sind dies beispielsweise Kamerachips [DIVICHI], Chips zur Kantendetektion auf Bildern [EDDA], analoge neuronale Netzwerke [EVOOPT], ANNA oder programmierbare Transistor-Felder [FPTA].

<sup>&</sup>lt;sup>1</sup>application specific integrated circuit

Der FPTA<sup>2</sup>-Chip soll zur künstlichen Evolution analoger Schaltungen benutzt werden. Kernstück ist ein Feld aus 256 Transistoren, die zu einer quadratischen Matrix zusammengefügt sind. Transistoren bilden die Grundeinheit analoger Schaltungen, da aus ihnen alle anderen Bauteile wie Kondensatoren, Widerstände, Operationsverstärker, etc. aufgebaut werden können. Die Kennlinie jeder Transistorzelle im FPTA ist konfigurierbar, und durch programmierbare Vernetzung der Zellen untereinander können Schaltkreise implementiert werden.

Die Suche nach neuen Schaltungen oder das Trainieren eines neuronalen Netzwerkes durch künstliche Evolution beruhen auf dem Prinzip von Selektion und Mutation. Dabei wird ein Problem definiert, das eine Schaltung bewältigen soll, indem zu einer Anzahl von Eingabevektoren die gewünschten Ausgaben des ASICs angegeben werden. Das Testsystem kann eine Konfiguration in den ASIC laden, alle Eingabevektoren anlegen und die Reaktion des ASICs mit dem vorgegebenen Ausgabewert vergleichen. Durch ein Bewertungsschema erhält man ein Maß für die Funktionsfähigkeit einer Konfiguration (Fitness) und kann beliebige Konfigurationen testen, bis ein befriedigendes Ergebnis erzielt wird. Da die Menge der sinnvollen Konfigurationen gegenüber dem gesamten Konfigurationsraum sehr klein ist, scheint eine zufällige Suche aussichtslos. Daher geht ein genetischer Algorithmus von einer Population von Individuen aus, also einer Menge von zufällig gewählten Konfigurationen, bewertet deren Funktionalität und nimmt dann gezielte Veränderungen vor. Individuen, die eine schlechte Fitness aufweisen, werden verworfen (Selektion), während die Population aufgefüllt wird mit Konfigurationen, die von den besser bewerteten Individuen abgeleitet sind. Mechanismen dafür sind die zufällige Veränderung (Mutation) und die Vermischung (Crossover) von Konfigurationen. So wird eine neue Generation gewonnen, die wiederum getestet wird, und auf diese Weise wird der Algorithmus über viele Generationen hinweg ausgeführt, um eine Verbesserung der Funktionalität bis hin zu einer Konfiguration zu erreichen, die das Problem löst.

Um die erste Inbetriebnahme eines konfigurierbaren gemischt analog/digitalen ASICs und später den Ablauf eines genetischen Algorithmus zu ermöglichen, muss ein Testsystem die folgenden Aufgaben bewältigen:

**Spannungsversorgung des Chips:** Die Bereitstellung der Versorgungsspannung des zu testenden ASICs ist grundlegend. Diese sollte gegen Überlast gesichert sein und einer Zerstörung des ASICs vorbeugen. Es sollte aber auch die Möglichkeit bestehen, mehrere regelbare Gleichspannungen bereitzustellen, die für getrennte Versorgung von IO<sup>3</sup>-Treibern, Spannungsreferenzen, o.ä. benutzt werden können.

**Digitale Kommunikation:** Ein ASIC wird über digitale Leitungen angesprochen, wobei ein digitaler Bus mit einer Breite von mehreren Byte ohne Probleme realisierbar sein sollte. Da es verschiedene Standards von Signallogiken gibt, soll es möglich sein, die Kommunikation an die unterschiedlichen Anforderungen anzupassen. Die hohen Geschwindigkeiten von bis zu 400 MHz implizieren die Vorab-Programmierung der digitalen Kommunikation und das Ablaufen dieser Programme auf einer schnellen Mikroelektronik.

<sup>&</sup>lt;sup>2</sup> field programmable transistor array

<sup>&</sup>lt;sup>3</sup>input/output

Analoge Stimuli: Um den Analogteil eines ASICs zu testen, müssen schnelle analoge Signale erzeugt werden, die jede beliebige Amplitude im zulässigen Wertebereich annehmen können. Eine freie Programmierung verschiedener Signalformen und Testmuster sollte leicht umzusetzen sein.

Analoge Messwerte aufnehmen: Zur Überprüfung des Analogverhaltens zählt auch die Aufnahme von analogen Spannungsmesswerten, die der ASIC unter Umständen in Abhängigkeit von analogen oder digitalen Eingaben ausgibt. Diese Messwerte müssen parallel zur Abarbeitung der digitalen Kommunikation und Erzeugung der analogen Stimuli aufgezeichnet werden und nach dem programmierten Test für eine Auswertung zur Verfügung stehen.

Rückkopplung: Für den Betrieb konfigurierbarer Hardware wie neuronalen Netzwerken oder programmierbaren Transistorfeldern ist es wesentlich, dass aktuelle Messungen Einfluss auf die Konfiguration bzw. Stimuli haben können und somit eine Rückkopplung implementiert werden kann. Dies kann im einfachsten Falle bedeuten, dass Eingaben für den Chip sich ändern, wenn ein bestimmtes analoges Verhalten festgestellt wurde bis hin zum komplizierten Fall, dass nach Auswertung bestimmter Messwerte eine komplette Neukonfiguration des Chips durchgeführt werden soll.

In der vorliegenden Arbeit werden die Entwicklung und Implementierung eines solchen Testsystems beschrieben, das es ermöglicht, die genannten Aufgaben zu erfüllen und komplexe digitale und analoge Kommunikation auf Chip-Ebene mit einer flexiblen Programmierung und komfortabler Benutzerschnittstelle zu vereinigen. Die grundlegenden Strukturen des Testaufbaus wurden bereits in [Bli00] für den Test des EDDA-Chips benutzt und haben bewiesen, dass sie den Anforderungen gerecht werden. Es gilt nun, das Konzept zu verallgemeinern und so eine Plattform für unterschiedlichste Testaufbauten bereit zu stellen. Außerdem wird den Neuentwicklungen auf dem Gebiet der elektronische Bauteile Rechnung getragen und modernste Technologien verwendet, um das bestehende Konzept umzusetzen.

### Kapitel 2

# Übersicht über das Gesamtsystem

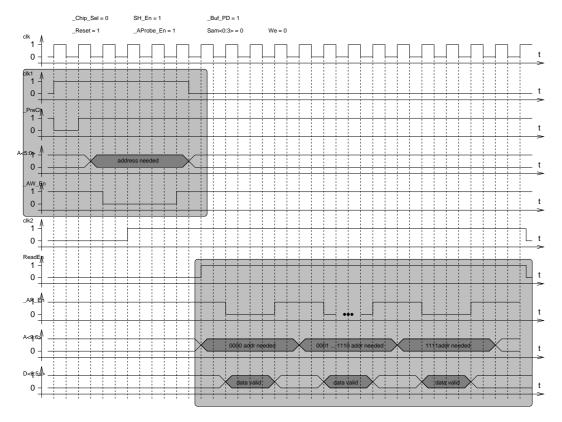

Kernstück des Testsystems ist eine  $\mathrm{PCI^1} ext{-}\mathrm{Karte}$ , die die Schnittstelle zwischen einer PC-Software und dem zu testenden ASIC darstellt. Die Ansteuerung des Chips wird beschrieben durch Timing-Diagramme, die meist auf einer synchronen digitalen Kommunikation aufbauen. Das heißt, ein Systemtakt stellt die Zeitbasis dar, wobei jeweils zu einer steigenden Flanke des Signals ein neuer Zustand auf der Datenleitung Gültigkeit erlangt. Da diese Kommunikation mit Taktfrequenzen im Bereich von 20 bis 100 MHz (LVTTL²) oder sogar bis zu 400 MHz (LVDS³) betrieben wird, wird ein Experiment nicht mehr voll durch direkte Interaktion eines Menschen, sondern durch eine programmierbare Hardware gesteuert. Ein wesentliches Merkmal dieses Verfahrens ist, dass die Programmabläufe mit der Geschwindigkeit der Hardware ausgeführt und Reaktionen in Echtzeit ( $10^{-8}\,s$ ) ausgewertet werden, während die Programmierung des Verhaltens und Eingriffe in das Experiment auf einer wesentlich größeren Zeitskala erfolgen (Tage).

Dies wird verwirklicht durch die Verwendung eines FPGAs<sup>4</sup>, der auf der einen Seite als Hardwareimplementation einer Gatterlogik die Kommunikation auf Chip-Ebene bewerkstelligen kann, auf der anderen Seite aber seine Konfiguration aus einer anspruchsvollen Entwicklungsumgebung erhält. Der Programmablauf wird in einer Hochsprache<sup>5</sup> programmiert, compiliert und auf die Hardware des FPGAs abgebildet. Im Entwicklungsstadium ist es außerdem möglich, Simulationsmodelle der zu testenden Chips zu erstellen und die Kommunikation zwischen FPGA und ASIC zu simulieren. Mit den heute verfügbaren Mitteln können die Anbindung an den PCI-Bus, Ansteuerung von Analog/Digitalwandlern, Verwaltung von Speicherbausteinen und komplizierte Testabläufe wie z.B. genetische Algorithmen programmiert, simuliert und auf einem FPGA dargestellt werden. Wegen der Rekonfigurierbarkeit des FPGAs können mit ein und derselben Hardware durch reine Programmentwicklung die unterschiedlichsten Experimente durchgeführt werden. Mit der Einbindung der Hardware in einen PC können die diversen Testaufbauten auch auf die Ressourcen

<sup>&</sup>lt;sup>1</sup>peripheral component interconnect

<sup>&</sup>lt;sup>2</sup>low voltage transistor-transistor logic

<sup>&</sup>lt;sup>3</sup>low voltage differential signaling

<sup>&</sup>lt;sup>4</sup>field programmable gate array

<sup>&</sup>lt;sup>5</sup>Hardwarebeschreibungssprache

2.1. HARDWARE 5

des Rechners zugreifen. Dies ermöglicht die Beeinflussung des laufenden Experimentes über Eingabemasken auf dem Bildschirm, direkte Visualisierung von Messungen und Statusanzeigen, Speicherung von Experimenten auf Festplatte, Vereinigung von mehreren Testsystemen in einem Computer oder sogar Zugriff auf die Hardware über ein Netzwerk.

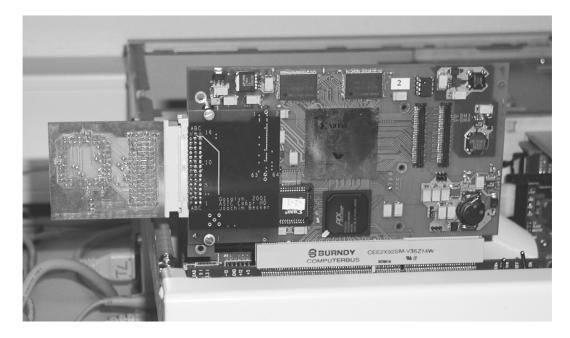

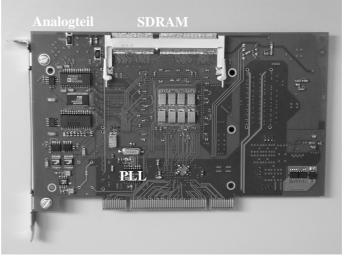

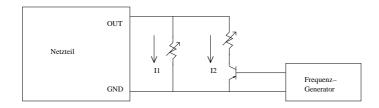

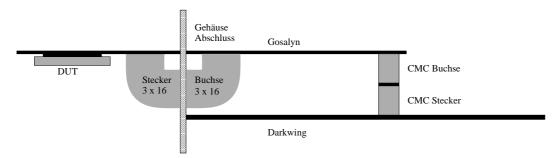

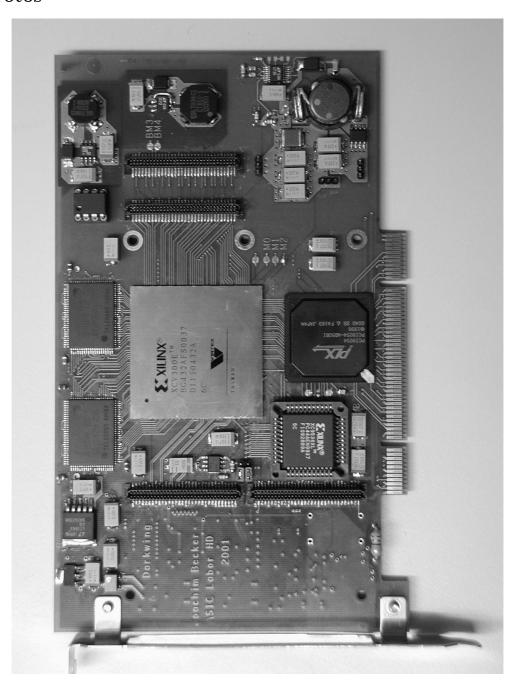

Abbildung 2.1: Aufbau eines Experiments

Abbildung 2.1 zeigt ein Foto eines aufgebauten Experiments. Die PCI-Karte mit dem Projektnamen Darkwing ist mit dem Computer (PC) verbunden, wobei sie hier auf einem PCI-Bus Extender aufgesteckt ist, um Messungen vorzunehmen und normalerweise in den geschlossenen Computer eingebaut ist. Auf der linken Seite der Karte befindet sich eine Adapterplatine (hier Gosalyn) die mit der Gehäuserückwand bündig abschließt und Anschlüsse für den externen Träger jedes individuellen ASICs bereitstellt. Hier zu sehen ist die Unterseite der Trägerplatine für einen EVOOPT-Chip. Im folgenden sollen ein tieferer Einblick in die Funktionsweise des Gesamtsystems sowie eine vollständige Erläuterung aller notwendigen Bestandteile gegeben werden.

#### 2.1 Hardware

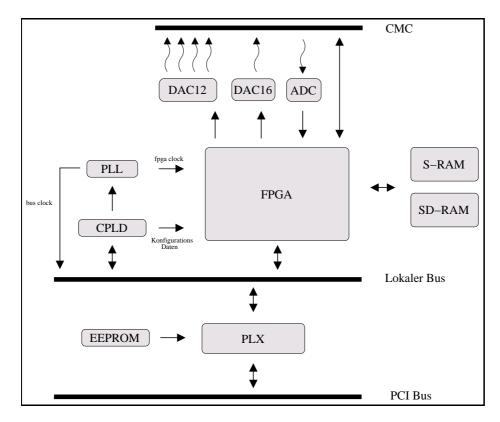

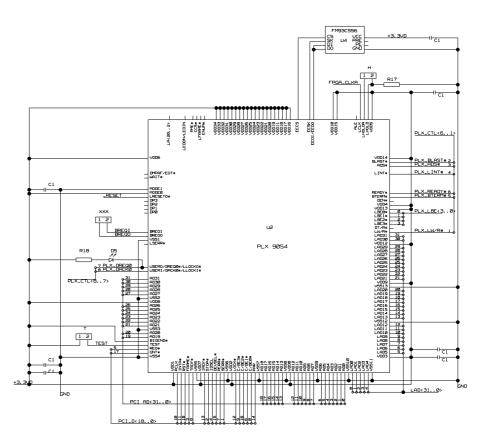

Eine schematische Sicht der Hauptkomponenten und Datenpfade zeigt Abbildung 2.2. Die Kommunikation zum PC findet auf dem PCI-Bus statt, an den viele verschiedene Karten in einem PC angeschlossen sind. Ein PCI-Masterchip vom Typ PCI9054 der Firma PLX übernimmt diese Kommunikation und stellt dann ausschließlich die Daten auf einem lokalen Bus auf Darkwing zur Verfügung, die an diese spezielle

Karte adressiert wurden [PLX9054]. Ein serielles  $\rm EEPROM^6$  dient zur dauerhaften Speicherung der Konfigurationsdaten, die bei jedem Systemstart ausgelesen werden.

Abbildung 2.2: Blockdiagramm der PCI-Karte

Auch der FPGA ist bei einem Systemstart nicht konfiguriert, und könnte eine Programmierung aus einem ROM lesen. Da es aber möglich sein soll, je nach Anwendung unterschiedliche Konfigurationen zu laden und den FPGA auch während des Betriebs zu rekonfigurieren, wird eine Programmierung über den PCI-Bus ermöglicht. Dabei empfängt der FPGA die Daten nicht selber, sondern ein fest programmierter Logikbaustein (CPLD<sup>7</sup>) setzt die Daten vom lokalen Bus auf das Initialisierungsprotokoll des FPGAs um. Eine weitere Aufgabe des CPLDs besteht in der Programmierung der PLL<sup>8</sup>, die zwei Taktsignale erzeugt. Dies sind die Zeitbasis für den lokalen Bus und eine zusätzliche Taktung für den FPGA.

Ist der FPGA initialisiert, so übernimmt er die zentrale Rolle auf der Karte. Er kommuniziert über den lokalen Bus und den PLX-Chip mit dem PC und kann alternativ zwei fest eingebaute S-RAM<sup>9</sup> Bausteine oder ein SD-RAM<sup>10</sup> Modul als lokalen Speicher ansteuern. Außerdem bedient er die analogen Bauteile. Dies sind

<sup>&</sup>lt;sup>6</sup>electrically erasable programmable read only memory

<sup>&</sup>lt;sup>7</sup>complex programmable logic device

<sup>&</sup>lt;sup>8</sup>phase locked loop

<sup>&</sup>lt;sup>9</sup>static random access memory

<sup>&</sup>lt;sup>10</sup>synchronous dynamic random access memory

2.2. SOFTWARE 7

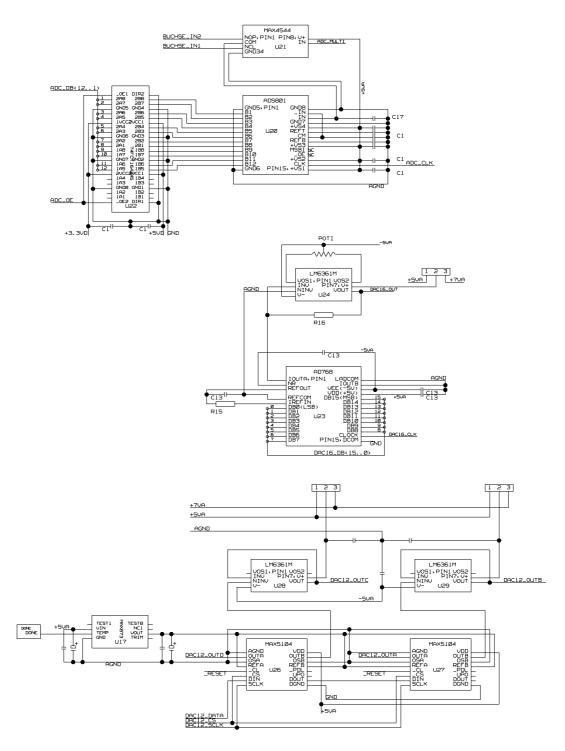

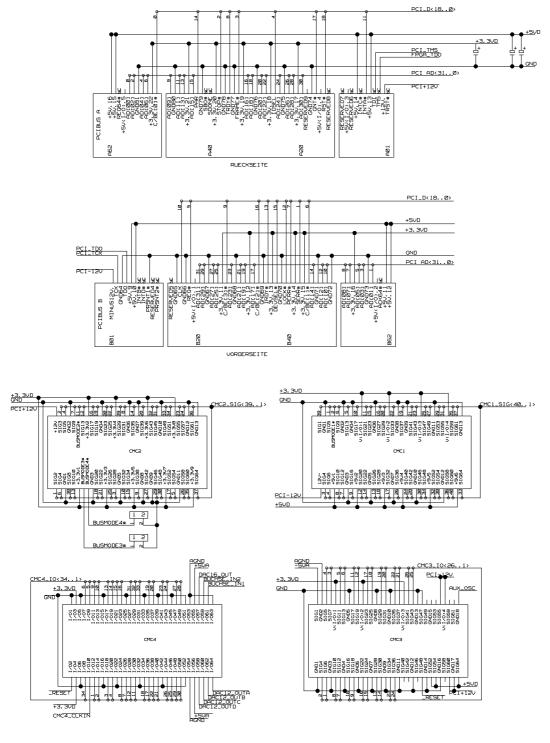

im Einzelnen vier DACs<sup>11</sup> mit einer Auflösung von 12 Bit zur Bereitstellung von Gleichspannungen und je ein DAC mit 16 Bit und ein ADC<sup>12</sup> mit 12 Bit Auflösung. Diese Bausteine werden benutzt, um das Analogverhalten des angeschlossenen ASICs (auch DUT<sup>13</sup>) zu testen. Weiterhin stellt der FPGA digitale Leitungen zum ASIC bereit. Alle Verbindungen nach außen liegen auf Steckern, damit jeder ASIC mit einer individuellen Tochterplatine auf die PCI-Karte aufgesteckt werden kann. Diese Tochterplatine kann kompatibel zum CMC<sup>14</sup>-Standard sein, und daher sind die Kontakte als CMC-Stecker ausgeführt.

#### 2.2 Software

Der Begriff Software wird in diesem Zusammenhang unterteilt in Hardware beschreibende Programme, die die Konfiguration des FPGAs darstellen und auf der Karte ablaufen, und PC-Software im eigentlichen Sinne, die als Benutzeroberfläche des Experimentes erscheint und auf einem PC-Betriebssystem aufsetzt, das die benutzte Hardware ansteuert.

#### 2.2.1 Hardwarebeschreibung

Um eine FPGA-Konfiguration zu erstellen, beginnt man mit der Entwicklung eines Quellcodes in einer Hardware beschreibenden Sprache (HDL<sup>15</sup>), wie zum Beispiel VHDL<sup>16</sup>. Diese Sprachen unterscheiden sich im Aufbau wesentlich von anderen Hochsprachen durch hierarchische Strukturen und Variablentypen, die Logik auf Bauteilebene repräsentieren können, womit der späteren Instantiierung des Codes in Hardware Rechnung getragen wird. Es kann die Verhaltensbeschreibung eines Bausteins programmiert werden, die durch Synthese auf Operatoren boolscher Algebra abgebildet wird [VHDL]. Die Hochsprache wird also in Gatterlogik übersetzt und an die Technologie des jeweiligen FPGAs angepasst. Daraus wird ein Bitstrom erstellt, der eine Konfiguration des FPGAs ermöglicht.

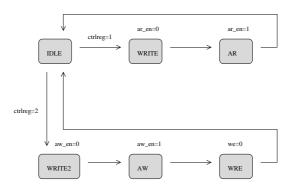

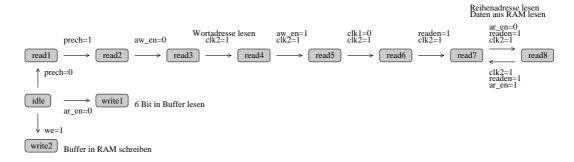

Ein weiteres Merkmal von HDLs ist die Parallelität, das heißt, dass alle Anweisungen in einem Block gleichzeitig ausgeführt werden. Eine Serialisierung muss manuell durch endliche Automaten, so genannte *state machines*, erzwungen werden, die synchron zum Taktsignal ihre Zustände ändern. Durch Verzweigungen in den entsprechenden Flussdiagrammen können die Timing-Diagramme, die zur Kommunikation mit anderen Bauteilen eingehalten werden müssen, abgebildet werden.

Mehrere solche Automaten laufen unter Umständen unabhängig voneinander gleichzeitig auf einem FPGA ab und übernehmen Teilaufgaben, die zusammengesetzt die gesamte Funktionalität des Chips ergeben. Für das vorliegende Testsystem gibt es einen umfangreichen Quellcode, der in die folgenden Bereiche unterteilt ist:

<sup>&</sup>lt;sup>11</sup>digital analog converter

<sup>&</sup>lt;sup>12</sup>analog digital converter

<sup>&</sup>lt;sup>13</sup>device under test

$<sup>^{14}</sup>$ common mezzanine card

<sup>&</sup>lt;sup>15</sup>hardware description language

<sup>&</sup>lt;sup>16</sup>very high speed integrated circuit - hardware description language

- Interne Register im FPGA

- Kommunikation mit dem lokalen Bus

- Ansteuerung des RAMs

- Ansteuerung der analogen Komponenten

- Kommunikation mit dem zu testenden Chip

Dementsprechend ist auch die feste Programmierung des CPLDs in einer HDL verfasst und wird als Bitkonfiguration in den nicht flüchtigen Speicherzellen des Bausteins hinterlegt. Der CPLD beinhaltet eine *state machine*, die die Konfiguration des FPGAs und der PLL leistet.

#### 2.2.2 PC-Software

Der Datenaustausch zwischen PC und FPGA findet in Form von Registerzugriffen statt. Im HDL-Code sind Register definiert, die Daten halten und durch eine entsprechende state machine über den lokalen Bus adressierbar sind, also beschrieben und ausgelesen werden können. Darin werden zum Beispiel Werte für die DACs und den ADC zwischengespeichert, und es gibt die Möglichkeit, über Registerzugriffe die state machines im FPGA zu beeinflussen und sie gezielte Kommandos ausführen zu lassen. Einer PCI-Karte ist ein gewisser Adressraum auf dem PCI-Bus zugeordnet, auf den durch einfache Lese- und Schreiboperationen zugegriffen werden kann, die durch einen Betriebssystem-Treiber [Bau01, Jungo] zur Verfügung gestellt werden. Diese Zugriffe werden über den PLX-Chip auf den lokalen Bus abgebildet, so dass eine PC-Software durch das Schreiben von Werten und Adressen auf dem PCI-Bus Zugriff auf die Register des FPGA hat.

Die PC-Software ist in einer beliebigen Hochsprache verfasst, und im vorliegenden Fall wird C++ benutzt, um Datenaustausch mit der Hardware und eine Benutzeroberfläche auf Windows oder Linux bereitzustellen. Eine Testsoftware besteht aus Eingabemasken für die spezifische Chip-Konfiguration, Bearbeitung von analogen Stimuli und Anzeige und Auswertung der analogen Messwerte. Experimente können auf Festplatte gespeichert werden und jederzeit wieder reproduziert werden. Weiterhin besteht die Möglichkeit, anspruchsvolle Rückkopplungen von Messungen auf Konfigurationen in Software zu schreiben, viele Konfigurationen im Speicher vorzuhalten und miteinander zu vergleichen. Somit ist dieses System die ideale Plattform für die Implementierung eines genetischen Algorithmus und die Anwendung künstlicher Evolution zur Gewinnung interessanter Konfigurationen.

## Kapitel 3

### Hardware

In der vorliegenden Arbeit liegt der Schwerpunkt auf der Implementierung der Hardware. Es ist eine Auswahl der Komponenten zu treffen und eine vollständige, funktionierende Schaltung zu entwerfen. Die funktionalen Elemente, die in der Übersicht Abbildung 2.2 genannt sind, bedingen durch ihre elektrischen Eigenschaften die Verwendung von Pegelkonvertern, Operationsverstärkern und passiven Bauelementen, die basierend auf den Datenblättern der entsprechenden Bauteile richtig dimensioniert werden müssen. Das folgende Kapitel wird auf diese Details der Hardware näher eingehen.

### 3.1 Mechanische Spezifikationen der Karte

Die Realisierung des Testsystems auf einer PCI-Karte bringt nicht nur die Vorteile der schnellen Rechneranbindung, sondern auch die der Bereitstellung von Versorgungsspannungen, Einbettung in ein Gehäuse und Belüftung. Allerdings erfordert sie auch die Einhaltung der Normen, wie sie in [PCI] definiert sind.

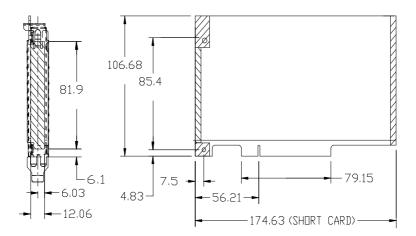

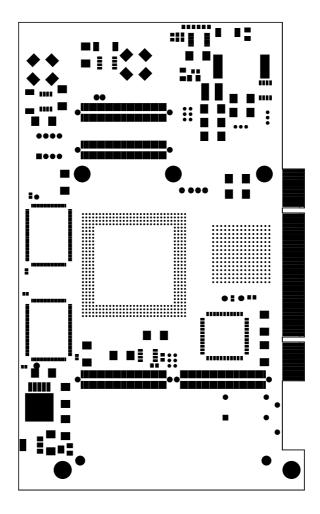

#### 3.1.1 Format der Platine

Abbildung 3.1 zeigt die mechanischen Abmessungen der Platine, die in einen Steckplatz auf der PC-Hauptplatine eingesteckt und mittels eines Kartenhalters am Gehäuse des PCs festgeschraubt wird. Die Dicke der Platine beträgt  $1.77 \pm 0.1\,\mathrm{mm}$ , und die erlaubten Bauhöhen sind  $14.48\,\mathrm{mm}$  auf der gezeigten Bestückungsseite und  $2.67\,\mathrm{mm}$  auf der Rückseite. Dies ermöglicht das Aufbringen einer Tochterplatine nach dem CMC-Standard auf der Oberseite, wie in 3.1.2 beschrieben.

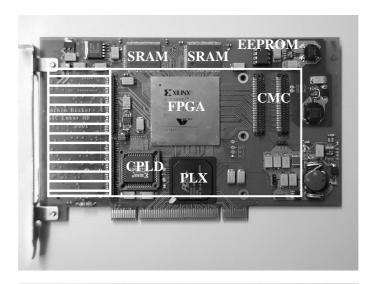

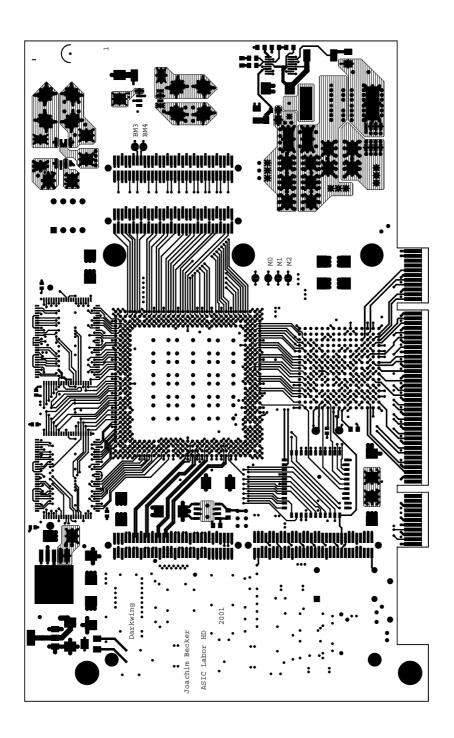

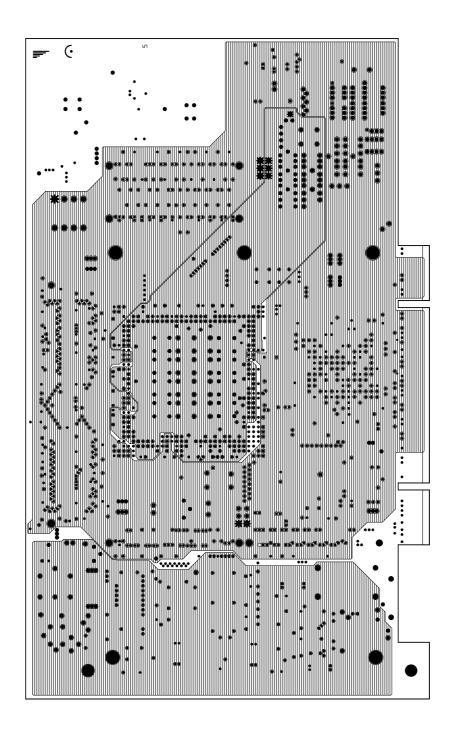

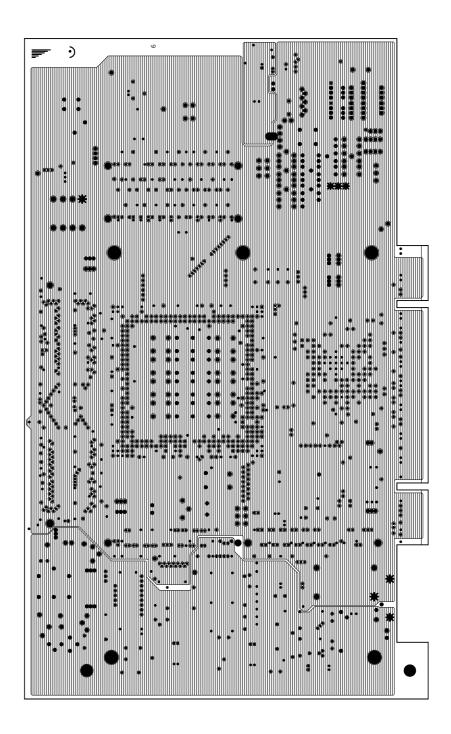

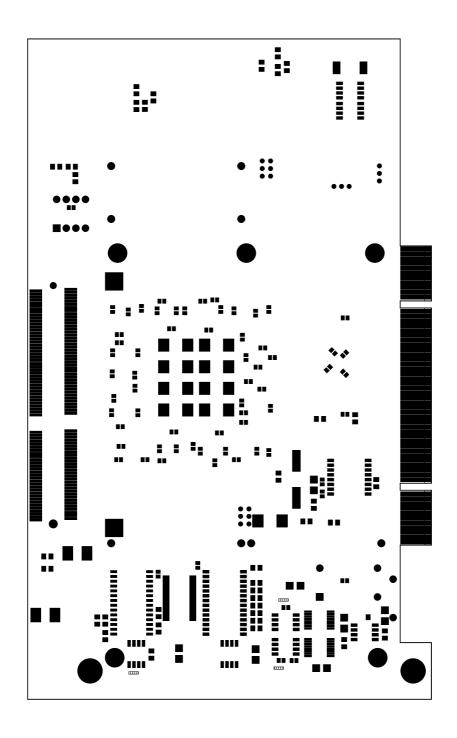

#### 3.1.2 Anordnung der Bauteile

Die Platzierung der Bauteile auf der Karte ist von großer Bedeutung, da durch eine geschickte Anordnung Leiterbahnlängen minimiert und die Signalqualitäten maxi-

Abbildung 3.1: Abmessungen nach PCI-Norm [PCI]

miert werden können. Weiterhin ist es für die Qualität der Signale von Vorteil, wenn die analogen Baugruppen räumlich getrennt von potentiellen Störungsquellen sind.

Fest definiert sind die Platzierung und Belegung der Kontaktleiste an der Unterkante der Karte. Die Anschlussbelegung des PLX-Chips sieht eine ausgezeichnete Richtung vor, die es erlaubt, die PCI-Signale kreuzungsfrei an den Stecker zu führen, und durch eine Zentrierung des Chips über der Kontaktleiste ist die erlaubte Leitungslänge der Bussignale von 37 mm<sup>1</sup> gut einzuhalten. Der lokale Bus führt von der Oberkante des PLX-Chips direkt zum FPGA, der im Zentrum der Karte liegt. Dies illustriert Abbildung 3.2

Entsprechend des Blockdiagramms (Abbildung 2.2) muss der CPLD ebenfalls Zugriff auf einen Teil der lokalen Busleitungen haben und ist deshalb links in der Nähe des Busses angesiedelt. Zusammen mit der Orientierung des FPGAs wird erreicht, dass der FPGA den lokalen Bustakt auf einem globalen Takteingang<sup>2</sup> empfangen kann und die vordefinierten Anschlüsse für die Konfigurationsleitungen<sup>3</sup> an der linken Seite des FPGAs in Nähe zum CPLD liegen. Die PLL befindet sich auf der Rückseite der Karte hinter dem CPLD, damit die Programmiereingänge und Taktausgänge zum CPLD und lokalen Bus kurz gehalten werden.

Die Spezifikation für Tochterplatinen nach dem CMC-Standard [IEEE:CMC] sieht eine rechteckige Platine<sup>4</sup> vor, die mindestens zwei CMC-Buchsen an definierten Stellen und einen sogenannten *IO-Space* an einer Kurzseite hat. Dieser *IO-Space* bedeutet, dass die CMC-Platine die volle Bauhöhe von 10 mm auf einer Länge von 40 mm benutzen darf, um Stecker für externe Anschlüsse bereitzustellen. Daher sind die CMC-Stecker und Haltelöcher so angebracht, dass die CMC-Karte mit dem *IO-Space* zur Rückwand des PCs zeigt und die definierte Frontblende in eine Ausfräsung im PCI-Kartenhalter passt. Dies schliesst nicht nur eine Bestückung der PCI-Karte im Bereich des *IO-Space* aus und legt die Anordnung der zwei standardmässigen CMC-

<sup>&</sup>lt;sup>1</sup>Steuerleitungen und Taktsignal dürfen bis zu 61 mm lang sein.

$<sup>^2</sup>$ siehe 3.3.2

<sup>&</sup>lt;sup>3</sup>verteilt auf FPGA-Bänke 2 und 3

<sup>&</sup>lt;sup>4</sup>80 \* 140 mm

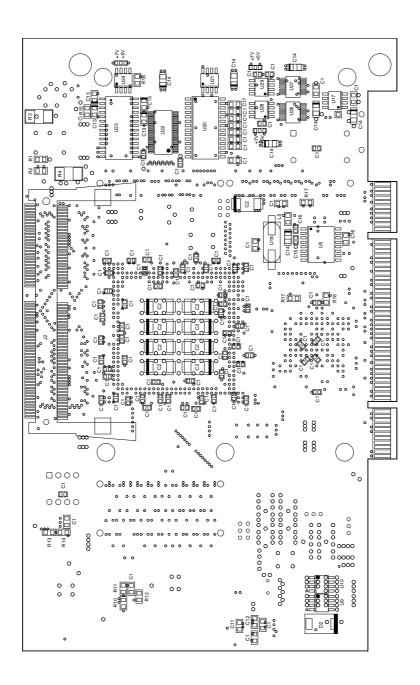

Abbildung 3.2: Anordnung der Bauteile

Stecker fest, sondern definiert zusätzliche Randbedingungen für die verbleibenden Bauteile.

Die für den *IO-Space* freigehaltene Fläche auf der Vorderseite der PCI-Karte ist ideal für die Platzierung der analogen Bauteile auf der Rückseite. In diesem Bereich befinden sich keine digitalen Bausteine, die Rauschen auf der Versorgungsspannung verursachen oder mit digitalen Bussen aus vielen Leitungen Störungen auf analogen Signalen durch Übersprechen hervorrufen können. Die Gruppierung der analogen Bauteile separat von digitalen ermöglicht die Trennung von Spannungsversorgungen, und die Anbringung auf der Rückseite sorgt zusätzlich für eine Abschirmung gegen elektromagnetische Felder, die auf der Oberseite erzeugt werden.

Der CMC-Standard definiert für die zwei obligatorischen Stecker rein digitale Signale (TTL) und eine Anordnung rechts vom FPGA. Darüber hinaus muss es eine Möglichkeit geben, die analogen Signale und digitalen LVDS-Signale mit der Toch-

terplatine auzutauschen. Aus Konsistenzgründen werden dazu auch CMC-Steckverbinder benutzt, jedoch befinden diese sich nicht an einer durch Normen festgelegten Stelle, sondern für die spezielle Funktion dieser Karte sinnvoll direkt neben dem IO-Space auf der Trennungslinie zwischen Analog- und Digitalteil. Dadurch können sowohl die digitalen Leitungen vom FPGA angeschlossen werden, als auch die analogen Signale von der Rückseite des IO-Spaces.

An der Oberkante des FPGAs liegt das RAM, das in direkter Nähe zum FPGA platziert ist, um die Leitungslänge dieses schnellen Busses zu minimieren. Dort befindet sich auch ein globaler Takteingang des FPGAs, der für die Ansteuerung des SD-RAMs benutzt wird. Die beiden S-RAM Bausteine sind auf der Oberseite zu sehen, währen sich der Sockel für das SD-RAM Modul auf der Unterseite befindet.

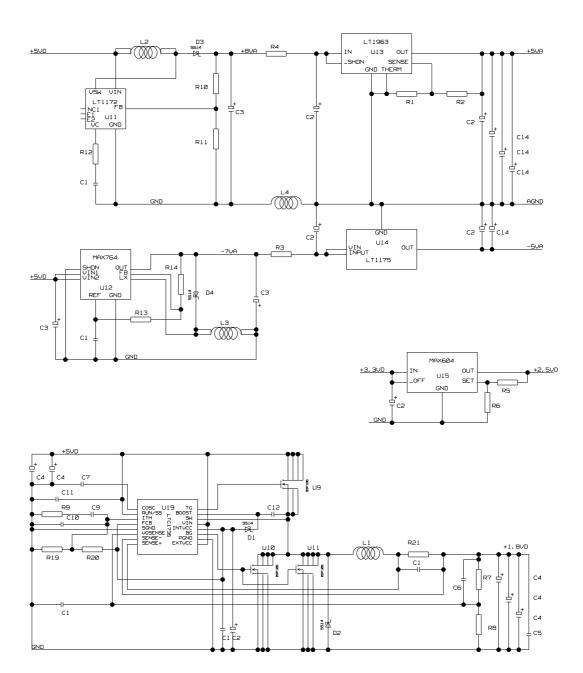

Die Anordnung der Netzteile berücksichtigt, dass Schaltregler, die wegen hochfrequenter Schaltvorgänge an Induktivitäten elektromagnetische Störungen verursachen, möglichst weit entfernt von den empfindlichen Analogbauteilen sind und die unkritischen Linearregler für die analoge Spannungsversorgung direkt neben dem Analogteil liegen.

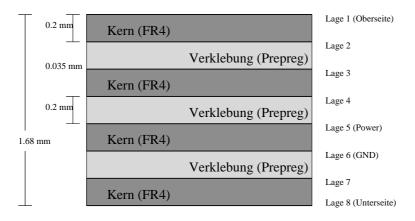

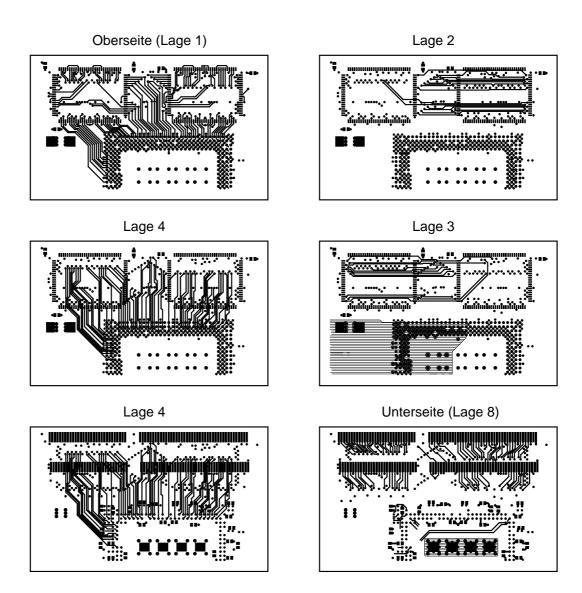

#### 3.1.3 Lagenaufbau

Der Lagenaufbau bezeichnet die interne Struktur der Platine, die aus abwechselnden Lagen von Leitern und Isolatoren besteht. Bedingt durch den Fertigungsprozess besteht eine Platine aus einem Kern aus Isolationsmaterial (glasfaserverstärktes Epoxydharz "FR4"), das auf der Ober- und Unterseite leitend beschichtet ist (Kupferfolie). Um eine mehrlagige Platine zu erhalten, werden mehrere solcher zweilagigen Teile verklebt, so dass immer eine geradzahlige Anzahl von leitenden Lagen entsteht. Die Materialdicke des Klebers (Prepreg) ist genau so gross wie die der Kerne und so wird ein symmetrischer Lagenaufbau erreicht. Einzelne Leiterbahnen entstehen durch Ätzung entsprechender Strukturen vor dem Verpressen, und Verbindungen zwischen Bauteilen können entweder auf einer Lage entlang führen oder durch sogenannte Vias die Lage wechseln.

Abbildung 3.3: Lagenaufbau der Platine

Um eine ausreichende Anzahl von Leiterbahnen zu ermöglichen, ist ein achtlagiger Aufbau gewählt, der als Querschnitt in Abbildung 3.3 zu sehen ist. Die inneren Lagen 5 und 6 werden als Flächen belassen und dienen der Spannungsversorgung, sowie als Abschirmung der Analogseite (Unterseite mit einer Ausweichlage) von der Digitalseite (Oberseite und 3 innere Lagen).

### 3.2 Bauteil-Gruppen zur Initialisierung der Karte

Sobald nach dem Einschalten des Rechners das Signal  $\overline{RESET}$  deaktiviert wird, beginnt die Initialisierung der Karte. Dabei sind die Inhalte aller flüchtigen Speicher ungültig und die Bauteile arbeiten mit Standardeinstellungen oder beziehen Konfigurationsdaten aus nicht flüchtigem Speicher. Der PLX-Chip initialisiert den lokalen Bus und meldet sich am PCI-Bus an, und der CPLD arbeitet gemäß seiner statischen Programmierung.

#### 3.2.1 Lokale Taktgenerierung (PLL)

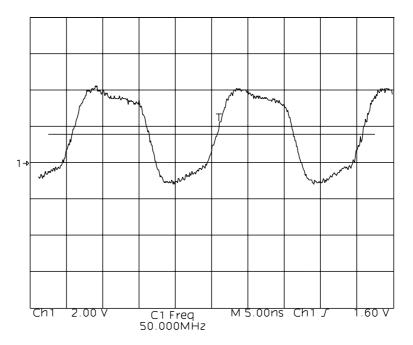

Zunächst wird für die gesamte synchrone Logik ein Taktsignal benötigt. Der lokale Bus kann mit bis zu 50 MHz betrieben werden, und der PLX, FPGA und CPLD benötigen eine entsprechende Taktung, um zu kommunizieren. Der FPGA kann intern diese Zeitbasis teilen oder vervielfachen, um Teile der Logik schneller oder langsamer zu takten. Darüber hinaus kann der FPGA eine zweite globale Taktung erhalten, die asynchron zur ersten ist.

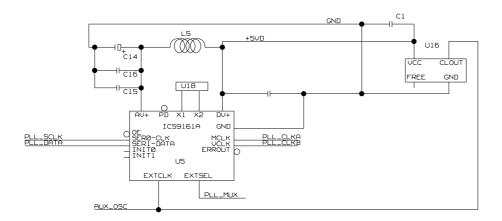

Ein geeigneter Takt wäre der PCI-Takt, der eine feste Frequenz von 33 MHz besitzt. Um eigene Frequenzen zu generieren, mit denen man die Geschwindigkeit des Systems in kleinen Stufen bis zu einem Maximalwert regeln kann, werden jedoch eigene PLLs auf dem Board implementiert. Der [ICS9161A] ist ein Baustein, der zwei unabhängige Taktsignale von 0.39 bis 120 MHz erzeugen kann. Als Eingangsfrequenzen dienen wahlweise ein Quarz oder ein Oszillator, der entweder auf dem Board eingelötet oder über einen CMC-Stecker auch von einer Tochterplatine bereit gestellt werden kann.

Durch ein serielles Programmierinterface, das der CPLD bedient, können die gewünschten Frequenzen eingestellt und zwischen Quarz oder Oszillatoreingang umgeschaltet werden. Dies gibt die Möglichkeit, während des laufenden Betriebes die Eingangsfrequenzen zu wechseln. So können Frequenzen, bei denen das Teilerverhältnis der PLL eine zu schlechte Langzeit-Phasentreue bedingen würde, am externen Eingang eingespeist und mit besseren Teilerverhältnissen getroffen werden oder Synchronisationen zu externen Takten erfolgen.

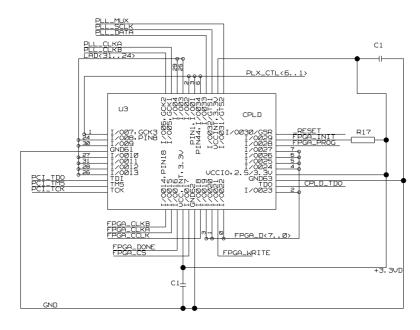

#### 3.2.2 CPLD

Da der FPGA von der PC-Software aus flexibel über den PCI-Bus programmiert werden soll, ist es nicht sinnvoll, eine feste Programmierung in nicht flüchtigem Speicher

auf der Karte zu hinterlegen. Allerdings kann der FPGA während der Neuprogrammierung nicht eigenständig die Ansteuerung des PCI-Busses übernehmen, sondern die Konfiguration muss von einem anderen Baustein gesteuert werden. Dies passiert durch den fest programmierten CPLD, dem ein Adressbereich auf dem lokalen Bus zugeordnet ist, über den er Konfigurationsdaten für den FPGA vom PC empfängt und im richtigen Protokoll an den FPGA liefert. Auf dieselbe Weise können Konfigurationsdaten für die PLL geschrieben werden, die vom CPLD auf die Programmierleitungen der PLL gegeben werden. Zur Kommunikation auf dem lokalen Bus besitzt der CPLD eine minimale Schnittstelle, bestehend aus acht Datenleitungen und den vier notwendigen Steuersignalen.

#### PLL-Kontrolle und Taktsignalkonvertierung

Der XC9536XL ist ein CPLD, der mit 3.3 V betrieben wird, aber 5 V-tolerante Eingänge hat. Dies wird ausgenutzt, um die beiden Taktsignale, die von der PLL mit 5 V getrieben werden, in den CPLD einzuspeisen und dann mit 3.3 V zum lokalen Bus und FPGA weiterzuleiten, denn die Eingänge des FPGAs sind nur mit maximal 3.3 V zu betreiben. Dies gibt neben dem notwendigen Pegelwandel die Möglichkeit, die Takte im CPLD ein- und auszuschalten oder zu halbieren/verdoppeln.

Die Weiterleitung des Taktes geschieht asynchron, während die PLL-Programmierung Teil einer synchronen state machine ist, die die Daten vom lokalen Bus entweder in das Programmier-timing der PLL umwandelt oder die Programmierung des FPGAs vornimmt.

#### FPGA Initialisierung

Die FPGAs der Virtex-E Reihe (siehe Abschnitt 3.3) unterstützen vier verschiedene Methoden zur Programmierung, die über Lötbrücken M0, M1, M2 auf der Platine gewählt werden können. Neben seriellen Protokollen wird auch der SelectMAP-Modus bereitgestellt, der eine 8 Bit parallele Datenübertragung erlaubt. Dieser Modus wird vom CPLD unterstützt, um schnelle Rekonfiguration während des Betriebs zu erlauben. Dazu werden acht Datenleitungen sowie FPGA\_CCLK, FPGA\_DONE, FPGA\_CS, FPGA\_WRITE, FPGA\_PROG und FPGA\_INIT benutzt.

Für die einsetzbaren FPGA-Typen XCV300E, XCV400E und XCV600E ist die Größe des Konfigurationsbitstromes 1.8 bis 3.9 MBit. Bei Ausnutzung der maximalen Geschwindigkeit des lokalen Busses von 50 MHz kann eine Initialisierung in 9 bis 20 ms erfolgen, während die serielle Übertragung entsprechend acht mal langsamer wäre.

Die Initialisierung des FPGAs [Xil:Data] beginnt automatisch beim Einschalten oder durch Betätigen der FPGA\_PROG Leitung. Daraufhin löscht der FPGA die internen Speicherzellen und signalisiert Bereitschaft mit FPGA\_INIT. Nun muss der Konfigurationstakt FPGA\_CCLK bereitgestellt werden, und sobald FPGA\_CS und FPGA\_WRITE vom CPLD aktiviert werden, empfängt der FPGA die Initialisierungsdaten. Falls die Taktfrequenz unter 50 MHz liegt, ist sichergestellt, dass der FPGA die Daten schnell genug verarbeiten kann. Höhere Frequenzen bis zu 66 MHz

sind nur mit Handshake möglich, damit der FPGA das Schicken weiterer Pakete unterbrechen kann. In der vorliegenden Implementierung wurde darauf aber verzichtet.

Sobald der FPGA fehlerfrei Daten in der Länge des Bitstroms empfangen hat, wird FPGA\_DONE aktiv und der CPLD erkennt, dass die Konfiguration abgeschlossen ist. CCLK bleibt bestehen, denn nach dem Empfangen der Daten muss der FPGA noch weitere Initialisierungen vornehmen. Der genaue Ablauf dieser Interna kann im Konfigurationsbitstrom definiert werden.

Abschaltung des ADC-Buffers Zum Abschluss dieses Abschnitts ist zu bemerken, dass die FPGA\_D Programmierdatenleitungen nicht nur vom CPLD zum FPGA gehen, sondern nach Abschluss der Programmierung im FPGA auch als Eingänge für die Daten des ADCs benutzt werden. Um die Konfiguration nicht zu stören, muss der Ausgangsbuffer des ADCs [FCT164245] deaktiviert werden, damit er nicht gleichzeitig zum CPLD versucht, die Leitungen zu treiben. Deshalb wird der Konfigurationsmodus des FPGAs gewählt<sup>5</sup>, der vor der Programmierung alle Ausgänge auf high setzt, damit auch der Output Enable  $\overline{OE}$  des Buffers high und damit ausgeschaltet ist. Ist der FPGA initialisiert, schaltet der CPLD seine Treiber inaktiv, und die Leitungen sind als Eingänge für den ADC im FPGA verfügbar.

#### 3.2.3 PLX

Das standardisierte PCI-Bus Protokoll sieht vor, dass es einen Bus-Master und einen Slave gibt, wobei der Master immer der Initiator eines Datentransfers auf ein Ziel (Target) ist. Obwohl es Bausteine mit integrierter Logik für PCI-Kommunikation gibt<sup>6</sup>, erfolgt die Anbindung der Prozessoren gewöhnlich über Wandler-Bausteine, die das komplizierte Timing auf dem Bus<sup>7</sup> in ein einfacheres, zeitlich nicht mit dem PCI-Bus korreliertes Protokoll auf einem lokalen Bus abbilden. Der [PLX9054] ist ein PCI-Bus Master-Chip, er kann also nicht nur Target eines Zugriffs sein, sondern auch selber Zugriffe initiieren. Die speziellen Fähigkeiten des Master-Chips werden benötigt, um DMA-Zugriffe benutzen zu können.

Ein normaler Datentransfer wird vom Master initiiert, und der Slave liest oder schreibt in einem festgelegten Protokoll einzelne Datenworte. Einzelne Wortübertragungen sind ineffizient, weil auf dem PCI-Bus Daten und Adressen auf den 32 Datenleitungen gemultiplext werden. Ausgehend davon, dass eine Lokalität der Daten besteht, ist es sehr wahrscheinlich, dass oft längere zusammenhängende Bereiche transferiert werden. Daher ist der PCI-Bus burst-orientiert. Burst-Zugriff bedeutet die Übertragung von mehreren aufeinander folgenden Datenworten, wobei zu Beginn nur einmal die Startadresse übergeben wird und das Target die Adressen selber entsprechend inkrementiert. Je länger ein Burst andauert, desto effizienter ist die Benutzung des Busses, da die Übertragung von Adressen entfällt.

$<sup>^5</sup>$ Lötbrücke M2 geschlossen

<sup>&</sup>lt;sup>6</sup>sowohl ASICs als auch FPGAs

<sup>&</sup>lt;sup>7</sup>u.U. mit langen Wartezeiten auf die Antwort eines Slaves

Es gibt einen entscheidenden Unterschied zwischen Lesen und Schreiben auf dem PCI-Bus. Beim Schreiben liegen die Daten dem Initiator vor und das Target kann die Übertragung so lange abblocken, bis es bereit zum Empfang ist. Dies geschieht durch das Signal RETRY#, wobei der Bus zwischen den Versuchen anderen Transaktionen zur Verfügung steht. Ist das Target bereit, wird nur die Zeit auf dem Bus verbraucht, die wirklich zur Übertragung notwendig ist.

Beim Lesen gibt der Initiator die Adresse des gewünschten Datums und wartet auf die Bereitstellung der Daten. Dabei hält er den gesamten Bus blockiert, während das Target die Daten (u.U. auf einem eigenen lokalen Bus) aquiriert und sendet. Es ist also wesentlich effizienter, statt eines Lesezyklus dem gewünschten Target nur die Adresse zu senden und diesen Schreibvorgang dann abzuschließen. Dann ist der PCI-Bus wieder frei, bis der angesprochene Slave die Daten bereit hat, den PCI-Bus für sich reserviert und als Initiator die gewünschten Daten im Burst zurück schreibt. Damit hat man einen langen, unteilbaren Lesevorgang in zwei effiziente Schreibvorgänge aufgeteilt. Dies ist der Grund, warum ein Master-Chip verwendet wird, der als Initiator arbeiten kann.

Beim ersten Einschalten des PCs fragt das BIOS<sup>8</sup> den PCI-Bus ab und prüft in der so genannten *Enumeration*, welche Steckplätze mit welchen Karten belegt sind. Außerdem geben die Karten an, wieviel Platz des adressierbaren 32 Bit (= 4 GByte großen) Adressraumes sie reservieren möchten. Das Betriebssystem verwaltet dann eine Tabelle der zugeordneten Adressierungsbereiche und kann so auf jede Karte individuell zugreifen. Auf der anderen Seite hat der lokale Bus des PLX-Chips auch 32 Bit, und da die Aufteilung der Adressräume der beiden Busse im Allgemeinen nicht übereinstimmt, muss der PLX-Chip die Abbildung zwischen den Adressbereichen der verschiedenen Busse vornehmen. In welcher Weise dieses *Mapping* funktioniert, kann beeinflusst werden<sup>9</sup>.

Der PLX unterstützt drei Betriebsmodi des lokalen Busses. Neben einer speziellen Anpassung an das Protokoll eines Motorola-Prozessors unterscheidet man zwischen je einem Modus mit und ohne Daten/Adress-Bündelung. Wie bereits erwähnt, ist der PCI-Bus ein gebündelter Bus, da sowohl Daten als auch Adressen über dieselben Busleitungen nacheinander übertragen werden. Ein nicht gemultiplexter Bus hat zusätzliche Leitungen für die Adressen und kann deshalb gleichzeitig Adressen und Daten liefern. Diesem potentiellen Geschwindigkeitsgewinn steht die verdoppelte Anzahl von Busleitungen entgegen. Da aber der PCI-Bus selbst mit 33 MHz und gemultiplext läuft und der lokale Bus mit bis zu 50 MHz, wird selbst ein gemultiplexter lokaler Bus schnell genug sein, um die Leistungsfähigkeit des PCI-Busses auszunutzen.

#### **3.2.4** EEPROM

Die zuvor erläuterten Einstellungen müssen vor der *Enumeration* durch das BIOS im PLX feststehen, sollen aber dennoch mit mäßigem Aufwand rekonfigurierbar sein.

<sup>&</sup>lt;sup>8</sup>basic input output system

<sup>&</sup>lt;sup>9</sup>siehe dazu auch [PLX9054] und [Bau01]

Deshalb wird die Konfiguration nicht im PLX-Chip hinterlegt, sondern auf einem externen seriellen EEPROM. Dieses EEPROM wird in einem DIL-8 Gehäuse auf einen Sockel auf der Karte gesteckt und kann so in einem separaten Schreibgerät programmiert, aber auch auf der Karte benutzt werden. Die Standardkonfiguration findet sich in Anhang A.

Der Zugriff auf das EEPROM erfolgt mit einem einfachen seriellen Protokoll auf den drei Signalen *Chip-Select*, *Clock* und *Data* wie in [EEPROM] beschrieben. Der verwendete Typ 93LC56 unterstützt sequential read, das einem *Burst-*Zugriff mit kompletter Auslese des gesamten Speichers entspricht. Beim Einschalten des PCs liest der PLX-Chip die Konfigurationsdaten aus dem EEPROM und übernimmt sie in interne Register. So kann sich die Karte an der *Enumeration* beteiligen und am Betriebsystem angemeldet werden.

Ist der Bootvorgang durchgeführt, kann auf den PLX und den lokalen Bus zugegriffen werden. Außerdem ist es möglich, über die serielle Verbindung Daten auf das EEPROM zu schreiben. Da der PLX aber nur einen open-drain Treiber für diese Leitung besitzt, muss ein externer Pullup-Widerstand am EEPROM die Treiberleistung bringen. Dieser Widerstand ist im Layout nicht vorgesehen, und somit wird ein versehentliches Überschreiben des EEPROMs ausgeschlossen.

#### 3.3 FPGA

Der FPGA ist das Herzstück des Testsystems, weil er die "lokale Intelligenz" jeder einzelnen Karte darstellt. Er definiert durch seine Konfigurationsdaten die Anpassung der allgemeinen Hardware an den jeweils zu testenden ASIC und ist der Schlüssel zur Benutzung der lokalen Hardware.

Ein FPGA ist ein Mikrochip, der aus einer Matrix von einigen hundert bis zu zehn tausend CLBs<sup>10</sup> besteht. Jeder dieser CLBs ist eine programmierbare digitale Zelle, die binäre Funktionen mit mehreren Ein- und Ausgängen darstellen kann. Ebenfalls konfigurierbar ist die Verschaltung dieser Zellen untereinander, so dass komplexe binäre Funktionen in Hardware implementiert werden können. Moderne FPGAs beinhalten außerdem Speicherzellen, konfigurierbare IO-Zellen, die vielfältige Standards zur Kommunikation mit anderen Bausteinen bereitstellen und herstellerspezifische Erweiterungen.

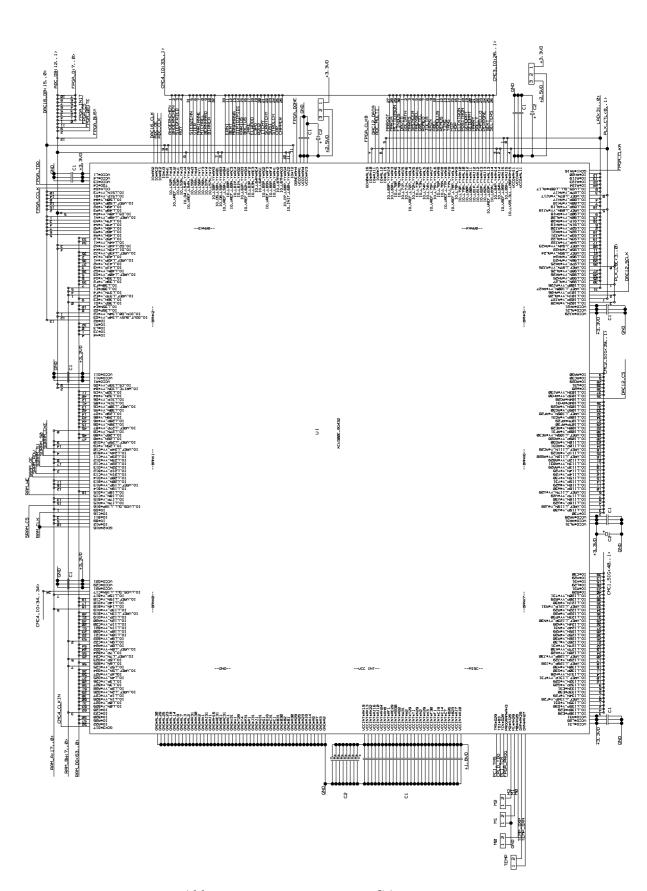

Entsprechend der Anforderungen an den FPGA, wie Matrixgröße, Geschwindigkeit, IO-Fähigkeiten und der technischen Möglichkeiten der heute erhältlichen FPGA-Typen, fiel die Wahl auf die Virtex-E Reihe der Firma Xilinx. Die Wahl des Gehäuses legt fest, welche Typen der Reihe verfügbar sind, und in diesem Projekt wird das BG432-Gehäuse benutzt, welches durch ein ball grid array mit 1.27 mm Rasterabstand und 432 Kontakten auf der Unterseite auf die Platine aufgebracht wird. In diesem Gehäuse verfügbar sind die Typen XCV300-E, XCV400-E und XCV600-E jeweils in den Geschwindigkeiten 6, 7 und 8. Es besteht also die Möglichkeit, den FPGA je nach Komplexität des Testsystems auszuwählen.

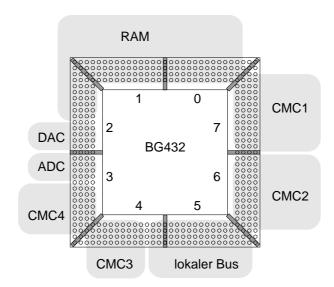

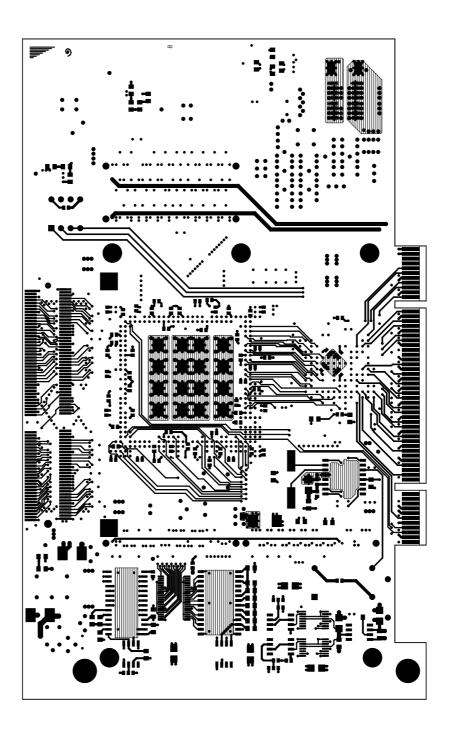

#### 3.3.1 IO-Aufteilung

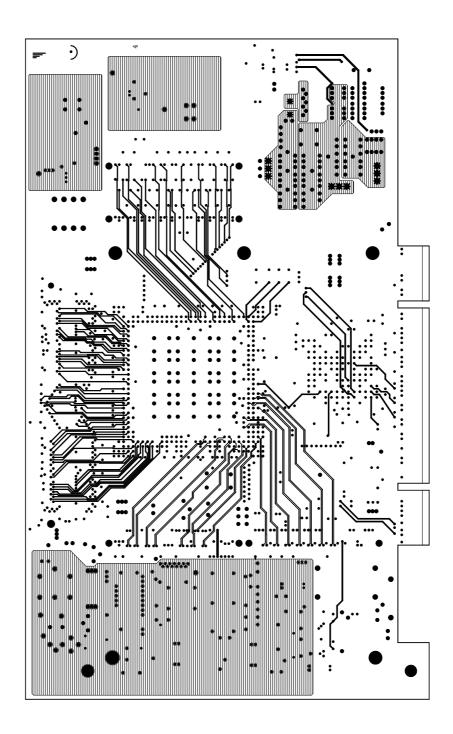

Das BGA432 hat neben Stromzuführungen und fest zugeordneten Anschlüssen 316 frei belegbare digitale Ein- und Ausgänge<sup>11</sup>. Diese IOs werden im FPGA eingeteilt in acht Bänke, und die Aufteilung der wichtigsten externen IO-Blöcke ergibt sich aus der Orientierung des FPGAs auf der Platine wie in Abbildung 3.4 angedeutet. Diese Orientierung stimmt mit der Sicht auf die Oberseite (Abbildung 3.2) überein.

Den größten Teil nimmt das RAM ein, denn es benötigt 18 Adress-, 64 Datenund 17 Steuerleitungen. Die standardisierten CMC-Stecker 1 und 2 befinden sich mit jeweils ca. 40 digitalen IOs rechts, und der lokale Bus mit 32 Daten- und 6 Steuerleitungen ist auf der rechten Unterseite angesiedelt, wo in direkter Nachbarschaft der PLX-Chip anschließt. Die selbst definierten CMC-Stecker 3 und 4 liegen auf *Dark*wing links vom FPGA und haben jeweils ca. 30 digitale IOs. Die übrigen Leitungen werden auf die Analogbauteile verteilt.

Die Aufteilung der Gruppen möglichst auf abgeschlossene Bänke ist aus zwei Gründen sinnvoll. Zum einen ist eine effiziente Platzierung der Logik im FPGA möglich, wenn Teile, die sich auf die Kommunikation mit einem bestimmten externen Chip beziehen, innerhalb einer Bank bzw. in benachbarten Bänken Platz finden und in

<sup>&</sup>lt;sup>10</sup>configurable logic block

<sup>&</sup>lt;sup>11</sup>im folgenden kurz IOs genannt

Abbildung 3.4: Aufteilung der IO-Bänke des FPGAs

räumlicher Nähe in der Matrix angesiedelt werden. Auch die Leiterbahnen auf der Platine können kreuzungsfrei und platzsparender verlegt werden, wenn Busse dicht nebeneinander liegen und vom FPGA direkt in Richtung des betreffenden Bauteils führen. Zum anderen kann die Wahl des in den IO-Treibern benutzten Logik-Standards (LVDS / LVTTL / etc.) nur bankweise zugeordnet werden und erfordert unter Umständen eine alternative Spannungsversorgung der gesamten Bank. Deshalb sollten sich die gleichartigen IOs in einer Bank befinden, um von anderen Logik-Standards separiert zu sein.

Die Bestrebungen, diese Richtlinien einzuhalten, haben Grenzen. So bleiben nach der Zuordnung der breiten Busse einzelne Leitungen übrig, die auf die vereinzelten, noch nicht zugeordneten Anschlüsse in den Bänken verteilt werden müssen. Dies betrifft die langsamen seriellen Leitungen zu den 12 Bit-DACs, einzelne Taktsignale oder andere Signale, die zeitlich unkritisch sind.

#### 3.3.2 FPGA-Taktung

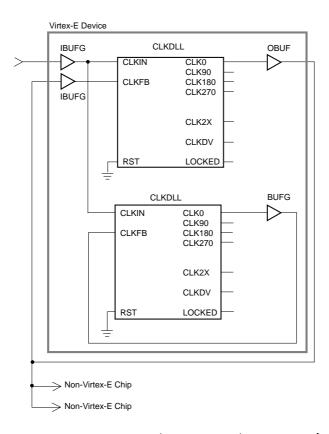

Der FPGA besitzt intern vier globale Netze für die Verteilung von Taktsignalen, die entweder von externen oder internen Signalen gespeist werden können. Wie bereits in 3.2.1 bzw. 3.2.2 beschrieben, erzeugt die PLL zwei Taktsignale auf TTL-Basis. Da die Eingangsbuffer des FPGAs aber maximal mit LVTTL mit 3.3 V betrieben werden dürfen, ist der CPLD mit 5 V-toleranten Eingängen und 3.3 V-Ausgängen dazwischen geschaltet, um die Signale an zwei globale Takteingänge des FPGAs zu bringen. Eine Taktfrequenz ist identisch mit der des lokalen Busses, die andere ist frei programmierbar.

Ein dritter Eingang wird für die SD-RAM Ansteuerung benötigt. Die Virtex-E FPGAs besitzen acht DLLs<sup>12</sup>, die entweder zur Verdopplung oder Phasenangleichung

<sup>&</sup>lt;sup>12</sup>delay locked loop

von Taktfrequenzen benutzt werden können [Xil:Data]. Bei der Ansteuerung des SD-RAMs benutzt man zwei gekoppelte DLLs, die diese Fähigkeiten ausnutzen. Die interne Logik des FPGAs kann mit einer niedrigen Frequenz von 50 MHz betrieben werden, während eine DLL diese verdoppelt und das RAM extern mit 100 MHz taktet. Bei derart hohen Frequenzen spielt die Laufzeit der Signale eine Rolle, denn das RAM erhält seine Taktung vom FPGA über einen Ausgangstreiber und eine Leitung mit gewisser Laufzeit. Werden Daten zum RAM geschrieben, erfahren Daten und Taktsignal dieselbe Verzögerung, und die Flanken von Daten und Takt sind synchron. Beim Lesen werden die Daten vom RAM zu einer steigenden Taktflanke auf den Bus gegeben. Da sich aber die Verzögerung des Taktsignals vom FPGA zum RAM und die Verzögerung der Daten vom RAM zum FPGA addieren, sind die Daten erst einige Zeit nach der steigenden Flanke am FPGA gültig. Bei einer Frequenz von 100 MHz dauert ein Zyklus 10 ns, und die Summe der Verzögerungen kann diese Zeitspanne überschreiten. Daher kann es passieren, dass ein verzögertes Signal nicht mehr zur steigenden Flanke des unverzögerten Taktsignals am FPGA empfangen werden kann und das Lesen scheitert.

Abbildung 3.5: Taktangleichung (clock mirror) mit DLLs [Xil:Data]

In [Xil:DLL] und [Xil:Data] ist ausgeführt, wie zwei DLLs benutzt werden, um die Verzögerung der Leitungen zu kompensieren. Über einen Abgriff des Taktsignals auf halber Länge zu den Empfängerbausteinen (hier RAM) wird eine Rückkopplung

3.3. *FPGA* 21

zum FPGA hergestellt, und die Taktflanke kommt gleichzeitig am Empfänger und am Rückkopplungseingang des FPGAs an.

Die Kombination der beiden DLLs wird verdeutlicht durch das Blockdiagramm in Abbildung 3.5. Die dargestellten Komponenten sind schematisierte Bibliotheksfunktionen, die als vordefinierte Blöcke verfügbar sind und im VHDL-Code benutzt werden können. Beide DLLs erhalten die interne Taktung an den Anschlüssen CLKIN. Die obere DLL kann über die Rückkopplung externe Verzögerungen kompensieren. Das Ausgangssignal an CLK0 wird dabei so eingestellt, dass die Phase des rückgekoppelten Signals CLKFB exakt mit der des internen CLKIN übereinstimmt. Durch die gleiche Weglänge der Rückkopplung und der Leitung zum Empfänger ist damit auch eine Taktflanke am Empfänger exakt gleichzeitig zum internen Signal.

Die untere DLL erzeugt die Taktung für die Empfängerlogik im FPGA. Dadurch, dass die Leitungen durch interne Buffer BUFG gehen, die in der Verzögerung dem Ausgangsbuffer OBUF entsprechen, kann durch zusätzliche interne Rückkopplung eine vollkommene Synchronität der IO-Buffer des FPGAs und des externen Empfängers mit dem internen Eingangstakt erreicht werden.

Der vierte der globalen Takteingänge ist auf einen CMC-Stecker gelegt, um eine Taktung des FPGAs von einer Tochterplatine aus zuzulassen. Dieser Eingang ist auch im LVDS-Modus zu benutzen, um die Register des FPGAs mit den Datensignalen des LVDS-Busses synchronisieren zu können. Dies ermöglicht quellensynchrone Übertragung, bei der das Taktsignal jeweils von dem Baustein erzeugt wird, der Daten sendet.

#### 3.3.3 LVDS/LVTTL-Bänke

Die Bänke 3 und 4 des FPGAs sind an die CMC-Stecker 4 und 3<sup>13</sup> verbunden, die keiner Norm unterliegen und deshalb frei belegt werden können. Dies wird ausgenutzt, um die Verteilung der Signale auf den Stecker so zu wählen, dass LVDS-Signale als differentielle Leitungspaare verwirklicht werden, was im folgenden erläutert wird.

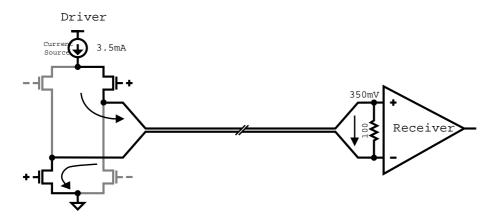

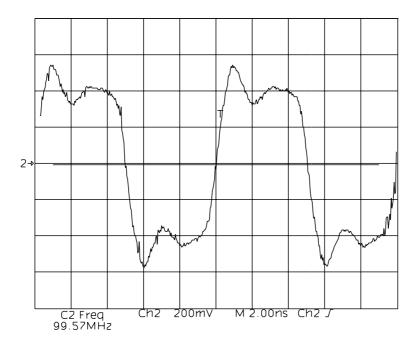

Ein typischer LVDS-Kanal ist in Abbildung 3.6 dargestellt. Eine Stromquelle von 3.5 mA im Sender treibt einen Stromfluss über die Leiterschleife. Direkt vor dem Empfänger ist ein Widerstand, über dem der Spannungsabfall gemessen wird. Typischerweise wird mit einer Spannungsdifferenz von 350 mV über einem  $100\,\Omega$  Abschlusswiderstand gearbeitet. Die logischen Zustände high und low werden durch die Stromrichtung repräsentiert.

Diese Schleife ist weniger anfällig gegen Störungen als herkömmliche Verbindungen, die eine Spannungsdifferenz zwischen einer Leitung und einem gemeinsamen Massepotential benutzen. Offensichtlich sind getrennte Stromrückflüsse die beste Möglichkeit, um die Signale zu separieren und ein Übersprechen, das von der gemeinsamen Masse herrührt, zu vermeiden. Dies verdoppelt zwar die Anzahl der benötigten Leitungen, was für einen Bus unter Umständen viel Platz verbraucht, aber es reduziert auf der anderen Seite die Anzahl der Masseverbindungen. Darüber hinaus schafft es die Möglichkeit, die elektrischen Eigenschaften der Übertragungsleitungen

<sup>&</sup>lt;sup>13</sup>siehe Abbildung 3.4

Abbildung 3.6: Ein LVDS Übertragungskanal [LVDS]

zu verbessern, um höhere Übertragungsraten zu erreichen. Die Leitungen werden in minimalem Abstand nebeneinander geführt. Dabei wird ausgenutzt, dass die Leitungen ähnlich auf elektromagnetische Störfelder reagieren, da sie nahezu am selben Ort liegen und die selbe Ausrichtung zum Feld haben. Weit auseinanderliegende Leitungen oder harte Ecken in den Leitungen führen dazu, dass Felder in unterschiedlicher Weise auf die Leitungen wirken können. Den Extremfall stellt der bei TTL übliche Stromrückfluss über eine Massefläche dar, wo ein Störfeld auf die frei laufende einzelne Leitung vollkommen anders wirkt als auf den zugehörigen Rückfluss. Da das Signal am Empfänger definiert ist als die Spannungsdifferenz an der Terminierung, wird eine so genannte Gleichtaktstörung dadurch unterdrückt, dass sie auf beide Leitungen gleichermaßen wirkt und der Hin- und Rückfluss nicht verschiedenen Einflüssen ausgesetzt sind.

Diese Verbesserung der Signalqualität ermöglicht erst den kleinen Spannungshub von einigen hundert mV und somit auch eine schnellere Umkehr der Stromrichtung. Somit können die Taktzeiten verkürzt und Taktfrequenzen von bis zu zwei GHz erreicht werden. Diese Techniken stellen aber auch höhere Ansprüche als bisher an das Leiterplattenlayout, denn bei hohen Geschwindigkeiten spielen Reflexion und Dämpfung von Signalen eine immer größere Rolle.

Aus der Telegraphengleichung<sup>14</sup> folgt, dass ein Signal auf einer realen Leitung mit Kapazität C pro Länge und Induktivität L pro Länge als Welle aufgefasst werden kann. Bei endlichen Leitungen tritt daher eine Reflexion des Signales am Ende auf, die in entgegengesetzter Richtung auf der Leitung weiter läuft. Bei einer getakteten Signalübertragung kann es passieren, dass die reflektierte Welle sich mit der einlaufenden Welle oder der des darauffolgenden Taktes überlagert und so das Signal verfälscht. Die Spannungsamplitude U am Ort x ist

$$U(x) = U_{r\ddot{u}ck}(x) + U_{hin}(x) = Ae^{-\gamma x} + Be^{\gamma x} \quad ; \quad \gamma = i\omega\sqrt{LC}$$

(3.1)

<sup>&</sup>lt;sup>14</sup>siehe jedes Elektronik-Lehrbuch; beispielsweise [Hin96, Formel (2.15)]

3.3. FPGA 23

Der Reflexionsfaktor r ist gegeben durch das Verhältnis der Amplituden der einund auslaufenden Welle und schreibt sich mit der Impedanz Z der Leitung und dem Abschlusswiderstand  $R_a$  als

$$r = \frac{U_{r\ddot{u}ck}}{U_{hin}} = \frac{R_a - Z}{R_a + Z} \qquad ; \qquad Z = \sqrt{L/C}$$

(3.2)

Bei hohen Übertragungsgeschwindigkeiten besteht keine Zeit, auf ein Abklingen der Reflexionen durch parasitäre Dämpfung der Leitung zu warten, sondern die Impedanz der Leitungen muss auf den Abschlusswiderstand angepasst sein, um die gesamte Energie der einlaufenden Welle aufzunehmen und Reflexion zu verhindern. Es ist sofort ersichtlich, dass bei gegebenem Abschlusswiderstand die Impedanz der Leitung gleich dem Abschlusswiderstand sein muss, um eine Reflexion zu vermeiden, denn der Einfluss der reflektierten Welle wird mit der Differenz der Widerstände größer. Für die Fälle  $R_a < Z$  und  $R_a > Z$  erfolgt Reflexion mit Phasenverschiebung kleiner bzw. größer  $90^{\circ}$ , wie aus der Wellenlehre bekannt.

Dies ist der Grund, warum LVDS nicht als das Treiben eines Signals auf einen Spannungspegel, sondern eines Stromes bei gegebenem Abschlusswiderstand definiert ist. Bei Standard TTL<sup>15</sup> oder LVTTL ist weder der Widerstand des Empfängers noch die Impedanz der Leitung festgelegt, was bei einer beliebigen Treiberleistung zu unkontrollierbaren Reflexionen führt. Abhilfe schafft hier nur eine einstellbare Treiberleistung, wie sie die IO-Zellen des FPGAs bieten, oder die Terminierung der Leitung durch einen Widerstand.

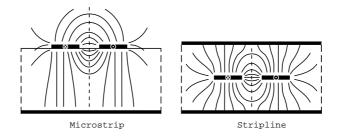

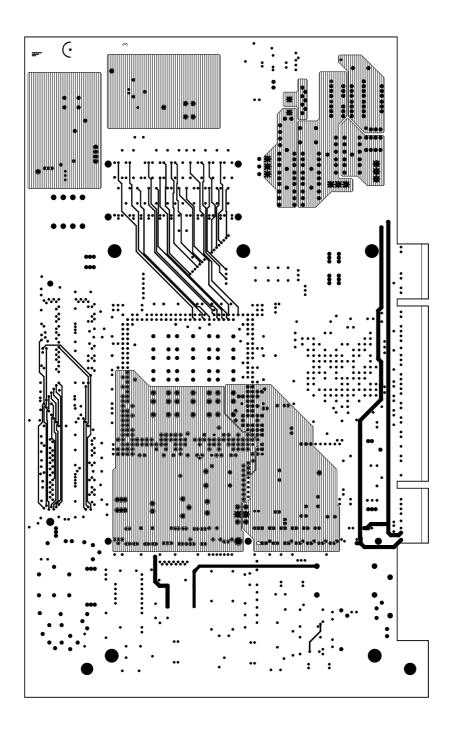

Um die Impedanz einer differentiellen Leitung zu kontrollieren, genügt es nicht, die Kapazität und Induktivität wie im Falle einer einzelnen Leitung auszurechnen, sondern es muss neben der kapazitiven Kopplung an eine Potentialfläche auch die Kopplung an die eng anliegende Nachbarleitung einbezogen werden. Abbildung 3.7 verdeutlicht den Verlauf der Feldlinien der zwei Standardkonfigurationen *Microstrip* und *Stripline*.

Abbildung 3.7: Feldlinien verschiedener LVDS Konfigurationen [LVDS]

Bei der *Microstrip* Leitung liegen die Leiterbahnen auf der Oberseite der Platine im Feld einer Potentialfläche (Masse oder Versorgungsspannung). Im Falle der *Stripline* ist das Leitungspaar eingeschlossen zwischen zwei Potentialflächen. Wichtig ist immer die Symmetrie sowohl des Leitungspaares untereinander, als auch der Lage des Paares in einem äußeren Feld, damit Felder auf die Leitungen gleich wirken.

<sup>&</sup>lt;sup>15</sup>transistor-transistor logic

Zur Berechnung der Impedanz unter Berücksichtigung der kapazitiven Kopplung gibt es heuristische Formeln [LVDS], die einige Standardfälle abdecken. Für eine genaue Berechnung auch besonderer Anordnungen existieren Computersimulationen, die durch lineare Approximation finiter Elemente den Feldverlauf annähern und aus der Geometrie der Leiter die Impedanz berechnen.

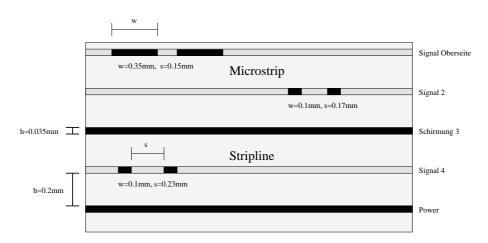

Zur Spezifikation der Anordnung benötigt das Simulationsprogramm [Polar] die Abmessungen und den Abstand der differentiellen Leitungen, den Abstand zu festgelegten Potentialflächen und die Dielektrizitätskonstanten der Isolatoren (Luft, Kernmaterial oder Verklebung). Durch den Lagenaufbau $^{16}$  sind die Dicke der Kerne und der Verklebung mit  $0.2\,\mathrm{mm}$  festgelegt sowie die Dicke der Leiterbahnen mit  $0.035\,\mathrm{mm}$ . Die Dielektrizitätskonstanten von FR4 und Prepreg sind ungefähr gleich und näherungsweise mit  $\epsilon_r=4.5$ anzunehmen.

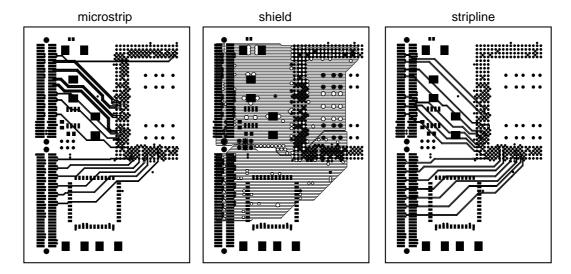

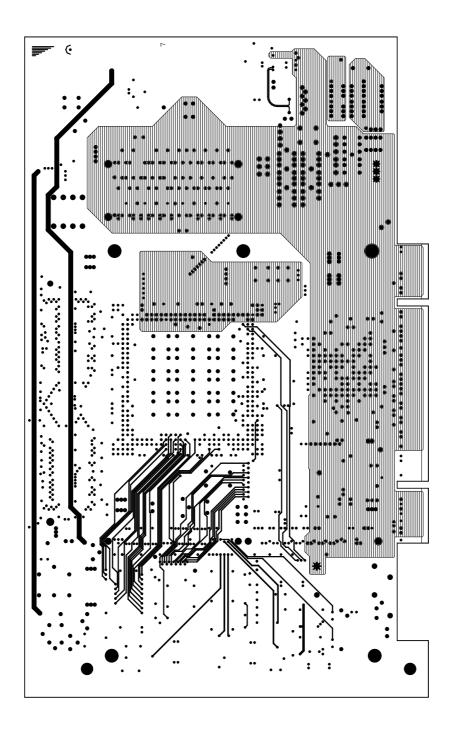

Auf der PCI-Karte sollen LVDS-Busse mit 15 Bit zu CMC3 und 13 Bit zu CMC4 auf engstem Raum untergebracht werden. Daher kann nicht auf eine einfache Konfiguration zurückgegriffen werden, wo zum Beispiel alle Leitungen nebeneinander als Microstrip verlegt werden. Der Lagenaufbau sieht über der flächigen Lage 5 vier Lagen für digitale Leitungen vor. Um genügend großen Abstand zwischen den Paaren zu ermöglichen, wird im Bereich der LVDS-Leitungen eine Abschirmungsfläche auf Lage 3 eingezogen, damit es zwei unabhängige Lagen für Striplines (Lage 4) und Microstrip (Oberseite bzw. Lage 2) gibt. Leitungen auf der Oberseite haben den Vorteil, dass sie keine Vias benötigen, die Reflexionen verursachen können. Falls aber auf der Oberseite Bauteile sind, die keinen Platz für Leiterbahnen erlauben, muss auf Lage 2 ausgewichen werden.

Abbildung 3.8: Querschnitt-Sicht auf LVDS Leitungen

Die Prozessparameter der Herstellung erlauben eine minimale Leiterbahnbreite und einen minimalen Isolationsabstand von  $0.1\,\mathrm{mm}$ . Die kleinste Realisierung von LVDS-Leitungen mit kontrollierter Impedanz von  $100\,\Omega$  ist in Abbildung 3.8 dargestellt, wobei über der obersten Lage noch Lötstopp-Lack angenommen wird. Die

<sup>&</sup>lt;sup>16</sup>siehe Absatz 3.1.3

3.3. FPGA 25

korrekten Bezeichnungen der Übertragungswege sind: coated microstrip (Lage 1), embedded microstrip (Lage 2) und symmetrical stripline (Lage 4).

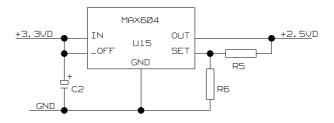

Abbildung 3.9: Aufsicht auf LVDS Leitungen

Die Aufsicht auf die Lagen zeigt Abbildung 3.9, wobei zur Orientierung immer auch die Pads der Oberseite eingezeichnet sind. Dies verdeutlicht, warum die Microstrip Leitungen im Bereich des CPLD (unten) und des 2.5 V Spannungsreglers (oben) nicht auf der Oberseite sondern auf Lage 2 laufen müssen. Da LVDS-Bänke mit 2.5 V IO-Spannung betrieben werden, ist der Regler in der Nähe der Bänke angesiedelt. Auf Lage 3 ist die flächige Abschirmung zu erkennen, die ausserdem die Versorgungsspannung vom Regler zu den LVDS-Bänken leitet. Lage 4 wird hier ausschließlich für das Verlegen der Striplines benutzt.

# 3.4 Lokaler Speicher

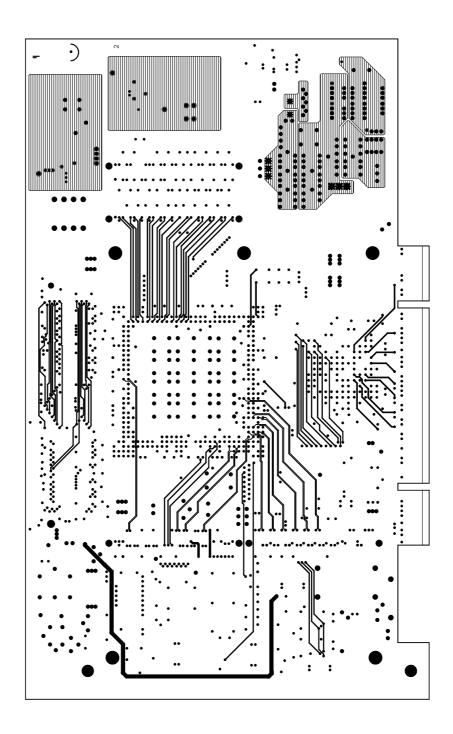

Die PCI-Karte verfügt über 2 S-RAM Bausteine zu je 1 MByte und einen Sockel für bis zu 128 MByte SD-RAM. Obwohl die beiden RAM-Typen grundlegend verschieden sind, können die Daten- und Adressleitungen gemeinsam benutzt werden. Dies verhindert zwar eine gleichzeitige Benutzung der beiden RAMs, jedoch bleibt es möglich, in kurzer Zeit zwischen den RAMs umzuschalten und sie uneingeschränkt nacheinander zu benutzen. Dies wird durch eine separate Beschaltung der *Chip-Select* Steuersignale erreicht.

Im Allgemeinen ist die Ansteuerung des S-RAMs einfacher zu realisieren und 2 MByte RAM sind standardmäßig auf jeder Karte vorhanden und reichen für viele Anwendungen aus. Soll ein speicherintensiveres System aufgebaut werden, das viele Daten lokal lagert, so kann optional bis zu 128 MByte SD-RAM aufgesteckt werden. Aus Platzgründen befindet sich ein SO-DIMM-Sockel mit 144 Anschlüssen [SDModul] auf der Rückseite der Platine. In [Xil:DLL] ist eine mögliche Ansteuerung des SD-RAMs beschrieben sowie als VHDL-Code verfügbar und kann mit Anpassungen an die spezifische Anschlussbelegung des FPGAs verwendet werden.

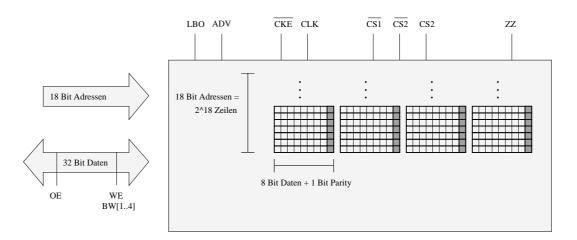

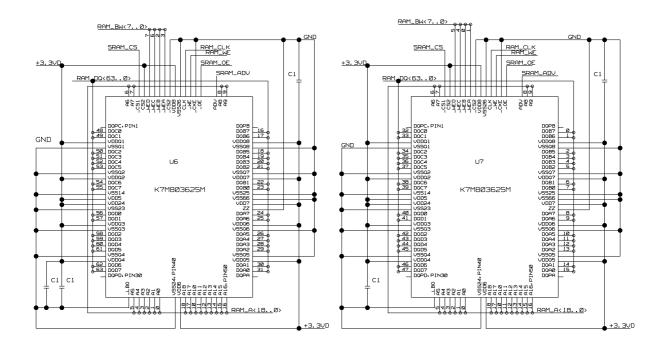

# 3.4.1 Statisches (S-) RAM

Die Bausteine der Reihe K7M-803625 [SRAM] sind S-RAMs mit 1 MByte Speicherkapazität in einer 36 Bit breiten, 256 K tiefen Architektur, die in Abbildung 3.10 vereinfacht dargestellt ist. Die Breite ist aufgeteilt in vier Worte zu 9 Bit, damit ein Byte Nutzdaten und ein Paritätsbit gespeichert werden können. Da das Paritätsbit aber weitere vier Signale benötigt und von dem SD-RAM Modul nicht unterstützt wird, wird in diesem Fall auf eine Benutzung verzichtet. Die Bausteine sind so genannte no turnaroud-SRAMs, das bedeutet, dass Lese- und Schreibzyklen ohne Wartezyklen wechseln dürfen, was die Ansteuerung vereinfacht.

Um eine hohe Bandbreite und doppelte Speicherkapazität zu erreichen, werden zwei S-RAM Bausteine nebeneinander an einen 64Bit breiten Datenbus angeschlossen, so dass sie dieselben Steuersignale bekommen und sich wie ein einziger Speicher verhalten. Dabei wird die byteweise Aufteilung der Bus-Datenleitungen auf die RAM-Anschlüsse durch eine günstige Anordnung im Layout bestimmt.

Neben den Adress- und Datenleitungen besitzt das RAM die folgenden Steuerleitungen:

**Takt:** Der Anschluss CLK ist der Eingang für die Zeitbasis, zu deren steigenden Flanken Zugriffe auf den Speicher erfolgen können. Durch das low aktive  $\overline{CKE}$ -Signal kann diese Taktung gehemmt werden, so dass keine Kommunikation mit der Logik des Bausteins möglich ist, weil keine Befehle decodiert werden können. Mit den benutzten Bausteinen kann eine maximale Taktfrequenz von 100 MHz erreicht werden.

Abbildung 3.10: Speicheraufbau des S-RAMs

Chip Select: Der Baustein hat drei Chip Select Leitungen, die zusammen die Befehlsdecodierung aktivieren. Damit der Baustein selektiert ist und Befehle akzeptiert, müssen  $\overline{CS_1}$  und  $\overline{CS_2}$  low sein und  $CS_2$  als Negation von  $\overline{CS_2}$  high. In jedem anderen Fall ist der Baustein nicht selektiert und empfängt zwar Befehle, führt sie aber nicht aus. Die drei Eingänge sind vollkommen gleichberechtigt und redundant, darum genügt es,  $\overline{CS_2}$  fest auf low und  $CS_2$  fest auf high zu legen und die Selektierung ausschließlich mit  $\overline{CS_1}$  zu steuern.

Output Enable: Das  $\overline{OE}$ -Signal erlaubt es zu jeder Zeit, die Ausgangstreiber des RAMs auszuschalten und so die Busleitungen hochohmig zu setzen. Dies bedeutet, dass die Leitungen nicht getrieben werden, damit andere Bauteile die Leitungen mit ihren Ausgangstreibern ansprechen und benutzen können.

Write Enable, Byte Write: Ein Arbeitszyklus beginnt, wenn der Baustein selektiert ist, zu jeder steigenden Taktflanke. Ist dabei  $\overline{WE}$  high gesetzt, beginnt ein Lesezyklus. Adressdaten werden eingelesen, und am Ende des Taktes liegen die Daten an den Ausgangstreibern an. Für den Beginn eines Schreibzyklus muss  $\overline{WE}$  low gesetzt sein und die anliegenden Daten werden im darauf folgenden Zyklus in den Speicher übernommen. Mittels der  $\overline{BW_{1,2,3,4}}$  Leitungen kann eine Maskierung angegeben werden, die bestimmt, welche der vier Bytes in einer Reihe mit den Daten des Busses überschrieben werden sollen.

Linear Burst Order, Adress Advance/Load: Über die Signale  $\overline{LBO}$  und ADV kann das RAM im Burst-Modus benutzt werden und intern automatisch Adressen erzeugen. Dies ist für die vorliegende Anwendung nicht von Interesse, da die Adressleitungen nicht mit den Datenleitungen gemultiplext sind und es keine Einschränkung bedeutet, die Adressen zu jedem Takt von außen einzulesen.

**Power Sleep:** Das asynchrone Signal  $\overline{ZZ}$  versetzt den Baustein zu jeder Zeit in einen energiesparenden Modus, der aber die Daten des Speichers erhält. Dieser Modus bleibt unbenutzt, da die Funktionalität des Abschaltens durch das *Chip Select* abgedeckt ist und auf eine Reduzierung der Stromaufnahme in diesem Fall verzichtet werden kann.

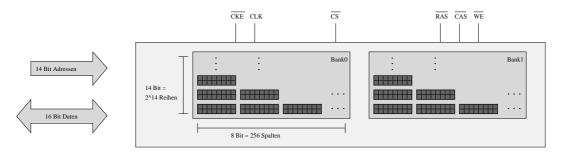

# 3.4.2 Synchron dynamisches (SD-) RAM

SD-RAM unterscheidet sich in der internen Funktionsweise grundsätzlich von S-RAM. Während in einer statischen Speicherzelle mehrere Transistoren so verschaltet sind, dass sie einen Zustand behalten, bis durch einen Treiber ein anderer Zustand erzwungen wird, unterliegt die Speicherung der Information in der Kapazität einer dynamischen RAM-Zelle einer ständigen Fluktuation. Da durch parasitäre Effekte immer Ladungen abfließen, muss in regelmäßigen Abständen eine Auffrischung der Information erfolgen. Der Vorteil von dynamischen Speicherzellen besteht in der geringeren Größe, daher kann im Allgemeinen mehr Speicherkapazität in einem Baustein untergebracht werden.

Ein Modul mit 64 Bit breitem Datenbus besteht aus 4 gleichartigen parallel geschalteten Bausteinen, denen je 16 Bit des Busses zugeordnet sind. Die Ansteuerung der gemeinsamen Adress- und Steuerleitungen ergibt sich aus den Spezifikationen der einzelnen Bausteine wie in [SDRAM] beschrieben. Zunächst ist der interne Speicher jedes Bauteils in zwei oder vier Bänke aufgeteilt, die getrennt voneinander angesprochen werden. Innerhalb einer Bank gibt es 2<sup>14</sup> Reihen und 2<sup>8</sup> Spalten von 16 Bit breiten Speicherzellen. Die Adressierung eines Datums erfolgt in zwei Takten, wobei im ersten Takt die Reihe selektiert wird und im zweiten Takt die Spalte.

Abbildung 3.11: Speicheraufbau eines SD-RAM Chips

Nach dem Einschalten muss es eine Initialisierungszeit von  $100 \,\mu s$  geben, in der keine Befehle angenommen werden. Danach muss die Logik als erstes im Leerlauf<sup>17</sup> betrieben werden, und es müssen einige *Refresh*-Zyklen erfolgen. Danach ist das SD-RAM bereit für den normalen Betrieb.

**Taktung und Chip Select:** Die CLK und  $\overline{CKE}$ -Signale sowie die einzelne  $\overline{CS}$ -Leitung haben beim SD-RAM dieselbe Funktion wie beim S-RAM. Bei einem RAM-

<sup>&</sup>lt;sup>17</sup>Befehl NOP - no operation

Modul, bei dem 4 Bausteine die Datenbusbreite abdecken, kann bei einer Bestückung mit 8 Bauteilen über doppelte *Clock Enable* und *Chip Select* Leitungen gewählt werden, welcher der beiden Chipsätze aktiv ist. So kann die Speicherkapazität verdoppelt werden.

Row Address Select, Column Address Select, Write Enable: Die Leitungen  $\overline{RAS}$ ,  $\overline{CAS}$  und  $\overline{WE}$  definieren den Befehlssatz des SD-RAMs. Sind alle drei Leitungen high, so bedeutet dies NOP, da die Signale low aktiv sind. Das SD-RAM ist nicht in jedem Takt identisch anzusprechen wie das S-RAM, sondern es gibt Befehle, die sich über mehrere Zyklen erstrecken und in der korrekten zeitlichen Abfolge angesteuert werden müssen. Durch  $\overline{RAS}$  wird eine Reihe aktiviert, was notwendige Voraussetzung für jeden Speicherzugriff ist. Im nächsten Zyklus kann durch  $\overline{CAS}$  eine Spalte selektiert werden und abhängig von  $\overline{WE}$  ein Schreib- oder Lesezyklus erfolgen.

Neben den Speicherzugriffen gibt es beim SD-RAM auch administrative Befehle wie das Schreiben von Werten in interne Konfigurationsregister, *Precharge* oder *Refresh*. Ein *Refresh*-Zyklus bedeutet, dass eine Reihe aufgefrischt wird, also intern gelesen und neu geschrieben. Eine Auffrischung des gesamten Speichers erfordert 4096 *Refresh*-Zyklen alle 64 ms, entweder verteilt über die Zeit oder gebündelt als *Burst Refresh*, wobei das Adressschema der Auffrischung von der internen Logik erzeugt wird. Bei einer Taktung von 100 MHz dauert ein *Burst Refresh* circa 0.4 ms, und somit ist der Anteil der Zeit, der für Auffrischung nötig wird, vernachlässigbar.

#### 3.4.3 Gemeinsame Benutzung der Busleitungen

Wie zu Beginn dieses Abschnittes erwähnt, werden möglichst viele Leitungen zum FPGA von beiden RAM-Sorten gemeinsam benutzt. Für die 64 Datenleitungen ist es selbstverständlich, dass beide RAMs byteweise den gesamten Bus abdecken müssen. Die Anzahl der Adress- und Steuerleitungen ist aber verschieden und muss sinnvoll aufgeteilt werden. Die *Chip Select* und *Clock Enable* Signale der Bausteine müssen einzeln ansprechbar sein, damit sie wechselseitig ausgeschaltet werden können und sichergestellt ist, dass die ausgeschalteten RAMs nicht die Kommunikation mit den eingeschalteten stören. Beim S-RAM muss außerdem durch eine individuelle Ansteuerung des *Output Enable* sichergestellt werden, dass die Ausgangstreiber deaktiviert werden können. Die Adressleitungen 1 bis 13 können direkt von beiden RAMs benutzt werden. Da das S-RAM aber mehr Adressleitungen benötigt als das SD-RAM, können die Adressleitungen 17 und 18 für Steuersignale des SD-RAMs benutzt werden. Tabelle 3.1 verdeutlicht diese Zuordnung.

| SD- $RAM$                               | FPGA                  | S-RAM |

|-----------------------------------------|-----------------------|-------|

| $\frac{\overline{S_0}}{\overline{S_1}}$ | $SDRAM\_S0$           |       |

| $\overline{S_1}$                        | $SDRAM\_S1$           |       |

| $CKE_0$                                 | $SDRAM\_CKE0$         |       |

| $CKE_1$                                 | $SDRAM\_CKE1$         |       |

| $CK_0$                                  | $_{RAM\ CLK}$         | CLK   |

| $CK_1$                                  | $\int_{0}^{RAM} -CLR$ | CLK   |

| $\overline{WE}$  | $RAM\_WE$    | $\overline{WE}$   |

|------------------|--------------|-------------------|

| $A_{013}$        | $RAM\_A0A13$ | $A_{013}$         |

| $BA_0$           | $RAM\_A14$   | $A_{14}$          |

| $BA_1$           | $RAM\_A15$   | $A_{15}$          |

|                  | $RAM\_A16$   | $A_{16}$          |

| $\overline{RAS}$ | $RAM\_A17$   | $A_{17}$          |

| $\overline{CAS}$ | $RAM\_A18$   | $A_{18}$          |

|                  | $SRAM\_ADV$  | ADV               |

|                  | $SRAM\_OE$   | $\overline{OE}$   |

|                  | low          | $\overline{CKE}$  |

|                  | $SRAM\_CS$   | $\overline{CS_1}$ |

|                  | low          | $\overline{CS_2}$ |

|                  | high         | $CS_2$            |

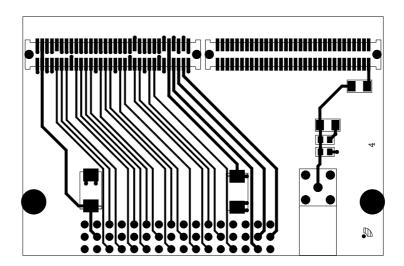

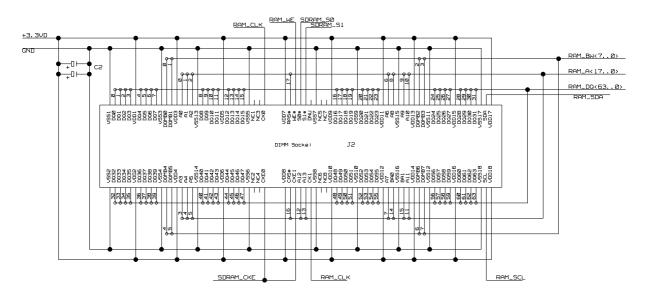

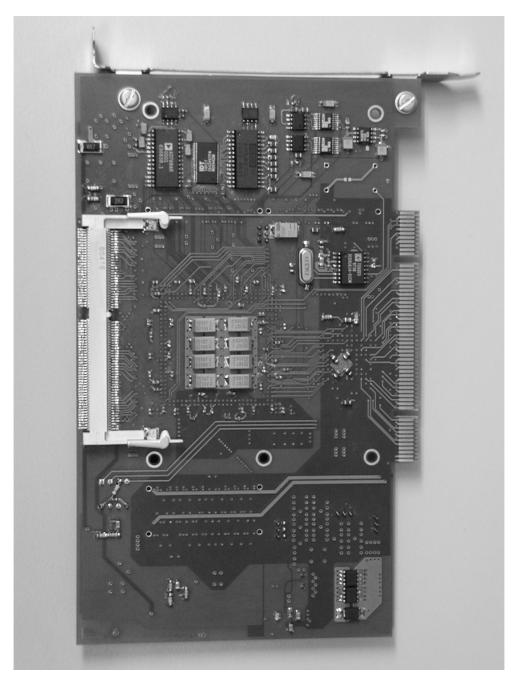

Die Verlegung dieser Verbindungen auf der Platine ist in Abbildung 3.12 gezeigt, wobei das S-RAM mit zwei Bausteinen auf der Oberseite der Platine liegt und der Sockel für das SD-RAM Modul auf der Rückseite der Platine.

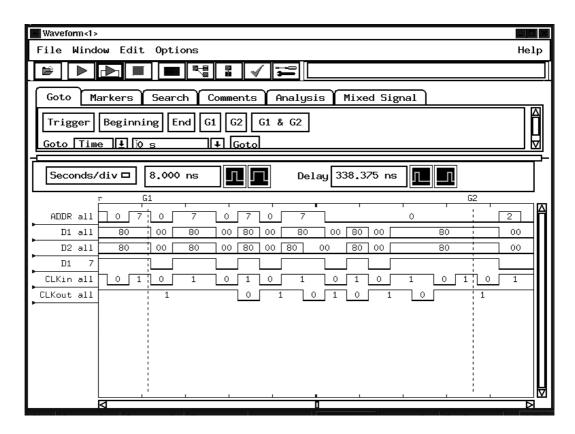

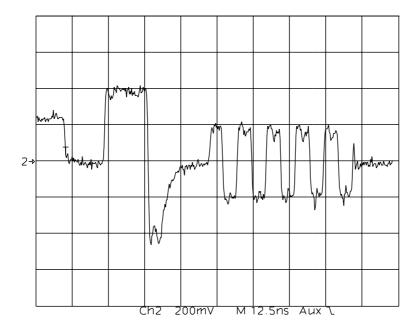

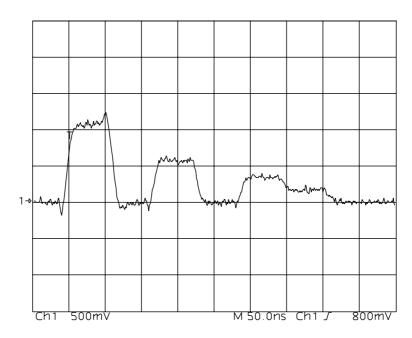

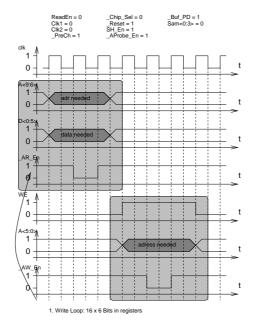

Tabelle 3.1: RAM Ansteuerung